SN75DP126

SLLSEA9B - FEBRUARY 2012-REVISED AUGUST 2015

# SN75DP126 DisplayPort™ 1:2 Re-Driver Switch with TMDS Translator

### **Features**

- One Dual-Mode DisplayPort™ (DP++) Input; Switchable to One DP++ Output or One TMDS Output Compatible with HDMI 1.4b and DVI

- Supports DP v1.1a and DP v1.2 Signaling Including HBR2 Data Rates to 5.4 Gbps

- Supports HDMI 1.4b with TMDS Clock Frequencies up to 340 MHz with 10 m Cable

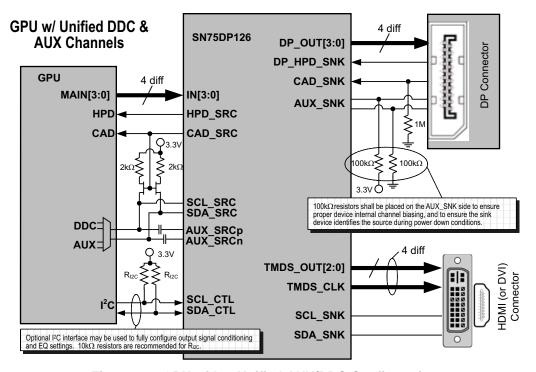

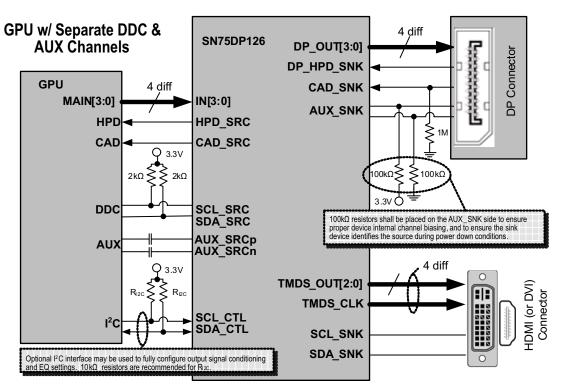

- Glue-less interface to AMD, Intel, and NVIDIA **Graphics Processors**

- Auto-Configuration Through Link Training for DisplayPort Connection

- Integrated DDC-Accessible DP-HDMI Adaptor ID for HDMI/DVI Sink Recognition

- Output Signal Conditioning with Tunable Voltage Swing and Pre-Emphasis Gain for both DisplayPort and TMDS Outputs

- Highly-Configurable Input-Variable Equalizer

- Two Device Options Including a Dual Power-Supply Configuration for Lowest Power

- 2-kV ESD HBM Protection

- Temperature Range: 0°C to 85°C

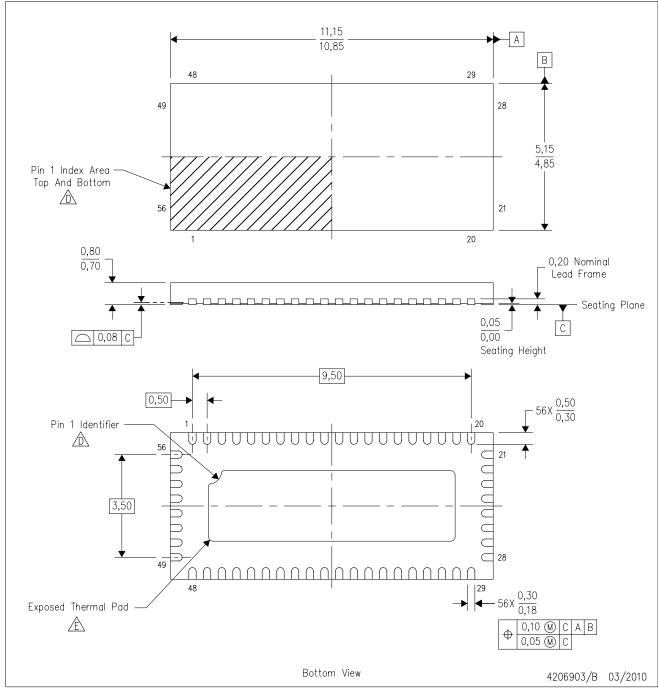

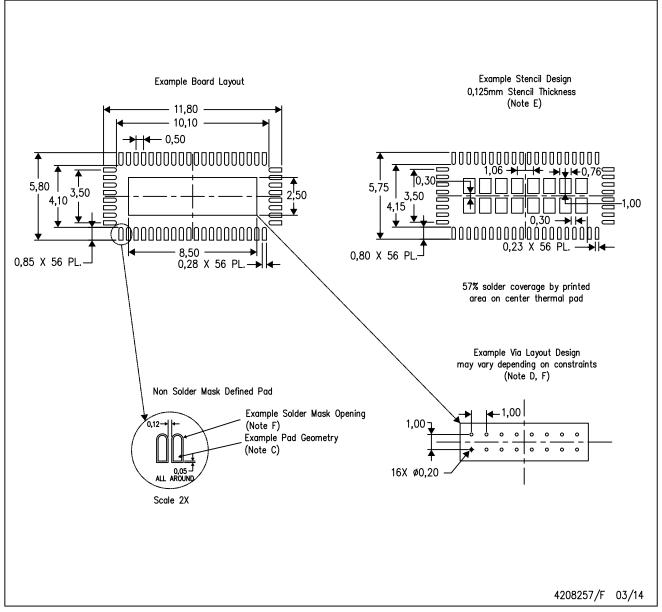

- 56-Pin 5-mm x 11-mm QFN Package

## **Applications**

- Notebook PC

- Desktop PC

- PC Docking Station

- PC Standalone Video Card

## 3 Description

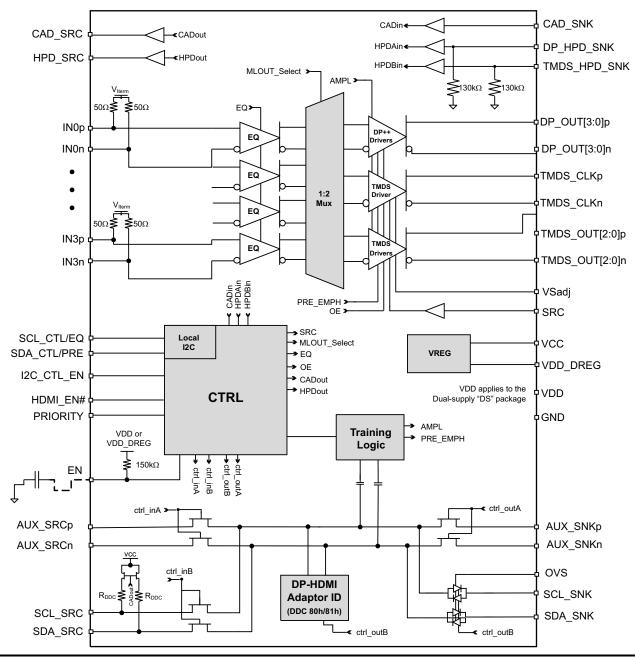

SN75DP126 switches one DisplayPort (DP++) input to one Dual-Mode DisplayPort (DP++) sink output or one HDMI/DVI sink output. The HDMI/DVI output has a built-in level translator compliant with DVI 1.0 and HDMI 1.4b standard TMDS signaling, and is specified up to a maximum data rate of 3.4 Gbps, supporting resolutions greater than 1920 X 1440 and HDTV deep color at 1080p. An integrated DP-HDMI Adaptor ID buffer can be accessed when the HDMI/DVI sink is selected to indicate support for HDMI signaling.

The device compensates for PCB-related frequency loss and switching-related loss to provide the optimum electrical performance from source to sink. The DP++ Main Link signal inputs featureconfigurable equalizers with selectable boost settings.

At the SN75DP126 DP++ Main Link output, four primary levels of differential output voltage (V<sub>OD</sub>) swing and four primary levels of pre-emphasis are available as well as a secondary level of boost adjustment, programmed through I<sup>2</sup>C, for fine-tuning the Main Link output. The device can monitor the AUX channel and automatically adjust output signaling levels and input equalizers based on DP Link Training commands.

#### Device Information<sup>(1)</sup>

| PART NUMBER | UMBER PACKAGE BODY |                    |  |

|-------------|--------------------|--------------------|--|

| SN75DP126   | WQFN (56)          | 11.00 mm × 5.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

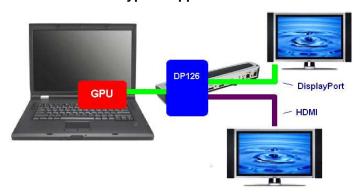

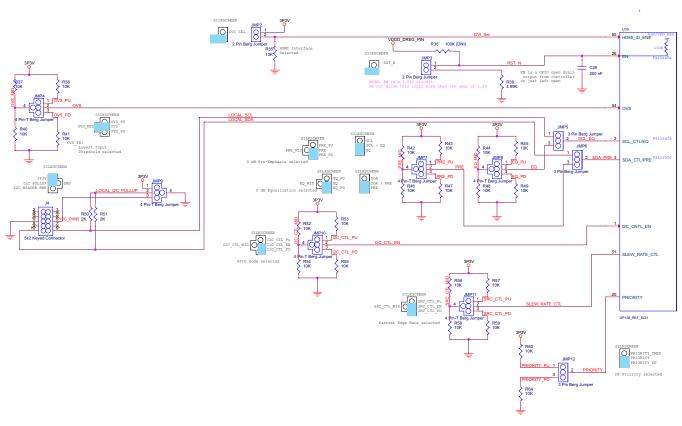

### **Typical Application**

### **Table of Contents**

| 2<br>3 | Applications 1                                              | 8  |                                                        |                  |

|--------|-------------------------------------------------------------|----|--------------------------------------------------------|------------------|

| 3      |                                                             | 0  | Detailed Description                                   | 19               |

|        | Description 1                                               |    | 8.1 Overview                                           | 19               |

| 4      | Revision History2                                           |    | 8.2 Functional Block Diagram                           | 19               |

| 5      | Description (continued)3                                    |    | 8.3 Feature Description                                | <mark>2</mark> 0 |

| 6      | Pin Configuration and Functions                             |    | 8.4 Device Functional Modes                            |                  |

| 7      | Specifications6                                             |    | 8.5 Register Maps                                      | 28               |

| •      | 7.1 Absolute Maximum Ratings                                | 9  | Application and Implementation                         | 36               |

|        | 7.2 ESD Ratings                                             |    | 9.1 Application Information                            | 36               |

|        | 7.3 Recommended Operating Conditions                        |    | 9.2 Typical Application                                | 36               |

|        | 7.4 Thermal Information                                     | 10 | Power Supply Recommendations                           | 40               |

|        | 7.5 Power Supply Electrical Characteristics                 |    | 10.1 Analog vs Digital vs High Power                   | 40               |

|        | 7.6 Main Link Input Electrical Characteristics 9            |    | 10.2 Analog Power-Supply Pins and Analog Refe Voltages |                  |

|        | 7.7 DisplayPort Main Link Output Electrical Characteristics | 11 | Layout                                                 | 40               |

|        | 7.8 HDMI/DVI Main Link Output Electrical                    |    | 11.1 Layout Guidelines                                 | 40               |

|        | Characteristics                                             |    | 11.2 Layout Example                                    | 43               |

|        | 7.9 HPD/CAD/EN Electrical Characteristics 10                | 12 | Device and Documentation Support                       | 45               |

|        | 7.10 AUX/DDC/I <sup>2</sup> C Electrical Characteristics    |    | 12.1 Community Resources                               | 45               |

|        | 7.11 DisplayPort Main Link Output Switching                 |    | 12.2 Trademarks                                        | 45               |

|        | Characteristics 11                                          |    | 12.3 Electrostatic Discharge Caution                   | 45               |

|        | 7.12 HDMI/DVI Main Link Switching Characteristics 12        |    | 12.4 Glossary                                          | 45               |

|        | 7.13 HPD/CAD Switching Characteristics                      | 13 | Mechanical, Packaging, and Orderable Information       | 4                |

### 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision A (March 2012) to Revision B

**Page**

#### Changes from Original (February 2012) to Revision A

Page

Submit Documentation Feedback

Copyright © 2012–2015, Texas Instruments Incorporated

## 5 Description (continued)

The SN75DP126 offers separate AUX and DDC source interfaces that connect to the DisplayPort AUX sink channel and the HDMI DDC sink channel, that seamlessly interface to graphics processor (GPU) comprising separate DDC and AUX interfaces as well as GPUs with combined DDC/AUX. Other sideband circuits such as Hot Plug Detect (HPD) are optimized to reduce external components providing a seamless connection to Intel, AMD, and NVIDIA graphics processors.

The SN75DP126 is optimized for mobile applications, and contains activity-detection circuitry on the DP++ Main Link input that transitions to a low-power Output Disable mode in the absence of a valid input signal. Other low power modes are supported, including a Standby mode with typical dissipation of ~2 mW when no video sink (for example, monitor) is connected.

The device is characterized for an extended operational temperature range from 0°C to 85°C.

At the SN75DP126 HDMI/DVI output, the differential output voltage swing and pre-emphasis levels are configurable. The SN75DP126 output signal conditioning and EQ parameters are programmable through the I<sup>2</sup>C interface, the VSadj terminal, and the I2C\_CTL\_EN terminal. The HDMI/DVI sink TMDS output slew rate is controlled by the SRC control input.

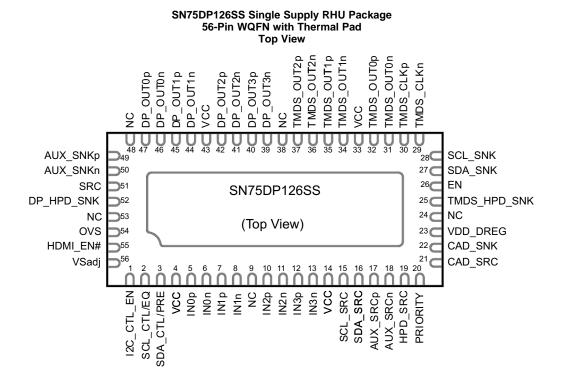

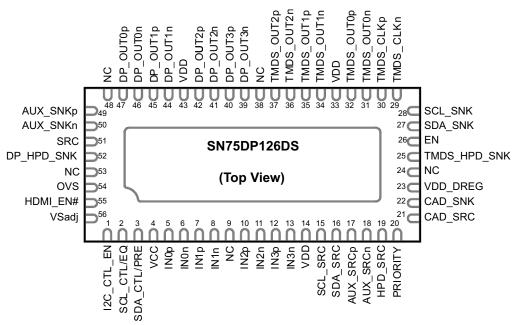

## 6 Pin Configuration and Functions

Copyright © 2012–2015, Texas Instruments Incorporated

#### SN75DP126DS Dual Supply RHU Package 56-Pin WQFN with Thermal Pad Top View

#### Pin Functions

| PIN                       |            | 1/0                            |                                                  |

|---------------------------|------------|--------------------------------|--------------------------------------------------|

| SIGNAL                    | SIGNAL NO. |                                | DESCRIPTION                                      |

| DISPLAYPORT AND           | HDMI MAI   | N LINK TERM                    | INALS                                            |

| IN0p, IN0n                | 5, 6       |                                | DisplayPort Main Link Lane 0 Differential Input  |

| IN1p, IN1n                | 7, 8       | 100Ω<br>Differential           | DisplayPort Main Link Lane 1 Differential Input  |

| IN2p, IN2n                | 10, 11     | Input                          | DisplayPort Main Link Lane 2 Differential Input  |

| IN3p, IN3n                | 12, 13     | •                              | DisplayPort Main Link Lane 3 Differential Input  |

| DP_OUT0p,<br>DP_OUT0n     | 47, 46     | 100Ω<br>Differential<br>Output | DisplayPort Main Link Lane 0 Differential Output |

| DP_OUT1p,<br>DP_OUT1n     | 45, 44     |                                | DisplayPort Main Link Lane 1 Differential Output |

| DP_OUT2p,<br>DP_OUT2n     | 42, 41     |                                | DisplayPort Main Link Lane 2 Differential Output |

| DP_OUT3p,<br>DP_OUT3n     | 40, 39     |                                | DisplayPort Main Link Lane 3 Differential Output |

| TMDS_CLKp,<br>TMDS_CLKn   | 30, 29     |                                | HDMI/DVI Clock TMDS Differential Output          |

| TMDS_OUT0p,<br>TMDS_OUT0n | 32, 31     | 100Ω<br>Differential           | HDMI/DVI Data Lane 0 TMDS Differential Output    |

| TMDS_OUT1p,<br>TMDS_OUT1n | 35, 34     | Output<br>(Failsafe)           | HDMI/DVI Data Lane 1 TMDS Differential Output    |

| TMDS_OUT2p,<br>TMDS_OUT2n | 37, 36     |                                | HDMI/DVI Data Lane 2 TMDS Differential Output    |

Submit Documentation Feedback

Copyright © 2012–2015, Texas Instruments Incorporated

# Pin Functions (continued)

| PIN                   |         |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|-----------------------|---------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SIGNAL                | NO.     | I/O                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| AUX CHANNEL AND       | DDC DAT | A TERMINALS         | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| AUX_SRCp,<br>AUX_SRCn | 17, 18  |                     | Source Side Bidirectional DisplayPort Auxiliary Data Channel. These signals are connected to the AUX_SNK channel when the DisplayPort sink is selected; AC coupling should be implemented.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| AUX_SNKp,<br>AUX_SNKn | 49, 50  | I/O                 | Sink Side Bidirectional DisplayPort Auxiliary Data Channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SCL_SRC,<br>SDA_SRC   | 15, 16  | (Failsafe)          | Source Side Bidirectional I $^2$ C Display Data Channel (DDC) for TMDS modes. These terminals include integrated 60 k $\Omega$ pull-up resistors.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| SCL_SNK,<br>SDA_SNK   | 28, 27  |                     | DMI/DVI Sink Side Bidirectional I <sup>2</sup> C Display Data Channel (DDC).                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| HOT PLUG DETECT       | AND CAD | TERMINALS           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

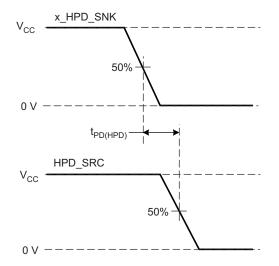

|                       |         |                     | Hot Plug Detect Output to the Source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

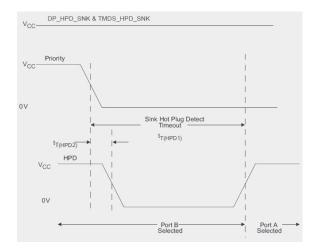

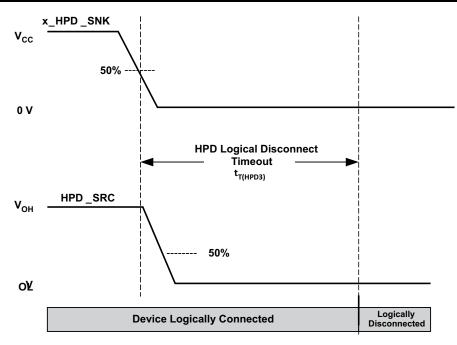

| HPD_SRC               | 19      | Output              | This output shall be driven high when the source shall be connected to either the HDMI/DVI sink or the DisplayPort sink, and driven low when no sink is selected. This output will be asserted for a fixed period of time during active (PRIORITY based) transition from one sink to the other.                                                                                                                                                                                                                            |  |  |  |  |

| CAD_SRC               | 21      |                     | Source Side Cable Adapter Detect Output. When the DisplayPort sink is selected, this output represents the condition of the CAD_SNK input, active high as default; polarity may be programmed through the local I <sup>2</sup> C interface. When the HDMI/DVI sink is selected, this output is driven high.                                                                                                                                                                                                                |  |  |  |  |

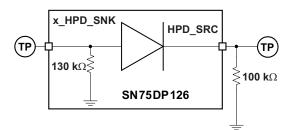

| DP_HPD_SNK            | 52      | Input<br>(Failsafe) | DisplayPort Hot Plug Detect Input from Sink. This device input is 5-V tolerant, and includes an integrated 130 k $\Omega$ pull-down resistor.  Note: pull this input high during compliance testing or use ${}^{\rho}C$ control interface to go into compliance test mode and control DP_HPD_SNK and HPD_SRC by software.                                                                                                                                                                                                  |  |  |  |  |

| TMDS_HPD_SNK          | 25      |                     | HDMI/DVI Hot Plug Detect Input from Sink. This device input is 5-V tolerant, and includes an integrated 130 k $\Omega$ pull-down resistor.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| CAD_SNK               | 22      | Input               | DisplayPort Cable Adapter Detect Input. An external $1M\Omega$ resistor to GND is recommended. This terminal is used to select DP mode (low input) or TMDS mode (high input) when the DisplayPort sink is selected .                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| CONTROL TERMINA       | ALS     |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| VSadj                 | 56      |                     | HDMI/DVI Sink Differential Voltage Swing Control. An external resistor connecting this pin to GND determines the output voltage swing. A value of 4.7 k $\Omega$ is recommended to provide a typical swing of 1000 mV. VSadj resistor values of 4.7 k $\Omega$ ± 1 k $\Omega$ control the output voltage swing in a near-linear function of approximately 2 mV/100 $\Omega$ . Note: this input does not impact the output when a DisplayPort sink is selected and operating in TMDS mode (as supported by the DP++ source) |  |  |  |  |

| HDMI_EN#              | 55      | Input               | HDMI/DVI Sink Type Control. When this input is low, the output is HDMI 1.4b compliant when the HDMI/DVI sink is selected. When this input is high, the output is DVI 1.0 compliant when the HDMI/DVI sink is selected.                                                                                                                                                                                                                                                                                                     |  |  |  |  |

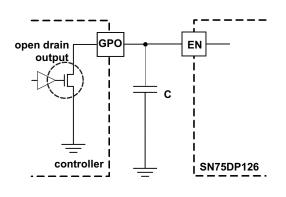

| PRIORITY              | 20      |                     | Output Select Priority. Selects the priority for the output in the case both DP_HPD_SNK and TMDS_HPD_SNK are high indicating two sinks are connected. When low, the DisplayPort sink has priority selection. When high, the HDMI/DVI sink has priority.  Note: An external RC circuit should be connected to the PRIORITY pin to insure that the SN76DP126 functions properly with some non-compliant monitors. See the SN75DP126 Reference Schematics for more information.                                               |  |  |  |  |

|                       |         |                     | TMDS Slew Rate Control. When the HDMI/DVI sink is selected, the slew rate is controlled by the HDMI_EN# input and by the SRC control input:                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                       |         |                     | V <sub>IL</sub> = TMDS rise and fall times meet tT1 specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| SRC                   | 51      | 3-Level<br>Input    | $V_{IM}$ (between $V_{IL}$ and $V_{IH}$ ) = TMDS rise and fall times meet $t_{T2}$ specifications (Recommended setting)                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                       |         | mpat                | $V_{IH}$ = TMDS rise and fall times meet $t_{T3}$ specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                       |         |                     | Note: this input does not impact the output when a DisplayPort sink is selected and operating in TMDS mode (as supported by the DP++ source)                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                       |         |                     | Source Side DDC Input/Output Buffer Control Input. When the HDMI/DVI sink is selected, the DDC $V_{OL}$ and $V_{IL}$ is controlled by the OVS control input:                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| ovs                   | 54      | 3-Level<br>Input    | $V_{IL}$ = Source DDC interface meets $V_{OL(3)}$ and $V_{IL(3)}$ specifications                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                       |         | mput                | $V_{IM}$ (between $V_{IL}$ and $V_{IH}$ ) = Source DDC interface meets $V_{OL(2)}$ and $V_{IL(2)}$ specifications                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                       |         |                     | $V_{IH}$ = Source DDC interface meets $V_{OL(1)}$ and $V_{IL(1)}$ specifications                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| I2C_CTL_EN            | 1       | 3-Level<br>Input    | Local $I^2C$ Interface Enable Control and Target Address Select. When low, the local $I^2C$ interface is disabled; when input is between $V_{IL}$ and $V_{IH}$ levels, the local $I^2C$ interface is enabled and is addressed at 0x58h (Write) and 0x59h (Read); when input is high, the local $I^2C$ interface is enabled and is addressed at 0x5Ah (Write) and 0x5Bh (Read).                                                                                                                                             |  |  |  |  |

| SCL_CTL/EQ            | 2       | 3-Level<br>Input    | Local I <sup>2</sup> C Interface Clock, or Equalizer Setting Control Input. When I2C_CTL_EN is input high or floating, this terminal is the local I <sup>2</sup> C interface clock used to configure SN75DP126.                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                       |         | (Failsafe)          | When I2C_CTL_EN is low, this terminal can be used to configure the input EQ.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

Copyright © 2012–2015, Texas Instruments Incorporated

### Pin Functions (continued)

| PIN             |                           |                                       | DEGODINATION                                                                                                                                                                                                                                                                              |

|-----------------|---------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL          | NO.                       | I/O                                   | DESCRIPTION                                                                                                                                                                                                                                                                               |

|                 |                           |                                       | Local I <sup>2</sup> C Interface Data, or TMDS Pre-emphasis Control Input. When I2C_CTL_EN is input high or floating, this terminal is the local I <sup>2</sup> C interface data signal.                                                                                                  |

|                 |                           |                                       | When I2C_CTL_EN is low, this terminal configures the HDMI/DVI sink TMDS output pre-emphasis as:                                                                                                                                                                                           |

|                 |                           | I/O                                   | $V_{\rm IL}$ = 0 dB pre-emphasis applied to TMDS output                                                                                                                                                                                                                                   |

| SDA_CTL/PRE     | 3                         | 3-Level                               | V <sub>IM</sub> = Not Recommended                                                                                                                                                                                                                                                         |

|                 |                           | Input<br>(Failsafe)                   | $V_{IH}$ = 2 dB pre-emphasis applied to TMDS output                                                                                                                                                                                                                                       |

|                 |                           | (                                     | When 2 dB pre-emphasis is enabled, the steady state TMDS output swing is reduced from that selected by VSadj, and the transition time is reduced from that selected by SRC.                                                                                                               |

|                 |                           |                                       | Note: this input does not impact the output when a DisplayPort sink is selected and operating in TMDS mode (as supported by the DP++ source), whereas no pre-emphasis is applied to the output signal in this condition.                                                                  |

|                 |                           | Low-Voltage<br>26 Input<br>(Failsafe) | Device Enable / Reset (Power Down). This input incorporates internal pullup of 150 k $\Omega$ , and only 1.2-V tolerant (the high level shall be limited to 1.2 V).                                                                                                                       |

|                 | 26                        |                                       | When high, the device is enabled for normal operation.                                                                                                                                                                                                                                    |

| EN              |                           |                                       | When low, the device is in power down mode; all outputs excluding HPD_SRC and CAD_SRC are high-impedance, and inputs excluding DP_HPD_SNK, TMDS_HPD_SNK, and CAD_SNK are ignored; all local I <sup>2</sup> C and DPCD registers are reset to their default values when this input is low. |

|                 |                           |                                       | At power up, the EN input must not be de-asserted until the $V_{\text{CC}}$ supply has reached at least the minimum recommended supply voltage level.                                                                                                                                     |

| SUPPLY AND GROU | ND TERMI                  | NALS                                  |                                                                                                                                                                                                                                                                                           |

|                 |                           | DP126SS                               |                                                                                                                                                                                                                                                                                           |

| V <sub>CC</sub> |                           | 1, 33, 43                             | 3.3-V Supply                                                                                                                                                                                                                                                                              |

|                 | SN/51                     | DP126DS<br>4                          |                                                                                                                                                                                                                                                                                           |

| V <sub>DD</sub> | SN75DP126DS<br>14, 33, 43 |                                       | 1.05-V Supply                                                                                                                                                                                                                                                                             |

|                 |                           |                                       | SN75DP126SS: Digital voltage regulator decoupling; install 1uF to GND.                                                                                                                                                                                                                    |

| $V_{DD\_DREG}$  | 23                        |                                       | SN75DP126DS: Treat same as $V_{DD}$ ; this pin will be most noisy of all $V_{DD}$ terminals and needs a de-coupling capacitor nearby.                                                                                                                                                     |

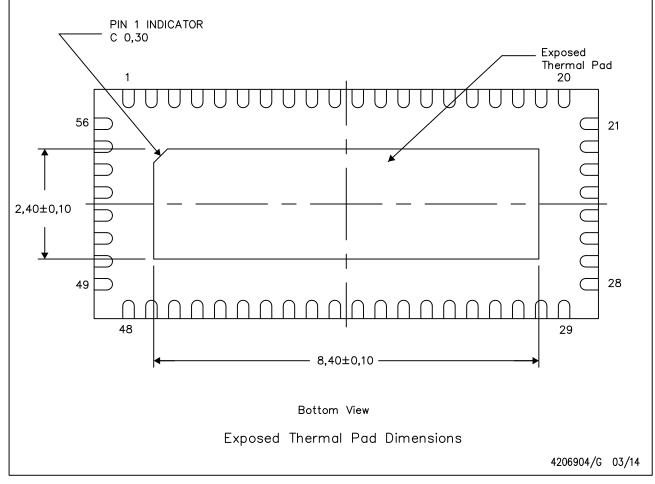

| GND             | Exposed                   | Thermal Pad                           | Ground. Reference GND connection shall be made to the exposed thermal pad.                                                                                                                                                                                                                |

| NC              | 9, 53,                    | 38, 48, 24                            | No connect. These terminals may be left unconnected, or connect to GND.                                                                                                                                                                                                                   |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                      |                                                                                                                                                                                                                                                                                                   | MIN                                                              | MAX                                | UNIT |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------|------|

| Cumply voltage range | Voltage range         V <sub>CC</sub> -0.3           V <sub>DD</sub> , V <sub>DD_DREG</sub> -0.3           Main Link I/O Differential Voltage         -0.3           DP_HPD_SNK, TMDS_HPD_SNK, SCL_SNK, SDA_SNK         -0.3           EN         -0.3           All other terminals         -0.3 | 4                                                                | V                                  |      |

| Supply voltage range | $V_{DD}, V_{DD\_DREG}$                                                                                                                                                                                                                                                                            | -0.3                                                             | 1.3                                | V    |

|                      | Main Link I/O Differential Voltage                                                                                                                                                                                                                                                                | -0.3                                                             | 1.4                                | V    |

| Voltago rango        | DP_HPD_SNK, TMDS_HPD_SNK, SCL_SNK, SDA_SNK                                                                                                                                                                                                                                                        | -0.3 4 V<br>-0.3 1.3 V<br>-0.3 1.4 V<br>-0.3 5.5 V<br>-0.3 1.3 V | V                                  |      |

| Voltage range        | EN                                                                                                                                                                                                                                                                                                | -0.3                                                             | 1.3                                | V    |

|                      | All other terminals                                                                                                                                                                                                                                                                               | -0.3                                                             | 4<br>1.3<br>1.4<br>5.5<br>1.3<br>4 | V    |

| T <sub>stg</sub>     | Storage temperature                                                                                                                                                                                                                                                                               | <del>-</del> 55                                                  | 150                                | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                                            |                                                                                |       | VALUE | UNIT |

|--------------------------------------------|--------------------------------------------------------------------------------|-------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 | .,    |      |

|                                            | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V     |      |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Submit Documentation Feedback

Copyright © 2012–2015, Texas Instruments Incorporated

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

| -                      | · ·                                    |                                                                  | MIN                    | NOM  | MAX                    | UNIT    |

|------------------------|----------------------------------------|------------------------------------------------------------------|------------------------|------|------------------------|---------|

| V <sub>CC</sub>        | Supply voltage                         |                                                                  | 3                      | 3.3  | 3.6                    | V       |

| $V_{DD}$               | Digital core and Main Lir              | nk supply voltage                                                | 1.0                    | 1.05 | 1.2                    | V       |

| T <sub>A</sub>         | Operating free-air temper              | rature                                                           | 0                      |      | 85                     | °C      |

| T <sub>S</sub>         | Storage temperature                    |                                                                  | -65                    |      | 150                    | °C      |

| T <sub>CASE</sub>      | Case temperature                       |                                                                  |                        | 97.1 |                        | °C      |

| DP++ MA                | IN LINK TERMINALS                      |                                                                  |                        |      |                        |         |

| $V_{ID}$               | Peak-to-peak input differ              | rential voltage; RBR, HBR, HBR2                                  | 0.3                    |      | 1.40                   | Vpp     |

| d <sub>R(DP)</sub>     | Data rate; DisplayPort si              | nk                                                               |                        | 5.4  |                        | Gbps    |

| d <sub>R(HDMI)</sub>   | Data rate; HDMI sink                   |                                                                  |                        | 3.4  |                        | Gbps    |

| C <sub>AC</sub>        | AC coupling capacitance                | oling capacitance (each DP input and each DP output line) 75 200 |                        | nF   |                        |         |

| R <sub>tdiff</sub>     | Differential output termin             | ation resistance; DisplayPort sink and HDMI sink                 | 80                     | 100  | 120                    | Ω       |

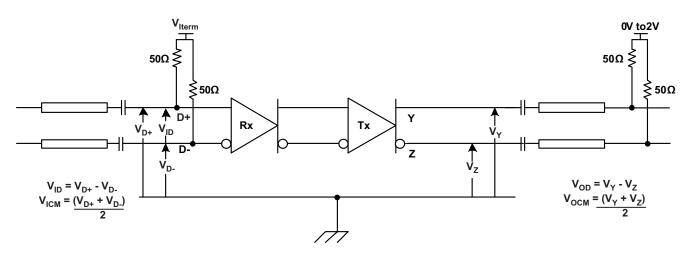

| V <sub>Oterm</sub>     | Output termination voltage             | ge (AC coupled)                                                  | 0                      |      | 2                      | V       |

| t <sub>SK(HBR2)</sub>  | Intra-pair skew at the inp             | out at 5.4 Gbps                                                  |                        | 20   |                        | ps      |

| t <sub>SK(HBR)</sub>   | Intra-pair skew at the inp             | out at 2.7 Gbps                                                  |                        | 100  |                        | ps      |

| t <sub>SK(RBR)</sub>   | Intra-pair skew at the inp             | out at 1.62 Gbps                                                 |                        | 300  |                        | ps      |

| AUX CHA                | NNEL DATA TERMINAL                     | s                                                                |                        |      |                        |         |

| $V_{I-DC}$             | DC Input Voltage, AUX_                 | SRCp/n and AUX_SNKp/n (DP and TMDS modes)                        | -0.5                   |      | 3.6                    | V       |

| $V_{ID}$               | Differential input voltage             | amplitude (DP mode only)                                         | 300                    |      | 1400                   | $mV_PP$ |

| d <sub>R(AUX)</sub>    | Data rate (before Manch                | ester encoding)                                                  | 0.8                    | 1    | 1.2                    | Mbps    |

| d <sub>R(FAUX)</sub>   | Data rate Fast AUX (300                | ppm frequency tolerance)                                         |                        | 720  |                        | Mbps    |

| t <sub>jccin_adj</sub> | Cycle-to-cycle AUX inpu                | t jitter adjacent cycle (DP mode only)                           |                        |      | 0.05                   | UI      |

| t <sub>jccin</sub>     | Cycle-to-cycle AUX inpu                | t jitter within one cycle (DP mode only)                         |                        |      | 0.1                    | UI      |

| C <sub>AC</sub>        | AUX AC coupling capac                  | itance                                                           | 75                     |      | 200                    | nF      |

| DDC, LO                | CAL I <sup>2</sup> C, AND CONTROL      | TERMINALS                                                        |                        |      |                        |         |

| \/                     | DC Input Voltage                       | DP_HPD_SNK, TMDS_HPD_SNK, SCL/SDA_SNK                            | -0.3                   |      | 5.5                    | V       |

| V <sub>I-DC</sub>      | DC input voltage                       | All other DDC, local I <sup>2</sup> C, and control terminals     | -0.3                   |      | 3.6                    | V       |

| V <sub>IH</sub>        | High-level input voltage               | SCL/SDA_SRC                                                      | 2.1                    |      |                        | V       |

| VIН                    | r light-level input voltage            | All other DDC, Local I <sup>2</sup> C, and control terminals     | V <sub>CC</sub> -0.5   |      |                        | V       |

| $V_{IL}$               | Low-level input voltage(1              | )                                                                |                        | 0.5  |                        | V       |

| $V_{IM}$               | Mid-level input voltage <sup>(2)</sup> |                                                                  | V <sub>CC</sub> /2-0.3 |      | V <sub>CC</sub> /2+0.3 | V       |

| $d_R$                  | Data rate                              |                                                                  |                        | 100  |                        | kbps    |

| $V_{TH(EN)}$           | EN input threshold voltage 280 8       |                                                                  | 800                    | mV   |                        |         |

| f <sub>SCL</sub>       |                                        | SCL clock frequency standard I <sup>2</sup> C mode               |                        |      |                        | kHz     |

| t <sub>w(L)</sub>      | SCL clock low period sta               | indard I <sup>2</sup> C mode                                     | 4.7                    |      |                        | μs      |

| t <sub>w(H)</sub>      | SCL clock high period st               | andard I <sup>2</sup> C mode                                     | 4.0                    |      |                        | μs      |

| C <sub>bus</sub>       | Total capacitive load for              | each bus line (DDC and local I <sup>2</sup> C terminals)         |                        | 400  |                        | pF      |

<sup>(1)</sup> V<sub>IL</sub> for SCL\_SRC and SDA\_SRC are listed in the AUX/DDC/I<sup>2</sup>C Electrical Characteristics Table.

(2) V<sub>IM</sub> is only applicable for 3-Level control pins.

#### 7.4 Thermal Information

|                      |                                              | SN75DP126  |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RHU (WQFN) | UNIT |

|                      |                                              | 56 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 35         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 25         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 15         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 2          | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 10         | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 8          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 7.5 Power Supply Electrical Characteristics

over recommended operating conditions (unless otherwise noted)

|                 | PARAMETER (1)                         | TEST CONDITIONS                                                                   | MIN | TYP  | MAX  | UNIT  |

|-----------------|---------------------------------------|-----------------------------------------------------------------------------------|-----|------|------|-------|

|                 |                                       | 4 DP Lanes; DP Sink                                                               |     |      |      |       |

|                 |                                       | Maximum Conditions: DP at 5.4-Gbps PRBS, V <sub>OD</sub> = 510 mV <sub>pp</sub> , |     |      |      |       |

|                 |                                       | PRE = 6 dB; AUX at 1-Mbps PRBS, V <sub>ID</sub> = 1000 mVpp; EQ = 6 dB            |     | 138  | 242  | mA    |

|                 |                                       | Typical Conditions: DP at 5.4-Gbps PRBS, V <sub>OD</sub> = 510 mVpp,              |     |      |      |       |

|                 |                                       | PRE = 0 dB AUX and $I^2C$ Idle; EQ = 3 dB                                         |     |      |      |       |

|                 |                                       | 2 DP Lanes; DP Sink                                                               |     |      |      |       |

|                 |                                       | Maximum Conditions: DP at 5.4-Gbps PRBS, V <sub>OD</sub> = 510 mVpp,              |     |      |      |       |

|                 |                                       | PRE = 6 dB; AUX at 1-Mbps PRBS, V <sub>ID</sub> = 1000 mVpp; EQ = 6 dB            |     | 73   | 125  | mA    |

|                 |                                       | Typical Conditions: DP at 5.4-Gbps PRBS, V <sub>OD</sub> = 510 mVpp,              |     |      |      |       |

|                 | Device current under normal           | PRE = 0 dB AUX and $I^2C$ Idle; EQ = 3 dB                                         |     |      |      | 70 mA |

| I <sub>CC</sub> | operation                             | 1 DP Lanes; DP Sink                                                               |     |      |      |       |

|                 |                                       | Maximum Conditions: DP at 5.4-Gbps PRBS, V <sub>OD</sub> = 510 mVpp,              |     |      |      |       |

|                 |                                       | PRE = 6 dB; AUX at 1-Mbps PRBS, V <sub>ID</sub> = 1000 mVpp; EQ = 6 dB            |     | 42   | 70   |       |

|                 |                                       | Typical Conditions: DP at 5.4-Gbps PRBS, V <sub>OD</sub> = 510 mVpp,              |     |      |      |       |

|                 |                                       | PRE = 0 dB AUX and $I^2C$ Idle; EQ = 3 dB                                         |     |      |      | 70 mA |

|                 |                                       | 4 DP Lanes; HDMI Sink                                                             |     |      |      |       |

|                 |                                       | Maximum Conditions: TMDS at 3.4 Gbps, V <sub>OD</sub> = 1200 mVpp,                |     |      |      |       |

|                 |                                       | V <sub>ID</sub> = 1000 mVpp                                                       |     | 130  | 160  | mA    |

|                 |                                       | Typical Conditions: TMDS at 3.4 Gbps, V <sub>OD</sub> = 1000 mVpp,                |     |      |      |       |

|                 |                                       | DDC and I <sup>2</sup> C Idle                                                     |     |      |      |       |

| $I_{SD}$        | Shutdown mode current                 | 4 DP Lanes                                                                        |     | 0.55 | 4.00 | mA    |

| $I_{SBY}$       | Standby mode current                  | 4 DP Lanes.                                                                       |     | 0.85 | 4.00 | mA    |

| $I_{D3}$        | D3 power down mode current            | 4 DP Lanes.                                                                       |     | 10   | 15   | mA    |

| I <sub>OD</sub> | Output disable (squelch) mode current | 4 DP Lanes.                                                                       |     | 53   | 75   | mA    |

<sup>(1)</sup> Values are V<sub>CC</sub> supply measurements for SN75DP126SS and V<sub>DD</sub> supply measurements for the SN75DP126DS; the maximum V<sub>CC</sub> supply measurement for the SN75DP126DS is 8 mA during normal operation and 0.5 mA during shutdown, standby, and D3 power down modes.

Submit Documentation Feedback

Copyright © 2012–2015, Texas Instruments Incorporated

## 7.6 Main Link Input Electrical Characteristics

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                           | TEST CONDITIONS                                                                                                          | MIN        | TYP | MAX              | UNIT |  |

|----------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------|-----|------------------|------|--|

| A <sub>EQ(HBR)</sub> | Equalizer gain for RBR/HBR                          | See Table 4 for EQ setting details;<br>Max value represents the typical value for the<br>maximum configurable EQ setting |            |     | 9                | dB   |  |

| AEQ(HBR2)            | Equalizer gain for HBR2                             |                                                                                                                          |            |     | 18               | dB   |  |

| AEQ(TMDS_D)          | Equalizer gain for DP sink in TMDS mode; data lanes |                                                                                                                          |            |     | 9                | dB   |  |

| AEQ(TMDS_C)          | Equalizer gain for DP sink in TMDS mode; clock lane |                                                                                                                          |            |     | 3                | dB   |  |

| AEQ(HDMI_D)          | EQ gain, HDMI sink; data lanes                      |                                                                                                                          |            |     | 9                | dB   |  |

| AEQ(HDMI_C)          | EQ gain, HDMI sink; clock lane                      |                                                                                                                          |            |     | 3                | dB   |  |

| RIN                  | Input termination impedance                         |                                                                                                                          | 40         | 50  | 60               | Ω    |  |

| VIterm               | Input termination voltage                           | AC coupled; self-biased                                                                                                  | 0          |     | 2                | V    |  |

|                      |                                                     | SQUELCH_SENSITIVITY = 00                                                                                                 |            | 60  |                  |      |  |

| M                    | Cauciah thrashold valtaga                           | SQUELCH_SENSITIVITY = 01 (default)                                                                                       | 115<br>160 |     | mV <sub>PP</sub> |      |  |

| V <sub>SQUELCH</sub> | Squelch threshold voltage                           | SQUELCH_SENSITIVITY = 10                                                                                                 |            |     |                  |      |  |

|                      |                                                     | SQUELCH_SENSITIVITY = 11                                                                                                 |            | 200 |                  | -    |  |

## 7.7 DisplayPort Main Link Output Electrical Characteristics

over recommended operating conditions (unless otherwise noted)

|                         | PARAMETER                                      | TEST CONDITI                                                                          | ONS        | MIN | TYP  | MAX  | UNIT       |  |

|-------------------------|------------------------------------------------|---------------------------------------------------------------------------------------|------------|-----|------|------|------------|--|

| V <sub>OD(L0)</sub>     |                                                |                                                                                       |            | 238 | 340  | 442  |            |  |

| V <sub>OD(L1)</sub>     |                                                | V <sub>PRE(L0)</sub> ; 675 Mbps D10.2 Test Pattern;                                   |            | 357 | 510  | 663  |            |  |

| $V_{OD(L2)}$            | Output Differential Voltage Swing              | BOOST = 01; $100-\Omega$ R <sub>tdiff</sub> Term                                      | nination   | 484 | 690  | 897  | $mV_PP$    |  |

| V <sub>OD(L3)</sub>     |                                                |                                                                                       |            | 700 | 1000 | 1300 |            |  |

| V <sub>OD(TMDS)</sub>   |                                                | 675 Mbps D10.2 Test Pattern;                                                          | BOOST = 01 | 420 | 600  | 780  |            |  |

| $\Delta V_{OD(L0L1)}$   |                                                |                                                                                       | ,          | 1.7 | 3.5  | 5.3  |            |  |

| $\Delta V_{OD(L1L2)}$   | Output Peak-to-Peak Differential Voltage Delta | $\Delta V_{ODn} = 20 \times \log(V_{ODL(n+1)} / V_0)$<br>Per PHY_CTS section 3.2 at T | DDL(n))    | 1.6 | 2.5  | 3.5  | dB         |  |

| $\Delta V_{OD(L2L3)}$   | Voltage Delta                                  | T el l'III_CTO section 5.2 at 1                                                       | 1 2        | 0.8 | 3.5  | 6.0  |            |  |

| V <sub>PRE(L0)</sub>    |                                                | All V <sub>OD</sub> options; Any BOOST setting                                        |            |     | 0    | 0.25 |            |  |

| V <sub>PRE(L1)</sub>    | Driver and and area and area                   | $V_{OD} = V_{OD(L0)}$ , $V_{OD(L1)}$ , or $V_{OD(L2)}$ ; BOOST = 01                   |            |     | 3.5  |      | dB         |  |

| V <sub>PRE(L2)</sub>    | Driver output pre-emphasis                     | $V_{OD} = V_{OD(L0)}$ or $V_{OD(L1)}$ ; BOOST = 01                                    |            |     | 6.0  |      |            |  |

| V <sub>PRE(L3)</sub>    |                                                | $V_{OD} = V_{OD(L0)}$ ; BOOST = 01                                                    |            |     | 9.5  |      |            |  |

|                         | Outrat V Brazil                                | BOOST = 10                                                                            |            |     | +15  |      | 0/ -ID     |  |

| V <sub>PRE(BOOST)</sub> | Output V <sub>PRE</sub> Boost                  | BOOST = 00                                                                            |            | -15 |      | %dB  |            |  |

| $\Delta V_{PRE(L1L0)}$  |                                                |                                                                                       |            | 2.0 |      |      |            |  |

| $\Delta V_{PRE(L2L1)}$  | Pre-emphasis Delta                             | Per PHY_CTS section 3.3 at TP2                                                        |            | 1.6 |      |      | dB         |  |

| $\Delta V_{PRE(L3L2)}$  |                                                |                                                                                       |            | 1.6 |      |      | 1          |  |

| $\Delta V_{ConsBit}$    | Non-transition bit voltage variation           | Per PHY_CTS section 3.3.5                                                             |            |     |      | 30   | %V         |  |

| R <sub>OUT</sub>        | Driver output impedance                        |                                                                                       |            | 40  | 50   | 60   | Ω          |  |

| V <sub>OCM(SS)</sub>    | Steady state output common mode voltage        |                                                                                       |            | 0   |      | 2    | V          |  |

|                         | Out-of-control of the control                  | Per PHY_CTS section 3.10                                                              | RBR, HBR   |     | 20   |      |            |  |

| $V_{OCM(PP)}$           | Output common mode noise                       |                                                                                       | HBR2       |     | 30   |      | $mV_{RMS}$ |  |

| I <sub>os</sub>         | Short circuit current limit                    | Main Link outputs shorted to G                                                        | ND         |     |      | 50   | mA         |  |

Product Folder Links: SN75DP126

## 7.8 HDMI/DVI Main Link Output Electrical Characteristics

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                                                | TEST CONDITIONS                               | MIN                  | TYP  | MAX                     | UNIT    |

|----------------------|--------------------------------------------------------------------------|-----------------------------------------------|----------------------|------|-------------------------|---------|

| V <sub>OH</sub>      | Single-end high level output voltage                                     | VSadj = 4.7 kΩ                                | V <sub>CC</sub> -10  |      | V <sub>CC</sub> +10     | mV      |

| V <sub>OL</sub>      | Single-end low level output voltage                                      | VSadj = 4.7 kΩ                                | V <sub>CC</sub> -600 |      | V <sub>CC</sub><br>-400 | mV      |

| V <sub>SWING</sub>   | Single-end output voltage swing                                          | VSadj = 4.7 kΩ; SDA_CTL/PRE ≤ V <sub>IL</sub> | 400                  |      | 600                     | mV      |

| $\Delta V_{SWING}$   | Change in single-end output voltage swing per $100\Omega$ $\Delta VSadj$ |                                               |                      | 20   |                         | mV      |

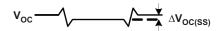

| V <sub>OCM(SS)</sub> | Steady state output common mode voltage                                  |                                               | V <sub>CC</sub> -300 |      | V <sub>CC</sub> -200    | mV      |

| $\Delta V_{OCM(SS)}$ | Change in steady state output common mode voltage between logic levels   |                                               | -5                   |      | 5                       | mV      |

| M                    | Deals to a selection of differential college                             | VSadj = 4.7 kΩ; SDA_CTL/PRE ≤ V <sub>IL</sub> | 800                  |      | 1200                    | \/      |

| $V_{OD(PP)}$         | Peak-to-peak output differential voltage                                 | VSadj = 4.7 kΩ; SDA_CTL/PRE ≥ V <sub>IH</sub> |                      | 640  |                         | $mV_PP$ |

| V                    | C4                                                                       | VSadj = 4.7 kΩ; SDA_CTL/PRE ≤ V <sub>IL</sub> |                      | 1000 |                         | \/      |

| $V_{OD(SS)}$         | Steady state output differential voltage                                 | VSadj = 4.7 kΩ; SDA_CTL/PRE ≥ V <sub>IH</sub> |                      | 630  |                         | $mV_PP$ |

| los                  | Short circuit current limit                                              | V <sub>ID</sub> = 500 mV                      |                      |      | 15                      | mA      |

### 7.9 HPD/CAD/EN Electrical Characteristics

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                                 | TEST CONDITIONS                                                 | MIN | TYP | MAX   | UNIT |

|---------------------|-----------------------------------------------------------|-----------------------------------------------------------------|-----|-----|-------|------|

| \/                  | High lovel input veltage                                  | HPD_SNK, CAD_SNK                                                | 2.1 |     |       | V    |

| $V_{IH}$            | High-level input voltage                                  | EN                                                              | 0.8 |     |       | V    |

| \/                  | Low level input veltage                                   | HPD_SNK, CAD_SNK                                                |     |     | 1.08  | V    |

| $V_{IL}$            | Low-level input voltage                                   | EN                                                              |     |     | 0.285 | V    |

| V <sub>OH</sub>     | High-level output voltage                                 | I <sub>OH</sub> = 500 μA; HPD_SRC, CAD_SRC                      | 2.7 |     | 3.6   | V    |

| $V_{OL}$            | Low-level output voltage                                  | I <sub>OH</sub> = 500 μA; HPD_SRC, CAD_SRC                      | 0   |     | 0.1   | V    |

| $R_{outCAD}$        | CAD series output resistance (1)                          | DP_HPD_SNK = CAD_SNK = V <sub>CC</sub>                          |     | 150 |       | Ω    |

| R <sub>outHPD</sub> | HPD series output resistance                              | DP_HPD_SNK = TMDS_HPD_SNK = V <sub>CC</sub>                     |     | 150 |       | Ω    |

|                     |                                                           | V <sub>CC</sub> = 0 V; V(pin) = 1.2 V; EN                       |     |     | 20    |      |

| I <sub>LEAK</sub>   | Failsafe condition leakage current                        | $V_{CC}$ = 0 V; V(pin) = 3.3 V; DP_HPD_SNK,<br>TMDS_HPD_SNK     |     |     | 40    | μA   |

| I <sub>H_HPD</sub>  | High level input current                                  | Device powered; V <sub>IH</sub> = 1.9 V;                        |     |     | 30    |      |

| $I_{H\_CAD}$        | High level input current                                  | I <sub>H_HPD</sub> includes R <sub>pdHPD</sub> resistor current |     |     | 1     | μA   |

| I <sub>L_HPD</sub>  | Low level input ourrent                                   | Device powered; V <sub>IL</sub> = 0.8 V;                        |     |     | 30    |      |

| $I_{L\_CAD}$        | Low level input current                                   | IL_HPD includes RpdHPD resistor current                         |     |     | 1     | μA   |

| R <sub>pdHPD</sub>  | HPD input termination to GND; DP_HPD_SNK and TMDS_HPD_SNK | V <sub>CC</sub> = 0 V                                           | 100 | 130 | 160   | kΩ   |

| R <sub>EN</sub>     | EN terminal pull-up resistor                              |                                                                 | 120 | 150 | 180   | kΩ   |

### 7.10 AUX/DDC/I<sup>2</sup>C Electrical Characteristics

over recommended operating conditions (unless otherwise noted)

|                            | PARAMETER                                                           | TEST CONDITIONS                                                                                                                                                                  | MIN | TYP | MAX | UNIT |

|----------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| C <sub>IO</sub>            | I/O capacitance                                                     | V <sub>IO</sub> = 0 V; f(test) = 1 MHz                                                                                                                                           |     | 10  |     | pF   |

|                            | On resistance AUX_SRCn to AUX_SNKn in DP mode                       | $V_{CC} = 3.0 \text{ V w/ } V_{I} = 2.6 \text{ V or } V_{CC} = 3.6 \text{ V}$<br>w/ $V_{I} = 3.4 \text{ V}; I_{O} = 5 \text{ mA}$                                                |     |     | 10  | Ω    |

| r <sub>ON</sub>            | On resistance AUX_SRCp to AUX_SNKp in DP mode                       | $V_{CC} = 3.0 \text{ V w/ } V_{I} = 0.3 \text{ V or } V_{CC} = 3.6 \text{ V}$ w/ $V_{I} = 0.4 \text{ V}; I_{O} = 500 \text{ mA}$                                                 |     |     | 10  | Ω    |

|                            | On resistance SCL/SDA_SRC to AUX_SNK in TMDS mode                   | $V_1 = 0.4 \text{ V}; I_0 = 3 \text{ mA}$                                                                                                                                        |     |     | 30  | Ω    |

| Δr <sub>ON</sub>           | On resistance variation with input signal voltage change in DP mode | $V_{CC} = 3.6 \text{ V}, I_{O} = 5 \text{ mA}, V_{I} = 2.6 \text{ V to } 3.4 \text{ V}$<br>$V_{CC} = 3.0 \text{ V}, I_{O} = 5 \text{ mA}, V_{I} = 0 \text{ V to } 0.4 \text{ V}$ |     |     | 5   | Ω    |

| V <sub>ID(HYS)</sub>       | Differential input hysteresis                                       | By design (simulation only)                                                                                                                                                      |     | 50  |     | mV   |

|                            |                                                                     | V <sub>CC</sub> = 0 V; V(pin) = 3.3 V; SCL/SDA_SNK                                                                                                                               |     |     | 40  |      |

|                            |                                                                     | V <sub>CC</sub> = 0 V; V(pin) = 3.3 V; AUX_SNK p/n                                                                                                                               |     |     | 20  |      |

| I <sub>LEAK</sub>          | Failsafe condition leakage current                                  | V <sub>CC</sub> = 0 V; V(pin) = 3.3 V; SCL_CTL/EQ,<br>SDA_CTL/PRE, AUX_SRCp                                                                                                      |     |     | 5   | μΑ   |

|                            |                                                                     | V <sub>CC</sub> = 0 V; V(pin) = 3.3 V; AUX_SRCn,<br>SCL/SDA_SRC                                                                                                                  |     |     | 60  |      |

| I <sub>H_AUX_DD</sub><br>C | AUX/DDC High level input current                                    | Device powered; V <sub>I</sub> = V <sub>CC</sub>                                                                                                                                 |     |     | 5   | μA   |

| I <sub>H_I2C</sub>         | I <sup>2</sup> C High level input current                           |                                                                                                                                                                                  |     |     | 20  | •    |

| I <sub>L_AUX</sub>         | AUX Low level input current                                         |                                                                                                                                                                                  |     |     | 5   |      |

| I <sub>L_I2C</sub>         | I <sup>2</sup> C Low level input current                            | Device powered; V <sub>I</sub> = GND ;                                                                                                                                           |     |     | 40  | μA   |

| I <sub>L_DDCSR</sub><br>C  | DDC Low level input current                                         | I <sub>L_DDCSRC</sub> includes R <sub>DDC</sub> resistor current                                                                                                                 |     |     | 80  | μ    |

| V <sub>AUX+</sub>          | AUX_SNKp voltage                                                    | Per PHY_CTS section 3.19                                                                                                                                                         | 0   |     | 0.4 | V    |

| V <sub>AUX</sub>           | AUX_SNKn voltage                                                    | Per PHY_CTS section 3.18                                                                                                                                                         | 2.4 |     | 3.6 | V    |

| S <sub>1122</sub>          | AC coupled AUX line insertion loss                                  | V <sub>ID</sub> = 400 mV, 360 MHz sine wave                                                                                                                                      |     |     | 3   | dB   |

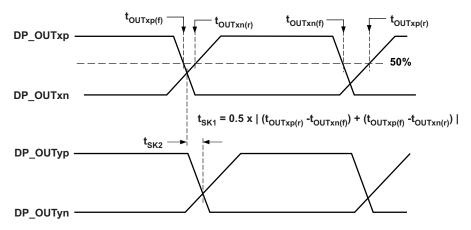

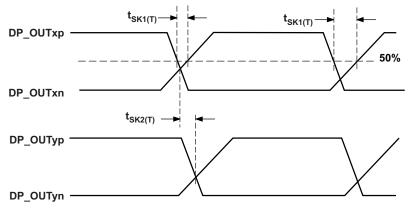

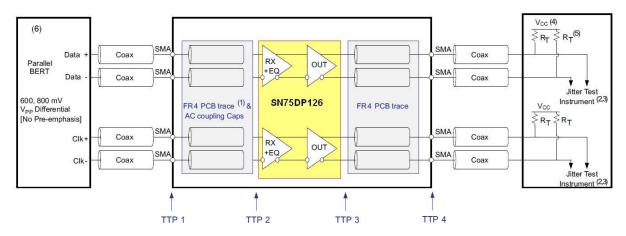

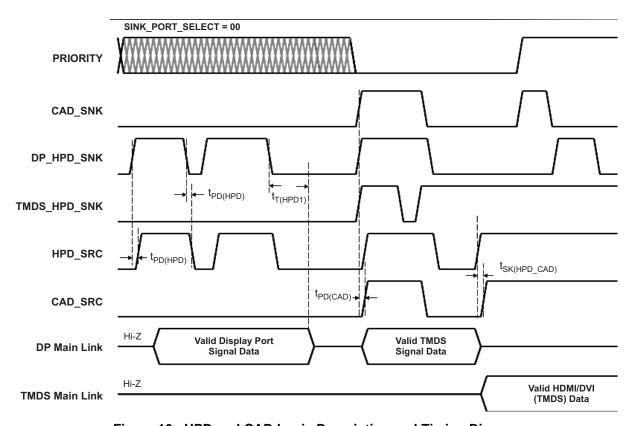

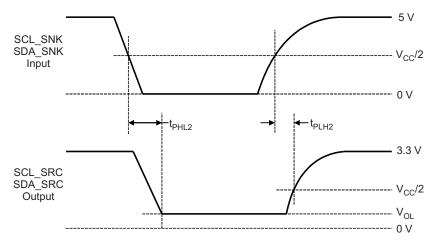

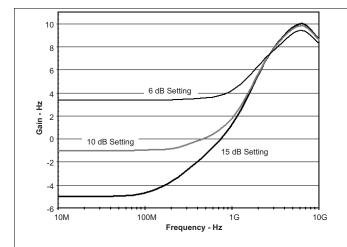

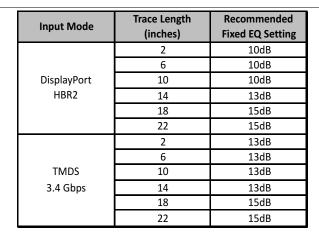

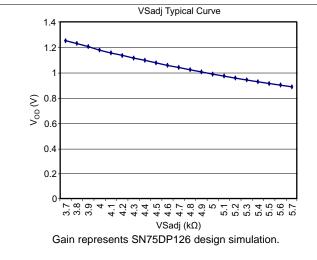

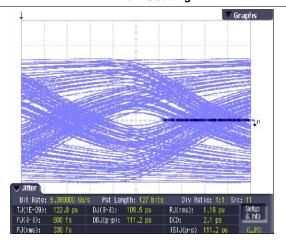

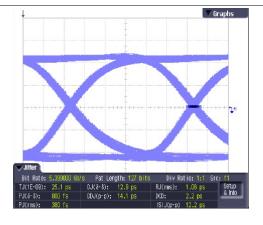

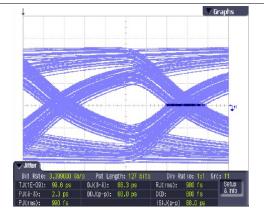

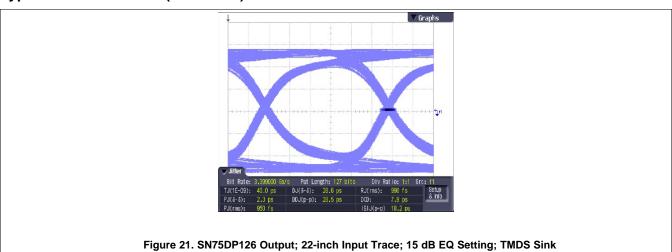

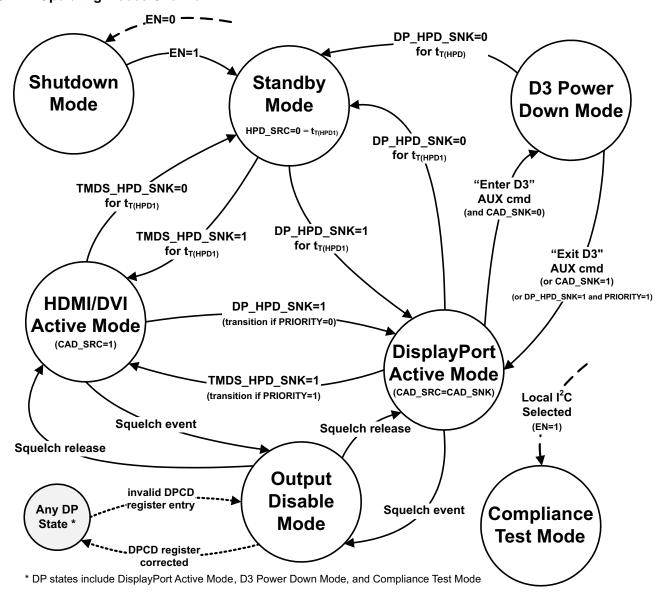

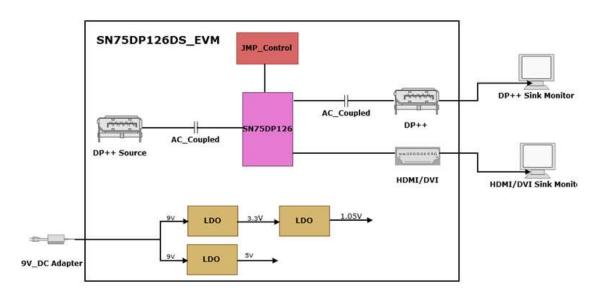

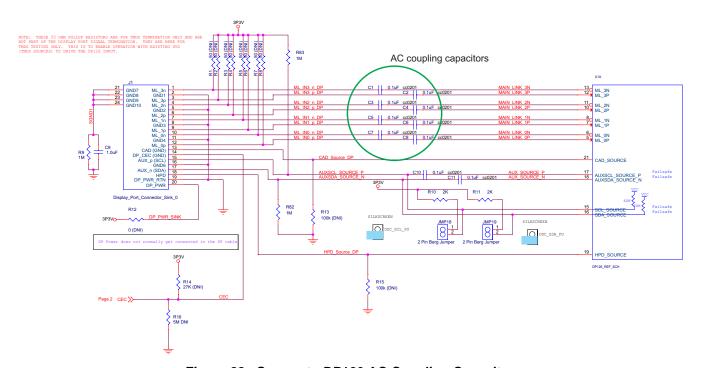

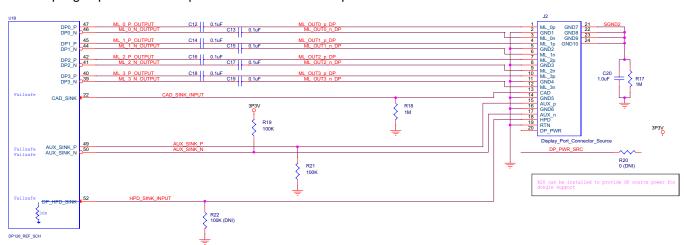

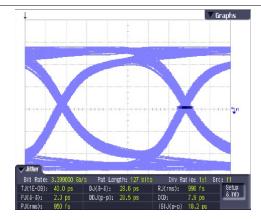

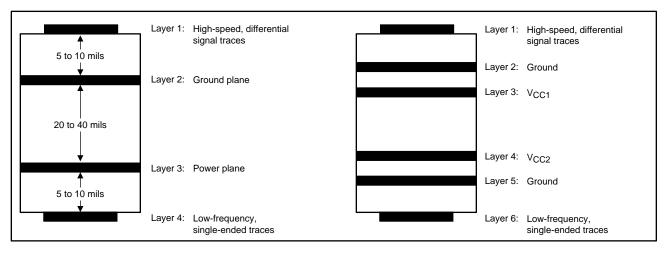

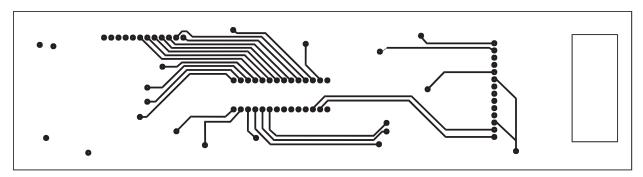

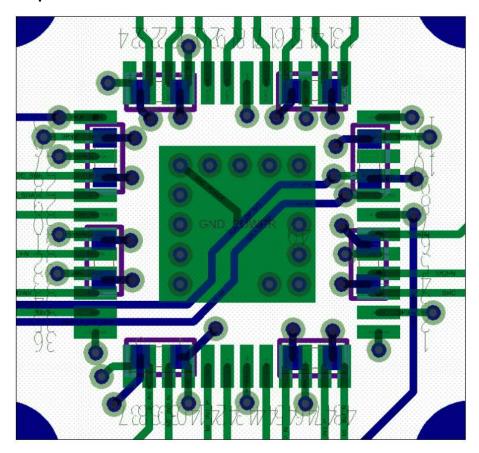

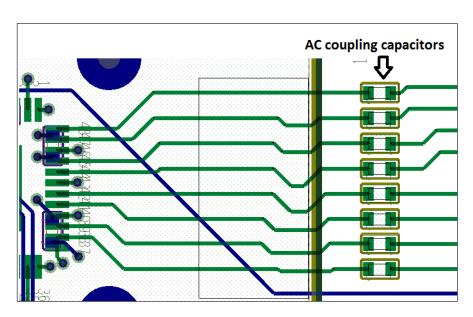

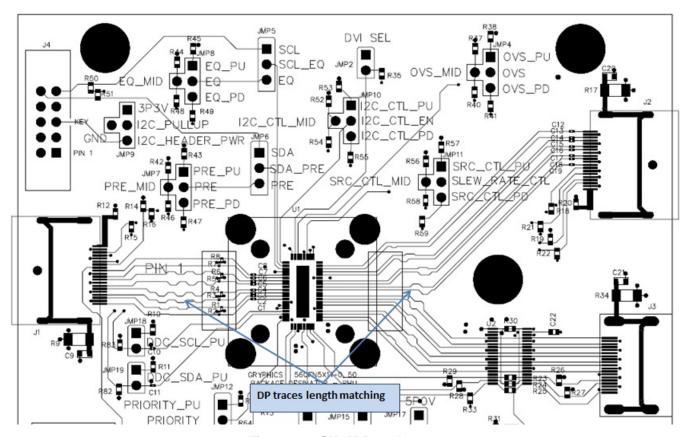

| $R_{DDC}$                  | Switchable pullup resistor on DDC at source side (SCL_DDC, SDA_DDC) | CAD_SNK = V <sub>IH</sub>                                                                                                                                                        | 48  | 60  | 72  | kΩ   |