Sample &

Buy

## TPS65132

SLVSBM1H - JUNE 2013-REVISED NOVEMBER 2016

# **TPS65132 Single Inductor - Dual Output Power Supply**

## 1 Features

Texas

- Input Voltage Range: 2.5 V to 5.5 V

- V<sub>POS</sub> Boost Converter: 4 V to 6 V (0.1-V step)

INSTRUMENTS

- V<sub>NEG</sub> Inverting Buck-Boost Converter: -6 V to -4 V (0.1-V step)

- Maximum Output Current: 80 mA or 150 mA

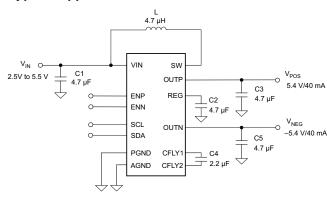

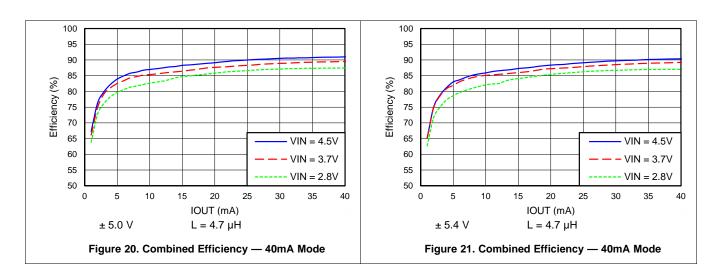

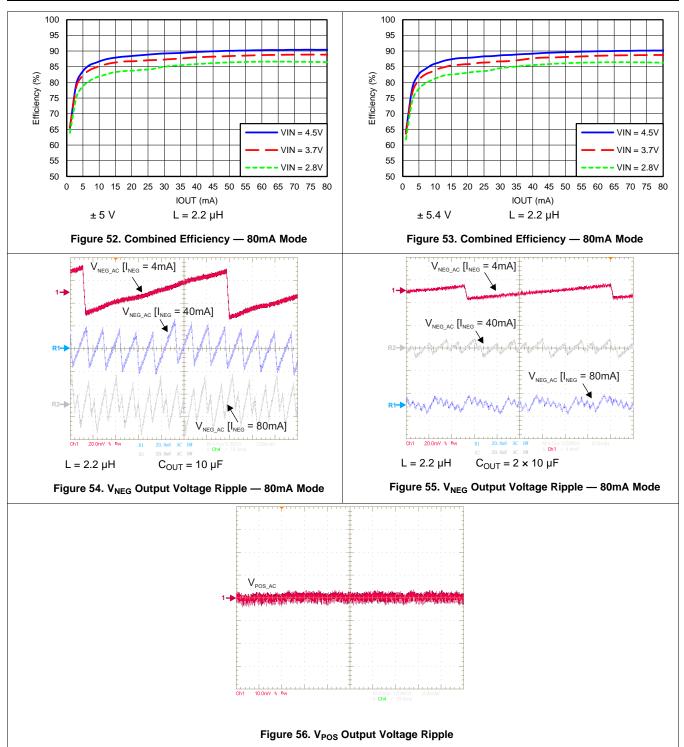

- Outstanding Combined Efficiency

- > 85% at I<sub>OUT</sub> > 10 mA

- > 90% at I<sub>OUT</sub> > 40 mA

- Excellent Performance

- Outstanding Transient Response

- 1% Output Voltage Accuracy over Full Temperature Range

- I<sup>2</sup>C Interface

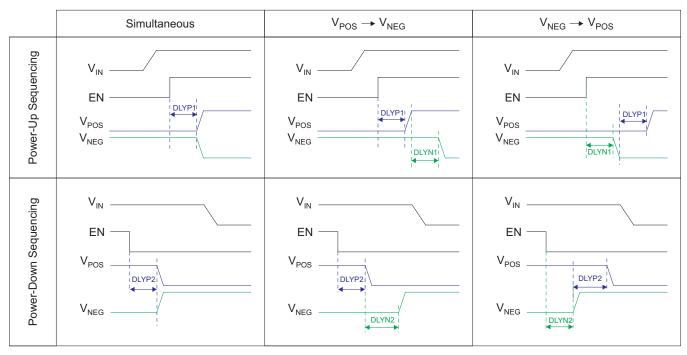

- Programmable Power-Up / -Down Sequencing Options

- Flexible Output Voltage Programming

- Programmable Active Output Discharge

- > 1000x Programmable Non-Volatile Memory

- Under-Voltage Lock-Out and Thermal Protection

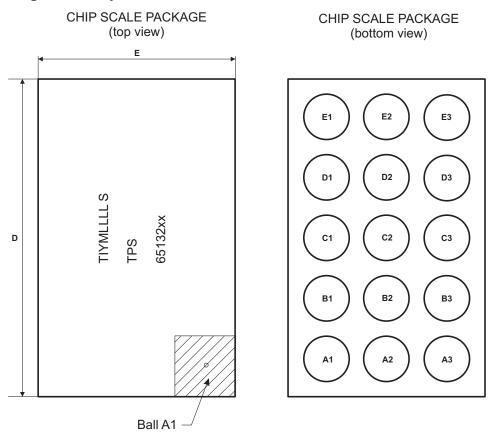

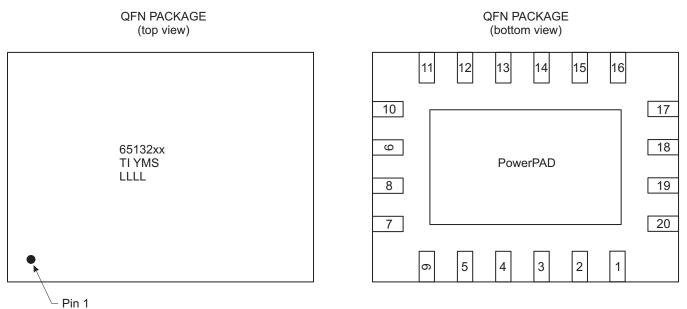

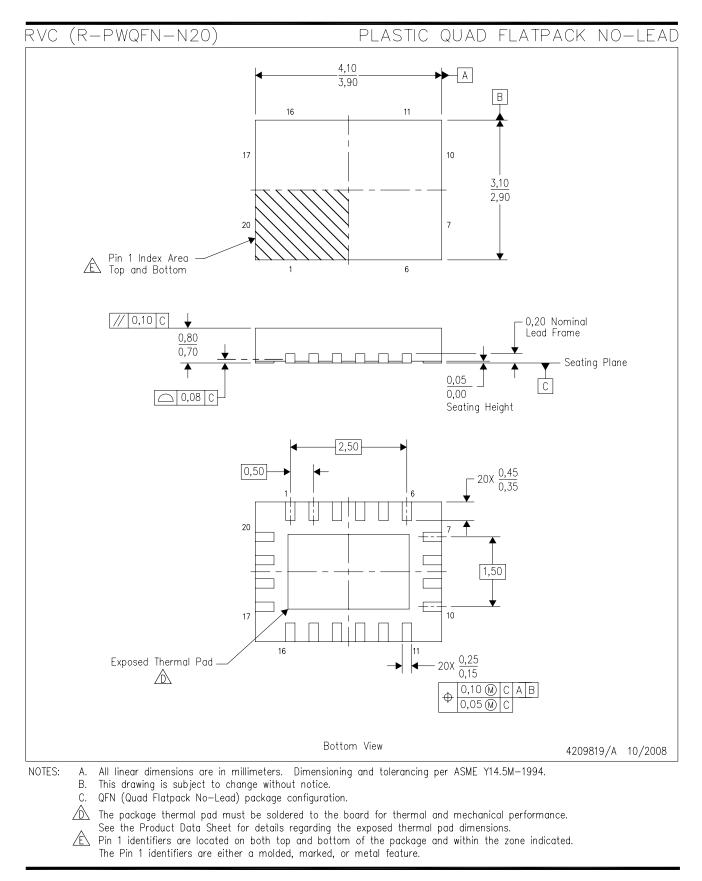

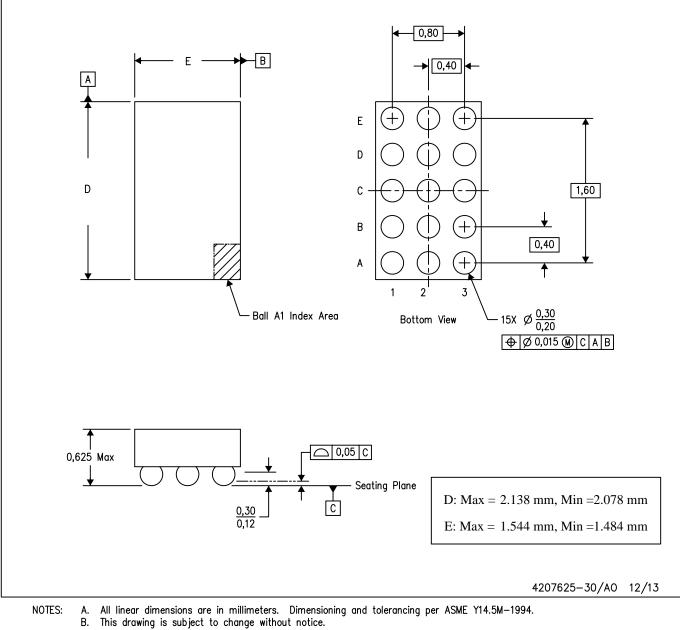

- Two Package Options

- 15-Ball CSP Package

- 20-Pins QFN Package

## 2 Applications

- Small-, Medium-Size Bipolar LCD Displays

- Smartphone, Tablet

- Camera, GPS

- Home Automation, Point-of-Sales

- Wearables (Smart Watch, Activity Tracker)

- General Split-Rail Power Supply

- Differential Audio, Headphone Amplifier

- Instrumentation, Operational Amplifier, Comparator

- DAC / ADC

## **3 Description**

The TPS65132 family is designed to supply positive/negative driven applications. The device uses a single inductor scheme for both outputs to provide the user smallest solution size, a small bill-of-material as well as high efficiency. The devices offer best line and load regulation at low noise. With its input voltage range of 2.5 V to 5.5 V, it is optimized for products powered by single-cell batteries (Li-Ion, Ni-Li, Li-Polymer) and fixed 3.3-V and 5-V rails. The TPS656132 family provides 80 mA and 150 mA output current options with programmability to 40 mA. There are both CSP and QFN package options available.

#### Device Information (1)

| PART NUMBER                | PACKAGE    | BODY SIZE (NOM.)  |

|----------------------------|------------|-------------------|

| TPS65132<br>-B, -L, -T, -S | DSBGA (15) | 2.11 mm × 1.51 mm |

| TPS65132W                  | WQFN (20)  | 4.00 mm × 3.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

## **Efficiency vs Output Current**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. UNLESS OTHERWISE NOTED, this document contains PRODUCTION DATA.

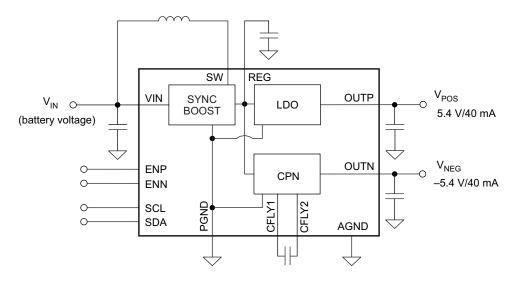

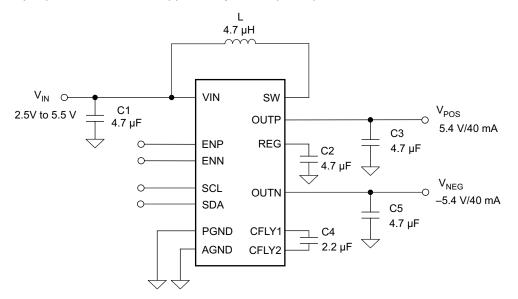

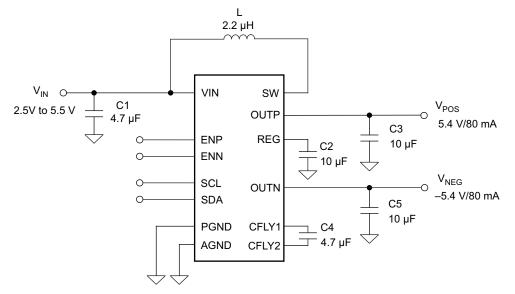

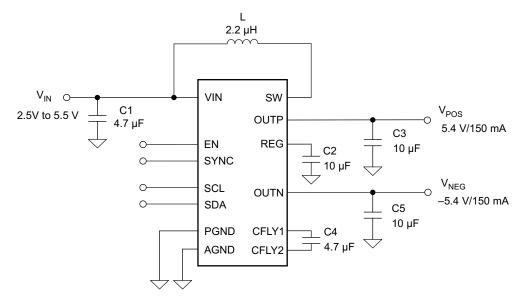

## Typical Application

Page

## **Table of Contents**

| 1 | Features 1     |                                                                  |  |  |  |  |  |  |

|---|----------------|------------------------------------------------------------------|--|--|--|--|--|--|

| 2 | Applications 1 |                                                                  |  |  |  |  |  |  |

| 3 | Des            | Description 1                                                    |  |  |  |  |  |  |

| 4 | Rev            | ision History 2                                                  |  |  |  |  |  |  |

| 5 | Dev            | ice Comparison Table 4                                           |  |  |  |  |  |  |

| 6 | Pin            | Configuration and Functions5                                     |  |  |  |  |  |  |

| 7 | Spe            | cifications8                                                     |  |  |  |  |  |  |

|   | 7.1            | Absolute Maximum Ratings 8                                       |  |  |  |  |  |  |

|   | 7.2            | ESD Ratings8                                                     |  |  |  |  |  |  |

|   | 7.3            | Recommended Operating Conditions 8                               |  |  |  |  |  |  |

|   | 7.4            | Thermal Information 8                                            |  |  |  |  |  |  |

|   | 7.5            | Electrical Characteristics9                                      |  |  |  |  |  |  |

|   | 7.6            | I <sup>2</sup> C Interface Timing Requirements / Characteristics |  |  |  |  |  |  |

|   |                |                                                                  |  |  |  |  |  |  |

|   | 7.7            | Typical Characteristics 11                                       |  |  |  |  |  |  |

| 8 | Deta           | ailed Description 12                                             |  |  |  |  |  |  |

|   | 8.1            | Overview 12                                                      |  |  |  |  |  |  |

|   | 8.2            | Functional Block Diagram 12                                      |  |  |  |  |  |  |

|   | 8.3            | Feature Description 12                                           |  |  |  |  |  |  |

|   | 8.4            | Device Functional Modes                                          |  |  |  |  |  |  |

|    | 8.5  | Programming 17                                     |

|----|------|----------------------------------------------------|

|    | 8.6  | Register Maps 19                                   |

| 9  | App  | lication and Implementation 26                     |

|    | 9.1  | Application Information                            |

|    | 9.2  | Typical Applications                               |

| 10 | Pow  | ver Supply Recommendations                         |

| 11 |      | out                                                |

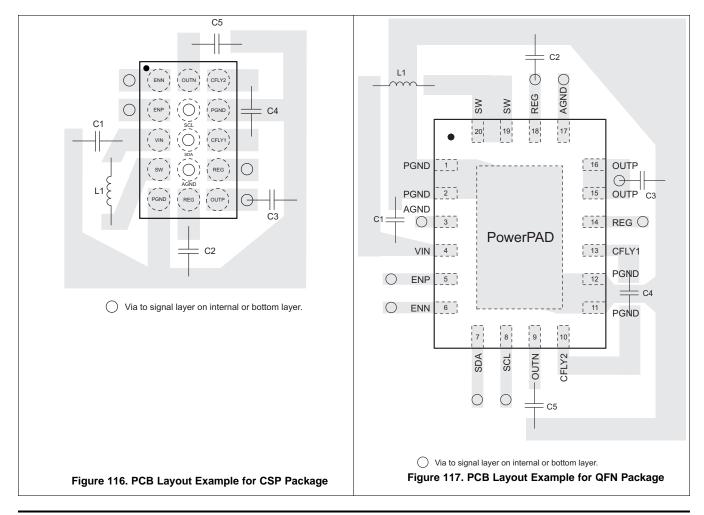

|    | -    | Layout Guidelines54                                |

|    | 11.2 | Layout Example 54                                  |

| 12 | Dev  | ice and Documentation Support                      |

|    | 12.1 | Device Support                                     |

|    | 12.2 | Receiving Notification of Documentation Updates 55 |

|    | 12.3 | Community Resources 55                             |

|    | 12.4 | Trademarks 55                                      |

|    | 12.5 | Electrostatic Discharge Caution 55                 |

|    | 12.6 | Glossary 55                                        |

| 13 | Mec  | hanical, Packaging, and Orderable                  |

|    |      | mation 55                                          |

|    | 13.1 | CSP Package Summary 56                             |

|    |      |                                                    |

## **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | nanges from Revision G (August 2015) to Revision H                  | Page |

|----|---------------------------------------------------------------------|------|

| •  | Removed Product Preview from TPS65132S.                             | 1    |

| •  | Changed Device Comparison Table                                     | 4    |

| •  | Added description of clock stretching                               | 17   |

|    | Deleted detailed I <sup>2</sup> C interface description             |      |

| •  | Added that the DLYx Register is only valid for TPS65132Sx versions. | 22   |

| •  | Changed Table 6                                                     | 23   |

| Cł | nanges from Revision F (June 2015) to Revision G     | Page |

|----|------------------------------------------------------|------|

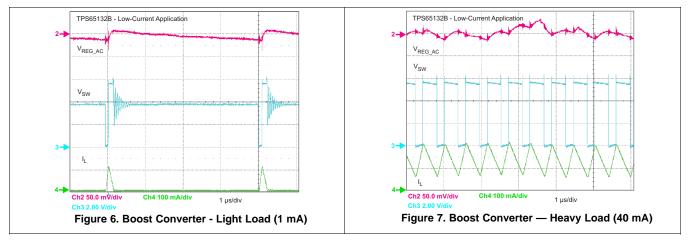

| •  | Changed scope figures for Boost Converter switching. | 13   |

#### Changes from Revision E (November 2014) to Revision F

| • | Added TPS65132L1 device to Device Comparison table                               | 4  |

|---|----------------------------------------------------------------------------------|----|

| • | Added TPS65132T6 device to the Device Comparison Table.                          | 4  |

| • | Separated LOGIC SCL, SDA spec MIN/MAX from LOGIC EN, ENN, ENP, SYNC spec MIN/MAX | 9  |

| • | Changed DAC Registers section for clarity                                        | 19 |

| • | Added High-current Applications (≤ 150 mA) section                               | 44 |

| Changes from Revision D (October 2014) to Revision E |                                                    |   |  |

|------------------------------------------------------|----------------------------------------------------|---|--|

| •                                                    | Added TPS65132L0 device to Device Comparison table | 4 |  |

Product Folder Links: TPS65132

## XAS STRUMENTS

www.ti.com

Page

Page

# Changes from Revision C (July 2014) to Revision D Page

## Changes from Revision B (May 2014) to Revision C

| • | Added note to Device Comparison Table                                                                       | . 4 |

|---|-------------------------------------------------------------------------------------------------------------|-----|

| • |                                                                                                             |     |

| • | Added Table 1 and various references to it                                                                  | 14  |

| ٠ | Added "Power-Down And Discharge (CPN) shows the V <sub>NEG</sub> discharge behavior of each device variant" | 16  |

| ٠ | Added Table 2 and various references to it                                                                  | 16  |

| • | Added note to Figure 18                                                                                     | 23  |

#### Changes from Revision A (August 2013) to Revision B

| • | Formatted to the new data sheet standard                     | 1 |

|---|--------------------------------------------------------------|---|

| • | Added new package option (QFN) to Device Information table   | 1 |

| • | Added new package option (QFN) to Pin Configurations section | 7 |

| • | Added the ESD Ratings table                                  | 8 |

| Changes from Original (June 2013) to Revision A Pa |                                                         |   |  |

|----------------------------------------------------|---------------------------------------------------------|---|--|

| •                                                  | Added TPS65132Bx devices to the Device Comparison table | 4 |  |

## 5 Device Comparison Table

| PART NUMBER <sup>(1)</sup> | PRE-<br>PROGRAMMED<br>OUTPUT<br>VOLTAGES              | I <sub>OUT_MAX</sub> | PRE-<br>PROGRAMMED<br>I <sub>OUT</sub> | PRE-<br>PROGRAMMED<br>ACTIVE<br>DISCHARGE <sup>(2)</sup> | STARTUP<br>TIME<br>VPOS / VNEG<br>(3) | I <sub>SD</sub> | PACKAGE |       |       |       |       |       |                                     |      |        |     |

|----------------------------|-------------------------------------------------------|----------------------|----------------------------------------|----------------------------------------------------------|---------------------------------------|-----------------|---------|-------|-------|-------|-------|-------|-------------------------------------|------|--------|-----|

| TPS65132A                  | V <sub>POS</sub> = 5.4 V<br>V <sub>NEG</sub> = -5.4 V | 80 mA                | 40 mA                                  | V <sub>POS</sub> / V <sub>NEG</sub>                      | FAST                                  | 30 µA           | CSP     |       |       |       |       |       |                                     |      |        |     |

| TPS65132A0                 | V <sub>POS</sub> = 5.0 V<br>V <sub>NEG</sub> = -5.0 V | 00 1114              | 40 11/4                                | VPOS / VNEG                                              | TAST                                  | 30 µA           | CSF     |       |       |       |       |       |                                     |      |        |     |

| TPS65132B                  | V <sub>POS</sub> = 5.4 V<br>V <sub>NEG</sub> = -5.4V  |                      |                                        |                                                          |                                       |                 |         |       |       |       |       |       |                                     |      |        |     |

| TPS65132B0                 | V <sub>POS</sub> = 5.0 V<br>V <sub>NEG</sub> = -5.0 V | 80 mA                | mA 40 mA                               | V <sub>POS</sub> / V <sub>NEG</sub>                      | FAST                                  | 130 nA          | CSP     |       |       |       |       |       |                                     |      |        |     |

| TPS65132B5                 | V <sub>POS</sub> = 5.5 V<br>V <sub>NEG</sub> = -5.5 V |                      |                                        |                                                          |                                       |                 |         |       |       |       |       |       |                                     |      |        |     |

| TPS65132B2                 | V <sub>POS</sub> = 5.2 V<br>V <sub>NEG</sub> = -5.2 V |                      |                                        |                                                          |                                       |                 |         |       |       |       |       |       |                                     |      |        |     |

| TPS65132L                  | V <sub>POS</sub> = 5.4 V<br>V <sub>NEG</sub> = -5.4 V | 80 mA                | 80 mA                                  | 80 mA                                                    | 80 mA                                 | 80 mA           | 80 mA   | 80 mA | 80 mA | 80 mA | 80 mA | 40 mA | V <sub>POS</sub> / V <sub>NEG</sub> | SLOW | 130 nA | CSP |

| TPS65132L0                 | V <sub>POS</sub> = 5.0 V<br>V <sub>NEG</sub> = -5.0 V |                      |                                        |                                                          |                                       |                 |         |       |       |       |       |       |                                     |      |        |     |

| TPS65132L1 <sup>(4)</sup>  | V <sub>POS</sub> = 5.1 V<br>V <sub>NEG</sub> = -5.1 V | 80 mA                | 40 mA                                  | V <sub>POS</sub> / V <sub>NEG</sub>                      | SLOW                                  | 130 nA          | CSP     |       |       |       |       |       |                                     |      |        |     |

| TPS65132T6                 | V <sub>POS</sub> = 5.6 V<br>V <sub>NEG</sub> = -5.6 V | 80 mA                | 80 mA                                  | V <sub>POS</sub> / V <sub>NEG</sub>                      | SLOW                                  | 130 nA          | CSP     |       |       |       |       |       |                                     |      |        |     |

| TPS65132S                  | V <sub>POS</sub> = 5.4 V<br>V <sub>NEG</sub> = -5.4 V | 150 mA               | 80 mA                                  | V <sub>POS</sub> / V <sub>NEG</sub>                      | SLOW                                  | 130 nA          | CSP     |       |       |       |       |       |                                     |      |        |     |

| TPS65132W                  | V <sub>POS</sub> = 5.4 V<br>V <sub>NEG</sub> = -5.4 V | 80 mA                | 80 mA                                  | V <sub>POS</sub> / V <sub>NEG</sub>                      | SLOW                                  | 130 nA          | QFN     |       |       |       |       |       |                                     |      |        |     |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com

(2) See *Power-Down And Discharge (LDO)* and *Power-Down And Discharge (CPN)* for a detailed description of how each device variant implements the active discharge function.

(3) Please refer to Power-Up And Soft-Start (LDO) and Power-Up And Soft-Start (CPN) for more details.

(4) Product preview.

4

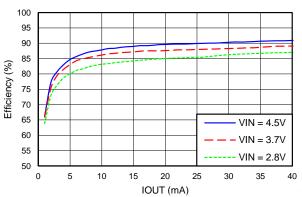

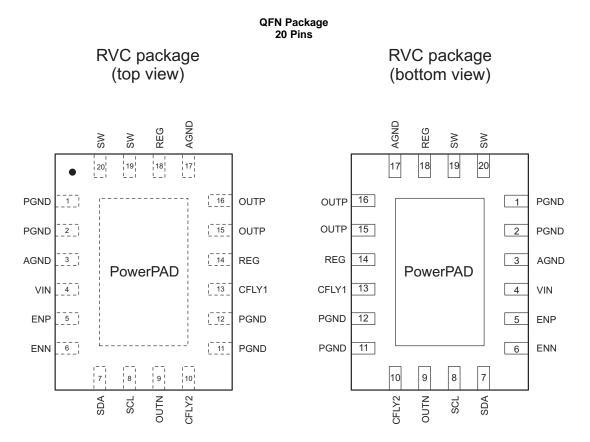

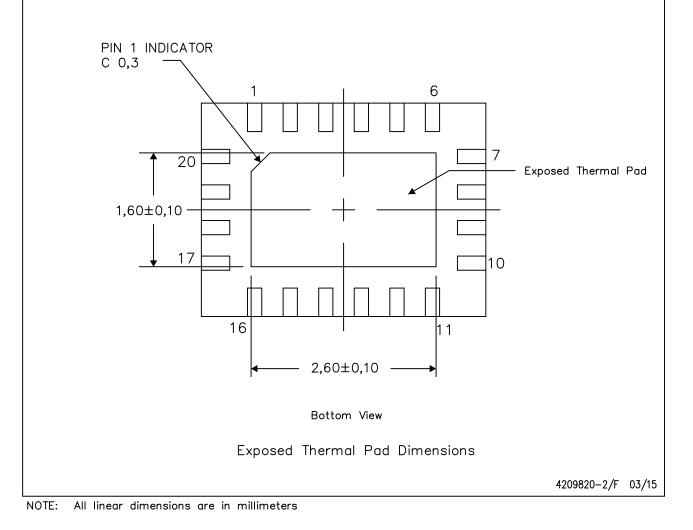

## 6 Pin Configuration and Functions

TPS65132 SLVSBM1H-JUNE 2013-REVISED NOVEMBER 2016

www.ti.com

Texas Instruments

|       |                |    |     | Pin Functions                                                           |  |  |

|-------|----------------|----|-----|-------------------------------------------------------------------------|--|--|

| PIN   |                |    | 1/0 | DESCRIPTION                                                             |  |  |

| NAME  | Ax, Bx, Lx, Tx | Sx | I/O | DESCRIPTION                                                             |  |  |

| AGND  | D2             | D2 | —   | Analog ground                                                           |  |  |

| CFLY1 | C3             | C3 | I/O | Negative charge pump flying capacitor pin                               |  |  |

| CFLY2 | A3             | A3 | I/O | Negative charge pump flying capacitor pin                               |  |  |

| EN    | —              | B1 |     | Enable pin (sequence programmed)                                        |  |  |

| ENN   | A1             | —  | Ι   | Enable pin for V <sub>NEG</sub> rail                                    |  |  |

| ENP   | B1             | B1 | I   | Enable pin for V <sub>POS</sub> rail                                    |  |  |

| OUTP  | E3             | E3 | 0   | Output pin of the LDO (V <sub>POS</sub> )                               |  |  |

| OUTN  | A2             | A2 | 0   | Output pin of the negative charge pump (V <sub>NEG</sub> )              |  |  |

| PGND  | B3             | B3 |     | Power ground                                                            |  |  |

| FGIND | E1             | E1 | _   |                                                                         |  |  |

| REG   | D3             | D3 | I/O | Boost converter output pin                                              |  |  |

| REG   | E2             | E2 | 1/0 |                                                                         |  |  |

| SCL   | B2             | B2 | I/O | I <sup>2</sup> C interface clock signal pin                             |  |  |

| SDA   | C2             | C2 | I/O | I <sup>2</sup> C interface data signal pin                              |  |  |

| SW    | D1             | D1 | I/O | Switch pin of the boost converter                                       |  |  |

| SYNC  | —              | A1 | Ι   | Synchronization pin. 150 mA current enabled if this pin is pulled HIGH. |  |  |

| VIN   | C1             | C1 | I   | Input voltage supply pin                                                |  |  |

#### **Pin Functions**

| PIN     |    | 1/0 | DECODIDITION                                               |  |  |

|---------|----|-----|------------------------------------------------------------|--|--|

| NAME    | Wx |     | DESCRIPTION                                                |  |  |

|         | 3  |     |                                                            |  |  |

| AGND    | 17 | _   | Analog ground                                              |  |  |

| CFLY1   | 13 | I/O | Negative charge pump flying capacitor pin                  |  |  |

| CFLY2   | 10 | I/O | Negative charge pump flying capacitor pin                  |  |  |

| ENN     | 6  | I   | Enable pin for V <sub>NEG</sub> rail                       |  |  |

| ENP     | 5  | I   | Enable pin for V <sub>POS</sub> rail                       |  |  |

| Ì       | 16 | 0   | $O_{1}$ that the LDO $(1/1)$                               |  |  |

| OUTP 15 |    | 0   | Output pin of the LDO (V <sub>POS</sub> )                  |  |  |

| OUTN    | 9  | 0   | Output pin of the negative charge pump (V <sub>NEG</sub> ) |  |  |

|         | 1  |     |                                                            |  |  |

| PGND    | 2  |     | Bower ground                                               |  |  |

| FGND    | 11 | _   | Power ground                                               |  |  |

|         | 12 |     |                                                            |  |  |

|         | 14 | I/O | Basst semienter sutrut nin                                 |  |  |

| REG     | 18 | 1/0 | Boost converter output pin                                 |  |  |

| SCL     | 8  | I/O | I <sup>2</sup> C interface clock signal pin                |  |  |

| SDA     | 7  | I/O | I <sup>2</sup> C interface data signal pin                 |  |  |

| CIM     | 19 | 1/0 | Switch air of the baset convertor                          |  |  |

| SW      | 20 | I/O | Switch pin of the boost converter                          |  |  |

| VIN     | 4  | I   | Input voltage supply pin                                   |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings<sup>(1)(2)</sup>

over operating free-air temperature range (unless otherwise noted)

|                         |                                                         | VAL                                                                                                                                                                    |                                                                                                                                  |    |

|-------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----|

|                         |                                                         | VALUE           MIN         MAX           -0.3         7           -7         0.3           See Thermal Information           -40         150           -40         85 | UNIT                                                                                                                             |    |

| Voltage range           | CFLY1, EN, ENN, ENP, OUTP, REG, SCL, SDA, SW, SYNC, VIN | -0.3                                                                                                                                                                   | MAX           3         7           0.3         0.3           Thermal Information           0         150           0         85 | V  |

|                         | CFLY2, OUTN                                             | -7                                                                                                                                                                     | 0.3                                                                                                                              | V  |

| Continuous total power  | dissipation                                             | See Therma                                                                                                                                                             | l Information                                                                                                                    |    |

| Operating junction temp | erature, T <sub>J</sub>                                 | -40                                                                                                                                                                    | 150                                                                                                                              | °C |

| Operating ambient temp  | perature, T <sub>A</sub>                                | -40                                                                                                                                                                    | 85                                                                                                                               | °C |

| Storage temperature, T  | stg                                                     | 65                                                                                                                                                                     | 150                                                                                                                              | °C |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to ground.

## 7.2 ESD Ratings

|                  |                                                                                         | VALUE | UNIT |

|------------------|-----------------------------------------------------------------------------------------|-------|------|

|                  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>             | ±2000 | V    |

| V <sub>ESD</sub> | Charged device model (CDM) per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

|                                                          |                                     | MIN | TYP MAX | UNIT |

|----------------------------------------------------------|-------------------------------------|-----|---------|------|

| V <sub>IN</sub>                                          | Input voltage range                 | 2.5 | 5.5     | V    |

| L                                                        | Inductor <sup>(1)</sup>             | 2.2 | 4.7     | μH   |

| C <sub>IN</sub>                                          | Input capacitor <sup>(1)(2)</sup>   | 4.7 |         | μF   |

| C <sub>FLY</sub>                                         | Flying capacitor <sup>(1)(2)</sup>  | 2.2 |         | μF   |

| C <sub>OUTP</sub> , C <sub>OUTN</sub> , C <sub>REG</sub> | Output capacitors <sup>(1)(2)</sup> | 4.7 |         | μF   |

| T <sub>A</sub>                                           | Operating ambient temperature       | -40 | 85      | °C   |

| TJ                                                       | Operating junction temperature      | -40 | 125     | °C   |

(1) Please see *Detailed Description* section for further information.

(2) X7R (or better dielectric material) is recommended.

## 7.4 Thermal Information

|                    |                                              | TPS65132   | TPS65132  |      |

|--------------------|----------------------------------------------|------------|-----------|------|

|                    | THERMAL METRIC <sup>(1)</sup>                | YFF        | RVC       | UNIT |

|                    |                                              | (15) BALLS | (20) PINS |      |

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance       | 76.5       | 39.0      | °C/W |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance    | 0.2        | 42.7      | °C/W |

| $R_{\theta JB}$    | Junction-to-board thermal resistance         | 44         | 13.6      | °C/W |

| ΨJT                | Junction-to-top characterization parameter   | 1.6        | 0.6       | °C/W |

| Ψјв                | Junction-to-board characterization parameter | 43.4       | 13.6      | °C/W |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance | N/A        | 3.8       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

TEXAS INSTRUMENTS

www.ti.com

## 7.5 Electrical Characteristics

$V_{IN}$  = 3.7 V, EN = ENN = ENP =  $V_{IN}$ ,  $V_{POS}$  = 5.4 V,  $V_{NEG}$  = -5.4 V,  $T_A$  = -40°C to 85°C; typical values are at  $T_A$  = 25°C (unless otherwise noted).

|                      | PARAMETER                                   | TEST CONDITIONS                                                                        | MIN  | TYP  | MAX  | UNIT |

|----------------------|---------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY C             | URRENT                                      |                                                                                        |      |      |      |      |

| V <sub>IN</sub>      | Input voltage range                         |                                                                                        | 2.5  |      | 5.5  | V    |

|                      |                                             | V <sub>IN</sub> rising                                                                 | 2.3  |      | 2.5  |      |

| V <sub>UVLO</sub>    | Undervoltage lockout threshold              | V <sub>IN</sub> falling                                                                | 2.1  |      | 2.3  | V    |

| l <sub>Q</sub>       | Quiescent current                           |                                                                                        |      | 0.54 |      | mA   |

|                      | Thermal shutdown                            |                                                                                        |      | 140  |      | °C   |

|                      | Thermal shutdown hysteresis                 |                                                                                        |      | 5    |      | °C   |

| LOGIC EN             | , ENN, ENP, SYNC                            |                                                                                        |      |      |      |      |

| VIH                  | High level input voltage                    |                                                                                        | 1.1  |      |      |      |

| V <sub>IL</sub>      | Low level input voltage                     | $V_{IN} = 2.5 V \text{ to } 5.5 V$                                                     |      |      | 0.4  | V    |

| R <sub>EN</sub>      | Pulldown resistors                          |                                                                                        |      | 200  |      | kΩ   |

| LOGIC SC             | L, SDA                                      | ·                                                                                      |      |      | 1    |      |

| V <sub>IH</sub>      | High level input voltage                    |                                                                                        | 1.1  |      |      |      |

| V <sub>IL</sub>      | Low level input voltage                     | $V_{IN} = 2.5 V \text{ to } 5.5 V$                                                     |      |      | 0.54 | V    |

| BOOST C              | ONVERTER                                    |                                                                                        |      |      |      |      |

| I <sub>LIM</sub>     | Boost converter valley current limit        |                                                                                        | 0.9  | 1.2  | 1.5  | А    |

| f <sub>SW</sub>      | Boost converter switching frequency         |                                                                                        | 1.35 | 1.80 | 2.25 | MHz  |

| LDO OUT              | PUT V <sub>POS</sub>                        |                                                                                        |      |      |      |      |

| V <sub>POS</sub>     | Positive output voltage range               |                                                                                        | 4.0  |      | 6.0  | V    |

| V <sub>POS_acc</sub> | Positive output voltage accuracy            |                                                                                        | -1 % |      | +1 % |      |

| I <sub>POS</sub>     | Positive output current capability          |                                                                                        | 200  |      |      | mA   |

| V <sub>DO</sub>      | Dropout voltage                             | $V_{\text{REG}} = V_{\text{POS(NOM)}} = 5.4 \text{V}, I_{\text{OUT}} = 150 \text{ mA}$ |      | 160  |      | mV   |

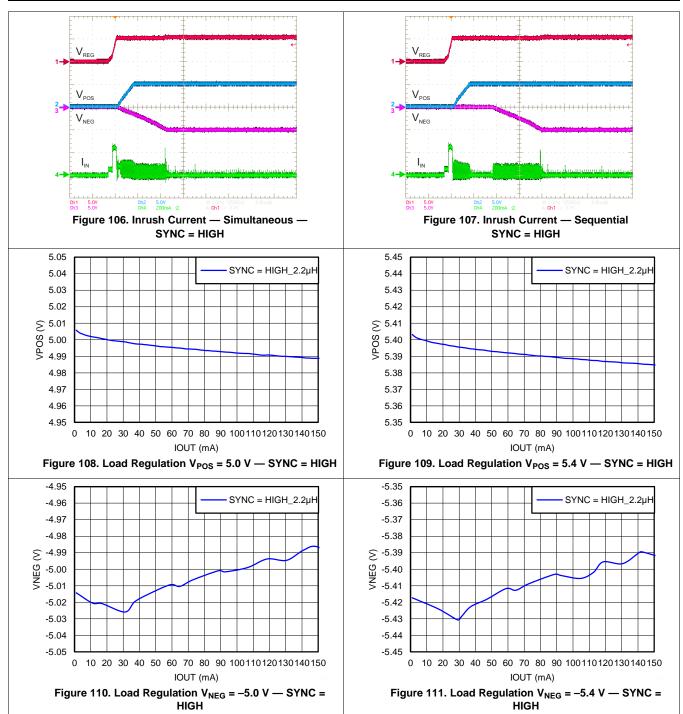

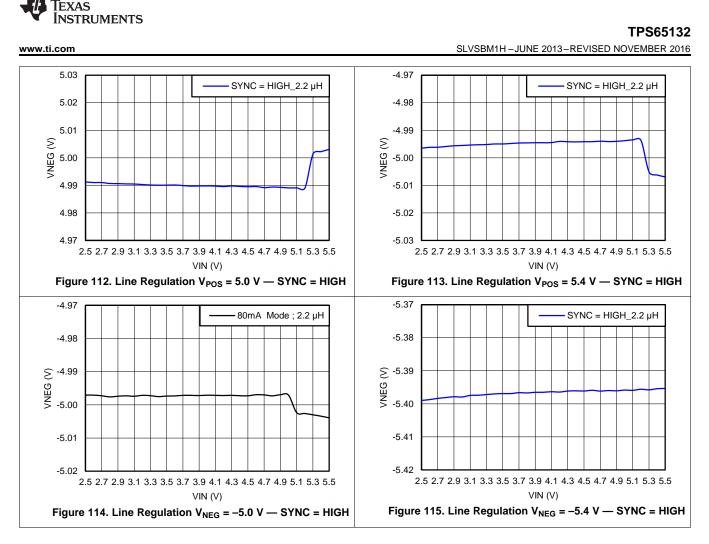

|                      | Line regulation                             | V <sub>IN</sub> = 2.5 V to 5.5 V, I <sub>OUT</sub> = 40 mA                             |      | 2.7  |      | mV   |

|                      | Load regulation                             | $\Delta I_{OUT} = 80 \text{ mA}$                                                       |      | 3.4  |      | %/A  |

| R <sub>D</sub>       | Discharge resistor                          |                                                                                        |      | 70   |      | Ω    |

| NEGATIV              | E CHARGE PUMP OUTPUT V <sub>NEG</sub>       |                                                                                        |      |      |      |      |

| V <sub>NEG</sub>     | Negative output voltage range               |                                                                                        | -6.0 |      | -4.0 | V    |

| V <sub>NEG_acc</sub> | Negative output voltage accuracy            |                                                                                        | -1 % |      | +1 % |      |

|                      |                                             | 40mA MODE                                                                              | 40   |      |      | - A  |

| I <sub>NEG</sub>     | Negative output current capability          | 80mA MODE                                                                              | 80   | -    |      | mA   |

| I <sub>NEG</sub>     | Negative output current capability          | TPS65132Sx, SYNC = HIGH                                                                | 150  |      |      | mA   |

| f <sub>OSC</sub>     | Negative charge pump switching<br>frequency |                                                                                        | 0.8  | 1.0  | 1.2  | MHz  |

|                      | Line regulation                             | V <sub>IN</sub> = 2.5 V to 5.5 V, I <sub>OUT</sub> = 40 mA                             |      | 3.3  |      | mV   |

|                      | Load regulation                             | ΔI <sub>OUT</sub> = 80 mA                                                              |      | 6.1  |      | %/A  |

| R <sub>D</sub>       | Discharge resistor                          |                                                                                        |      | 20   |      | Ω    |

**NSTRUMENTS**

EXAS

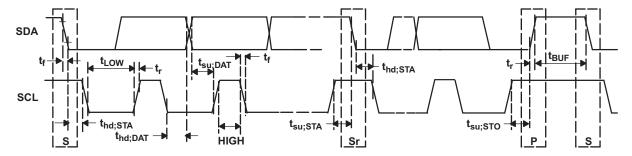

## 7.6 I<sup>2</sup>C Interface Timing Requirements / Characteristics (1)

|                                  | PARAMETER                                                | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MIN                       | TYP | MAX  | UNIT |

|----------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|------|------|

| ,                                |                                                          | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                           |     | 100  | kHz  |

| f <sub>SCL</sub>                 | SCL clock frequency                                      | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |     | 400  | kHz  |

| ILOW LOW period of the SCL clock |                                                          | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.7                       |     |      | μs   |

| t <sub>LOW</sub>                 | LOW period of the SCL clock                              | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.3                       |     |      | μs   |

|                                  |                                                          | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.0                       |     |      | μs   |

| t <sub>HIGH</sub>                | HIGH period of the SCL clock                             | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 600                       |     |      | ns   |

|                                  |                                                          | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.7                       |     |      | μs   |

| t <sub>BUF</sub>                 | Bus free time between a STOP and START condition         | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.3                       |     |      | μs   |

|                                  |                                                          | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.0                       |     |      | μs   |

| t <sub>hd;STA</sub>              | Hold time for a repeated START condition                 | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 600                       |     |      | ns   |

|                                  | Cotum times for a new seted CTADT and differ             | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.7                       |     |      | μs   |

| t <sub>su;STA</sub>              | Setup time for a repeated START condition                | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 600                       |     |      | ns   |

|                                  |                                                          | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 250                       |     |      | ns   |

| t <sub>su;DAT</sub>              | Data setup time                                          | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 100                       |     |      | ns   |

|                                  | Detechedd far                                            | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.05                      |     | 3.45 | μs   |

| [hd;DAT                          | Data hold time                                           | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.05                      |     | 0.9  | μs   |

| Rise time of SCL si              | Rise time of SCL signal after a repeated START condition | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 +<br>0.1C <sub>B</sub> |     | 1000 | ns   |

| t <sub>RCL1</sub>                | and after an acknowledge bit                             | Standard mode         Fast mode         Standard mode | 20 +<br>0.1C <sub>B</sub> |     | 1000 | ns   |

|                                  |                                                          | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 +<br>0.1C <sub>B</sub> |     | 1000 | ns   |

| t <sub>RCL</sub>                 | Rise time of SCL signal                                  | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 +<br>0.1C <sub>B</sub> |     | 300  | ns   |

|                                  |                                                          | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 +<br>0.1C <sub>B</sub> |     | 300  | ns   |

| t <sub>FCL</sub>                 | Fall time of SCL signal                                  | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 +<br>0.1C <sub>B</sub> |     | 300  | ns   |

|                                  | Pice time of SDA signal                                  | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 +<br>0.1C <sub>B</sub> |     | 1000 | ns   |

| t <sub>RDA</sub>                 | Rise unie of SDA signal                                  | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 +<br>0.1C <sub>B</sub> |     | 300  | ns   |

|                                  | Fall time of SDA signal                                  | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20 +<br>0.1C <sub>B</sub> |     | 300  | ns   |

| t <sub>FDA</sub>                 | Fall time of SCL signal                                  | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 +<br>0.1C <sub>B</sub> |     | 300  | ns   |

|                                  |                                                          | Standard mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.0                       |     |      | μs   |

| ι <sub>su;STO</sub>              | Setup time for STOP condition                            | Fast mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 600                       |     |      | ns   |

| CB                               | Capacitive load for SDA and SCL                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                           |     | 0.4  | nF   |

(1) Industry standard I<sup>2</sup>C timing characteristics according to I<sup>2</sup>C-Bus Specification, Version 2.1, January 2000. Not tested in production.

## Figure 1. Serial Interface Timing For F/S-Mode

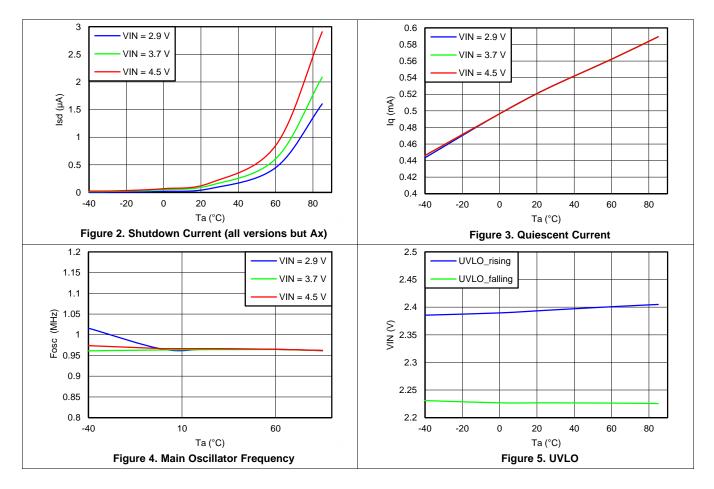

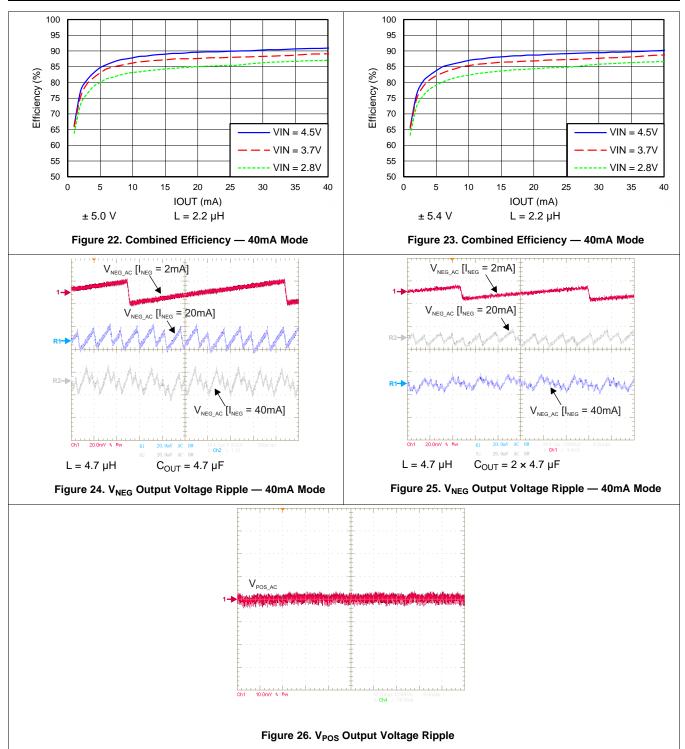

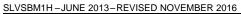

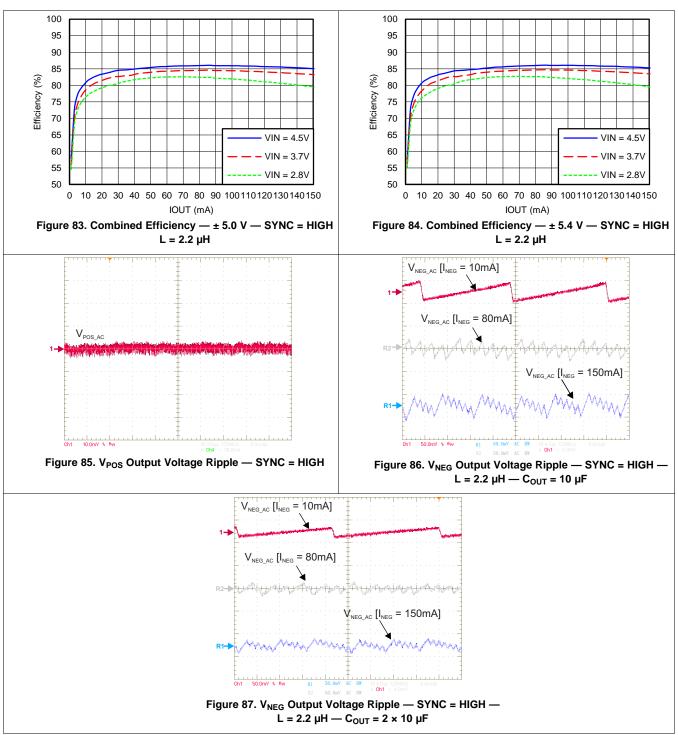

## 7.7 Typical Characteristics

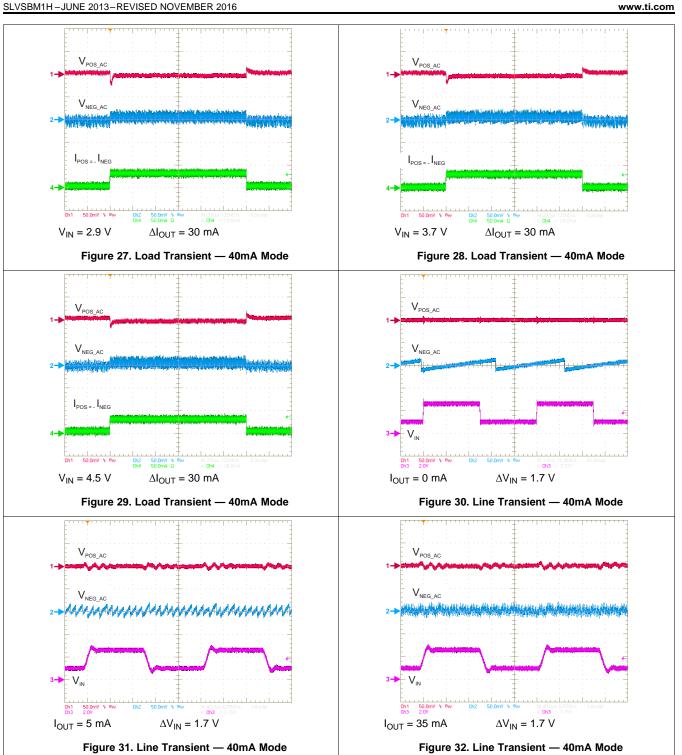

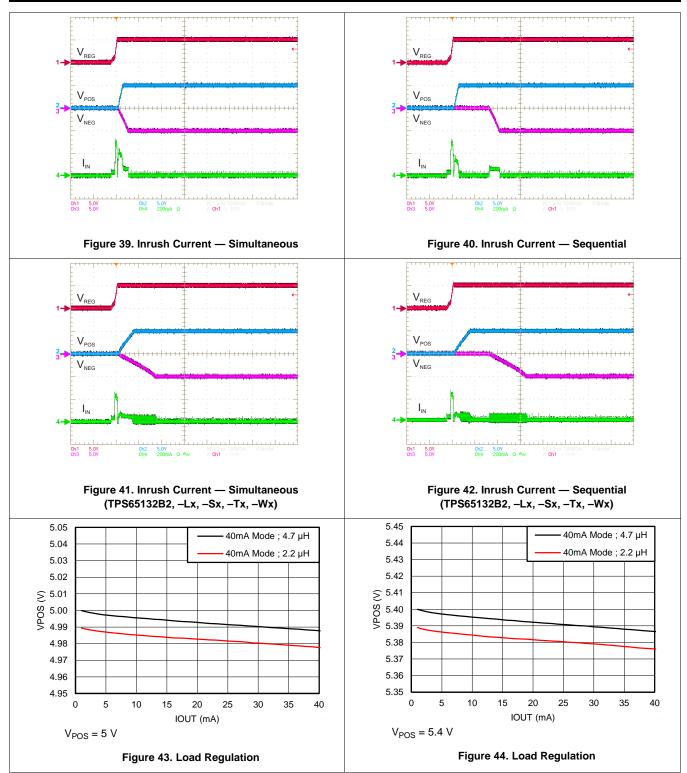

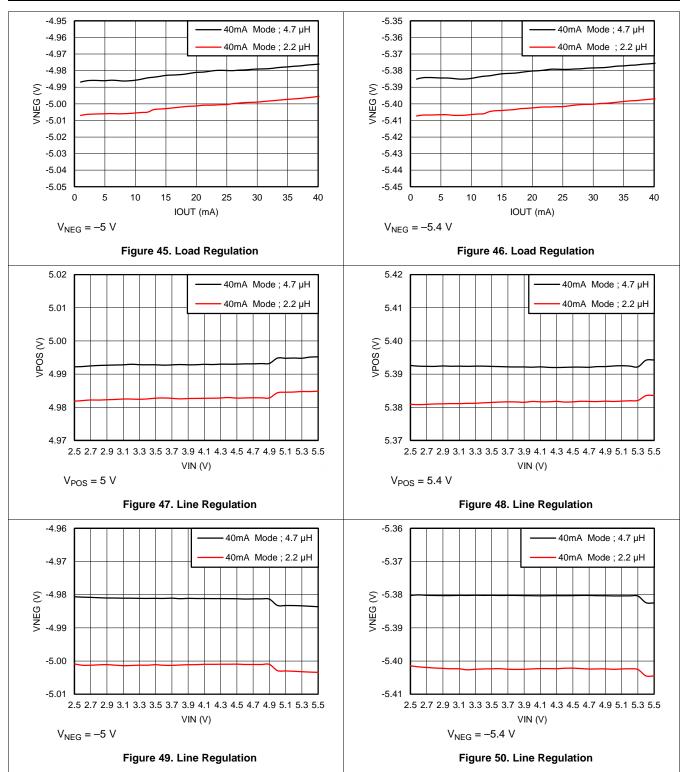

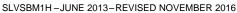

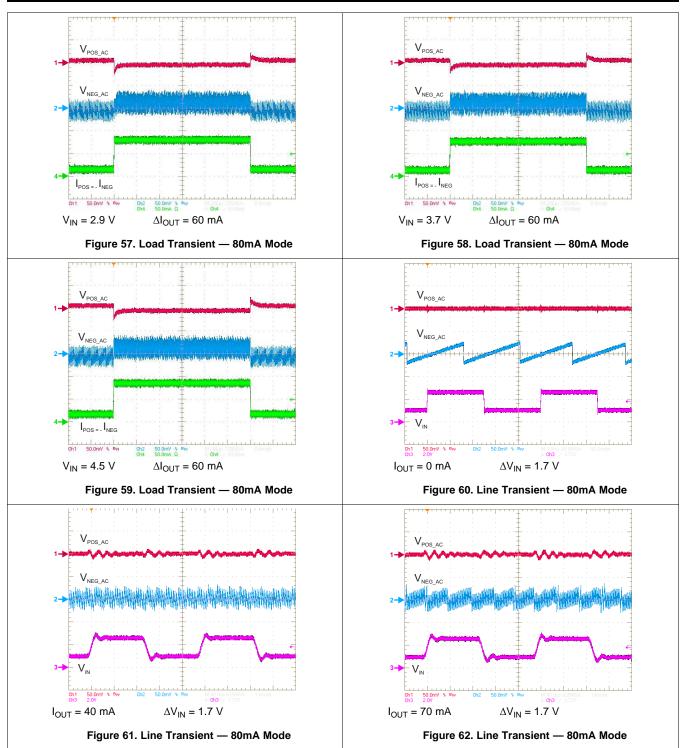

$V_{\text{IN}}\text{=}$  3.7 V,  $V_{\text{POS}}\text{=}$  5.4 V,  $V_{\text{NEG}}\text{=}$  –5.4 V, unless otherwise noted

## 8 Detailed Description

## 8.1 Overview

The TPS65132, supporting input voltage range from 2.5 V to 5.5 V, operates with a single inductor scheme to provide a high efficiency with a small solution size. The synchronous boost converter generates a positive voltage that is regulated down by an integrated LDO, providing the positive supply rail ( $V_{POS}$ ). The negative supply rail ( $V_{NEG}$ ) is generated by an integrated negative charge pump (or CPN) driven from the boost converter output pin, REG. The operating mode can be selected between 40mA and 80mA in order to select the necessary output current capability and to get the best efficiency possible based on the application. The device topology allows a 100% asymmetry of the output currents.

## 8.2 Functional Block Diagram

## 8.3 Feature Description

## 8.3.1 Undervoltage Lockout (UVLO)

The TPS65132 integrates an undervoltage lockout block (UVLO) that enables the device once the voltage on the VIN pin exceeds the UVLO threshold (2.5 V maximum). No output voltage will be generated as long as the enable signals are not pulled HIGH. The device, as well as all converters (boost converter, LDO, CPN), will be disabled as soon as the  $V_{IN}$  voltage falls below the UVLO threshold. The UVLO threshold is designed in a way that the TPS65132 will continue operating as long as  $V_{IN}$  stays above 2.3 V. This guarantees a proper operation even in the event of extensive line transients when the battery gets suddenly heavily loaded.

For TPS65132Ax, a 40 ms delay is starting as soon as the UVLO threshold is reached. This delay prevents the device to be disabled and enabled by an unwanted VIN voltage spike. Once this delay has passed, the output rails can be enabled and disabled as desired with the enable signals without any delay.

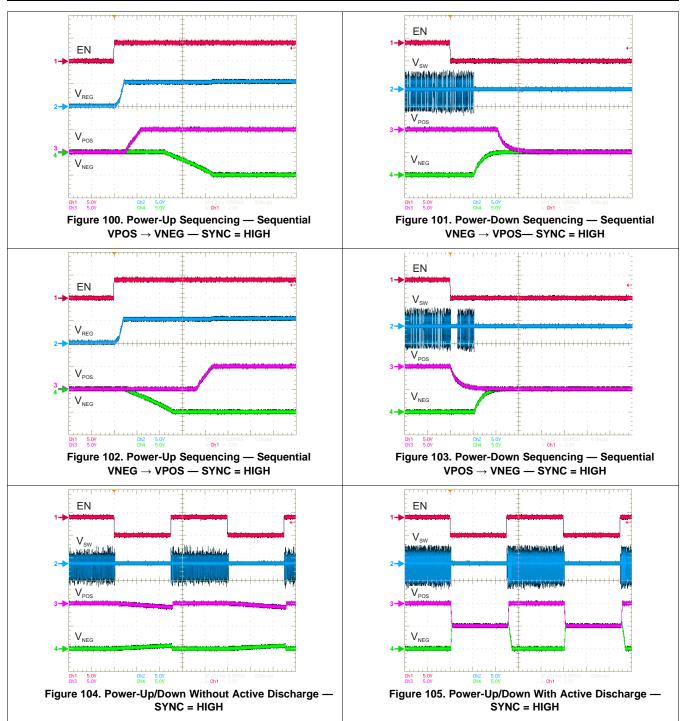

## 8.3.2 Active Discharge

An active discharge of the positive rail and/or the negative rail can be programmed (DISP and DISN bits respectively - refer to *Registers*). If programmed to be active, the discharge will occur at power down, when the enable signals go LOW (Figure 37 and Figure 38 for TPS65132Ax, Bx, Lx, Tx, Wx — Figure 105 and Figure 104 for TPS65132Sx). See *Power-Down And Discharge (LDO)* and *Power-Down And Discharge (CPN)* for a detailed description of how each device variant implements the active discharge function.

## **Feature Description (continued)**

#### 8.3.3 Boost Converter

#### 8.3.3.1 Boost Converter Operation

The synchronous boost converter uses a current mode topology and operates at a quasi-fixed frequency of typically 1.8 MHz, allowing chip inductors such as 2.2  $\mu$ H or 4.7  $\mu$ H to be used. The converter is internally compensated and provides a regulated output voltage automatically adjusted depending on the programmed V<sub>POS</sub> and V<sub>NEG</sub> voltages. The boost converter operates either in continuous conduction mode (CCM) or Pulse Frequency Modulation mode (PFM), depending on the load current in order to provide the highest efficiency possible. The switch node waveforms for CCM and DCM operation are shown in Figure 6 and Figure 7.

#### 8.3.3.2 Power-Up And Soft-Start (Boost Converter)

The boost converter starts switching as soon as one enable signal is pulled HIGH and the voltage on VIN pin is above the UVLO threshold. For TPS65132Ax, in the case where one enable signal is already HIGH when  $V_{IN}$  reaches the UVLO threshold, the boost converter will only start switching after a 40 ms delay has passed (see *Undervoltage Lockout (UVLO)*).

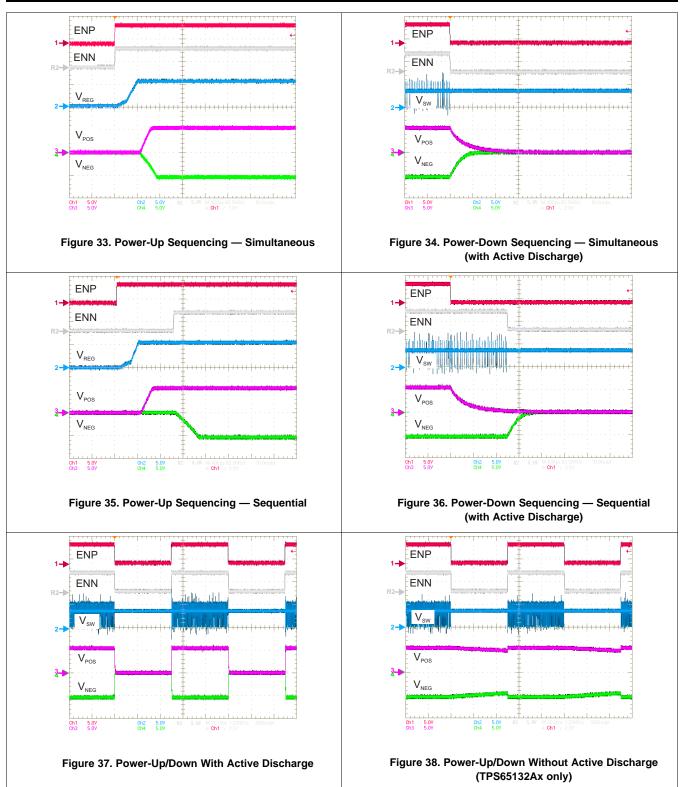

The boost converter starts up with an integrated soft-start to avoid drawing excessive inrush current from the supply. The output voltage  $V_{REG}$  is slowly ramped up to its target value. Typical startup waveforms for low-current applications are shown in Figure 33 and Figure 35.

#### 8.3.3.3 Power-Down (Boost Converter)

The boost converter stops switching when  $V_{IN}$  is below the UVLO threshold or when both output rails are disabled. For example, due to a special sequencing, the LDO might still be operating while the CPN is already disabled, in which case, the boost will continue operating until the LDO has been disabled. Typical power-down waveforms for low-current applications are shown in Figure 34 and Figure 36.

#### 8.3.3.4 Isolation (Boost Converter)

The boost converter output (REG) is isolated from the input supply  $V_{IN}$ , providing a true shutdown.

#### 8.3.3.5 Output Voltage (Boost Converter)

The output voltage of the boost converter is automatically adjusted depending on the programmed  $V_{POS}$  and  $V_{NEG}$  voltages.

### 8.3.3.6 Advanced Power-Save Mode For Light-Load Efficiency And PFM

The TPS65132 device integrates a power save mode to improve efficiency at light load. In power save mode the converter stops switching when the inductor current reaches 0 A. The device resumes its switching activity with one or more pulses once the  $V_{REG}$  voltage falls below its regulation level, and goes again into power save mode once the inductor current reaches 0 A. The pulse duration remains constant, but the frequency of these pulses varies according to the output load. This operating mode is also known as Pulse Frequency Modulation or PFM. Figure 6 provides plots of the inductor current and the switch node in PFM mode.

#### TPS65132 SLVSBM1H – JUNE 2013 – REVISED NOVEMBER 2016

www.ti.com

## Feature Description (continued)

## 8.3.4 LDO Regulator

## 8.3.4.1 LDO Operation

The Low Dropout regulator (or LDO) generates the positive voltage rail,  $V_{POS}$ , by regulating down the output voltage of the boost converter ( $V_{REG}$ ). Its inherent power supply rejection helps filtering the output ripple of the boost converter in order to provide on OUTP pin a clean voltage, e.g. to supply the source driver IC of the display.

## 8.3.4.2 Power-Up And Soft-Start (LDO)

The LDO starts operating as soon as the ENP signal is pulled HIGH, V<sub>IN</sub> voltage is above the UVLO threshold and the boost converter has reached its Power Good threshold.

In the case where the enable signal is already HIGH when  $V_{IN}$  exceeds the UVLO threshold, the boost converter will start first and the LDO will only start after the boost converter has reached its target voltage. For TPS65132Ax, the boost will start after the 40 ms delay has passed (see *Undervoltage Lockout (UVLO)*).

For TPS65132Sx the LDO startup is defined by the setting of the DLYx register and the SEQU bits, see *Registers* for more details.

The LDO integrates a soft-start that slowly ramps up its output voltage  $V_{POS}$  regardless of the output capacitor and the target voltage, as long as the LDO current limit is not reached. For TPS65132Ax and TPS65132Bx (except TPS65132B2), the typical startup time is 140 µs. For TPS65132B2, TPS65132Lx, TPS65132Sx, TPS65132Tx and TPS65132Wx, the typical ramp-up time is 500 µs and the inrush current is also reduced by a factor of 3. Typical startup waveforms for the low-current application are shown in Figure 33 to Figure 35.

#### 8.3.4.3 Power-Down And Discharge (LDO)

The LDO stops operating when  $V_{IN}$  is below the UVLO threshold or when ENP is pulled LOW. Or for TPS65132Sx when EN is pulled LOW, and the internal sequencing has passed.

The positive rail can be actively discharged to GND during power-down if required. A discharge selection bit is available to enable or disable this function. See *Registers* for more details, as well as waveforms in Figure 37 and Figure 38. Table 1 shows the  $V_{POS}$  active discharge behavior of each device variant.

| PART NUMBER | V <sub>IN</sub>     | ENP (or EN) | ENN (or SYNC) | V <sub>POS</sub> DISCHARGE |  |  |

|-------------|---------------------|-------------|---------------|----------------------------|--|--|

|             | < V <sub>UVLO</sub> | Don't Care  | Don't Care    | On                         |  |  |

|             |                     | Low         | Low           | Determined by DISP bit     |  |  |

| TPS65132Ax  | > V <sub>UVLO</sub> | Low         | High          | Determined by DISP bit     |  |  |

|             |                     | High        | Low           | Off                        |  |  |

|             |                     | High        | High          | Off                        |  |  |

| Table 1 | . V <sub>POS</sub> | Active | Discharge | Behavior |

|---------|--------------------|--------|-----------|----------|

|---------|--------------------|--------|-----------|----------|

## Feature Description (continued)

| PART NUMBER              | V <sub>IN</sub>                 | ENP (or EN) | ENN (or SYNC) | VPOS DISCHARGE         |

|--------------------------|---------------------------------|-------------|---------------|------------------------|

|                          | < V <sub>UVLO</sub>             | Don't Care  | Don't Care    | On                     |

| TPS65132Bx<br>TPS65132Lx | k<br>k<br>k > V <sub>UVLO</sub> | Low         | Low           | On                     |

| TPS65132Sx               |                                 | Low         | High          | Determined by DISP bit |

| TPS65132Tx<br>TPS65132Wx |                                 | High        | Low           | Off                    |

| 11 00010200              |                                 | High        | High          | Off                    |

Table 1. V<sub>POS</sub> Active Discharge Behavior (continued)

## 8.3.4.4 Isolation (LDO)

The LDO is isolating the  $V_{POS}$  rail from  $V_{REG}$  (boost converter output) as long as the rail is not enabled in order to ensure flexible startup like  $V_{NEG}$  before  $V_{POS}$ .

## 8.3.4.5 Setting The Output Voltage (LDO)

The output voltage of the LDO is programmable via a  $I^2C$  compatible interface, from -6.0 V to -4.0 V in 100 mV steps. For more details, please refer to the VPOS Register – Address: 0x00

## 8.3.5 Negative Charge Pump

## 8.3.5.1 Operation

The negative charge pump (CPN) generates the negative voltage rail,  $V_{NEG}$ , by inverting and regulating the output voltage of the boost converter ( $V_{REG}$ ). The charge pump uses 4 switches and an external flying capacitor to generate the negative rail. Two of the switches are turned on in the first phase to charge the flying capacitor up to  $V_{REG}$ , and in the second phase they are turned-off and the two others turn on to pump the energy negatively out of the OUTN capacitor.

## 8.3.5.2 Power-Up And Soft-Start (CPN)

The CPN starts operating as soon as the ENN signal is pulled HIGH, V<sub>IN</sub> voltage is above the UVLO threshold and the boost converter has reached its Power Good threshold.

In the case where the enable signal is already HIGH when  $V_{IN}$  reaches the UVLO threshold, the boost converter will start first and the CPN will only start after the boost converter has reached its target voltage. For TPS65132Ax, the boost will start after the 40 ms delay has passed (see *Undervoltage Lockout (UVLO)*).

For TPS65132Sx the CPN startup is defined by the setting of the DLYx register and the SEQU bits, see *Registers* for more details.

The CPN integrates a soft-start that slowly ramps up its output voltage  $V_{NEG}$  within a time defined by the selected mode (40mA or 80mA), the output voltage and the output capacitor value. For TPS65132Ax and TPS65132Bx (except TPS65132B2), the startup current charging the output capacitor in 40mA mode is 50 mA, and 100 mA typically in 80mA mode. For TPS65132B2, TPS65132Lx, TPS65132Tx, and TPS65132Wx, the typical ramp-up times are slowed down by a factor of 4 (i.e 12.5 mA and 25 mA typical output current for 40mA and 80mA modes respectively) and the inrush current is also reduced by a factor of about 4. Typical startup waveforms for the low-current application are shown in Figure 39 to Figure 42.

For TPS65132Sx, the negative rail starts-up in 40mA or 80mA mode, thus the startup current is set by the mode the device is programmed to, and not related to the SYNC pin state. The full current of 150 mA minimum is only released once both rails ( $V_{POS}$  and  $V_{NEG}$ ) have reached their Power Good levels.

$$t_{\text{STARTUP}} = \frac{C_{\text{OUT}} \times V_{\text{NEG}}}{I_{\text{STARTUP}}}$$

The estimated startup time can be calculated using the following formula:

Where:

$t_{\text{STARTUP}} = \text{startup time of the } V_{\text{NEG}} \text{ rail} \\ C_{\text{OUT}} = \text{output capacitance of the } V_{\text{NEG}} \text{ rail} \\ V_{\text{NEG}} = \text{target output voltage}$

$I_{\text{STARTUP}}$  = output current of the V<sub>NEG</sub> rail charging up the output capacitor at startup (12.5 mA, 25 mA, 50 mA or 100 mA as described above)

## 8.3.5.3 Power-Down And Discharge (CPN)

The CPN stops operating when  $V_{IN}$  is below the UVLO threshold or when ENN is pulled LOW.

Or when EN is pulled LOW in the TPS65132Sx, and the internal sequencing has passed.

The negative rail can be actively discharged to GND during power-down if required. A discharge selection bit is available to enable or disable this function. See for more details, as well as waveforms Figure 37 and Figure 38. Table 2 shows the V<sub>NEG</sub> discharge behavior of each device variant.

| PART NUMBER              | V <sub>IN</sub>     | ENP (or EN) | ENN (or SYNC) | V <sub>NEG</sub> DISCHARGE |

|--------------------------|---------------------|-------------|---------------|----------------------------|

|                          | < V <sub>UVLO</sub> | Don't Care  | Don't Care    | On                         |

|                          |                     | Low         | Low           | Determined by DISN bit     |

| TPS65132Ax               |                     | Low         | High          | Off                        |

|                          | > V <sub>UVLO</sub> | High        | Low           | Determined by DISN bit     |

|                          |                     | High        | High          | Off                        |

|                          | < V <sub>UVLO</sub> | Don't Care  | Don't Care    | On                         |

| TPS65132Bx               |                     | Low         | Low           | On                         |

| TPS65132Lx<br>TPS65132Tx |                     | Low         | High          | Off                        |

| TPS65132Wx               | > V <sub>UVLO</sub> | High        | Low           | Determined by DISN bit     |

|                          |                     | High        | High          | Off                        |

|                          | < V <sub>UVLO</sub> | Don't Care  | Don't Care    | On                         |

|                          |                     | Low         | Low           | On                         |

| TPS65132Sx               |                     | Low         | High          | Determined by DISN bit     |

|                          | > V <sub>UVLO</sub> | High        | Low           | Off                        |

|                          |                     | High        | High          | Off                        |

Table 2. V<sub>NEG</sub> Active Discharge Behavior

#### 8.3.5.4 Isolation (CPN)

The CPN isolates the  $V_{NEG}$  rail from  $V_{REG}$  (boost converter output) as long as the rail is not enabled in order to ensure flexible startup like  $V_{POS}$  before  $V_{NEG}$ .

#### 8.3.5.5 Setting The Output Voltage (CPN)

The output voltage of the CPN is programmable via a  $I^2C$  compatible interface, from -4.0 V to -6.0 V in 100 mV steps. For more details, please refer to the *VNEG Register* – *Address 0x01*.

#### 8.4 Device Functional Modes

#### 8.4.1 Enabling and Disabling the Device

At startup ( $V_{IN}$  goes above UVLO and at least one of the enable pins (ENP, ENN, or EN) goes HIGH), the EEPROM content is loaded into the DAC registers and the IC starts with these default values. The TPS65132 is enabled as long as the  $V_{IN}$  voltage is above the UVLO and one of the enable pins (ENP, ENN, or EN) is HIGH.

Pulling ENP or ENN LOW disables either rail ( $V_{POS}$  or  $V_{NEG}$  respectively); and, pulling both pins LOW disables the device entirely (the internal oscillator of the TPS65132Ax continues running to allow access to the I<sup>2</sup>C interface).

For TPS65132Sx, pulling EN LOW disables the device.

## 8.5 Programming

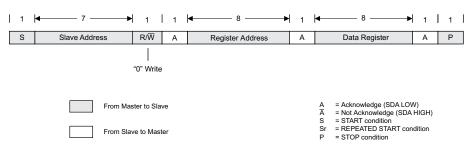

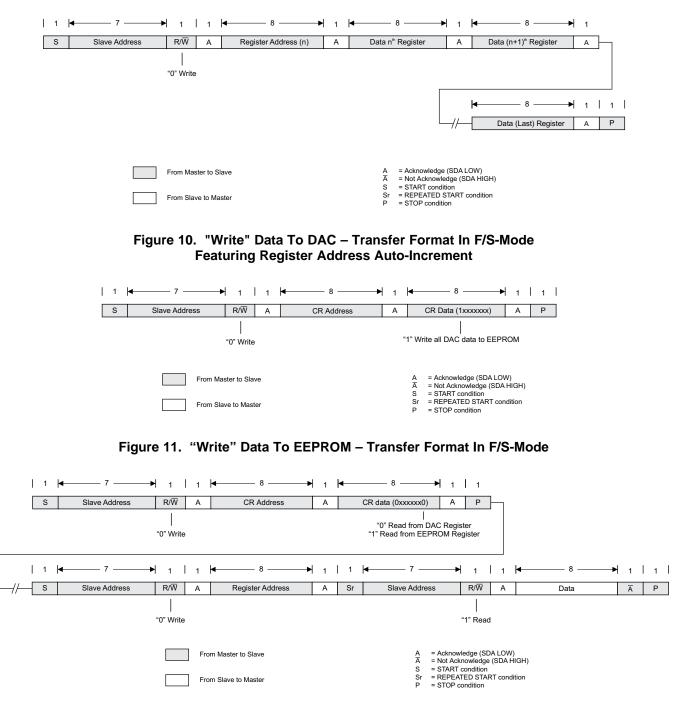

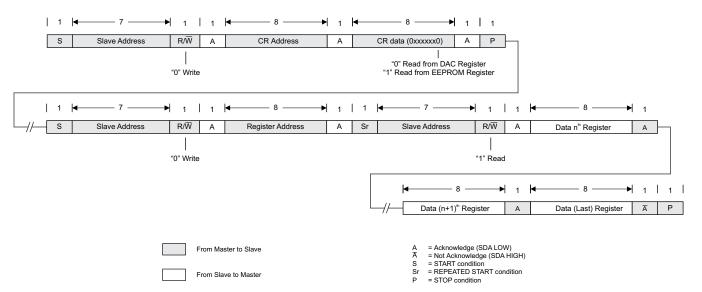

#### 8.5.1 I<sup>2</sup>C Serial Interface Description

The TPS65132 communicates through an industry standard I<sup>2</sup>C compatible interface, to receive data in slave mode. I<sup>2</sup>C is a 2-wire serial interface developed by Philips Semiconductor (see I<sup>2</sup>C-Bus Specification, Version 2.1, January 2000).