Sample &

Buy

## ADS8331, ADS8332

SBAS363E - DECEMBER 2009 - REVISED AUGUST 2016

# ADS833x Low-Power, 16-Bit, 500-kSPS, 4- and 8-Channel Unipolar Input Analog-to-Digital Converters With Serial Interface

#### Features 1

- Low-Power, Flexible Supply Range:

- 2.7-V to 5.5-V Analog Supply

- 8.7 mW (250 kSPS in Auto-NAP Mode, VA = 2.7 V, VBD = 1.65 V)

- 14.2 mW (500 kSPS, VA = 2.7 V, VBD = 1.65 V)

- Up to 500-kSPS Sampling Rate

- Excellent DC Performance:

- ±1.2 LSB Typical, ±2 LSB Maximum INL at 2.7 V

- ±0.6 LSB Typical, -1, 1.5 LSB Maximum DNL at 2.7 V

- 16-Bit NMC Over Temperature

- Excellent AC Performance at 5 V,  $f_{IN} = 1$  kHz:

- 91.5-dB SNR, 101-dB SFDR, -100-dB THD

- Flexible Analog Input Arrangement:

- On-Chip 4-, 8-Channel Mux With Breakout

- Auto, Manual Channel Select and Trigger

- Other Hardware Features:

- On-Chip Conversion Clock (CCLK)

- Software, Hardware Reset

- Programmable Status, Polarity EOC/INT

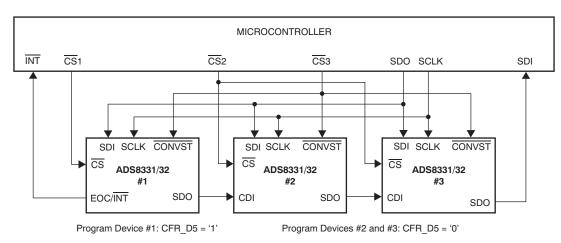

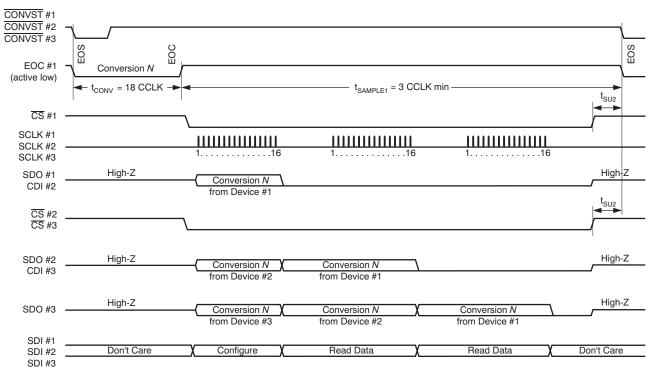

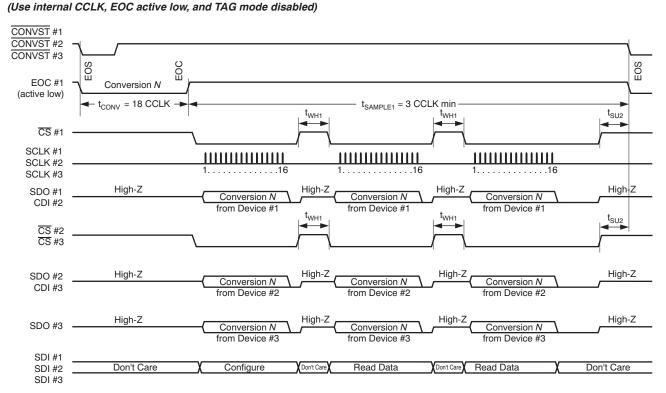

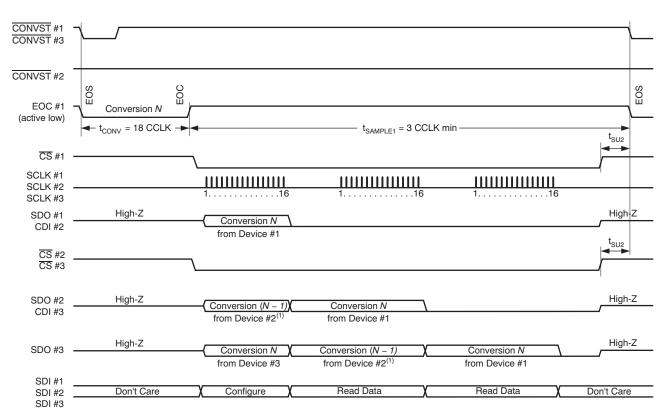

- **Daisy-Chain Mode**

- Global CONVST (Independent of CS)

- Deep, Nap, and Auto-NAP Powerdown Modes

- SPI™, DSP Compatible Serial Interface

- Separate I/O Supply: 1.65 V to VA

- SCLK up to 40 MHz (VA = VBD = 5 V)

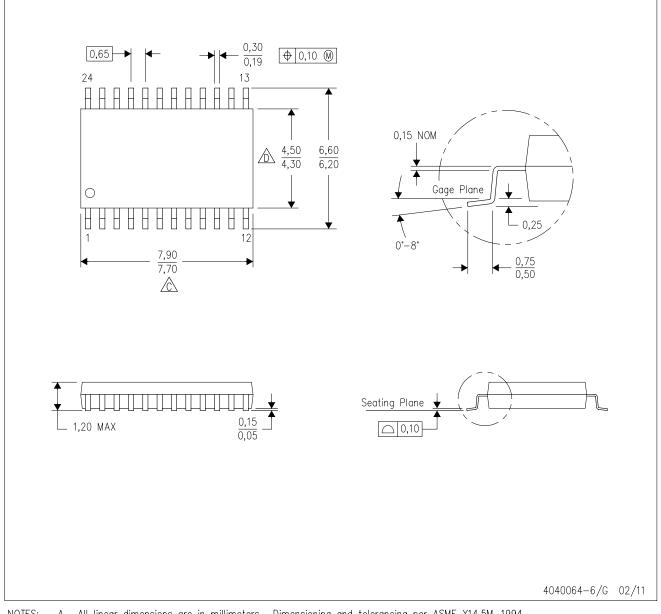

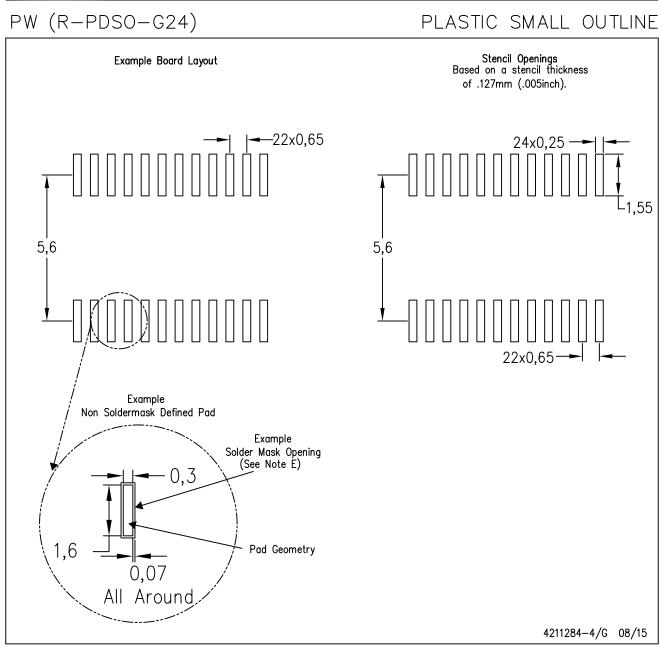

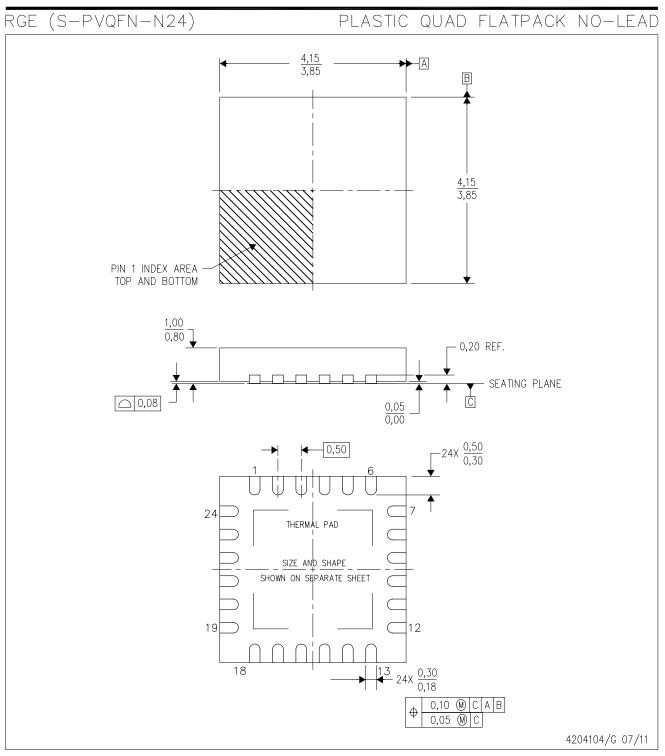

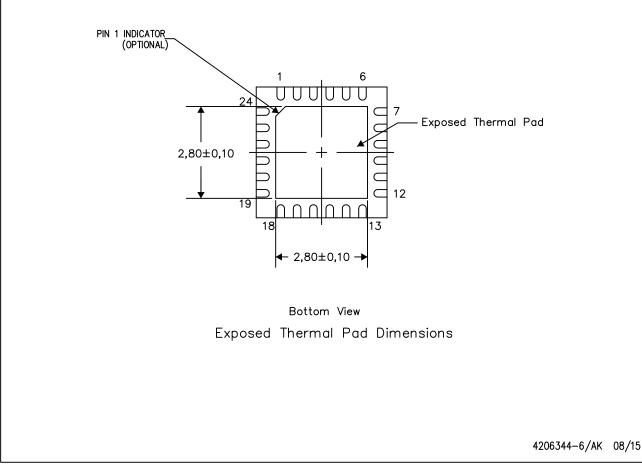

- 24-Pin 4-mm × 4-mm VQFN and 24-Pin TSSOP Packages

# 2 Applications

- Communications •

- Transducer Interfaces

- Medical Instruments

- Magnetometers

- Industrial Process Controls

- Data Acquisition Systems

- Automatic Test Equipment

# 3 Description

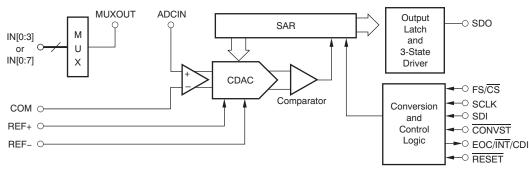

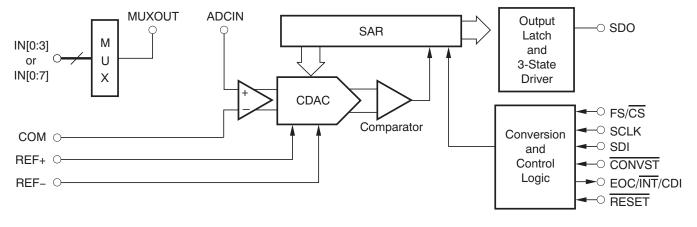

The ADS8331 is a low-power, 16-bit, 500-k samplesper-second (SPS) analog-to-digital converter (ADC) with a unipolar, 4-to-1 multiplexer (mux) input. The device includes a 16-bit capacitor-based successive approximation register (SAR) ADC with inherent sample and hold.

The ADS8332 is based on the same core and includes a unipolar 8-to-1 input mux. Both devices offer a high-speed, wide-voltage serial interface and are capable of daisy-chain operation when multiple converters are used.

These converters are available in 24-pin, 4 × 4 VQFN and 24-pin TSSOP packages and are fully specified for operation over the industrial -40°C to 85°C temperature range.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |  |

|-------------|------------|-------------------|--|

| 400000      | VQFN (24)  | 4.00 mm × 4.00 mm |  |

| ADS833x     | TSSOP (24) | 7.80 mm × 4.40 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## Block Diagram

# **Table of Contents**

| 1 | Feat | ures 1                                     |

|---|------|--------------------------------------------|

| 2 | Арр  | lications 1                                |

| 3 | Des  | cription 1                                 |

| 4 | Revi | sion History 2                             |

| 5 |      | panion Products                            |

| 6 | Devi | ice Comparison 4                           |

| 7 |      | Configuration and Functions 4              |

| 8 | Spe  | cifications6                               |

|   | 8.1  | Absolute Maximum Ratings 6                 |

|   | 8.2  | ESD Ratings 6                              |

|   | 8.3  | Recommended Operating Conditions           |

|   | 8.4  | Thermal Information 6                      |

|   | 8.5  | Electrical Characteristics: VA = 2.7 V 7   |

|   | 8.6  | Electrical Characteristics: VA = 5 V 9     |

|   | 8.7  | Timing Requirements: VA = 2.7 V 11         |

|   | 8.8  | Timing Characteristics: VA = 5 V 12        |

|   | 8.9  | Typical Characteristics: DC Performance 14 |

|   | 8.10 | Typical Characteristics: AC Performance 17 |

| 9 | Deta | niled Description                          |

|   | 9.1  | Overview 20                                |

|   |      |                                            |

|    | 9.2   | Functional Block Diagram                        | 20 |

|----|-------|-------------------------------------------------|----|

|    | 9.3   | Feature Description                             | 20 |

|    | 9.4   | Device Functional Modes                         | 22 |

|    | 9.5   | Programming                                     | 29 |

| 10 | Арр   | lication and Implementation                     | 37 |

|    | 10.1  | Application Information                         | 37 |

|    | 10.2  | Typical Applications                            | 41 |

| 11 | Pow   | er Supply Recommendations                       | 44 |

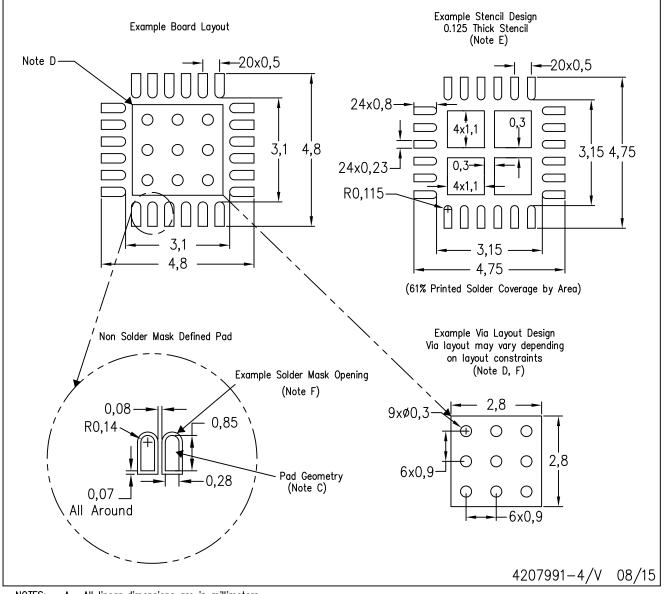

| 12 | Layo  | out                                             | 44 |

|    | 12.1  | Layout Guidelines                               | 44 |

|    | 12.2  | Layout Example                                  | 46 |

| 13 | Devi  | ice and Documentation Support                   | 47 |

|    | 13.1  | Documentation Support                           | 47 |

|    | 13.2  | Related Links                                   | 47 |

|    | 13.3  | Receiving Notification of Documentation Updates | 47 |

|    | 13.4  | Community Resources                             | 47 |

|    | 13.5  | Trademarks                                      | 47 |

|    | 13.6  | Electrostatic Discharge Caution                 | 47 |

|    | 13.7  | Glossary                                        | 48 |

| 14 |       | hanical, Packaging, and Orderable               |    |

|    | Infor | mation                                          | 48 |

|    |       |                                                 |    |

# **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision D (October 2015) to Revision E                                                                                                                                                                                                                                                   | Page               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Changed VA parameter maximum specification in Recommended Operating Conditions table                                                                                                                                                                                                                   |                    |

| Changes from Revision C (May 2012) to Revision D                                                                                                                                                                                                                                                       | Page               |

| <ul> <li>Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and<br/>section, Power Supply Recommendations section, Layout section, Device and Documentation Su<br/>Mechanical, Packaging, and Orderable Information section</li> </ul>                         | oport section, and |

|                                                                                                                                                                                                                                                                                                        |                    |

|                                                                                                                                                                                                                                                                                                        | Page               |

|                                                                                                                                                                                                                                                                                                        |                    |

| <ul> <li>Changes from Revision B (December 2010) to Revision C</li> <li>Changed name of last column in Low-Power, High-Speed, SAR Converter Family table</li> <li>Deleted 4-channel and 8-channel rows from 14-Bit Pseudo-Diff resolution in Low-Power, High-Speed</li> </ul>                          | 4<br>eed, SAR      |

| <ul> <li>Changes from Revision B (December 2010) to Revision C</li> <li>Changed name of last column in Low-Power, High-Speed, SAR Converter Family table</li> </ul>                                                                                                                                    |                    |

| <ul> <li>Changes from Revision B (December 2010) to Revision C</li> <li>Changed name of last column in Low-Power, High-Speed, SAR Converter Family table</li> <li>Deleted 4-channel and 8-channel rows from 14-Bit Pseudo-Diff resolution in Low-Power, High-Spe<br/>Converter Family table</li> </ul> | 4 eed, SAR 4       |

www.ti.com

# **5** Companion Products

| Part number                                                                                               | Name                                                                                                 |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| REF3240                                                                                                   | 4.096V 4ppm/°C, 100uA SOT23-6 Series (Bandgap) Voltage Reference                                     |

| DAC8562                                                                                                   | 16-bit, dual-channel, low-power, ultra-low glitch, buffered voltage output DAC with 2.5V,4ppm/°C ref |

| DAC8568 16-bit, octal-channel, ultra-low glitch, voltage output DAC with 2.5V, 2ppm/°C internal reference |                                                                                                      |

| LM5160                                                                                                    | Wide Input 65V, 1.5A Synchronous Step-Down DC-DC Conv                                                |

| OPA2348                                                                                                   | 1MHz, 45uA, RRIO, Dual Op Amp                                                                        |

#### ADS8331, ADS8332 SBAS363E – DECEMBER 2009 – REVISED AUGUST 2016

www.ti.com

NSTRUMENTS

ÈXAS

# 6 Device Comparison

| RESOLUTION | CHANNELS | f <sub>S</sub> ≤ 250 kSPS | 250 kSPS < f <sub>S</sub> ≤ 500 kSPS | 500 kSPS < f <sub>S</sub> ≤ 1 MSPS |

|------------|----------|---------------------------|--------------------------------------|------------------------------------|

| 18 bits    | 8        | —                         | ADS8698                              | —                                  |

| TO DIIS    | 4        | —                         | ADS8694                              |                                    |

|            | 0        | ADS8344                   | ADS8688                              |                                    |

|            | 8        | ADS8345                   | ADS8688A                             | —                                  |

| 16 bits    |          | ADS8341                   | ADS8684                              |                                    |

|            | 4        | ADS8342                   | ADS8684A                             | _                                  |

|            |          | ADS8343                   |                                      |                                    |

|            |          | TLC3548                   |                                      |                                    |

| 1.4 hito   | 8        | TLC3578                   | ADS8678                              | —                                  |

| 14 bits    | 4        | TLC3544                   | - ADS8674                            | AD27000                            |

|            |          | TLC3574                   |                                      | ADS7263                            |

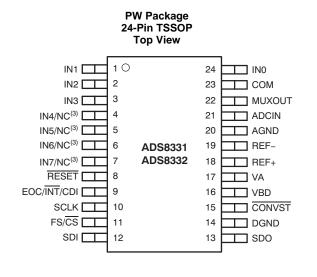

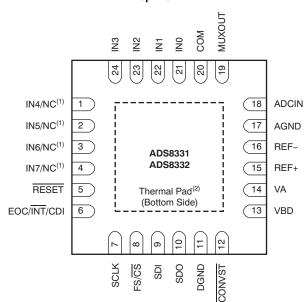

# 7 Pin Configuration and Functions

- (1) NC = No internal connection (ADS8331 only).

- (2) Connect thermal pad to analog ground.

- (3) NC = No internal connection (ADS8331 only).

### Pin Functions: ADS8331

|        | PIN   |      | 1/0 | DESCRIPTION                                                   |  |

|--------|-------|------|-----|---------------------------------------------------------------|--|

| NAME   | TSSOP | VQFN | 1/0 | DESCRIPTION                                                   |  |

| ADCIN  | 21    | 18   | Ι   | ADC input                                                     |  |

| AGND   | 20    | 17   | _   | Analog ground                                                 |  |

| DGND   | 14    | 11   | —   | Digital interface ground                                      |  |

| COM    | 23    | 20   | Ι   | Common ADC input (usually connected to AGND)                  |  |

| CONVST | 15    | 12   | Ι   | Conversion start. Freezes sample and hold, starts conversion. |  |

## Pin Functions: ADS8331 (continued)

| PIN                 |         | 1/0   | DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                                |  |

|---------------------|---------|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                | TSSOP   | VQFN  | 1/0         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                    |  |

| EOC/INT/CDI         | 9       | 6     | 0/0/I       | Status output. If programmed as end-of-conversion (EOC), this pin is low (default) when a conversion is in progress. If programmed as an interrupt (INT), this pin is low (default) after the end of conversion and returns high after FS/CS goes low. The polarity of EOC or INT is programmable.<br>This pin can also be used as a chain data input (CDI) when operated in daisy-chain mode. |  |

| FS/CS               | 11      | 8     | Ι           | Frame sync signal for DSP (such as TMS320 <sup>™</sup> DSP) or chip select input for SPI.                                                                                                                                                                                                                                                                                                      |  |

| IN <sub>[0:3]</sub> | 1-3, 24 | 21-24 | I           | Mux inputs                                                                                                                                                                                                                                                                                                                                                                                     |  |

| NC                  | 4-7     | 1-4   | —           | No connection                                                                                                                                                                                                                                                                                                                                                                                  |  |

| MUXOUT              | 22      | 19    | 0           | Mux output                                                                                                                                                                                                                                                                                                                                                                                     |  |

| REF+                | 18      | 15    | I           | External reference input                                                                                                                                                                                                                                                                                                                                                                       |  |

| REF-                | 19      | 16    | _           | External reference ground (connect to AGND through an individual via on the printed-circuit-<br>board)                                                                                                                                                                                                                                                                                         |  |

| RESET               | 8       | 5     | I           | External reset (active low)                                                                                                                                                                                                                                                                                                                                                                    |  |

| SCLK                | 10      | 7     | I           | SPI clock for serial interface                                                                                                                                                                                                                                                                                                                                                                 |  |

| SDI                 | 12      | 9     | Ι           | SPI serial data in                                                                                                                                                                                                                                                                                                                                                                             |  |

| SDO                 | 13      | 10    | 0           | SPI serial data out                                                                                                                                                                                                                                                                                                                                                                            |  |

| VA                  | 17      | 14    | _           | Analog supply, 2.7 V to 5.5 V                                                                                                                                                                                                                                                                                                                                                                  |  |

| VBD                 | 16      | 13    | _           | Digital interface supply                                                                                                                                                                                                                                                                                                                                                                       |  |

#### Pin Functions: ADS8332

| PIN                 |         | 1/0            | DECODIDION |                                                                                                                                                                                                                                                                                                                                                                                                |  |

|---------------------|---------|----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                | TSSOP   | VQFN           | 1/0        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                    |  |

| ADCIN               | 21      | 18             | I          | ADC input                                                                                                                                                                                                                                                                                                                                                                                      |  |

| AGND                | 20      | 17             | _          | Analog ground                                                                                                                                                                                                                                                                                                                                                                                  |  |

| DGND                | 14      | 11             | —          | Digital interface ground                                                                                                                                                                                                                                                                                                                                                                       |  |

| COM                 | 23      | 20             | I          | Common ADC input (usually connected to AGND)                                                                                                                                                                                                                                                                                                                                                   |  |

| CONVST              | 15      | 12             | I          | Conversion start. Freezes sample and hold, starts conversion.                                                                                                                                                                                                                                                                                                                                  |  |

| EOC/INT/CDI         | 9       | 6              | 0/0/I      | Status output. If programmed as end-of-conversion (EOC), this pin is low (default) when a conversion is in progress. If programmed as an interrupt (INT), this pin is low (default) after the end of conversion and returns high after FS/CS goes low. The polarity of EOC or INT is programmable.<br>This pin can also be used as a chain data input (CDI) when operated in daisy-chain mode. |  |

| FS/CS               | 11      | 8              | I.         | Frame sync signal for DSP (such as TMS320 <sup>™</sup> DSP) or chip select input for SPI.                                                                                                                                                                                                                                                                                                      |  |

| IN <sub>[0:7]</sub> | 1-7, 24 | 1-4, 21-<br>24 | I          | Mux inputs                                                                                                                                                                                                                                                                                                                                                                                     |  |

| MUXOUT              | 22      | 19             | 0          | Mux output                                                                                                                                                                                                                                                                                                                                                                                     |  |

| REF+                | 18      | 15             | I          | External reference input                                                                                                                                                                                                                                                                                                                                                                       |  |

| REF-                | 19      | 16             | _          | External reference ground (connect to AGND through an individual via on the printed-circuit-<br>board)                                                                                                                                                                                                                                                                                         |  |

| RESET               | 8       | 5              | I          | External reset (active low)                                                                                                                                                                                                                                                                                                                                                                    |  |

| SCLK                | 10      | 7              | I          | SPI clock for serial interface                                                                                                                                                                                                                                                                                                                                                                 |  |

| SDI                 | 12      | 9              | I          | SPI serial data in                                                                                                                                                                                                                                                                                                                                                                             |  |

| SDO                 | 13      | 10             | 0          | SPI serial data out                                                                                                                                                                                                                                                                                                                                                                            |  |

| VA                  | 17      | 14             | —          | Analog supply, 2.7 V to 5.5 V                                                                                                                                                                                                                                                                                                                                                                  |  |

| VBD                 | 16      | 13             |            | Digital interface supply                                                                                                                                                                                                                                                                                                                                                                       |  |

SBAS363E - DECEMBER 2009-REVISED AUGUST 2016

www.ti.com

#### Specifications 8

## 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                |                                               | MIN                   | MAX                                                       | UNIT |  |

|--------------------------------|-----------------------------------------------|-----------------------|-----------------------------------------------------------|------|--|

|                                | IN <sub>X</sub> , MUXOUT, ADCIN, REF+ to AGND | -0.3                  | VA + 0.3                                                  |      |  |

|                                | COM, REF- to AGND                             | -0.3                  | 0.3                                                       |      |  |

| Voltage                        | VA to AGND                                    | -0.3                  | 7                                                         | V    |  |

|                                | VBD to DGND                                   | -0.3                  | 7                                                         |      |  |

|                                | AGND to DGND                                  | -0.3                  | 0.3                                                       |      |  |

| Digital input                  | voltage to DGND                               | -0.3                  | VBD + 0.3                                                 | V    |  |

| Digital output voltage to DGND |                                               | -0.3                  | VBD + 0.3                                                 | V    |  |

| 4 × 4                          | Power dissipation                             | (T <sub>J</sub> Max – | (T <sub>J</sub> Max – T <sub>A</sub> ) / R <sub>θJA</sub> |      |  |

| VQFN-24<br>Package             | R <sub>0JA</sub> thermal impedance            |                       | 47                                                        | °C/W |  |

| TSSOP-24                       | Power dissipation                             | (T <sub>J</sub> Max - | – Τ <sub>Α</sub> ) / θ <sub>JA</sub>                      | W    |  |

| Package                        | R <sub>0JA</sub> thermal impedance            |                       | 47                                                        | °C/W |  |

| Operating fro                  | ee-air temperature, T <sub>A</sub>            | -40                   | 85                                                        | °C   |  |

| Junction terr                  | perature, T <sub>J</sub> Max                  |                       | 150                                                       | °C   |  |

| Storage tem                    | perature range, T <sub>stg</sub>              | -65                   | 150                                                       | °C   |  |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolutemaximum-rated conditions for extended periods may affect device reliability.

## 8.2 ESD Ratings

|                      |                        |                                                                          | VALUE | UNIT |

|----------------------|------------------------|--------------------------------------------------------------------------|-------|------|

|                      |                        | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>        | ±2000 |      |

| V <sub>(ESD)</sub> E | lectrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{(2)}$ | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (1)

(2)

## 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|     |                        | MIN  | NOM | MAX      | UNIT |

|-----|------------------------|------|-----|----------|------|

| VA  | Analog supply voltage  | 2.7  | 3   | 5.5      | V    |

| VBD | Digital supply voltage | 1.65 | 3   | VA + 0.2 | V    |

## 8.4 Thermal Information

|                       |                                              | ADS        | ADS833x    |      |  |  |

|-----------------------|----------------------------------------------|------------|------------|------|--|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGE (VQFN) | PW (TSSOP) | UNIT |  |  |

|                       |                                              | 24 PINS    | 24 PINS    |      |  |  |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 31.9       | 78.3       | °C/W |  |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 29.2       | 12.1       | °C/W |  |  |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 8.7        | 33.8       | °C/W |  |  |

| ΨJT                   | Junction-to-top characterization parameter   | 0.3        | 0.3        | °C/W |  |  |

| Ψјв                   | Junction-to-board characterization parameter | 8.7        | 33.5       | °C/W |  |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.25       | NA         | °C/W |  |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application (1) report, SPRA953.

## 8.5 Electrical Characteristics: VA = 2.7 V

at  $T_A = -40^{\circ}$ C to 85°C, VA = 2.7 V, VBD = 1.65 V to 2.7 V,  $V_{REF} = 2.5$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

|                              | PARAMETER                                                                     | TEST C                                                | ONDITIONS               | MIN        | TYP   | MAX              | UNIT               |  |

|------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------|------------|-------|------------------|--------------------|--|

| ANALOG                       | INPUT                                                                         |                                                       |                         |            |       |                  |                    |  |

|                              | Full-scale input voltage (1)                                                  | IN <sub>X</sub> – COM, ADCIN – COI                    | M                       | 0          |       | V <sub>REF</sub> | V                  |  |

|                              |                                                                               | IN <sub>X</sub> , ADCIN                               | IN <sub>X</sub> , ADCIN |            |       | VA + 0.2         |                    |  |

|                              | Absolute input voltage                                                        | COM                                                   |                         | AGND - 0.2 |       | AGND + 0.2       | V                  |  |

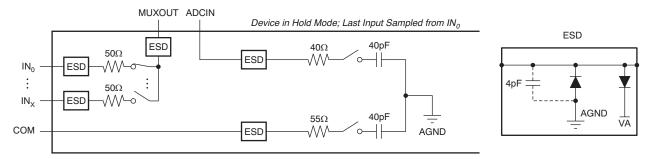

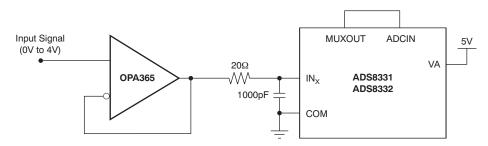

|                              | Input capacitance                                                             | ADCIN                                                 |                         |            | 40    | 45               | pF                 |  |

|                              | Input leakage current                                                         | Unselected ADC input                                  |                         |            | ±1    |                  | nA                 |  |

| SYSTEM                       | PERFORMANCE                                                                   |                                                       |                         |            |       |                  |                    |  |

|                              | Resolution                                                                    |                                                       |                         |            | 16    |                  | Bits               |  |

|                              | No missing codes                                                              |                                                       |                         | 16         |       |                  | Bits               |  |

| 15.11                        | late and line and t                                                           | ADS8331I, ADS8332I                                    |                         | -3         | ±2    | 3                | 100(2)             |  |

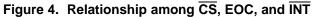

| INL                          | Integral linearity                                                            | ADS8331IB, ADS8332IB                                  |                         | -2         | ±1.2  | 2                | LSB <sup>(2)</sup> |  |

| DNII                         |                                                                               | ADS8331I, ADS8332I                                    |                         | -1         | ±0.6  | 2                | 100(2)             |  |

| DNL                          | Differential linearity                                                        | ADS8331IB, ADS8332IB                                  |                         | -1         | ±0.6  | 1.5              | LSB <sup>(2)</sup> |  |

| Eo                           | Offset error <sup>(3)</sup>                                                   |                                                       |                         | -0.5       | ±0.15 | 0.5              | mV                 |  |

| -                            | Offset error drift                                                            |                                                       |                         |            | ±1    |                  | PPM/°C             |  |

|                              | Offset error matching                                                         |                                                       |                         | -0.2       |       | 0.2              | mV                 |  |

| E <sub>G</sub>               | Gain error                                                                    |                                                       |                         | -0.25      | -0.06 | 0.25             | %FSR               |  |

|                              | Gain error drift                                                              |                                                       |                         |            | ±0.4  |                  | PPM/°C             |  |

|                              | Gain error matching                                                           |                                                       |                         | -0.003     |       | 0.003            | %FSR               |  |

|                              | Transition noise                                                              |                                                       |                         |            | 28    |                  | μV RMS             |  |

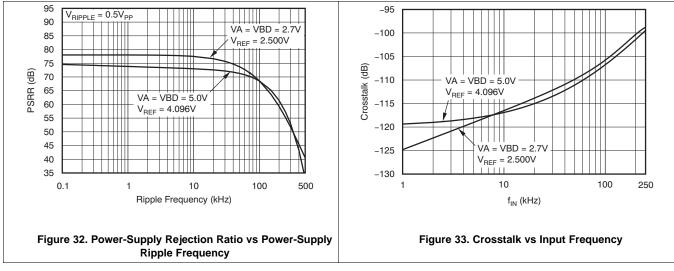

| PSRR                         | Power-supply rejection ratio                                                  |                                                       |                         |            | 74    |                  | dB                 |  |

| SAMPLIN                      | NG DYNAMICS                                                                   |                                                       |                         |            |       |                  |                    |  |

| t <sub>CONV</sub>            | Conversion time                                                               |                                                       |                         |            | 18    |                  | CCLK               |  |

| t <sub>SAMPLE1</sub>         |                                                                               | Manual-trigger mode                                   |                         | 3          |       |                  |                    |  |

| t <sub>SAMPLE2</sub>         | Acquisition time                                                              | Auto-trigger mode                                     |                         |            | 3     |                  | CCLK               |  |

| -                            | Throughput rate                                                               |                                                       |                         |            |       | 500              | kSPS               |  |

| DYNAMI                       | C CHARACTERISTICS                                                             |                                                       |                         | IL.        |       | L. L.            |                    |  |

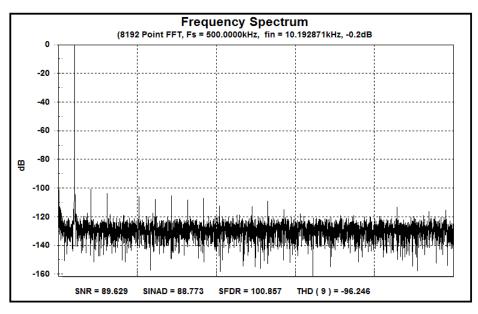

|                              |                                                                               | $V_{IN} = 2.5 V_{PP}$ at 1 kHz                        |                         |            | -101  |                  |                    |  |

| THD                          | Total harmonic distortion <sup>(4)</sup>                                      | V <sub>IN</sub> = 2.5 V <sub>PP</sub> at 10 kHz       |                         |            | -95   |                  | dB                 |  |

|                              |                                                                               |                                                       | ADS8331I, ADS8332I      |            | 88    |                  |                    |  |

|                              |                                                                               | $V_{IN} = 2.5 V_{PP} \text{ at } 1 \text{ kHz}$       | ADS8331IB, ADS8332IB    |            | 89    |                  |                    |  |

| SNR                          | Signal-to-noise ratio                                                         |                                                       | ADS8331I, ADS8332I      |            | 86.5  |                  | dB                 |  |

|                              |                                                                               | $V_{IN} = 2.5 V_{PP}$ at 10 kHz                       | ADS8331IB, ADS8332IB    |            | 87.5  |                  |                    |  |

|                              |                                                                               |                                                       | ADS8331I, ADS8332I      |            | 87.5  |                  |                    |  |

|                              |                                                                               | $V_{IN} = 2.5 V_{PP}$ at 1 kHz                        | ADS8331IB, ADS8332IB    |            | 88.5  |                  |                    |  |

| SINAD                        | Signal-to-noise + distortion                                                  |                                                       | ADS8331I, ADS8332I      |            | 86    |                  | dB                 |  |

|                              |                                                                               | $V_{IN} = 2.5 V_{PP}$ at 10 kHz                       | ADS8331IB, ADS8332IB    |            | 87    |                  |                    |  |

|                              |                                                                               | V <sub>IN</sub> = 2.5 V <sub>PP</sub> at 1 kHz        |                         |            | 103   |                  |                    |  |

| SFDR                         | R Spurious-free dynamic range V <sub>IN</sub> = 2.5 V <sub>PP</sub> at 10 kHz |                                                       |                         |            | 98    |                  | dB                 |  |

|                              | 0                                                                             | $V_{IN} = 2.5 V_{PP}$ at 1 kHz                        |                         |            | 125   |                  |                    |  |

|                              | Crosstalk                                                                     | V <sub>IN</sub> = 2.5 V <sub>PP</sub> at 100 kHz      |                         |            | 108   |                  | dB                 |  |

|                              |                                                                               | IN <sub>X</sub> – COM with MUXOUT                     | tied to ADCIN           |            | 17    |                  |                    |  |

| -3-dB small-signal bandwidth |                                                                               | $M_{X}^{2} = COM WITH MOXOOT HER TO ADDINADCIN – COM$ |                         |            | 30    |                  | MHz                |  |

(1) Ideal input span; does not include gain or offset error.

(2) LSB means least significant bit.

(3) Measured relative to an ideal full-scale input ( $IN_X - COM$ ) of 2.5 V when VA = 2.7 V.

(4) Calculated on the first nine harmonics of the input frequency.

# Electrical Characteristics: VA = 2.7 V (continued)

at  $T_A = -40^{\circ}$ C to 85°C, VA = 2.7 V, VBD = 1.65 V to 2.7 V,  $V_{REF} = 2.5$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

|                  | PARAMETER                         |                        | TEST CONDITIONS                                                       | MIN        | TYP          | MAX        | UNIT       |

|------------------|-----------------------------------|------------------------|-----------------------------------------------------------------------|------------|--------------|------------|------------|

| CLOCK            |                                   |                        |                                                                       |            |              | ·          |            |

|                  | Internal conver<br>frequency      | rsion clock            |                                                                       | 10.5       | 11           | 12.2       | MHz        |

|                  |                                   |                        | Used as I/O clock only                                                |            |              | 25         | MHz        |

|                  | SCLK external                     | Serial Clock           | Used as both I/O clock and conversion clock                           | 1          |              | 21         | MHz        |

| EXTERN           | AL VOLTAGE R                      | EFERENCE INPUT         |                                                                       |            |              |            |            |

|                  | Input                             |                        |                                                                       | 1.2        |              | 2.525      |            |

| V <sub>REF</sub> | reference<br>range <sup>(5)</sup> | (REF–) – AGND          |                                                                       | -0.1       |              | 0.1        | V          |

|                  | Resistance (6)                    |                        | Reference input                                                       |            | 20           |            | kΩ         |

| DIGITAL          | INPUT/OUTPUT                      | •                      |                                                                       |            |              |            |            |

|                  | Logic family                      |                        |                                                                       |            | CMOS         |            |            |

|                  |                                   |                        | 1.65 V < VBD < 2.5 V                                                  | 0.8 × VBD  |              | VBD + 0.3  |            |

| V <sub>IH</sub>  | High-level inpu                   | it voltage             | $2.5 V \le VBD \le VA$                                                | 0.65 × VBD |              | VBD + 0.3  | V          |

|                  |                                   |                        | 1.65 < VBD < 2.5 V                                                    | -0.3       |              | 0.1 × VBD  |            |

| V <sub>IL</sub>  | Low-level inpu                    | t voltage              | $2.5 V \le VBD \le VA$                                                | -0.3       |              | 0.25 × VBD | V          |

| l <sub>l</sub>   | Input current                     |                        | V <sub>IN</sub> = VBD or DGND                                         | -1         |              | 1          | μA         |

| Cı               | Input capacitar                   | nce                    |                                                                       |            | 5            |            | pF         |

| V <sub>OH</sub>  | High-level outp                   | out voltage            | $VA \ge VBD \ge 1.65V$ , $I_0 = 100 \ \mu A$                          | VBD - 0.6  |              | VBD        | V          |

| V <sub>OL</sub>  | Low-level outp                    | ut voltage             | $VA \ge VBD \ge 1.65 \text{ V}, \text{ I}_{O} = -100 \mu\text{A}$     | 0          |              | 0.4        | V          |

| Co               | SDO pin capa                      | citance                | Hi-Z state                                                            |            | 5            |            | pF         |

| CL               | Load capacitar                    | nce                    |                                                                       |            |              | 30         | pF         |

|                  | Data format                       |                        |                                                                       | Stra       | aight binary | ,          |            |

| POWER-           | SUPPLY REQU                       | REMENTS                |                                                                       |            |              | ·          |            |

| VA               | Analog supply                     | voltage <sup>(5)</sup> |                                                                       | 2.7        |              | 3.6        | V          |

| VBD              | Digital I/O sup                   | ply voltage            |                                                                       | 1.65       |              | VA + 0.2   | V          |

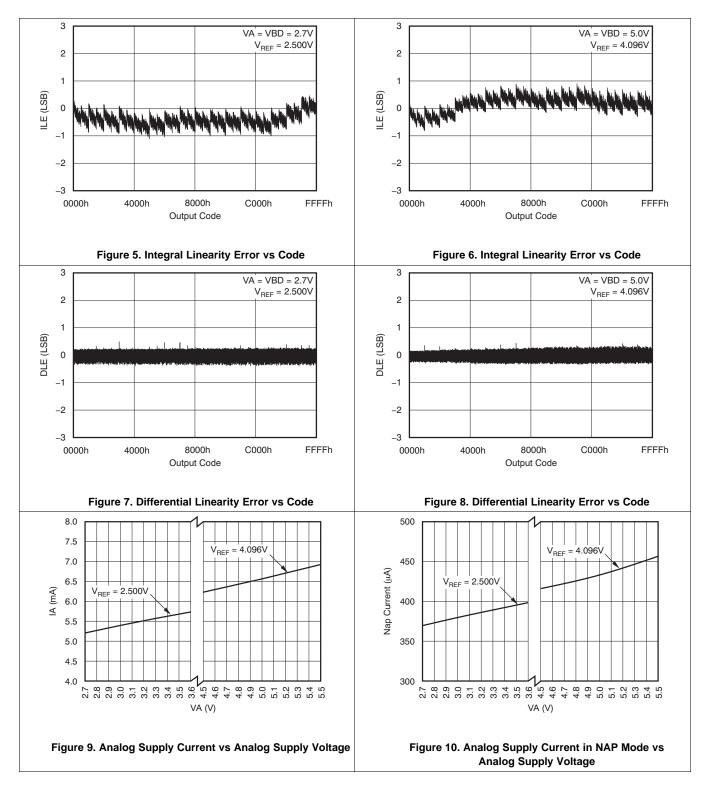

|                  |                                   |                        | f <sub>SAMPLE</sub> = 500 kSPS                                        |            | 5.2          | 6.5        |            |

| 1.0              |                                   | ourropt                | f <sub>SAMPLE</sub> = 250 kSPS in Auto-NAP mode                       |            | 3.2          |            | mA         |

| IA               | Analog supply                     | current                | Nap mode, SCLK = VBD or DGND                                          |            | 325          | 400        | μA         |

|                  |                                   |                        | Deep PD mode, SCLK = VBD or DGND                                      |            | 50           | 250        | nA         |

| חסו              | Digital I/O aug                   | alv aurrant            | f <sub>SAMPLE</sub> = 500 kilobytes per second                        |            | 0.1          | 0.4        | <b>س</b> ۸ |

| IBD              | Digital I/O supply current        |                        | f <sub>SAMPLE</sub> = 250 kSPS in Auto-NAP mode                       |            | 0.05         |            | mA         |

|                  | Power dissipation                 |                        | VA = 2.7 V, VBD = 1.65 V, f <sub>SAMPLE</sub> = 500 kSPS              |            | 14.2         | 18.2       |            |

|                  |                                   |                        | VA = 2.7V, VBD = 1.65 V, $\rm f_{SAMPLE}$ = 250 kSPS in Auto-NAP mode |            | 8.72         |            | mW         |

| TEMPER           | ATURE RANGE                       |                        |                                                                       |            |              |            |            |

| T <sub>A</sub>   | Operating free                    | -air temperature       |                                                                       | -40        |              | 85         | °C         |

(5) The ADS8331, ADS8332 operates with VA from 2.7 V to 5.5 V, and V<sub>REF</sub> between 1.2 V and VA. However, the device may not meet the specifications listed in the *Electrical Characteristics* when VA is from 3.6 V to 4.5 V.

(6) Can vary ±30%.

## 8.6 Electrical Characteristics: VA = 5 V

at  $T_A = -40^{\circ}$ C to 85°C, VA = 5 V, VBD = 1.65 V to 5 V,  $V_{REF} = 4.096$  V, and  $f_{SAMPLE} = 500$  kSPS (unless otherwise noted)

|                      | PARAMETER                                | TEST CO                                    | NDITIONS                              | MIN        | TYP   | MAX              | UNIT               |

|----------------------|------------------------------------------|--------------------------------------------|---------------------------------------|------------|-------|------------------|--------------------|

| ANALOG II            | NPUT                                     |                                            |                                       |            |       |                  |                    |

|                      | Full-scale input voltage (1)             | IN <sub>X</sub> – COM, ADCIN               | I – COM                               | 0          |       | V <sub>REF</sub> | V                  |

|                      | Abaaluta incut valtage                   | IN <sub>X</sub> , ADCIN                    |                                       | AGND - 0.2 |       | VA + 0.2         | V                  |

|                      | Absolute input voltage                   | СОМ                                        | СОМ                                   |            |       | AGND + 0.2       | v                  |

|                      | Input capacitance                        | ADCIN                                      |                                       |            | 40    | 45               | pF                 |

|                      | Input leakage current                    | Unselected ADC in                          | put                                   |            | ±1    |                  | nA                 |

| SYSTEM P             | ERFORMANCE                               |                                            |                                       |            |       |                  |                    |

|                      | Resolution                               |                                            |                                       |            | 16    |                  | Bits               |

|                      | No missing codes                         |                                            |                                       | 16         |       |                  | Bits               |

| INL                  | Integral linearity                       | ADS8331I, ADS833                           | 321                                   | -3         | ±2    | 3                | LSB <sup>(2)</sup> |

|                      | mograi moanty                            | ADS8331IB, ADS8                            | 332IB                                 | -2         | ±1    | 2                | LOD                |

| DNL                  | Differential linearity                   | ADS8331I, ADS833                           | 321                                   | -1         | ±1    | 2                | LSB <sup>(2)</sup> |

| DITE                 | -                                        | ADS8331IB, ADS8                            | 332IB                                 | -1         | ±0.5  | 1.5              | LOD                |

| Eo                   | Offset error <sup>(3)</sup>              |                                            |                                       | -1         | ±0.23 | 1                | mV                 |

|                      | Offset error drift                       |                                            |                                       |            | ±1    |                  | PPM/°C             |

|                      | Offset error matching                    |                                            |                                       | -0.125     |       | 0.125            | mV                 |

| E <sub>G</sub>       | Gain error                               |                                            |                                       | -0.25      | -0.06 | 0.25             | %FSR               |

|                      | Gain error drift                         |                                            |                                       |            | ±0.02 |                  | PPM/°C             |

|                      | Gain error matching                      |                                            |                                       | -0.003     |       | 0.003            | %FSR               |

|                      | Transition noise                         |                                            |                                       |            | 30    |                  | μV RMS             |

| PSRR                 | Power-supply rejection ratio             |                                            |                                       |            | 78    |                  | dB                 |

| SAMPLING             | DYNAMICS                                 |                                            |                                       |            |       |                  |                    |

| t <sub>CONV</sub>    | Conversion time                          |                                            |                                       |            | 18    |                  | CCLK               |

| t <sub>SAMPLE1</sub> | Acquisition time                         | Manual-trigger mod                         | Manual-trigger mode Auto-trigger mode |            | 3     |                  | CCLK               |

| t <sub>SAMPLE2</sub> |                                          | Auto-trigger mode                          |                                       |            | 3     |                  |                    |

|                      | Throughput rate                          |                                            |                                       |            |       | 500              | kSPS               |

| DYNAMIC              | CHARACTERISTICS                          |                                            |                                       |            |       |                  |                    |

|                      |                                          | $V_{IN}$ = 4.096 $V_{PP}$ at               | 1 kHz                                 |            | -100  |                  |                    |

| THD                  | Total harmonic distortion <sup>(4)</sup> | V <sub>IN</sub> = 4.096 V <sub>PP</sub> at | ADS8331I,<br>ADS8332I                 |            | -94   |                  | dB                 |

|                      |                                          | 10 kHz                                     | ADS8331IB,<br>ADS8332IB               |            | -95   |                  |                    |

|                      |                                          | V <sub>IN</sub> = 4.096 V <sub>PP</sub> at | ADS8331I,<br>ADS8332I                 |            | 90.5  |                  |                    |

| SNR                  | Signal-to-noise ratio                    | 1 kHz                                      | ADS8331IB,<br>ADS8332IB               |            | 91.5  |                  | dB                 |

|                      |                                          | $V_{IN} = 4.096 V_{PP}$ at                 | 10 kHz                                |            | 88    |                  |                    |

|                      |                                          | V <sub>IN</sub> = 4.096 V <sub>PP</sub> at | ADS8331I,<br>ADS8332I                 |            | 90    |                  |                    |

| SINAD                | Signal-to-noise + distortion             | 1 kHz                                      | ADS8331IB,<br>ADS8332IB               |            | 91    |                  | dB                 |

|                      |                                          | $V_{IN} = 4.096 V_{PP}$ at                 | 10 kHz                                |            | 87    |                  |                    |

|                      | Pourious free duramis range              | $V_{IN}$ = 4.096 $V_{PP}$ at               | 1 kHz                                 |            | 101   |                  | d٦                 |

| SFDR                 | Spurious-free dynamic range              | $V_{IN} = 4.096 V_{PP}$ at                 | 10 kHz                                |            | 96    |                  | dB                 |

|                      | Greentelly                               | $V_{IN} = 4.096 V_{PP}$ at                 | 1 kHz                                 |            | 119   |                  | -ID                |

|                      | Crosstalk                                | $V_{IN} = 4.096 V_{PP}$ at                 | 100 kHz                               |            | 107   |                  | dB                 |

|                      | –3-dB small-signal bandwidth             | IN <sub>X</sub> – COM with MU<br>ADCIN     | JXOUT tied to                         |            | 22    |                  | MHz                |

|                      |                                          | ADCIN - COM                                | ADCIN – COM                           |            | 40    |                  |                    |

Ideal input span; does not include gain or offset error. LSB means least significant bit. (1)

(2)

Measured relative to an ideal full-scale input ( $IN_X - COM$ ) of 4.096 V when VA = 5 V. Calculated on the first nine harmonics of the input frequency. (3)

(4)

Copyright © 2009–2016, Texas Instruments Incorporated

## Electrical Characteristics: VA = 5 V (continued)

at  $T_A = -40^{\circ}$ C to 85°C, VA = 5 V, VBD = 1.65 V to 5 V, V<sub>REF</sub> = 4.096 V, and  $f_{SAMPLE}$  = 500 kSPS (unless otherwise noted)

|                 | PARAMETER               |                | TEST CONDITIONS                                                         | MIN        | TYP          | MAX        | UNIT |  |

|-----------------|-------------------------|----------------|-------------------------------------------------------------------------|------------|--------------|------------|------|--|

| CLOCK           |                         |                |                                                                         |            |              |            |      |  |

|                 | Internal conversion c   | lock frequency |                                                                         | 10.9       | 11.5         | 12.6       | MHz  |  |

|                 |                         |                | Used as I/O clock only                                                  |            |              | 40         |      |  |

|                 | SCLK external serial    | clock          | Used as both I/O clock and conversion<br>clock                          | 1          |              | 21         | MHz  |  |

| EXTERN          | AL VOLTAGE REFEREN      | CE INPUT       |                                                                         |            |              |            |      |  |

|                 | Input reference (F      | REF+) – (REF–) |                                                                         | 1.2        | 4.096        | 4.2        | V    |  |

| $V_{REF}$       | . (5)                   | REF–) – AGND   |                                                                         | -0.1       |              | 0.1        | V    |  |

|                 | Resistance (6)          |                | Reference input                                                         |            | 20           |            | kΩ   |  |

| DIGITAL         | INPUT/OUTPUT            |                |                                                                         |            |              |            |      |  |

|                 | Logic family            |                |                                                                         |            | CMOS         |            |      |  |

|                 |                         |                | 1.65 < VBD < 2.5 V                                                      | 0.8 × VBD  |              | VBD + 0.3  |      |  |

| VIH             | High-level input volta  | ge             | $2.5 V \le VBD \le VA$                                                  | 0.65 × VBD |              | VBD + 0.3  | V    |  |

|                 |                         |                | 1.65 < VBD < 2.5 V                                                      | -0.3       |              | 0.1 × VBD  |      |  |

| V <sub>IL</sub> | Low-level input voltage | ge             | $2.5 V \le VBD \le VA$                                                  | -0.3       |              | 0.25 × VBD | V    |  |

| I <sub>I</sub>  | Input current           |                | V <sub>IN</sub> = VBD or DGND                                           | -1         |              | 1          | μA   |  |

| CI              | Input capacitance       |                |                                                                         |            | 5            |            | pF   |  |

| V <sub>OH</sub> | High-level output volt  | age            | VA ≥ VBD ≥ 1.65 V, I <sub>O</sub> = 100 μA                              | VBD - 0.6  |              | VBD        | V    |  |

| V <sub>OL</sub> | Low-level output volt   | age            | $VA \ge VBD \ge 1.65 V$ , $I_O = -100 \mu A$                            | 0          |              | 0.4        | V    |  |

| Co              | SDO pin capacitance     |                | Hi-Z state                                                              |            | 5            |            | pF   |  |

| CL              | Load capacitance        |                |                                                                         |            |              | 30         | pF   |  |

| -               | Data format             |                |                                                                         | Str        | aight binary |            |      |  |

| POWER-          | SUPPLY REQUIREMENT      | S              |                                                                         |            | 0 ,          |            |      |  |

| VA              | Analog supply voltag    |                |                                                                         | 4.5        | 5            | 5.5        | V    |  |

| VBD             | Digital I/O supply vol  |                |                                                                         | 1.65       |              | VA + 0.2   | V    |  |

|                 |                         | 0              | f <sub>SAMPLE</sub> = 500 kSPS                                          |            | 6.6          | 7.75       |      |  |

|                 |                         |                | f <sub>SAMPLE</sub> = 250 kSPS in Auto-NAP mode                         |            | 4.2          |            | mA   |  |

| IA              | Analog supply currer    | nt             | Nap mode, SCLK = VBD or DGND                                            |            | 390          | 500        | μA   |  |

|                 |                         |                | Deep PD mode, SCLK = VBD or<br>DGND                                     |            |              | 250        | nA   |  |

|                 |                         |                | f <sub>SAMPLE</sub> = 500 kSPS                                          | 1.2        |              | 2          |      |  |

| IBD             | Digital I/O supply cur  | rent           | f <sub>SAMPLE</sub> = 250 kSPS in Auto-NAP mode                         |            | 0.7          |            | mA   |  |

|                 |                         |                | VA = 5 V, VBD = 5 V, f <sub>SAMPLE</sub> = 500<br>kSPS                  |            | 39           | 48.75      |      |  |

|                 | Power dissipation       |                | VA = 5 V, VBD = 5 V, f <sub>SAMPLE</sub> = 250<br>kSPS in Auto-NAP mode | 24.5       |              |            | mW   |  |

| TEMPER          | ATURE RANGE             |                |                                                                         |            |              |            |      |  |

| T <sub>A</sub>  | Operating free-air ter  | nperature      |                                                                         | -40        |              | 85         | °C   |  |

(5) The ADS8331, ADS8332 operates with VA from 2.7 V to 5.5 V, and V<sub>REF</sub> between 1.2 V and VA. However, the device may not meet the specifications listed in the *Electrical Characteristics* when VA is from 3.6 V to 4.5 V.

(6) Can vary ±30%.

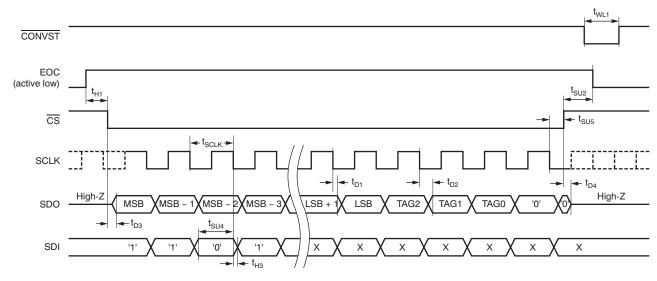

## 8.7 Timing Requirements: VA = 2.7 V

at  $T_A = -40^{\circ}$ C to 85°C, VA = 2.7 V, and VBD = 1.65 V (unless otherwise noted)<sup>(1)(2)</sup>

|                     |                                                                                    |                                                     | MIN  | NOM | MAX                  | UNIT |

|---------------------|------------------------------------------------------------------------------------|-----------------------------------------------------|------|-----|----------------------|------|

| £                   |                                                                                    | External, f <sub>CCLK</sub> = 1/2 f <sub>SCLK</sub> | 0.5  |     | 10.5                 |      |

| f <sub>CCLK</sub>   | Frequency, conversion clock, CCLK                                                  | Internal                                            | 10.5 | 11  | 12.2                 | MHz  |

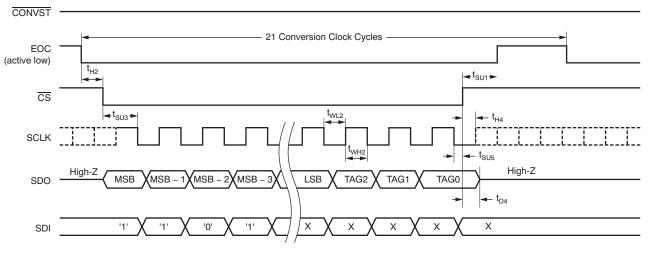

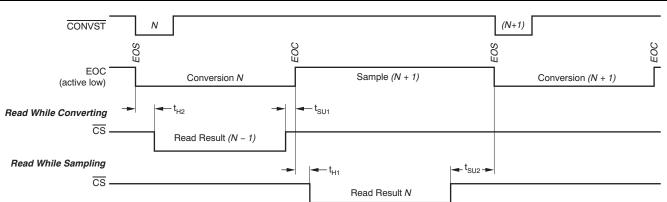

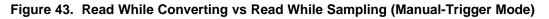

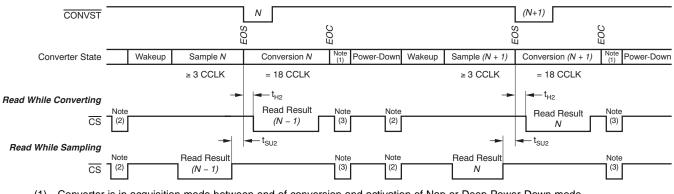

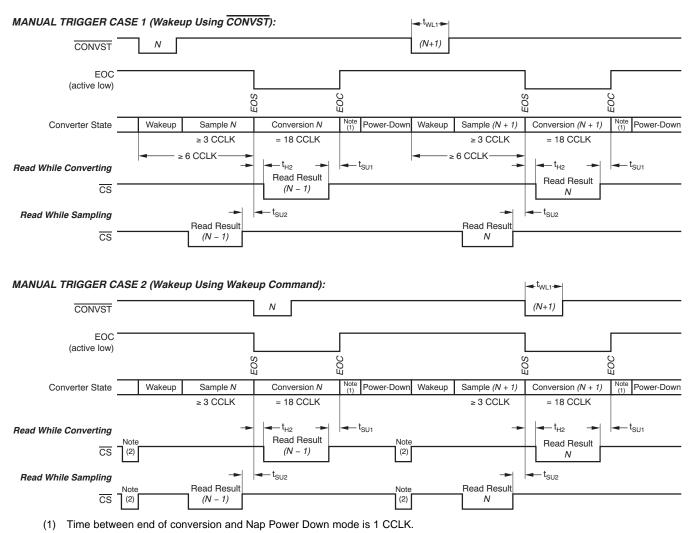

| t <sub>SU1</sub>    | Setup time, rising edge of $\overline{\text{CS}}$ to EOC <sup>(3)</sup>            | Read while converting                               | 1    |     |                      | CCLK |

| t <sub>H1</sub>     | CS hold time with respect to EOC <sup>(3)</sup>                                    | Read while sampling                                 | 25   |     |                      | ns   |

| t <sub>WL1</sub>    | Pulse duration, CONVST low                                                         |                                                     | 40   |     |                      | ns   |

| t <sub>WH1</sub>    | Pulse duration, CS high                                                            |                                                     | 40   |     |                      | ns   |

| t <sub>SU2</sub>    | Setup time, rising edge of $\overline{CS}$ to EOS                                  | Read while sampling                                 | 25   |     |                      | ns   |

| t <sub>H2</sub>     | CS hold time with respect to EOS                                                   | Read while converting                               | 25   |     |                      | ns   |

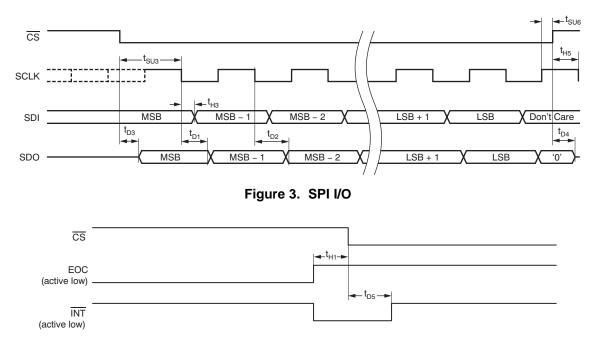

| t <sub>SU3</sub>    | Setup time, falling edge of $\overline{CS}$ to first falling edge of SCLK          |                                                     | 14   |     |                      | ns   |

| t <sub>WL2</sub>    | Pulse duration, SCLK low                                                           |                                                     | 17   |     | $t_{SCLK} - t_{WH2}$ | ns   |

| t <sub>WH2</sub>    | Pulse duration, SCLK high                                                          |                                                     | 12   |     | $t_{SCLK} - t_{WL2}$ | ns   |

|                     | Cycle time, SCLK                                                                   | I/O clock only                                      | 40   |     |                      |      |

|                     |                                                                                    | I/O and conversion clocks                           | 47.6 |     | 1000                 |      |

| t <sub>SCLK</sub>   |                                                                                    | I/O clock, daisy-chain mode                         | 40   |     |                      | ns   |

|                     |                                                                                    | I/O and conversion clocks, daisy-chain mode         | 47.6 |     | 1000                 |      |

| t <sub>D1</sub>     | Delay time, falling edge of SCLK to SDO invalid                                    | 10-pF load                                          | 8    |     |                      | ns   |

| t <sub>D2</sub>     | Delay time, falling edge of SCLK to SDO valid                                      | 10-pF load                                          |      |     | 35                   | ns   |

| t <sub>D3</sub>     | Delay time, falling edge of $\overline{\text{CS}}$ to SDO valid, SDO MSB output    | 10-pF load                                          |      |     | 35                   | ns   |

| t <sub>SU4</sub>    | Setup time, SDI to falling edge of SCLK                                            |                                                     | 8    |     |                      | ns   |

| t <sub>H3</sub>     | Hold time, SDI to falling edge of SCLK                                             |                                                     | 8    |     |                      | ns   |

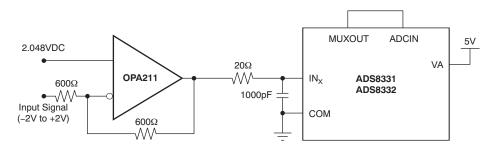

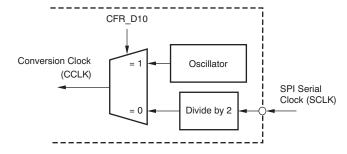

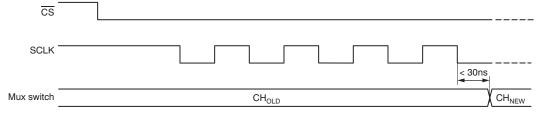

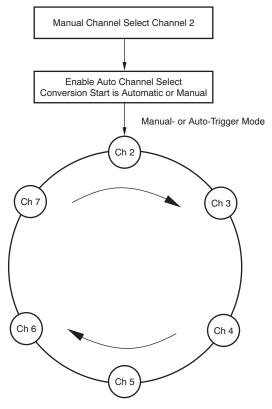

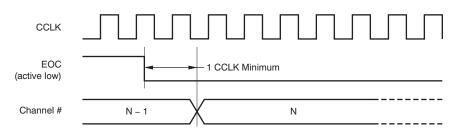

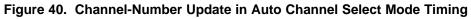

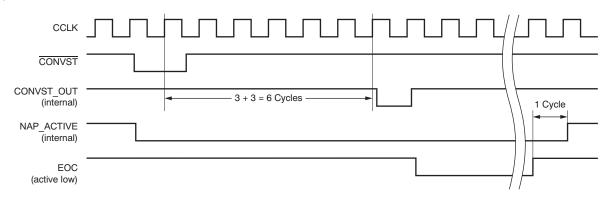

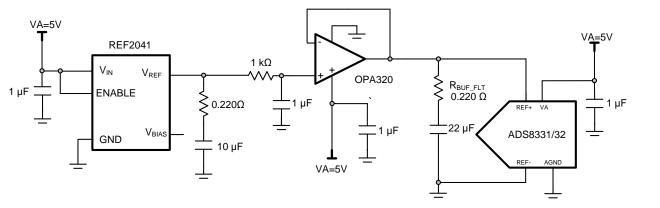

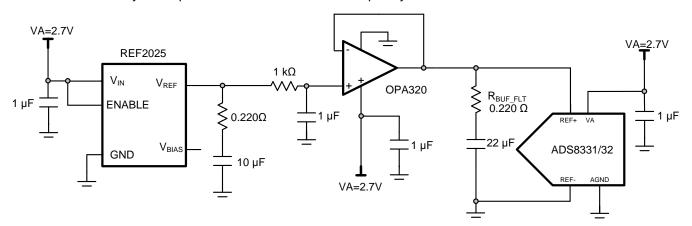

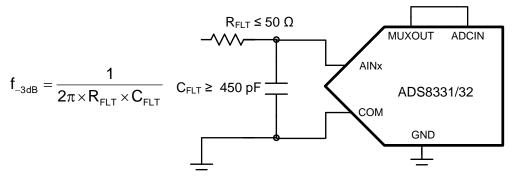

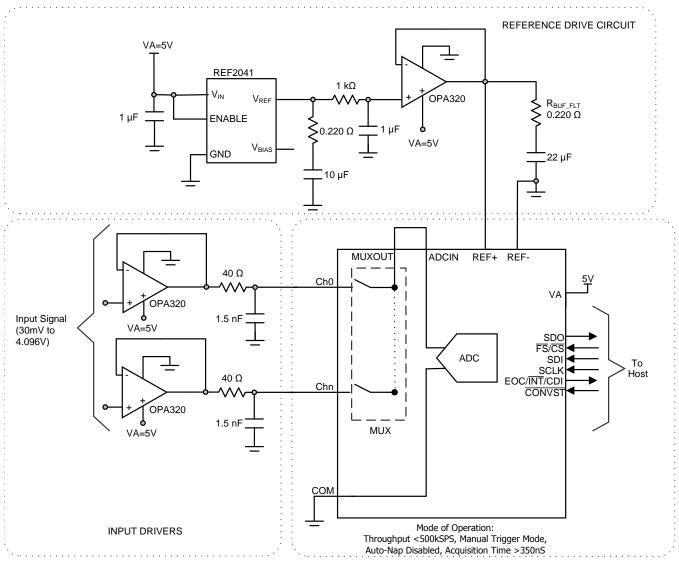

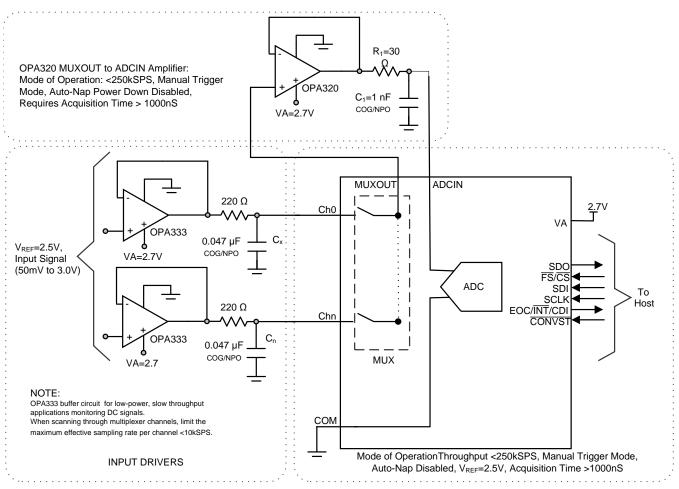

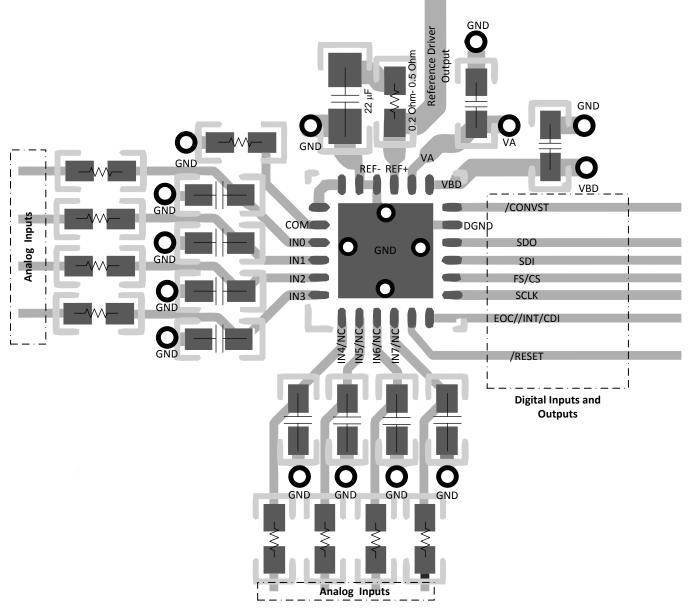

| t <sub>D4</sub>     | Delay time, rising edge of $\overline{CS}$ to SDO 3-state                          | 10-pF load                                          |      |     | 15                   | ns   |