# Octal, 14-Bit, Low-Power, High-Voltage Output, Serial Input DIGITAL-TO-ANALOG CONVERTER

Check for Samples: DAC8218

## FEATURES

www.ti.com

- Bipolar Output: ±2V to ±16.5V

- Unipolar Output: 0V to +33V

- 14-Bit Resolution

- Low Power: 14.4mW/Ch (Bipolar Supply)

- Relative Accuracy: 1 LSB Max

- Low Zero/Full-Scale Error

- Before User Calibration: ±2.5 LSB Max

- After User Calibration: ±1 LSB

- Flexible System Calibration

- Low Glitch: 4nV-s

- Settling Time: 15µs

- Channel Monitor Output

- Programmable Gain: x4/x6

- Programmable Offset

- SPI™: Up to 50MHz, 1.8V/3V/5V Logic

- Schmitt Trigger Inputs

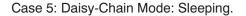

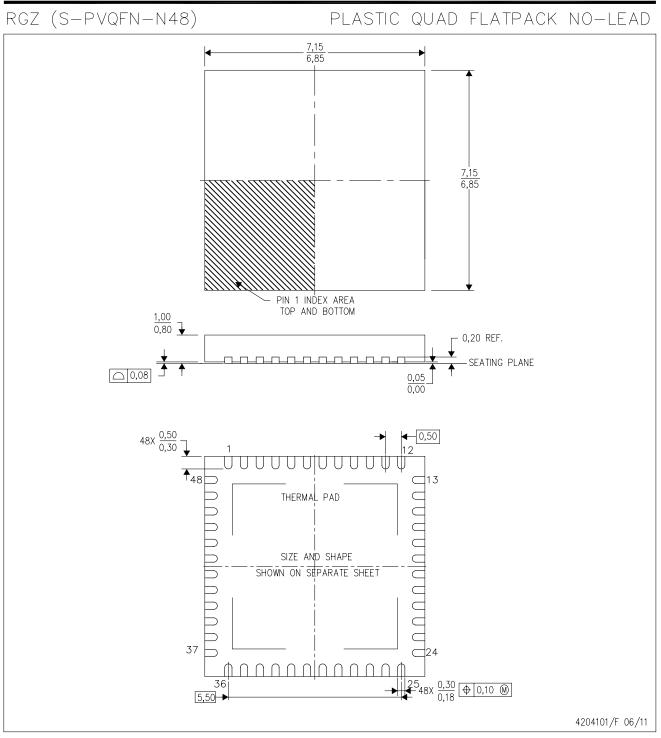

- Daisy-Chain with Sleep Mode Enhancement

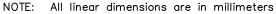

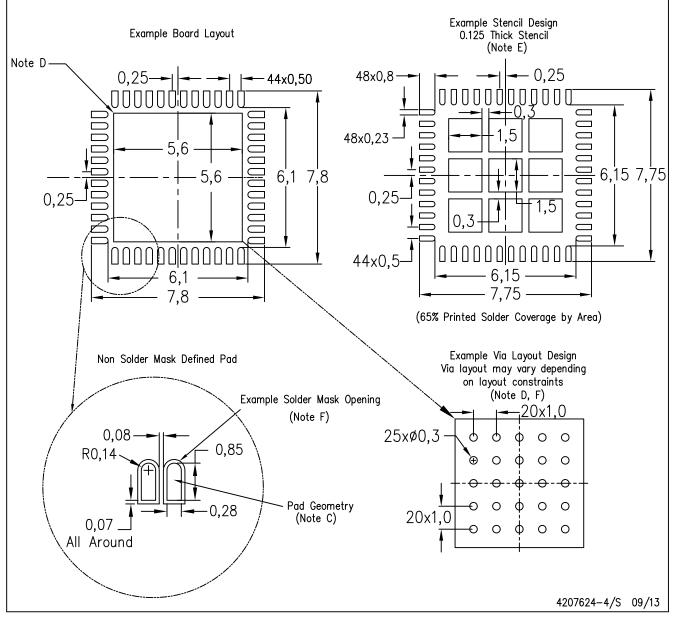

- Packages: QFN-48 (7x7mm), TQFP-64 (10x10mm)

## **APPLICATIONS**

- Automatic Test Equipment

- PLC and Industrial Process Control

- Communications

## DESCRIPTION

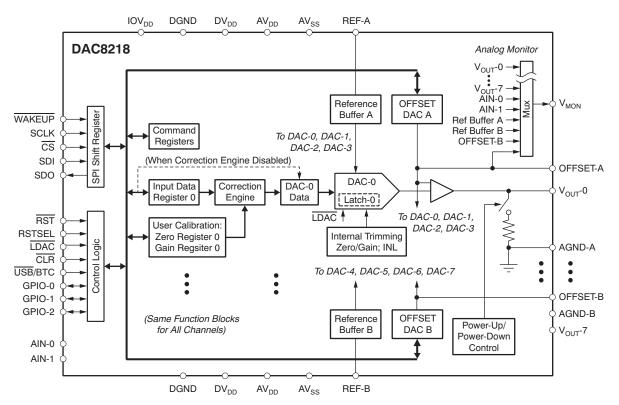

The DAC8218 is a low-power, octal, 14-bit digital-to-analog converter (DAC). With a 5V reference, the output can either be a bipolar ±15V voltage when operating from dual ±15.5V (or higher) power supplies, or a unipolar 0V to +30V voltage when operating from a +30.5V (or higher) power supply. With a 5.5V reference, the output can either be a bipolar ±16.5V voltage when operating from dual ±17V (or higher) power supplies, or a unipolar 0V to +33V voltage when operating from a +33.5V (or higher) power supply. This DAC provides low-power operation, good linearity, and low glitch over the specified temperature range of -40°C to +105°C. This device is trimmed in manufacturing and has very low zero-code and gain error. In addition, system level calibration can be performed to achieve ±1 LSB bipolar zero/full-scale error with bipolar supplies, or ±1 LSB zero code/full-scale error with a unipolar supply, over the entire signal chain. The output range can be offset by using the DAC offset register.

The DAC8218 features a standard, high-speed serial peripheral interface (SPI) that operates at up to 50MHz and is 1.8V, 3V, and 5V logic compatible, to communicate with a DSP or microprocessor. The input data of the device are double-buffered. An asynchronous load input (LDAC) transfers data from the DAC data register to the DAC latch. The asynchronous CLR input sets the output of all eight DACs to AGND. The V<sub>MON</sub> pin is a monitor output that connects to the individual analog outputs, the offset DAC, the reference buffer outputs, and two external inputs through a multiplexer (mux).

The DAC8218 is pin-to-pin and function-compatible with the DAC8718 (16-bit) and the DAC7718 (12-bit).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

DSP is a trademark of Texas Instruments. SPI, QSPI are trademarks of Motorola Inc. Microwire is a trademark of National Semiconductor. All other trademarks are the property of their respective owners.

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

|         |                               | ONDE                               |                  |                       |                                   |                    |

|---------|-------------------------------|------------------------------------|------------------|-----------------------|-----------------------------------|--------------------|

| PRODUCT | RELATIVE<br>ACCURACY<br>(LSB) | DIFFERENTIAL<br>LINEARITY<br>(LSB) | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING |

| DAC8218 | ±1                            | ±1                                 | QFN-48           | RGZ                   | –40°C to +105°C                   | DAC8218            |

| DAC6216 | ±1                            | ±1                                 | TQFP-64          | PAG                   | -40°C to +105°C                   | DAC8218            |

### **ORDERING INFORMATION**<sup>(1)</sup>

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this data sheet, or see the TI web site at www.ti.com.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted).

|                                                                   |                                    |      | DAC8218                                      | UNIT |

|-------------------------------------------------------------------|------------------------------------|------|----------------------------------------------|------|

| AV <sub>DD</sub> to AV <sub>SS</sub>                              |                                    |      | -0.3 to 38                                   | V    |

| AV <sub>DD</sub> to AGND                                          |                                    |      | -0.3 to 38                                   | V    |

| AV <sub>SS</sub> to AGND, DGND                                    |                                    |      | -19 to 0.3                                   | V    |

| DV <sub>DD</sub> to DGND                                          |                                    |      | -0.3 to 6                                    | V    |

| IOV <sub>DD</sub> to DGND                                         |                                    |      | -0.3 to min of (6 or DV <sub>DD</sub> + 0.3) | V    |

| AGND-x to DGND                                                    |                                    |      | -0.3 to 0.3                                  | V    |

| Digital input voltage to D                                        | GND                                |      | -0.3 to IOV <sub>DD</sub> + 0.3              | V    |

| SDO to DGND                                                       |                                    |      | -0.3 to IOV <sub>DD</sub> + 0.3              | V    |

| V <sub>OUT</sub> -x, V <sub>MON</sub> , AIN-x to AV <sub>SS</sub> |                                    |      | –0.3 to AV <sub>DD</sub> + 0.3               | V    |

| REF-A, REF-B to AGND                                              |                                    |      | –0.3 to DV <sub>DD</sub>                     | V    |

| GPIO-n to DGND                                                    |                                    |      | –0.3 to IOV <sub>DD</sub> + 0.3              | V    |

| GPIO-n input current                                              |                                    |      | 5                                            | mA   |

| Maximum current from V                                            | MON                                |      | 3                                            | mA   |

| Operating temperature ra                                          | nge                                |      | -40 to +105                                  | °C   |

| Storage temperature rang                                          | ge                                 |      | -65 to +150                                  | °C   |

| Maximum junction tempe                                            | rature (T <sub>J</sub> max)        |      | +150                                         | °C   |

|                                                                   | Human body model (HBM)             |      | 2.5                                          | kV   |

| ESD ratings                                                       | Charged device model (CDM          | 1)   | 1000                                         | V    |

|                                                                   | Machine model (MM)                 |      | 200                                          | V    |

|                                                                   | Junction-to-ambient, $\theta_{JA}$ | TQFP | 55                                           | °C/W |

| Thermal impedance                                                 |                                    | QFN  | 27.5                                         | °C/W |

| mennar impedance                                                  | Junction-to-case, θ <sub>ιC</sub>  | TQFP | 21                                           | °C/W |

|                                                                   |                                    | QFN  | 10.8                                         | °C/W |

| Power dissipation                                                 |                                    |      | $(T_J max - T_A) / \theta_{JA}$              | W    |

(1) Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

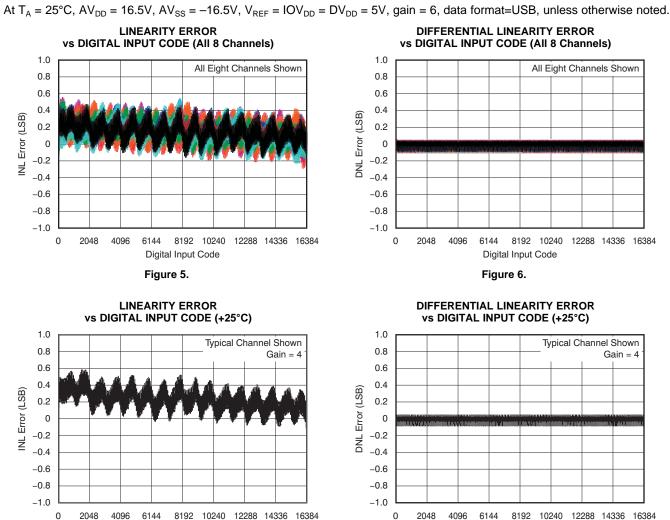

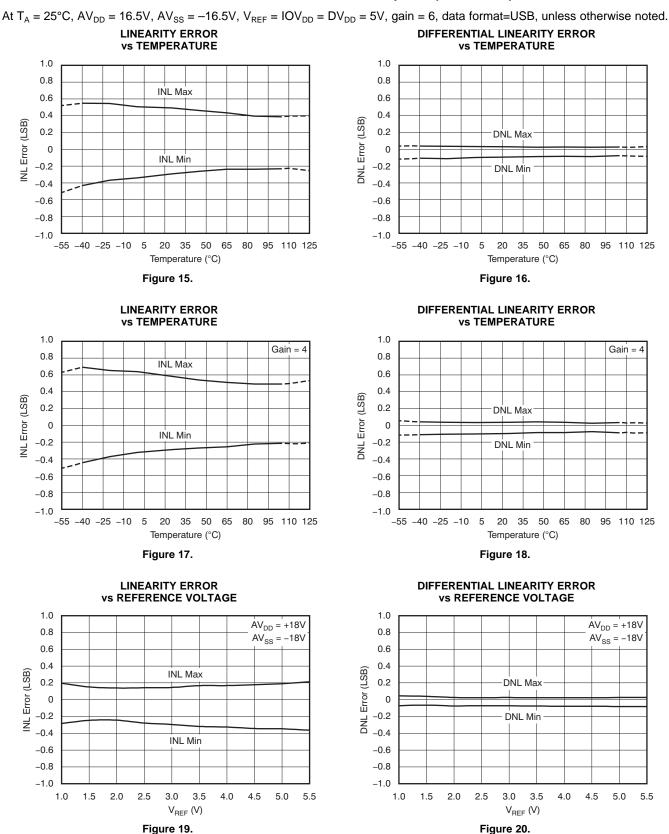

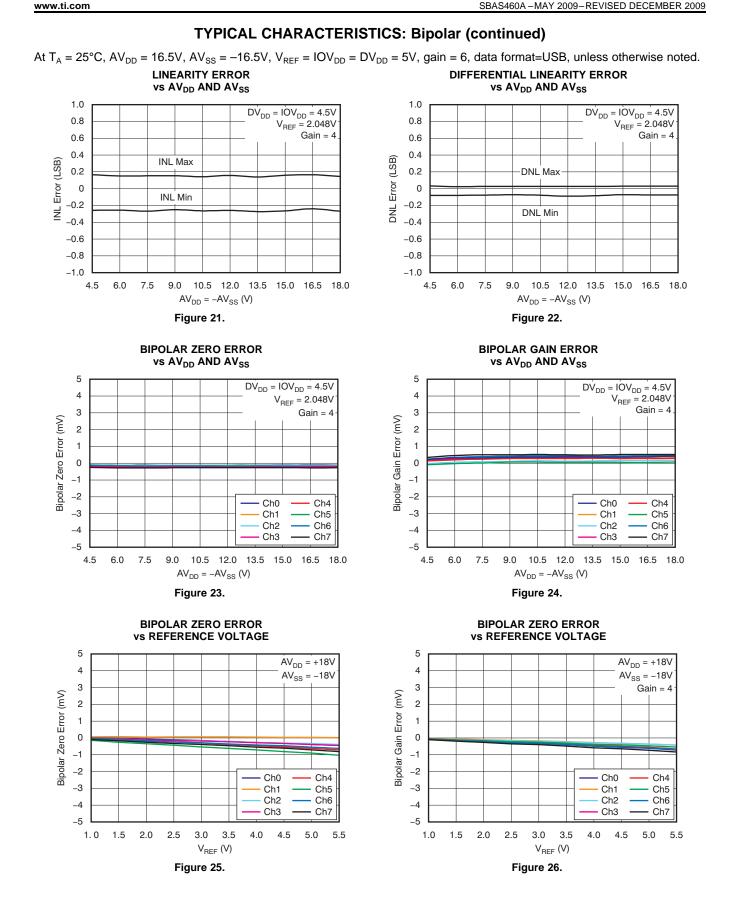

## ELECTRICAL CHARACTERISTICS: Dual-Supply

All specifications at  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = +16.5V$ ,  $AV_{SS} = -16.5V$ ,  $IOV_{DD} = DV_{DD} = +5V$ , REF-A and REF-B = +5V, gain = 6, AGND-x = DGND = 0V, data format = straight binary, and Offset DAC A and Offset DAC B are at default values<sup>(1)</sup>, unless otherwise noted.

|                                   |                                                                          | D   |      |      |            |

|-----------------------------------|--------------------------------------------------------------------------|-----|------|------|------------|

| PARAMETER                         | CONDITIONS                                                               | MIN | TYP  | MAX  | UNIT       |

| STATIC PERFORMANCE <sup>(2)</sup> | · · · ·                                                                  |     |      |      |            |

| Resolution                        |                                                                          | 14  |      |      | Bits       |

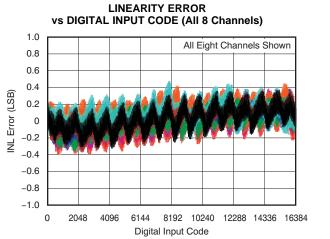

| Linearity error                   | Measured by line passing through codes 0000h and 3FFFh                   |     |      | ±1   | LSB        |

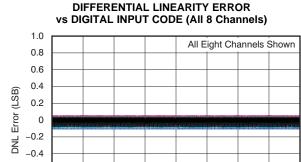

| Differential linearity error      | Measured by line passing through codes 0000h and 3FFFh                   |     |      | ±1   | LSB        |

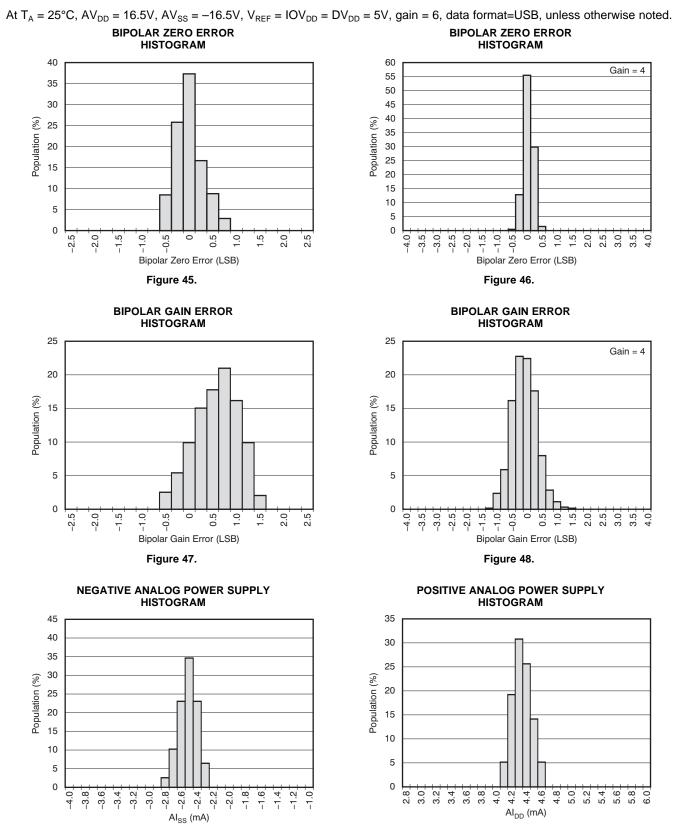

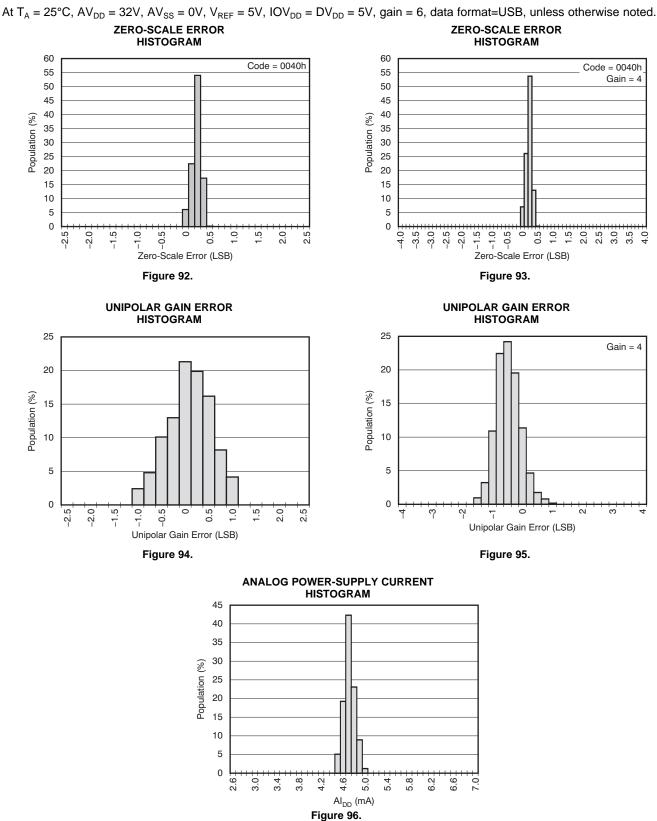

|                                   | $T_A = +25^{\circ}C$ , before user calibration, gain = 6, code = 2000h   |     |      | ±2.5 | LSB        |

| Bipolar zero error                | $T_A = +25^{\circ}C$ , before user calibration, gain = 4, code = 2000h   |     |      | ±4   | LSB        |

|                                   | $T_A = +25^{\circ}C$ , after user calib., gain = 4 or 6, code = 2000h    |     | ±1   |      | LSB        |

| Bipolar zero error TC             | Gain = 4 or 6, code = 2000h                                              |     | ±0.5 | ±2   | ppm FSR/°C |

| Zero-code error                   | $T_A = +25^{\circ}C$ , gain = 6, code = 0000h                            |     |      | ±2.5 | LSB        |

| Zero-code error                   | $T_A = +25^{\circ}C$ , gain = 4, code = 0000h                            |     |      | ±4   | LSB        |

| Zero-code error TC                | Gain = 4 or 6, code = 0000h                                              |     | ±0.5 | ±3   | ppm FSR/°C |

| Online annua                      | $T_{A} = +25^{\circ}C, \text{ gain} = 6$                                 |     |      | ±2.5 | LSB        |

| Gain error                        | $T_{A} = +25^{\circ}C$ , gain = 4                                        |     |      | ±4   | LSB        |

| Gain error TC                     | Gain = 4 or 6                                                            |     | ±1   | ±3   | ppm FSR/°C |

|                                   | $T_A = +25^{\circ}C$ , before user calibration, gain = 6, code = 3FFFh   |     |      | ±2.5 | LSB        |

| Full-scale error                  | $T_A = +25^{\circ}C$ , before user calibration, gain = 4, code = 3FFFh   |     |      | ±4   | LSB        |

|                                   | $T_A = +25^{\circ}C$ , after user calib., gain = 4 or 6, code = 3FFFh    |     | ±1   |      | LSB        |

| Full-scale error TC               | Gain = 4 or 6, code = 3FFFh                                              |     | ±0.5 | ±3   | ppm FSR/°C |

| DC crosstalk <sup>(3)</sup>       | Measured channel at code = 2000h, full-scale change on any other channel |     | 0.05 |      | LSB        |

(1) Offset DAC A and Offset DAC B are trimmed in manufacturing to minimize the error for symmetrical output. The default value may vary no more than ±3 LSB from the nominal number listed in Table 7. The Offset DAC pins are not intended to drive an external load, and must not be connected during dual-supply operation.

(2) Gain = 4 and TC specified by design and characterization.

(3) The DAC outputs are buffered by op amps that share common AV<sub>DD</sub> and AV<sub>SS</sub> power supplies. DC crosstalk indicates how much dc change in one or more channel outputs may occur when the dc load current changes in one channel (because of an update). With high-impedance loads, the effect is virtually immeasurable. Multiple AV<sub>DD</sub> and AV<sub>SS</sub> terminals are provided to minimize dc crosstalk.

## ELECTRICAL CHARACTERISTICS: Dual-Supply (continued)

All specifications at  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = +16.5V$ ,  $AV_{SS} = -16.5V$ ,  $IOV_{DD} = DV_{DD} = +5V$ , REF-A and REF-B = +5V, gain = 6, AGND-x = DGND = 0V, data format = straight binary, and Offset DAC A and Offset DAC B are at default values <sup>(1)</sup>, unless otherwise noted.

|                                              |                                                                                                               | D    |      |      |                  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|------------------|

| PARAMETER                                    | CONDITIONS                                                                                                    | MIN  | TYP  | MAX  | UNIT             |

| ANALOG OUTPUT (Vout-0 to Vo                  | DUT-7) <sup>(4)</sup>                                                                                         |      |      |      |                  |

| Voltage output <sup>(5)</sup>                | V <sub>REF</sub> = +5V                                                                                        | -15  |      | +15  | V                |

| Vollage oulpul <sup>14</sup>                 | V <sub>REF</sub> = +1.5V                                                                                      | -4.5 |      | +4.5 | V                |

| Output impedance                             | Code = 2000h                                                                                                  |      |      | 0.5  | Ω                |

| Short-circuit current <sup>(6)</sup>         |                                                                                                               |      | ±8   |      | mA               |

| Load current                                 | See Figure 37                                                                                                 |      | ±3   |      | mA               |

| Outrast daith an time a                      | $T_A = +25^{\circ}C$ , device operating for 500 hours, full-scale output                                      |      | 3.4  |      | ppm of FSR       |

| Output drift vs time                         | $T_A = +25^{\circ}C$ , device operating for 1000 hours, full-scale output                                     |      | 4.3  |      | ppm of FSR       |

| Capacitive load stability                    |                                                                                                               |      |      | 500  | pF               |

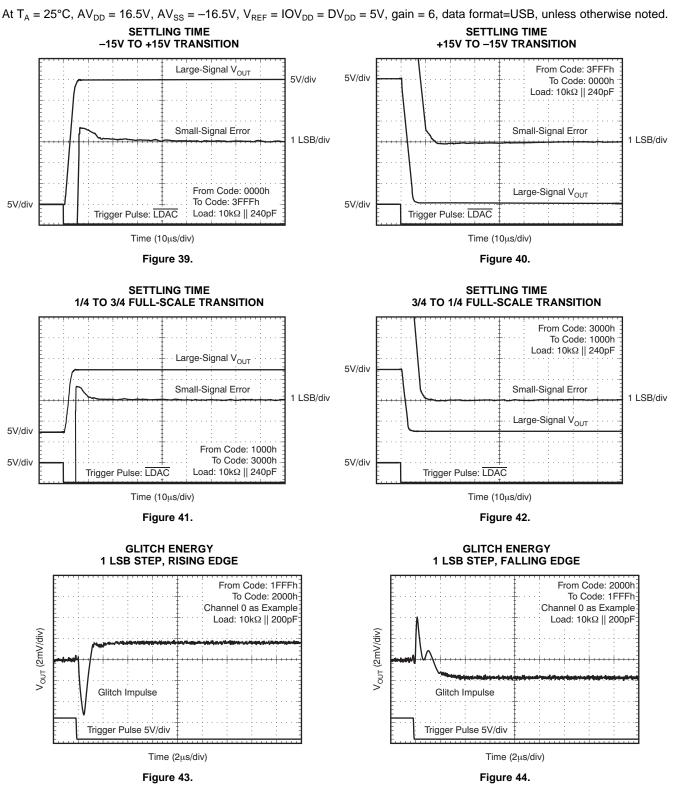

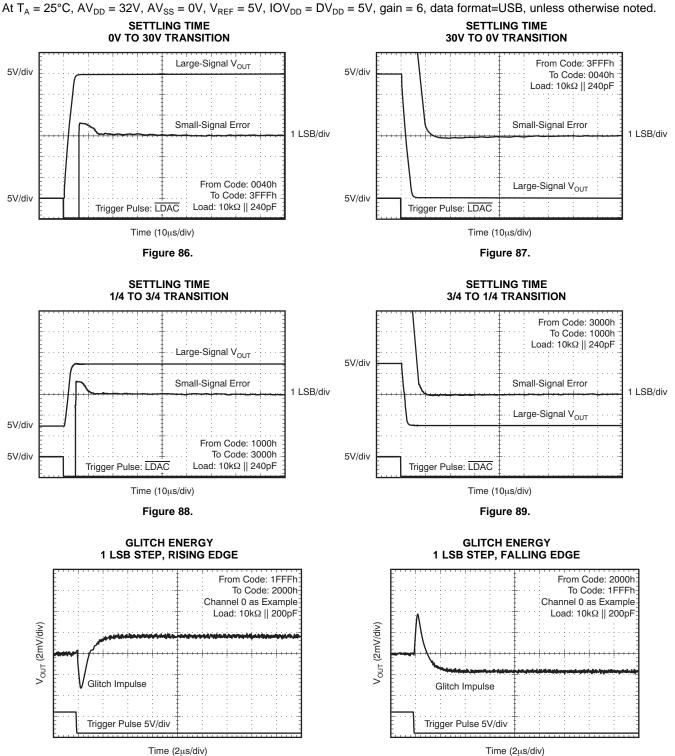

|                                              | To 0.03% of FSR, C_ = 200pF, R_= 10k\Omega, code from 0000h to 3FFFh and 3FFFh to 0000h                       |      | 10   |      | μs               |

| Settling time                                | To 1 LSB, $C_L$ = 200pF, $R_L$ = 10k $\Omega$ , code from 0000h to 3FFFh and 3FFFh to 0000h                   |      | 15   |      | μs               |

|                                              | To 1 LSB, C <sub>L</sub> = 200pF, R <sub>L</sub> = 10k $\Omega$ , code from 1FC0h to 2040h and 2040h to 1FC0h |      | 6    |      | μs               |

| Slew rate (7)                                |                                                                                                               |      | 6    |      | V/µs             |

| Power-on delay <sup>(8)</sup>                | From IOV <sub>DD</sub> $\ge$ +1.8V and DV <sub>DD</sub> $\ge$ +2.7V to $\overline{\text{CS}}$ low             |      | 200  |      | μs               |

| Power-down recovery time                     |                                                                                                               |      | 60   |      | μs               |

| Digital-to-analog glitch <sup>(9)</sup>      | Code from 1FFFh to 2000h and 2000h to 1FFFh                                                                   |      | 4    |      | nV-s             |

| Glitch impulse peak amplitude                | Code from 1FFFh to 2000h and 2000h to 1FFFh                                                                   |      | 5    |      | mV               |

| Channel-to-channel isolation <sup>(10)</sup> | $V_{REF} = 4V_{PP}, f = 1kHz$                                                                                 |      | 88   |      | dB               |

| DAC-to-DAC crosstalk <sup>(11)</sup>         | DACs in the same group                                                                                        |      | 7.5  |      | nV-s             |

| DAC-to-DAC crosstaik                         | DACs among different groups                                                                                   |      | 1    |      | nV-s             |

| Digital crosstalk <sup>(12)</sup>            |                                                                                                               |      | 1    |      | nV-s             |

| Digital feedthrough <sup>(13)</sup>          |                                                                                                               |      | 1    |      | nV-s             |

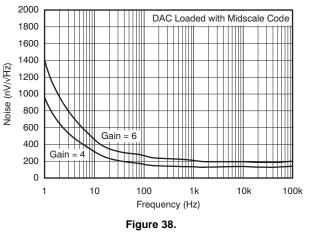

|                                              | $T_A = +25^{\circ}C$ at 10kHz, gain = 6                                                                       |      | 200  |      | nV/√Hz           |

| Output noise                                 | $T_A = +25^{\circ}C$ at 10kHz, gain = 4                                                                       |      | 130  |      | nV/√Hz           |

|                                              | 0.1Hz to 10Hz, gain = 6                                                                                       |      | 20   |      | μV <sub>PP</sub> |

| Power-supply rejection <sup>(14)</sup>       | $AV_{DD} = \pm 15.5V$ to $\pm 16.5V$                                                                          |      | 0.05 |      | LSB              |

(4) Specified by design.

(5) The analog output range of V<sub>OUT</sub>-0 to V<sub>OUT</sub>-7 is equal to (6 × V<sub>REF</sub> – 5 × OUTPUT\_OFFSET\_DAC) for gain = 6. The maximum value of the analog output must not be greater than (AV<sub>DD</sub> – 0.5V), and the minimum value must not be less than (AV<sub>SS</sub> + 0.5V). All specifications are for a ±16.5V power supply and a ±15V output, unless otherwise noted.

(6) When the output current is greater than the specification, the current is clamped at the specified maximum value.

(7) Slew rate is measured from 10% to 90% of the transition when the output changes from 0 to full-scale.

(8) Power-on delay is defined as the time from when the supply voltages reach the specified conditions to when CS goes low, for valid digital communication.

(9) Digital-to-analog glitch is defined as the amount of energy injected into the analog output at the major code transition. It is specified as the area of the glitch in nV-s. It is measured by toggling the DAC register data between 1FFFh and 2000h in straight binary format.

(10) Otherward is a base of the glitch in the area of the glitch is a straight binary format.

(10) Channel-to-channel isolation refers to the ratio of the signal amplitude at the output of one DAC channel to the amplitude of the sinusoidal signal on the reference input of another DAC channel. It is expressed in dB and measured at midscale.

(11) DAC-to-DAC crosstalk is the glitch impulse that appears at the output of one DAC as a result of both the full-scale digital code and subsequent analog output change at another DAC. It is measured with LDAC tied low and expressed in nV-s.

(12) *Digital crosstalk* is the glitch impulse transferred to the output of one converter as a result of a full-scale code change in the DAC input register of another converter. It is measured when the DAC output is not updated, and is expressed in nV-s.

- (13) Digital feedthrough is the glitch impulse injected to the output of a DAC as a result of a digital code change in the DAC input register of the same DAC. It is measured with the full-scale digital code change without updating the DAC output, and is expressed in nV-s.

- (14) The output must not be greater than  $(AV_{DD} 0.5V)$  and not less than  $(AV_{SS} + 0.5V)$ .

## **ELECTRICAL CHARACTERISTICS: Dual-Supply (continued)**

All specifications at  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = +16.5V$ ,  $AV_{SS} = -16.5V$ ,  $IOV_{DD} = DV_{DD} = +5V$ , REF-A and REF-B = +5V, gain = 6, AGND-x = DGND = 0V, data format = straight binary, and Offset DAC A and Offset DAC B are at default values <sup>(1)</sup>, unless otherwise noted.

|                                                 |                                           | D                        |          |                 |      |

|-------------------------------------------------|-------------------------------------------|--------------------------|----------|-----------------|------|

| PARAMETER                                       | CONDITIONS                                | MIN                      | TYP M    | XAN             | UNIT |

| OFFSET DAC OUTPUT <sup>(15)</sup> (16)          |                                           |                          |          |                 |      |

| Voltage output                                  | $V_{REF} = +5V$                           | 0                        |          | 5               | V    |

| Full-scale error                                | $T_A = +25^{\circ}C$                      |                          | ±1       |                 | LSB  |

| Zero-code error                                 | $T_A = +25^{\circ}C$                      |                          | ±0.5     |                 | LSB  |

| Linearity error                                 |                                           |                          | ±1.5     |                 | LSB  |

| Differential linearity error                    |                                           |                          |          | ±1              | LSB  |

| ANALOG MONITOR PIN (V <sub>MON</sub> )          | ·                                         |                          |          |                 |      |

| Output impedance <sup>(17)</sup>                | $T_A = +25^{\circ}C$                      |                          | 2        |                 | kΩ   |

| Three-state leakage current                     |                                           |                          | 100      |                 | nA   |

| AUXILIARY ANALOG INPUT                          | ·                                         |                          |          |                 |      |

| Input range                                     |                                           | AV <sub>SS</sub>         | A        | V <sub>DD</sub> | V    |

| Input impedance<br>(AIN-x to V <sub>MON</sub> ) | T <sub>A</sub> = +25°C                    |                          | 2        |                 | kΩ   |

| Input capacitance <sup>(15)</sup>               |                                           |                          | 4        |                 | pF   |

| Input leakage current                           |                                           |                          | 30       |                 | nA   |

| REFERENCE INPUT                                 | ·                                         |                          |          |                 |      |

| Reference input voltage range <sup>(18)</sup>   |                                           | 1.0                      |          | 5.5             | V    |

| Reference input dc impedance                    |                                           |                          | 10       |                 | MΩ   |

| Reference input capacitance <sup>(15)</sup>     |                                           |                          | 10       |                 | pF   |

| DIGITAL INPUT <sup>(15)</sup>                   |                                           |                          |          |                 |      |

|                                                 | IOV <sub>DD</sub> = +4.5V to +5.5V        | 3.8                      | 0.3 + IC | V <sub>DD</sub> | V    |

| High-level input voltage, V <sub>IH</sub>       | IOV <sub>DD</sub> = +2.7V to +3.3V        | 2.3                      | 0.3 + IC | V <sub>DD</sub> | V    |

|                                                 | IOV <sub>DD</sub> = +1.7V to 2.0V         | 1.5                      |          | V <sub>DD</sub> | V    |

|                                                 | IOV <sub>DD</sub> = +4.5V to +5.5V        | -0.3                     | -0.3 0.8 |                 | V    |

| Low-level input voltage, VIL                    | IOV <sub>DD</sub> = +2.7V to +3.3V        | -0.3                     |          | 0.6             | V    |

|                                                 | IOV <sub>DD</sub> = +1.7V to 2.0V         | -0.3                     |          | 0.3             | V    |

|                                                 | CLR, LDAC, RST, CS, and SDI               |                          |          | ±1              | μA   |

| Input current                                   | USB/BTC, RSTSEL, and GPIO-n               |                          |          | ±5              | μA   |

|                                                 | CLR, LDAC, RST, CS, and SDI               |                          | 5        |                 | pF   |

| Input capacitance                               | USB/BTC and RSTSEL                        |                          | 12       |                 | pF   |

|                                                 | GPIO-n                                    |                          | 14       |                 | pF   |

| DIGITAL OUTPUT <sup>(15)</sup>                  | 1                                         | 1                        |          | 1               |      |

| High-level output voltage, VOH                  | $IOV_{DD} = +2.7V$ to +5.5V, sourcing 1mA | IOV <sub>DD</sub> - 0.4  | IC       | V <sub>DD</sub> | V    |

| (SDO)                                           | $IOV_{DD} = +1.8V$ , sourcing 200 $\mu$ A | 1.6                      |          | V <sub>DD</sub> | V    |

| Low-level output voltage, V <sub>OL</sub>       | $IOV_{DD} = +2.7V$ to +5.5V, sinking 1mA  | 0                        |          | 0.4             | V    |

| (SDO)                                           | IOV <sub>DD</sub> = +1.8V, sinking 200µA  | 0                        |          | 0.2             | V    |

| GPIO-n output voltage low, V <sub>OL</sub>      | 1mA sink from IOV <sub>DD</sub>           |                          | 0.15     |                 | V    |

| GPIO-n output voltage high, V <sub>OH</sub>     | 10kΩ pull-up resistor to $IOV_{DD}$       | 0.99 × IOV <sub>DD</sub> |          |                 | V    |

| High-impedance leakage current                  | SDO and GPIO-n                            |                          | ±5       |                 | μA   |

| High-impedance output                           | SDO                                       |                          | 5        |                 | pF   |

| capacitance                                     | GPIO-n                                    |                          | 14       |                 | pF   |

(15) Specified by design.

(16) Offset DAC A and Offset DAC B are trimmed in manufacturing to minimize the error for symmetrical output. The default value may vary no more than ±3 LSB from the nominal number listed in Table 7. The Offset DAC pins are not intended to drive an external load, and must not be connected during dual-supply operation.

(17) 8kΩ when V<sub>MON</sub> is connected to Reference Buffer A or B, and 4kΩ when V<sub>MON</sub> is connected to Offset DAC-A or -B.

(18) Reference input voltage  $\leq DV_{DD}$ .

SBAS460A - MAY 2009 - REVISED DECEMBER 2009

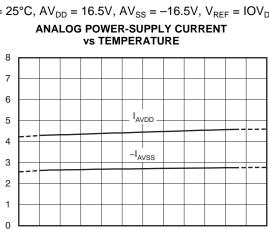

# ELECTRICAL CHARACTERISTICS: Dual-Supply (continued)

All specifications at  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = +16.5V$ ,  $AV_{SS} = -16.5V$ ,  $IOV_{DD} = DV_{DD} = +5V$ , REF-A and REF-B = +5V, gain = 6, AGND-x = DGND = 0V, data format = straight binary, and Offset DAC A and Offset DAC B are at default values <sup>(1)</sup>, unless otherwise noted.

|                                   |                                                         | D    |      |      |      |

|-----------------------------------|---------------------------------------------------------|------|------|------|------|

| PARAMETER                         | CONDITIONS                                              | MIN  | TYP  | MAX  | UNIT |

| POWER SUPPLY                      |                                                         |      |      |      |      |

| AV <sub>DD</sub>                  |                                                         | +4.5 |      | +18  | V    |

| AV <sub>SS</sub>                  |                                                         | -18  |      | -4.5 | V    |

| DV <sub>DD</sub>                  |                                                         | +2.7 |      | +5.5 | V    |

| IOV <sub>DD</sub> <sup>(19)</sup> |                                                         | +1.8 |      | +5.5 | V    |

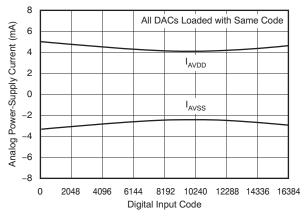

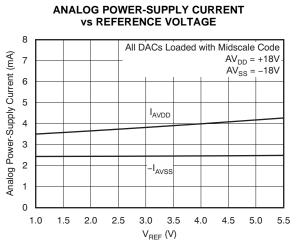

| A1                                | Normal operation, midscale code, output unloaded        |      | 4.3  | 6    | mA   |

| AI <sub>DD</sub>                  | Power down, output unloaded                             |      | 35   |      | μA   |

| A.I.                              | Normal operation, midscale code, output unloaded        | -4   | -2.7 |      | mA   |

| Al <sub>ss</sub>                  | Power down, output unloaded                             |      | 35   |      | μA   |

|                                   | Normal operation                                        |      | 78   |      | μA   |

| DI <sub>DD</sub>                  | Power down                                              |      | 36   |      | μA   |

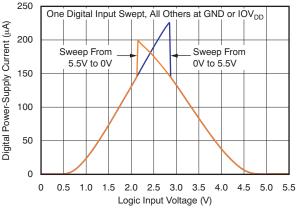

| 101                               | Normal operation, $V_{IH} = IOV_{DD}$ , $V_{IL} = DGND$ |      | 5    |      | μA   |

| IOI <sub>DD</sub>                 | Power down, $V_{IH} = IOV_{DD}$ , $V_{IL} = DGND$       |      | 5    |      | μA   |

| Power dissipation                 | Normal operation, ±16.5V supplies, midscale code        |      | 115  | 165  | mW   |

| TEMPERATURE RANGE                 | · · · · · ·                                             |      |      |      |      |

| Specified performance             |                                                         | -40  |      | +105 | °C   |

(19)  $IOV_{DD} \leq DV_{DD}$ .

6

www.ti.com

## ELECTRICAL CHARACTERISTICS: Single-Supply

All specifications at  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = +32V$ ,  $AV_{SS} = 0V$ ,  $IOV_{DD} = DV_{DD} = +5V$ , REF-A and REF-B = +5V, gain = 6, AGND-x = DGND = 0V, data format = straight binary, and OFFSET-A = OFFSET-B = AGND, unless otherwise noted.

|                                            |                                                                                            | D   |      |      |            |

|--------------------------------------------|--------------------------------------------------------------------------------------------|-----|------|------|------------|

| PARAMETER                                  | CONDITIONS                                                                                 | MIN | TYP  | MAX  | UNIT       |

| STATIC PERFORMANCE <sup>(1)</sup>          |                                                                                            |     |      |      |            |

| Resolution                                 |                                                                                            | 14  |      |      | Bits       |

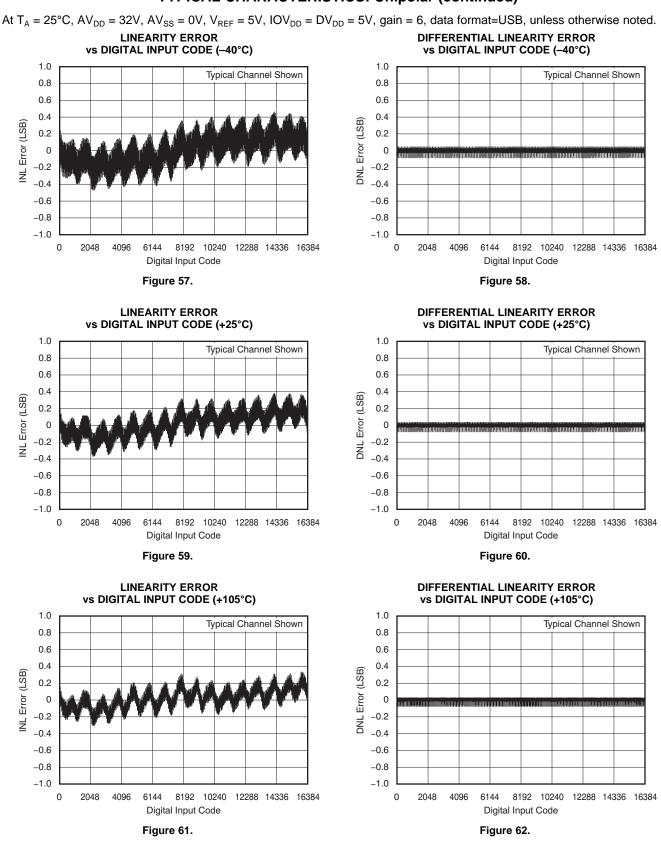

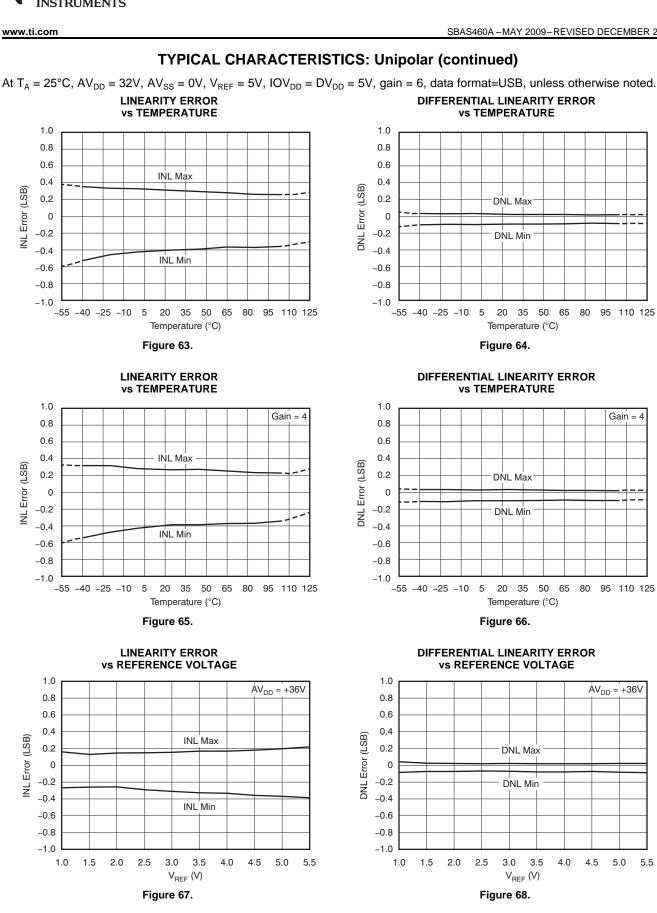

| Linearity error                            | Measured by line passing through codes 0040h and 3FFFh                                     |     |      | ±1   | LSB        |

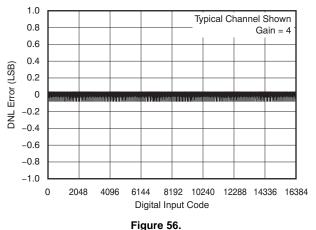

| Differential linearity error               | Measured by line passing through codes 0040h and 3FFFh                                     |     |      | ±1   | LSB        |

|                                            | $T_A = +25^{\circ}C$ , before user calibration, gain = 6, code = 0040h                     |     |      | ±2.5 | LSB        |

| Unipolar zero error                        | $T_A = +25^{\circ}C$ , before user calibration, gain = 4, code = 0040h                     |     |      | ±4   | LSB        |

|                                            | $T_A = +25^{\circ}C$ , after user calib., gain = 4 or 6, code = 0040h                      |     | ±1   |      | LSB        |

| Unipolar zero error TC                     | Gain = 4 or 6, code = 0040h                                                                |     | ±0.5 | ±3   | ppm FSR/°C |

|                                            | $T_{A} = +25^{\circ}C$ , gain = 6                                                          |     |      | ±2.5 | LSB        |

| Gain error                                 | $T_A = +25^{\circ}C$ , gain = 4                                                            |     |      | ±4   | LSB        |

| Gain error TC                              | Gain = 4 or 6                                                                              |     | ±1   | ±3   | ppm FSR/°C |

|                                            | $T_A = +25^{\circ}C$ , before user calibration, gain = 6, code = 3FFFh                     |     |      | ±2.5 | LSB        |

| Full-scale error                           | $T_A = +25^{\circ}C$ , before user calibration, gain = 4, code = 3FFFh                     |     |      | ±4   | LSB        |

|                                            | $T_A = +25^{\circ}C$ , after user calib., gain = 4 or 6, code = 3FFFh                      |     | ±1   |      | LSB        |

| Full-scale error TC                        | Gain = 4 or 6, code = 3FFFh                                                                |     | ±0.5 | ±3   | ppm FSR/°C |

| DC crosstalk <sup>(2)</sup>                | Measured channel at code = 2000h, full-scale change on any other channel                   |     | 0.05 |      | LSB        |

| ANALOG OUTPUT (V <sub>OUT</sub> -0 to      | o V <sub>OUT</sub> -7) <sup>(3)</sup>                                                      |     |      |      |            |

| V = 14 = = = = = = = = = = = = = = = = =   | V <sub>REF</sub> = +5V                                                                     | 0   |      | +30  | V          |

| Voltage output <sup>(4)</sup>              | V <sub>REF</sub> = +1.5V                                                                   | 0   |      | +9   | V          |

| Output impedance                           | Code = 2000h                                                                               |     |      | 0.5  | Ω          |

| Short-circuit current <sup>(5)</sup>       |                                                                                            |     | ±8   |      | mA         |

| Load current                               | See Figure 84 and Figure 85                                                                |     | ±3   |      | mA         |

| Output drift vo time                       | $T_A$ = +25°C, device operating for 500 hours, full-scale output                           |     | 3.4  |      | ppm of FSR |

| Output drift vs time                       | $T_A$ = +25°C, device operating for 1000 hours, full-scale output                          |     | 4.3  |      | ppm of FSR |

| Capacitive load stability                  |                                                                                            |     |      | 500  | pF         |

|                                            | To 0.03% of FSR, CL = 200pF, RL = 10k\Omega, code from 0040h to 3FFFh and 3FFFh to 0040h   |     | 10   |      | μs         |

| Settling time                              | To 1 LSB, $C_L$ = 200pF, $R_L$ = 10k $\Omega,$ code from 0040h to 3FFFh and 3FFFh to 0040h |     | 15   |      | μs         |

|                                            | To 1 LSB, $C_L$ = 200pF, $R_L$ = 10k $\Omega,$ code from 1FC0h to 2040h and 2040h to 1FC0h |     | 6    |      | μs         |

| Slew rate <sup>(6)</sup>                   |                                                                                            |     | 6    |      | V/µs       |

| Power-on delay <sup>(7)</sup>              | From $IOV_{DD} \ge +1.8V$ and $DV_{DD} \ge +2.7V$ to $\overline{CS}$ low                   |     | 200  |      | μs         |

| Power-down recovery time                   |                                                                                            |     | 90   |      | μs         |

| Digital-to-analog glitch <sup>(8)</sup>    | Code from 1FFFh to 2000h and 2000h to 1FFFh                                                |     | 4    |      | nV-s       |

| Glitch impulse peak amplitude              | Code from 1FFFh to 2000h and 2000h to 1FFFh                                                |     | 5    |      | mV         |

| Channel-to-channel isolation <sup>(9</sup> | $V_{\text{REF}} = 4V_{\text{PP}}, \text{ f} = 1\text{ kHz}$                                |     | 88   |      | dB         |

(1) Gain = 4 and TC specified by design and characterization.

(2) The DAC outputs are buffered by op amps that share common AV<sub>DD</sub> and AV<sub>SS</sub> power supplies. DC crosstalk indicates how much dc change in one or more channel outputs may occur when the dc load current changes in one channel (because of an update). With high-impedance loads, the effect is virtually immeasurable. Multiple AV<sub>DD</sub> and AV<sub>SS</sub> terminals are provided to minimize dc crosstalk.

(3) Specified by design

(3) Specified by design.

(4) The analog output range of V<sub>OUT</sub>-0 to V<sub>OUT</sub>-7 is equal to  $(6 \times V_{REF})$  for gain = 6. The maximum value of the analog output must not be greater than (AV<sub>DD</sub> - 0.5V). All specifications are for a +32V power supply and a 0V to +30V output, unless otherwise noted.

(5) When the output current is greater than the specification, the current is clamped at the specified maximum value.

(6) Slew rate is measured from 10% to 90% of the transition when the output changes from 0 to full-scale.

(7) *Power-on delay* is defined as the time from when the supply voltages reach the specified conditions to when CS goes low, for valid digital communication.

(8) *Digital-to-analog glitch* is defined as the amount of energy injected into the analog output at the major code transition. It is specified as the area of the glitch in nV-s. It is measured by toggling the DAC register data between 1FFFh and 2000h in straight binary format.

(9) Channel-to-channel isolation refers to the ratio of the signal amplitude at the output of one DAC channel to the amplitude of the sinusoidal signal on the reference input of another DAC channel. It is expressed in dB and measured at midscale.

### EXAS **INSTRUMENTS**

www.ti.com

## ELECTRICAL CHARACTERISTICS: Single-Supply (continued)

All specifications at  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = +32V$ ,  $AV_{SS} = 0V$ ,  $IOV_{DD} = DV_{DD} = +5V$ , REF-A and REF-B = +5V, gain = 6, AGND-x = DGND = 0V, data format = straight binary, and OFFSET-A = OFFSET-B = AGND, unless otherwise noted.

|                                                  |                                         | D                |                         |                  |  |

|--------------------------------------------------|-----------------------------------------|------------------|-------------------------|------------------|--|

| PARAMETER                                        | CONDITIONS                              | MIN              | MIN TYP MAX             |                  |  |

|                                                  | DACs in the same group                  |                  | 10                      | nV-s             |  |

| DAC-to-DAC crosstalk <sup>(10)</sup>             | DACs among different groups             |                  | 1                       | nV-s             |  |

| Digital crosstalk <sup>(11)</sup>                |                                         |                  | 1                       | nV-s             |  |

| Digital feedthrough <sup>(12)</sup>              |                                         |                  | 1                       | nV-s             |  |

|                                                  | $T_A = +25^{\circ}C$ at 10kHz, gain = 6 |                  | 200                     | nV/√Hz           |  |

| Output noise                                     | $T_A = +25^{\circ}C$ at 10kHz, gain = 4 |                  | 130                     | nV/√Hz           |  |

|                                                  | 0.1Hz to 10Hz, gain = 6                 |                  | 20                      | μV <sub>PP</sub> |  |

| Power-supply rejection <sup>(13)</sup>           | AV <sub>DD</sub> = +33V to +36V         |                  | 0.05                    | LSB              |  |

| ANALOG MONITOR PIN (V <sub>MON</sub> )           | 1                                       |                  |                         |                  |  |

| Output impedance <sup>(14)</sup>                 | T <sub>A</sub> = +25°C                  |                  | 2                       | kΩ               |  |

| Three-state leakage current                      |                                         |                  | 100                     | nA               |  |

| AUXILIARY ANALOG INPUT                           |                                         | 1                |                         | 1                |  |

| Input range                                      |                                         | AV <sub>SS</sub> | AV <sub>DD</sub>        | V                |  |

| Input impedance<br>(AIN-x to V <sub>MON</sub> )  | T <sub>A</sub> = +25°C                  |                  | 2                       |                  |  |

| Input capacitance <sup>(15)</sup>                |                                         |                  | 4                       | pF               |  |

| Input leakage current                            |                                         |                  | 30                      | nA               |  |

| REFERENCE INPUT                                  |                                         |                  |                         |                  |  |

| Reference input voltage<br>range <sup>(16)</sup> |                                         | 1.0              | 5.5                     | V                |  |

| Reference input dc impedance                     |                                         |                  | 10                      | MΩ               |  |

| Reference input capacitance <sup>(15)</sup>      |                                         |                  | 10                      | pF               |  |

| DIGITAL INPUT <sup>(15)</sup>                    |                                         |                  |                         |                  |  |

|                                                  | IOV <sub>DD</sub> = +4.5V to +5.5V      | 3.8              | 0.3 + IOV <sub>DD</sub> | V                |  |

| High-level input voltage, V <sub>IH</sub>        | IOV <sub>DD</sub> = +2.7V to +3.3V      | 2.3              | 0.3 + IOV <sub>DD</sub> | V                |  |

|                                                  | IOV <sub>DD</sub> = +1.7V to 2.0V       | 1.5              | 0.3 + IOV <sub>DD</sub> | V                |  |

|                                                  | IOV <sub>DD</sub> = +4.5V to +5.5V      | -0.3             | 0.8                     | V                |  |

| Low-level input voltage, V <sub>IL</sub>         | IOV <sub>DD</sub> = +2.7V to +3.3V      | -0.3             | 0.6                     | V                |  |

|                                                  | IOV <sub>DD</sub> = +1.7V to 2.0V       | -0.3             | 0.3                     | V                |  |

| tt                                               | CLR, LDAC, RST, CS, and SDI             |                  | ±1                      | μA               |  |

| Input current                                    | USB/BTC, RSTSEL, and GPIO-n             |                  | ±5                      | μA               |  |

|                                                  | CLR, LDAC, RST, CS, and SDI             |                  | 5                       | pF               |  |

| Input capacitance                                | USB/BTC and RSTSEL                      |                  | 12                      | pF               |  |

|                                                  | GPIO-n                                  |                  | 14                      | pF               |  |

(10) DAC-to-DAC crosstalk is the glitch impulse that appears at the output of one DAC as a result of both the full-scale digital code and subsequent analog output change at another DAC. It is measured with LDAC tied low and expressed in nV-s.

(11) Digital crosstalk is the glitch impulse transferred to the output of one converter as a result of a full-scale code change in the DAC input register of another converter. It is measured when the DAC output is not updated, and is expressed in nV-s.

(12) Digital feedthrough is the glitch impulse injected to the output of a DAC as a result of a digital code change in the DAC input register of the same DAC. It is measured with the full-scale digital code change without updating the DAC output, and is expressed in nV-s.

(13) The analog output must not be greater than ( $AV_{DD} - 0.5V$ ). (14)  $8k\Omega$  when  $V_{MON}$  is connected to Reference Buffer A or B, and  $4k\Omega$  when  $V_{MON}$  is connected to Offset DAC-A or -B.

(15) Specified by design.

(16) Reference input voltage ≤ DV<sub>DD</sub>.

#### www.ti.com

## ELECTRICAL CHARACTERISTICS: Single-Supply (continued)

All specifications at  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD} = +32V$ ,  $AV_{SS} = 0V$ ,  $IOV_{DD} = DV_{DD} = +5V$ , REF-A and REF-B = +5V, gain = 6, AGND-x = DGND = 0V, data format = straight binary, and OFFSET-A = OFFSET-B = AGND, unless otherwise noted.

|                                             |                                                         | DAC8218                |      |                   |      |

|---------------------------------------------|---------------------------------------------------------|------------------------|------|-------------------|------|

| PARAMETER                                   | CONDITIONS                                              | MIN                    | TYP  | MAX               | UNIT |

| DIGITAL OUTPUT <sup>(17)</sup>              | L                                                       |                        |      |                   |      |

| High-level output voltage, V <sub>OH</sub>  | $IOV_{DD} = +2.7V$ to +5.5V, sourcing 1mA               | $IOV_{DD} - 0.4$       |      | IOV <sub>DD</sub> | V    |

| (SDO)                                       | $IOV_{DD} = +1.8V$ , sourcing 200µA                     | 1.6                    |      | IOV <sub>DD</sub> | V    |

| Low-level output voltage, V <sub>OL</sub>   | $IOV_{DD} = +2.7V$ to +5.5V, sinking 1mA                | 0                      |      | 0.4               | V    |

| (SDO)                                       | $IOV_{DD} = +1.8V$ , sinking 200µA                      | 0                      |      | 0.2               | V    |

| GPIO-n output voltage low, V <sub>OL</sub>  | 1mA sink from IOV <sub>DD</sub>                         |                        | 0.15 |                   | V    |

| GPIO-n output voltage high, V <sub>OH</sub> | 10k $\Omega$ pull-up resistor to IOV <sub>DD</sub>      | $0.99 \times IOV_{DD}$ |      |                   | V    |

| High-impedance leakage current              | SDO and GPIO-n                                          |                        | ±5   |                   | μA   |

| High-impedance output                       | SDO                                                     |                        | 5    |                   | pF   |

| capacitance                                 | GPIO-n                                                  |                        | 14   |                   | pF   |

| POWER SUPPLY                                |                                                         |                        |      |                   |      |

| AV <sub>DD</sub>                            |                                                         | +9                     |      | +36               | V    |

| DV <sub>DD</sub>                            |                                                         | +2.7                   |      | +5.5              | V    |

| IOV <sub>DD</sub> <sup>(18)</sup>           |                                                         | +1.8                   |      | +5.5              | V    |

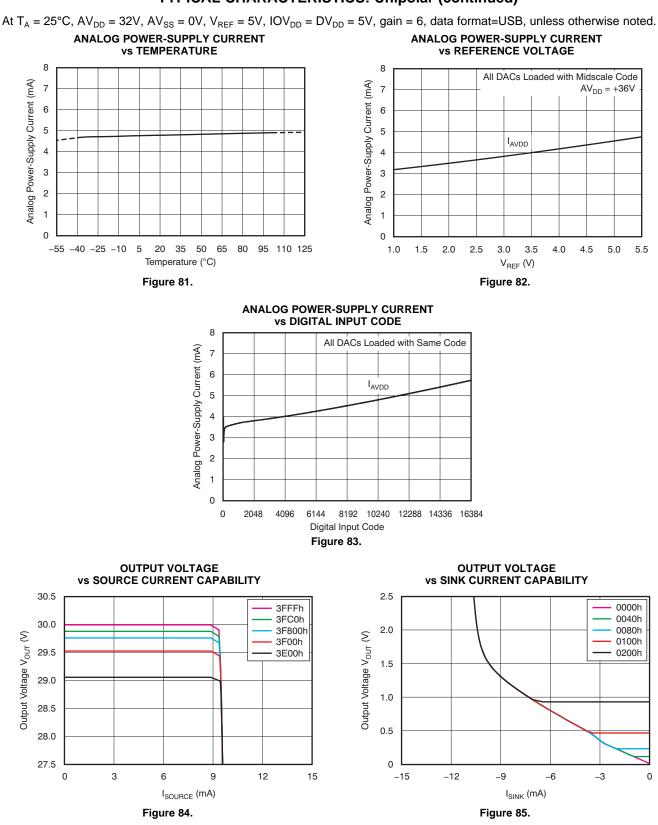

| ٨١                                          | Normal operation, midscale code, output unloaded        |                        | 4.5  | 7                 | mA   |

| Al <sub>DD</sub>                            | Power down, output unloaded                             |                        | 35   |                   | μA   |

| DI                                          | Normal operation                                        |                        | 70   |                   | μA   |

| DI <sub>DD</sub>                            | Power down                                              |                        | 36   |                   | μA   |

|                                             | Normal operation, $V_{IH} = IOV_{DD}$ , $V_{IL} = DGND$ |                        | 5    |                   | μA   |

| IOI <sub>DD</sub>                           | Power down, $V_{IH} = IOV_{DD}$ , $V_{IL} = DGND$       |                        | 5    |                   | μA   |

| Power dissipation                           | Normal operation                                        |                        | 140  | 225               | mW   |

| TEMPERATURE RANGE                           | ·                                                       | · ·                    |      |                   |      |

| Specified performance                       |                                                         | -40                    |      | +105              | °C   |

(17) Specified by design. (18)  $IOV_{DD} \le DV_{DD}$ .

SBAS460A - MAY 2009 - REVISED DECEMBER 2009

## FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

### TEXAS INSTRUMENTS

### www.ti.com

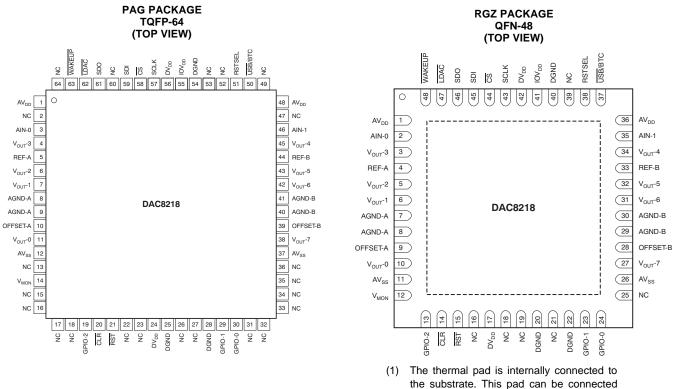

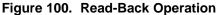

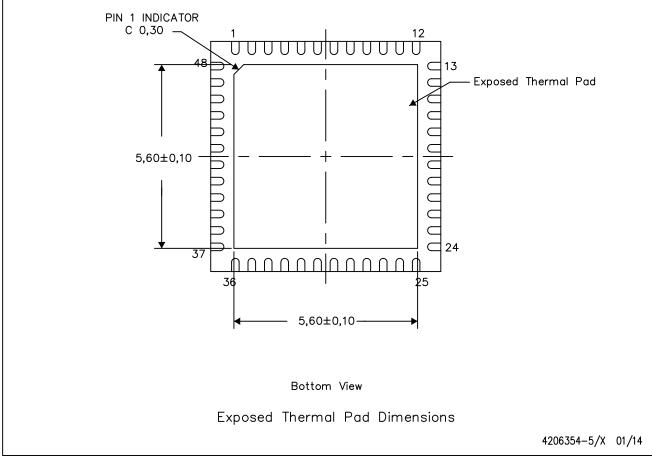

# PIN CONFIGURATIONS

The thermal pad is internally connected to the substrate. This pad can be connected to AV<sub>SS</sub> or left floating. Keep the thermal pad separate from the digital ground, if possible.

### **PIN DESCRIPTIONS**

| PIN                 | PIN    | NO.     |     |                                                                                                                                                                                                                                                                                                |

|---------------------|--------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                | QFN-48 | TQFP-64 | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                    |

| AV <sub>DD</sub>    | 1      | 1       | I   | Positive analog power supply                                                                                                                                                                                                                                                                   |

| AIN-0               | 2      | 3       | I   | Auxiliary analog input 0, directly routed to the analog mux                                                                                                                                                                                                                                    |

| V <sub>OUT</sub> -3 | 3      | 4       | 0   | DAC-3 output                                                                                                                                                                                                                                                                                   |

| REF-A               | 4      | 5       | I   | Group A <sup>(1)</sup> reference input                                                                                                                                                                                                                                                         |

| V <sub>OUT</sub> -2 | 5      | 6       | 0   | DAC-2 output                                                                                                                                                                                                                                                                                   |

| V <sub>OUT</sub> -1 | 6      | 7       | 0   | DAC-1 output                                                                                                                                                                                                                                                                                   |

| AGND-A              | 7      | 8       | I   | Group A analog ground and the ground of REF-A. This pin must be tied to AGND-B and DGND.                                                                                                                                                                                                       |

| AGND-A              | 8      | 9       | I   | Group A analog ground and the ground of REF-A. This pin must be tied to AGND-B and DGND.                                                                                                                                                                                                       |

| OFFSET-A            | 9      | 10      | 0   | OFFSET DAC-A analog output. Must be connected to AGND-A during single power-supply operation ( $AV_{SS} = 0V$ ). This pin is not intended to drive an external load.                                                                                                                           |

| V <sub>OUT</sub> -0 | 10     | 11      | 0   | DAC-0 output                                                                                                                                                                                                                                                                                   |

| AV <sub>SS</sub>    | 11     | 12      | I   | Negative analog power supply                                                                                                                                                                                                                                                                   |

| V <sub>MON</sub>    | 12     | 14      | 0   | Analog monitor output. This pin is either in Hi-Z status, connected to one of the eight DAC outputs, reference buffer outputs, offset DAC outputs, or one of the auxiliary analog inputs, depending on the content of the Monitor Register. See the Monitor Register, Table 12, for details.   |

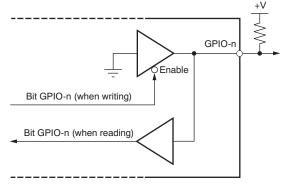

| GPIO-2              | 13     | 19      | I/O | General-purpose digital input/output 2. This pin is a bidirectional digital input/output, open-drain and requires an external pull-up resistor. See the <i>GPIO Pins</i> section for details.                                                                                                  |

| CLR                 | 14     | 20      | I   | Clear input, level triggered. When the $\overline{\text{CLR}}$ pin is logic '0', all V <sub>OUT</sub> -X pins connect to AGND-x through switches and internal low-impedance. When the $\overline{\text{CLR}}$ pin is logic '1', all V <sub>OUT</sub> -X pins connect to the amplifier outputs. |

| RST                 | 15     | 21      | I   | Reset input (active low). Logic low on this pin resets the DAC registers and DACs to the values defined by the RSTSEL pin. CS must be logic high when RST is active.                                                                                                                           |

(1) Group A consists of DAC-0, DAC-1, DAC-2, and DAC-3. Group B consists of DAC-4, DAC-5, DAC-6, and DAC-7.

## **PIN DESCRIPTIONS (continued)**

| PIN                 | PIN                       | NO.                                                                        |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|---------------------------|----------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                | QFN-48                    | TQFP-64                                                                    | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DV <sub>DD</sub>    | 17                        | 24                                                                         | I   | Digital power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DGND                | 20                        | 25                                                                         | I   | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DGND                | 22                        | 28                                                                         | I   | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GPIO-1              | 23                        | 29                                                                         | I/O | General-purpose digital input/output 1. This pin is a bidirectional digital input/output, open-drain and requires an external resistor. See the <i>GPIO Pins</i> section for details.                                                                                                                                                                                                                                                                                                                                                  |

| GPIO-0              | 24                        | 30                                                                         | I/O | General-purpose digital input/output 0. This pin is a bidirectional digital input/output, open-drain and requires an external resistor. See the <i>GPIO Pins</i> section for details.                                                                                                                                                                                                                                                                                                                                                  |

| AV <sub>SS</sub>    | 26                        | 37                                                                         | Ι   | Negative analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>OUT</sub> -7 | 27                        | 38                                                                         | 0   | DAC-7 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OFFSET-B            | 28                        | 39                                                                         | 0   | OFFSET DAC-B analog output. Must be connected to AGND-B during single-supply operation $(AV_{SS} = 0V)$ .                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AGND-B              | 29                        | 40                                                                         | I   | Group B <sup>(1)</sup> analog ground and the ground of REF-B. This pin must be tied to AGND-A and DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AGND-B              | 30                        | 41                                                                         | I   | Group B analog ground and the ground of REF-B. This pin must be tied to AGND-A and DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>OUT</sub> -6 | 31                        | 42                                                                         | 0   | DAC-6 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>OUT</sub> -5 | 32                        | 43                                                                         | 0   | DAC-5 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| REF-B               | 33                        | 44                                                                         | I   | Group B reference input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>OUT</sub> -4 | 34                        | 45                                                                         | 0   | DAC-4 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AIN-1               | 35                        | 46                                                                         | I   | Auxiliary analog input 1, directly routed to the analog mux                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AV <sub>DD</sub>    | 36                        | 48                                                                         | I   | Positive analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| USB/BTC             | 37                        | 50                                                                         | I   | Data format selection of Input DAC data and Offset DAC data. Data are in straight binary format when connected to DGND or in twos complement format when connected to IOV <sub>DD</sub> . The command data are always in straight binary format. Refer to <i>Input Data Format</i> section for details.                                                                                                                                                                                                                                |

| RSTSEL              | 38                        | 51                                                                         | I   | Output reset selection. Selects the output voltage on the V <sub>OUT</sub> pin after power-on or hardware reset. Refer to the <i>Power-On Reset</i> section for details.                                                                                                                                                                                                                                                                                                                                                               |

| DGND                | 40                        | 54                                                                         | I   | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IOV <sub>DD</sub>   | 41                        | 55                                                                         | I   | Interface power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DV <sub>DD</sub>    | 42                        | 56                                                                         | I   | Digital power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

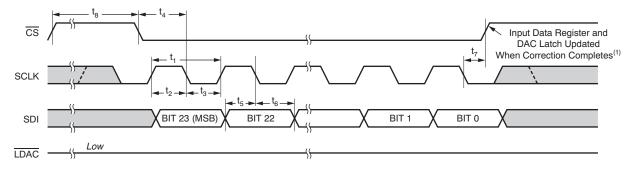

| SCLK                | 43                        | 57                                                                         | I   | SPI bus serial clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CS                  | 44                        | 58                                                                         | I   | SPI bus chip select input (active low). Data are not clocked into SDI unless $\overline{CS}$ is low. When $\overline{CS}$ is high, SDO is in a high-impedance state and the SCLK and SDI signals are blocked from the device.                                                                                                                                                                                                                                                                                                          |

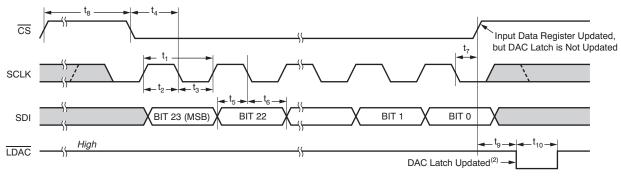

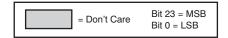

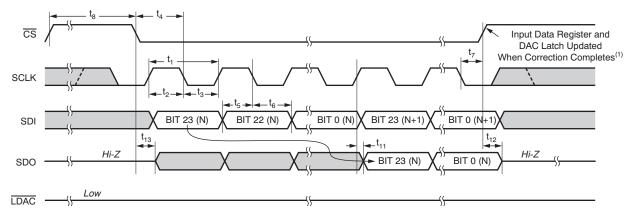

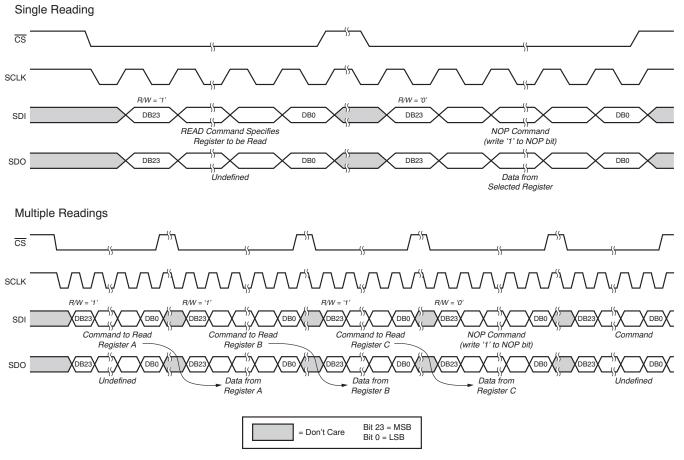

| SDI                 | 45                        | 59                                                                         | I   | SPI bus serial data input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |