# LM3200 Miniature, Adjustable, Step-Down DC-DC Converter with Bypass Mode for RF Power Amplifiers

Check for Samples: LM3200

## FEATURES

- 2 MHz (typ.) PWM Switching Frequency

- Operates from a Single Li-Ion Cell (2.7V to 5.5V)

- Variable Output Voltage (0.8V to 3.6V)

- 300 mA Maximum Load Capability (PWM Mode)

- 500 mA Maximum Load Capability (Bypass Mode)

- PWM, Forced and Automatic Bypass Mode

- High Efficiency (96% Typ at 3.6V<sub>IN</sub>, 3.2V<sub>OUT</sub> at 120 mA) from Internal Synchronous Rectification

- 10-pin DSBGA Package

- Current Overload Protection

- Thermal Overload Protection

# **APPLICATIONS**

- Cellular Phones

- Hand-Held Radios

- RF PC Cards

- Battery Powered RF Devices

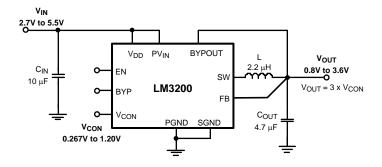

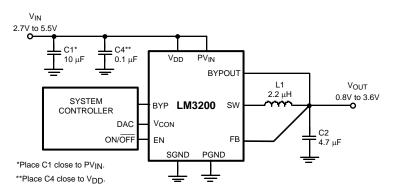

## **TYPICAL APPLICATION**

## DESCRIPTION

The LM3200 is a DC-DC converter optimized for powering RF power amplifiers (PAs) from a single Lithium-Ion cell. It steps down an input voltage of 2.7V to 5.5V to a variable output voltage of 0.8V to 3.6V. The output voltage is set using an analog input ( $V_{CON}$ ) for optimizing efficiency of the RF PA at various power levels.

LM3200 offers superior The features and performance for mobile phones and similar RF PA applications. Fixed-frequency PWM mode minimizes RF interference. Bypass mode turns on an internal bypass switch to power the PA directly from the battery. LM3200 has both forced and automatic bypass modes. Shutdown mode turns the device off and reduces battery consumption to 0.1 µA (typ.). The LM3200 is available in a 10-pin lead free DSBGA package. A high switching frequency (2 MHz) allows use of tiny surface-mount components. Only three small external surface-mount components, inductor and two ceramic capacitors are required.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

www.ti.com

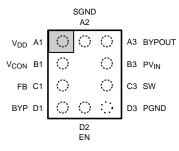

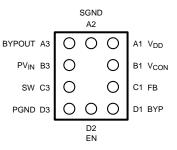

# **CONNECTION DIAGRAMS**

Figure 1. Top View

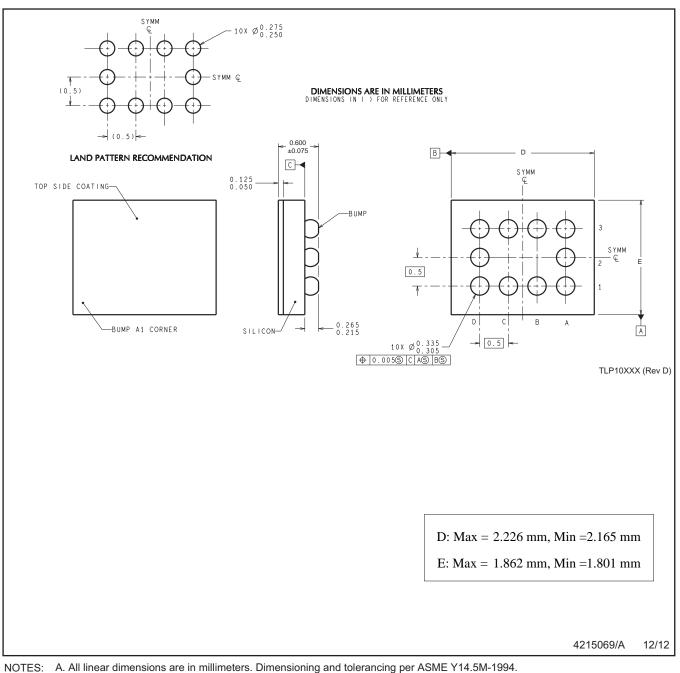

# 10–Bump Thin DSBGA Package, Large Bump See NS Package Number YPA0010NHA

Figure 2. Bottom View

#### **PIN DESCRIPTION**

| Pin # | Name                                                                                                 | Description                                                                                                                                                                                                                      |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A1    | V <sub>DD</sub>                                                                                      | Analog Supply Input. A 0.1 $\mu$ F ceramic capacitor is recommended to be placed as close to this pin as possible. (Figure 33)                                                                                                   |  |  |  |  |  |

| B1    | V <sub>CON</sub>                                                                                     | Voltage Control Analog input. $V_{CON}$ controls $V_{OUT}$ in PWM mode. Set: $V_{OUT} = 3 \times V_{CON}$ . Do not leave floating.                                                                                               |  |  |  |  |  |

| C1    | FB                                                                                                   | Feedback Analog Input. Connect to the output at the output filter capacitor. (Figure 33)                                                                                                                                         |  |  |  |  |  |

| D1    | D1 BYP Bypass. Use this digital input to command operation in Bypass mode. Set BYP low for normal op |                                                                                                                                                                                                                                  |  |  |  |  |  |

| D2    | EN                                                                                                   | Enable Input. Set this digital input high after Vin >2.7V for normal operation. For shutdown, set low.                                                                                                                           |  |  |  |  |  |

| D3    | PGND                                                                                                 | Power Ground                                                                                                                                                                                                                     |  |  |  |  |  |

| C3    | SW                                                                                                   | Switching Node connection to the internal PFET switch and NFET synchronous rectifier.<br>Connect to an inductor with a saturation current rating that exceeds the maximum Switch Peak Current Limit specification of the LM3200. |  |  |  |  |  |

| B3    | PVIN                                                                                                 | Power Supply Voltage Input to the internal PFET switch and Bypass FET. (Figure 33)                                                                                                                                               |  |  |  |  |  |

| A3    | BYPOUT                                                                                               | Bypass FET Drain. Connect to the output capacitor. (Figure 33) Do not leave floating.                                                                                                                                            |  |  |  |  |  |

| A2    | SGND                                                                                                 | Analog and Control Ground                                                                                                                                                                                                        |  |  |  |  |  |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### www.ti.com

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)(2)(3)</sup>

| V <sub>DD</sub> , PV <sub>IN</sub> to SGND      |                  | -0.2V to +6.0V                                            |

|-------------------------------------------------|------------------|-----------------------------------------------------------|

| PGND to SGND                                    |                  | -0.2V to +0.2V                                            |

| EN, FB, BYP, V <sub>CON</sub>                   |                  | (SGND -0.2V)<br>to (V <sub>DD</sub> +0.2V)<br>w/6.0V max  |

| SW, BYPOUT                                      |                  | (PGND -0.2V)<br>to (PV <sub>IN</sub> +0.2V)<br>w/6.0V max |

| PV <sub>IN</sub> to V <sub>DD</sub>             |                  | -0.2V to +0.2V                                            |

| Continuous Power Dissipation <sup>(4)</sup>     |                  | Internally Limited                                        |

| Junction Temperature (T <sub>J-MAX)</sub>       |                  | +150°C                                                    |

| Storage Temperature Range                       |                  | -65°C to +150°C                                           |

| Maximum Lead Temperature<br>(Soldering, 10 sec) |                  | +260°C                                                    |

| ESD Rating <sup>(5)</sup>                       | Human Body Model | 2.0 kV                                                    |

|                                                 | Machine Model    | 200V                                                      |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply specified performance limits. For specified performance limits and associated test conditions, see the Electrical Characteristics table.

(2) All voltages are with respect to the potential at the GND pins.

(3) If Military/Aerospace specified devices are required, please contact the TI Sales Office/ Distributors for availability and specifications.

(4) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $\dot{T}_J = 150^{\circ}C$  (typ.) and disengages at  $T_J = 130^{\circ}C$  (typ.).

(5) The Human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. (MIL-STD-883 3015.7) The machine model is a 200 pF capacitor discharged directly into each pin. TI recommends that all integrated circuits be handled with Appropriate precautions. Failure to observe proper ESD handling techniques can result in damage.

#### **OPERATING RATINGS**<sup>(1)(2)</sup>

| Input Voltage Range                          | 2.7V to 5.5V                                               |                 |  |  |  |

|----------------------------------------------|------------------------------------------------------------|-----------------|--|--|--|

| Recommended Load Current                     | PWM Mode                                                   | 0 mA to 300 mA  |  |  |  |

|                                              | Bypass Mode                                                | 0 mA to 500 mA  |  |  |  |

| Junction Temperature (T <sub>J</sub> ) Range |                                                            | −25°C to +125°C |  |  |  |

| Ambient Temperature (T <sub>A</sub> ) Range  | Ambient Temperature (T <sub>A</sub> ) Range <sup>(3)</sup> |                 |  |  |  |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply specified performance limits. For specified performance limits and associated test conditions, see the Electrical Characteristics table.

(2) All voltages are with respect to the potential at the GND pins.

(3) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be de-rated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

#### THERMAL PROPERTIES

| Junction-to-Ambient Thermal                                 | 100°C/W |

|-------------------------------------------------------------|---------|

| Resistance (θ <sub>JA</sub> ), YPA10 Package <sup>(1)</sup> |         |

Junction-to-ambient thermal resistance (θ<sub>JA</sub>) is taken from thermal measurements, performed under the conditions and guidelines set forth in the JEDEC standard JESD51-7. A 1" x 1", 4 layer, 1.5 oz. Cu board was used for the measurements.

www.ti.com

## ELECTRICAL CHARACTERISTICS<sup>(1)(2)</sup>

Limits in standard typeface are for  $T_A = T_J = 25^{\circ}$ C. Limits in **boldface** type apply over the full operating ambient temperature range ( $-25^{\circ}$ C  $\leq T_A = T_J \leq +85^{\circ}$ C). Unless otherwise noted, specifications apply to the LM3200 with:  $PV_{IN} = V_{DD} = EN = 3.6V$ , BYP = 0V.

| Symbol                     | Parameter                                   | Conditions                                       | Min   | Тур   | Max  | Units |

|----------------------------|---------------------------------------------|--------------------------------------------------|-------|-------|------|-------|

| V <sub>IN</sub>            | Input Voltage Range (3)                     | $PV_{IN} = V_{DD} = V_{IN}$                      | 2.7   |       | 5.5  | V     |

| V <sub>FB, MIN</sub>       | Feedback Voltage at<br>Minimum Setting      | $V_{CON} = 0.267V, V_{IN} = 3.6V$                | 0.75  | 0.800 | 0.85 | V     |

| V <sub>FB, MAX</sub>       | Feedback Voltage at<br>Maximum Setting      | V <sub>CON</sub> = 1.20V, V <sub>IN</sub> = 4.2V | 3.600 | 3.672 | V    |       |

| OVP                        | Over-Voltage Protection<br>Threshold        | (4)                                              |       | 330   | 400  | mV    |

| V <sub>BYPASS</sub> -      | Auto Bypass Detection<br>Negative Threshold | (5)                                              | 250   | 320   | mV   |       |

| V <sub>BYPASS+</sub>       | Auto Bypass Detection<br>Positive Threshold | (5)                                              | 450   | 540   | mV   |       |

| I <sub>SHDN</sub>          | Shutdown Supply<br>Current <sup>(6)</sup>   | $EN = SW = BYPOUT = V_{CON} = FB = 0V$           |       | 0.1   | 3    | μA    |

| I <sub>Q_PWM</sub>         | DC Bias Current into                        | $V_{CON} = 0.267V$ , FB = 2V, No-Load            |       | 720   | 850  | μA    |

| I <sub>Q_BYP</sub>         | V <sub>DD</sub>                             | $BYP = 3.6V, V_{CON} = 0V, No-Load$              |       | 720   | 850  | μA    |

| R <sub>DSON (P)</sub>      | Pin-Pin Resistance for<br>PFET              | I <sub>SW</sub> = 500mA                          |       | 320   | 450  | mΩ    |

| R <sub>DSON (N)</sub>      | Pin-Pin Resistance for<br>N-FET             | I <sub>SW</sub> = - 200mA                        |       | 310   | 450  | mΩ    |

| R <sub>DSON</sub><br>(BYP) | Pin-Pin Resistance for<br>Bypass FET        | I <sub>BYPOUT</sub> = 500mA                      |       | 85    | 120  | mΩ    |

| I <sub>LIM-PFET</sub>      | Switch Current Limit                        | (7)                                              | 700   | 820   | 940  | mA    |

| I <sub>LIM-BYP</sub>       | Bypass FET Current<br>Limit                 | (8)                                              | 800   | 1000  | 1200 | mA    |

| F <sub>OSC</sub>           | Internal Oscillator<br>Frequency            |                                                  | 1.7   | 2     | 2.2  | MHz   |

| V <sub>IH</sub>            | Logic High Input<br>Threshold for EN, BYP   |                                                  | 1.20  |       |      | V     |

| V <sub>IL</sub>            | Logic Low Input<br>Threshold for EN, BYP    |                                                  |       |       | 0.4  | V     |

| I <sub>PIN</sub>           | Pin Pull Down Current<br>for EN, BYP        | EN, BYP = 3.6V                                   |       | 5     | 10   | μA    |

| Gain                       | V <sub>CON</sub> to V <sub>OUT</sub> Gain   |                                                  |       | 3     |      | V/V   |

| I <sub>CON</sub>           | V <sub>CON</sub> Input Leakage<br>Current   | V <sub>CON</sub> = 1.2V                          |       | 10    |      | nA    |

(1) All voltages are with respect to the potential at the GND pins.

(2) Min and Max limits are specified by design, test, or statistical analysis. Typical numbers are not ensured, but do represent the most likely norm.

(3) The LM3200 is designed for mobile phone applications where turn-on after power-up is controlled by the system controller and where requirements for a small package size overrule increased die size for internal Under Voltage Lock-Out (UVLO) circuitry. Thus, it should be kept in shutdown by holding the EN pin low until the input voltage exceeds 2.7V.

(4) Over-Voltage protection (OVP) threshold is the voltage above the nominal VOUT where the OVP comparator turns off the PFET switch while in PWM mode.

(5) V<sub>IN</sub> is compared to the programmed output voltage (V<sub>OUT</sub>). When V<sub>IN</sub>–V<sub>OUT</sub> falls below V<sub>BYPASS</sub>- for longer than T<sub>BYP</sub> the Bypass FET turns on and the switching FETs turn off. This is called the Bypass mode. Bypass mode is exited when V<sub>IN</sub>–V<sub>OUT</sub> exceeds V<sub>BYPASS</sub><sup>+</sup> for longer than T<sub>BYP</sub>, and PWM mode returns. The hysterisis for the bypass detection threshold V<sub>BYPASS</sub><sup>+</sup> – V<sub>BYPASS</sub><sup>-</sup> will always be positive and will be approximately 200 mV(typ.).

(6) Shutdown current includes leakage current of PFET and Bypass FET.

(7) Electrical Characteristics table reflects open loop data (FB=0V and current drawn from SW pin ramped up until cycle by cycle current limit is activated). Refer to Typical Performance Characteristics (Open/Closed Loop Current Limit vs Temperature curve) for closed loop data and its variation with regards to supply voltage and temperature. Closed loop current limit is the peak inductor current measured in the application circuit by increasing output current until output voltage drops by 10%.

(8) Bypass FET current limit is defined as the load current at which the FB voltage is 1V lower than V<sub>IN</sub>.

#### SYSTEM CHARACTERISTICS

The following spec table entries are specified by design if the component values in the typical application circuit are used. **These parameters are not specified by production testing.**

| Symbol                | Parameter                                                             | Conditions                                                                                                                                                                                   | Min | Тур | Max | Units |

|-----------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>RESPONSE</sub> | Time for V <sub>OUT</sub> to Rise<br>from 0.8V to 3.4V in<br>PWM Mode | $ \begin{array}{l} V_{\text{IN}}=4.2V,C_{\text{OUT}}=4.7\;\mu\text{F},\\ R_{\text{LOAD}}=15\Omega\\ L=2.2\;\text{uH} \end{array} $                                                           |     | 25  |     | μs    |

| C <sub>CON</sub>      | V <sub>CON</sub> Input Capacitance                                    | V <sub>CON</sub> = 1V,<br>Test frequency = 100 kHz                                                                                                                                           |     |     | 15  | pF    |

| T <sub>ON_BYP</sub>   | Bypass FET Turn On<br>Time In Bypass Mode                             | $ \begin{array}{l} V_{\text{IN}}=3.6\text{V}, V_{\text{CON}}=0.267\text{V},\\ C_{\text{OUT}}=4.7\ \mu\text{F}, \text{R}_{\text{LOAD}}=15\Omega\\ \text{BYP}=\text{Low to High} \end{array} $ |     |     | 30  | μs    |

| T <sub>BYP</sub>      | Auto Bypass Detect<br>Delay Time                                      | (1)                                                                                                                                                                                          | 10  | 15  | 20  | μs    |

(1) V<sub>IN</sub> is compared to the programmed output voltage (V<sub>OUT</sub>). When V<sub>IN</sub>-V<sub>OUT</sub> falls below V<sub>BYPASS</sub>- for longer than T<sub>BYP</sub> the Bypass FET turns on and the switching FETs turn off. This is called the Bypass mode. Bypass mode is exited when V<sub>IN</sub>-V<sub>OUT</sub> exceeds V<sub>BYPASS</sub><sup>+</sup> for longer than T<sub>BYP</sub>, and PWM mode returns. The hysterisis for the bypass detection threshold V<sub>BYPASS</sub><sup>+</sup> - V<sub>BYPASS</sub><sup>-</sup> will always be positive and will be approximately 200 mV(typ.).

SNVS319C-NOVEMBER 2004-REVISED APRIL 2013

0.80

0.78

0.76

0.74

0.72

0.70

0.68

0.66

4.0

3.0

2.0

1.0

0.0

-1.0

-2.0

-3.0

-4.0

1.510

1.508

1.506

1.504

1.502

1.500

-40

OUTPUT VOLTAGE (V)

-40

SWITCHING FREQUENCY VARIATION (%)

2.5

QUIESCENT CURRENT (mA)

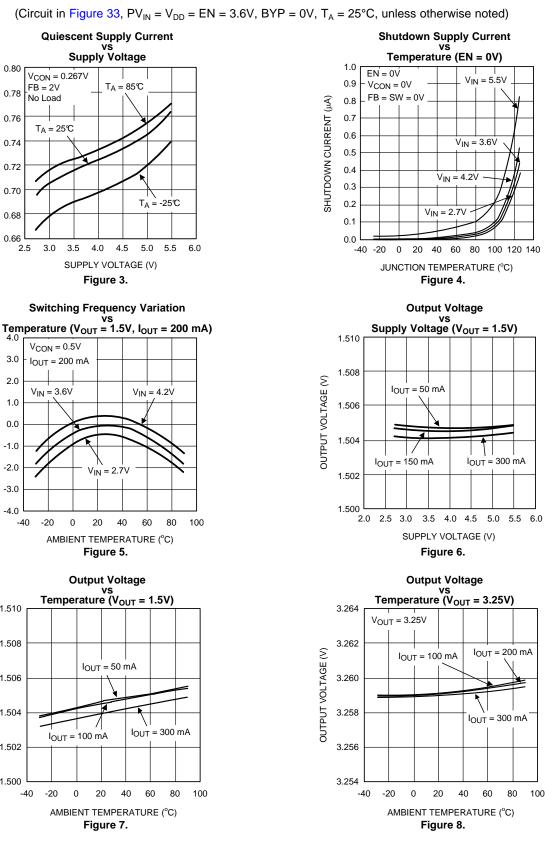

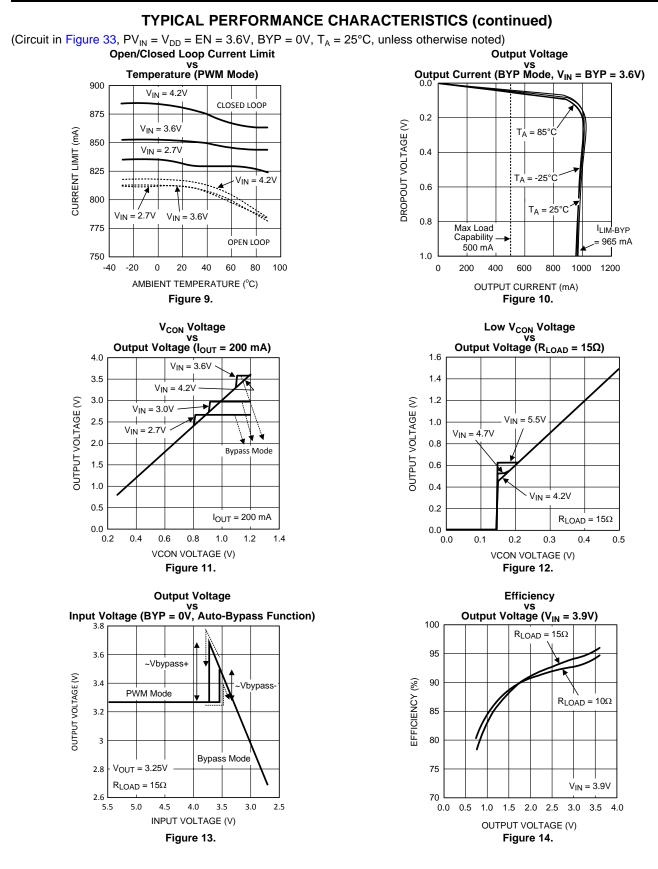

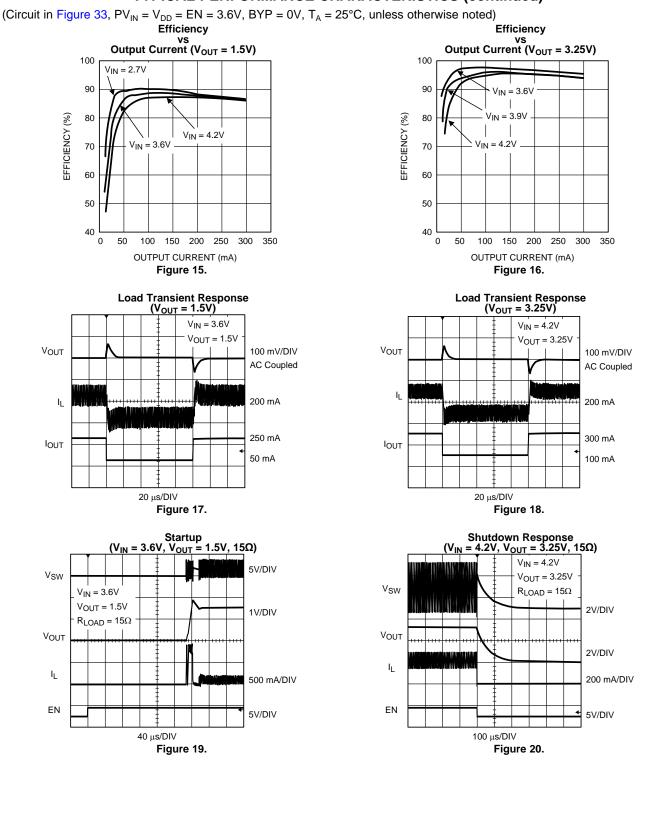

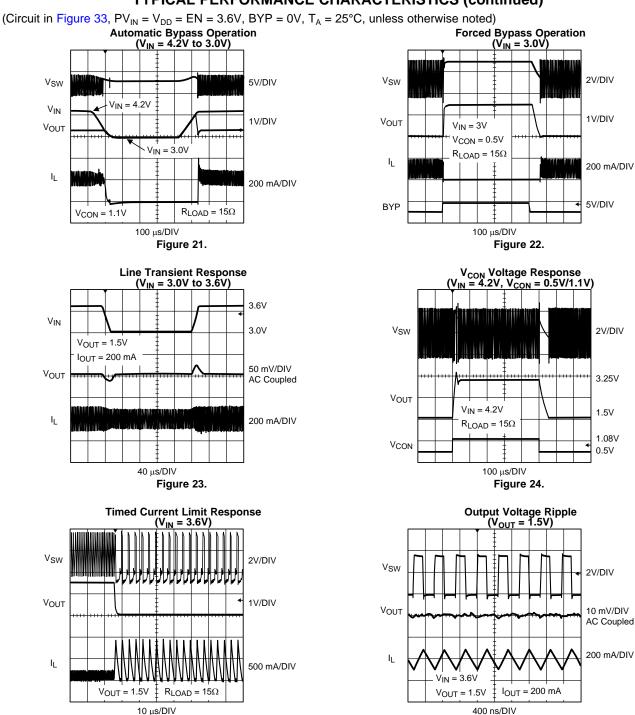

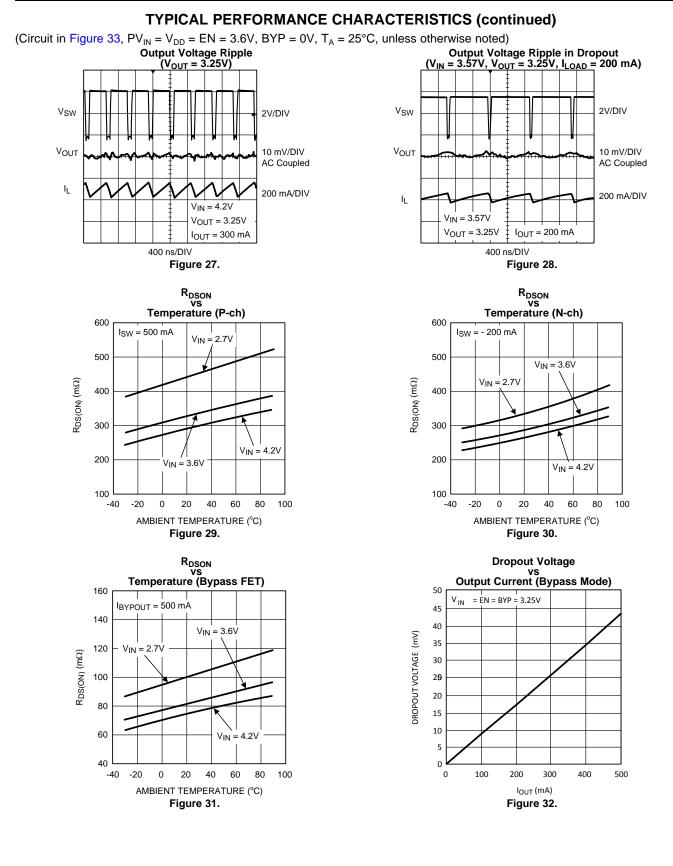

## **TYPICAL PERFORMANCE CHARACTERISTICS**

SNVS319C-NOVEMBER 2004-REVISED APRIL 2013

7

TEXAS INSTRUMENTS

www.ti.com

SNVS319C-NOVEMBER 2004-REVISED APRIL 2013

SNVS319C-NOVEMBER 2004-REVISED APRIL 2013

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

Figure 25.

Figure 26.

TEXAS INSTRUMENTS

www.ti.com

#### SNVS319C-NOVEMBER 2004-REVISED APRIL 2013

ÈXAS

**NSTRUMENTS**

#### SNVS319C-NOVEMBER 2004-REVISED APRIL 2013

www.ti.com

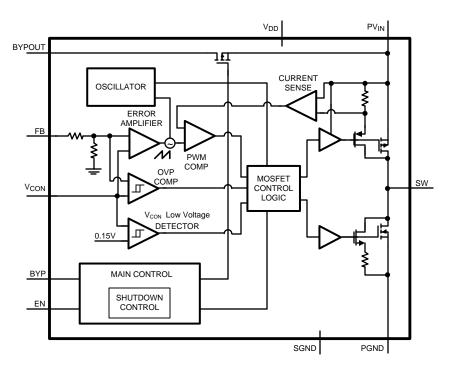

#### **OPERATION DESCRIPTION**

The LM3200 is a simple, step-down DC-DC converter with a bypass switch, optimized for powering RF power amplifiers (PAs) in mobile phones, portable communicators, and similar battery powered RF devices. It is designed to allow the RF PA to operate at maximum efficiency over a wide range of power levels from a single Li-Ion battery cell. It is based on current-mode buck architecture, with synchronous rectification for high efficiency. It is designed for a maximum load capability of 300 mA in PWM mode and 500 mA in bypass mode. Maximum load range may vary from this depending on input voltage, output voltage and the inductor chosen.

The device has three-pin selectable operating modes required for powering RF PAs in mobile phones and other sophisticated portable device with complex power management needs. Fixed-frequency PWM operation offers regulated output at high efficiency while minimizing interference with sensitive IF and data acquisition circuits. Bypass mode (Forced or Automatic) turns on an internal FET bypass switch to power the PA directly from the battery. Shutdown mode turns the device off and reduces battery consumption to  $0.1 \,\mu$ A (typ).

DC PWM mode output voltage precision is +/-2% for 3.6V<sub>OUT</sub>. Efficiency is typically around 96% for a 120 mA load with 3.2V output, 3.6V input. PWM mode quiescent current is 0.7 mA typ. The output voltage is dynamically programmable from 0.8V to 3.6V by adjusting the voltage on the control pin without the need for external feedback resistors. This ensures longer battery life by being able to change the PA supply voltage dynamically depending on its transmitting power.

Additional features include current overload protection, over voltage protection and thermal shutdown.

The LM3200 is constructed using a chip-scale 10-pin DSBGA package. This package offers the smallest possible size, for space-critical applications such as cell phones, where board area is an important design consideration. Use of a high switching frequency (2 MHz) reduces the size of external components. As shown in Figure 33, only few external components are required for implementation. Use of a DSBGA package requires special design considerations for implementation. (See DSBGA PACKAGE ASSEMBLY AND USE) Its fine bump-pitch requires careful board design and precision assembly equipment. Use of this package is best suited for opaque-case applications, where its edges are not subject to high-intensity ambient red or infrared light. Also, the system controller should set EN low during power-up and other low supply voltage conditions. (See Shutdown Mode)

Figure 33. Typical Operating System Circuit

#### **Circuit Operation**

Referring to Figure 33, the LM3200 operates as follows. During the first part of each switching cycle, the control block in the LM3200 turns on the internal PFET (P-channel MOSFET) switch. This allows current to flow from the input through the inductor to the output filter capacitor and load. The inductor limits the current to a ramp with a slope of around  $(V_{IN}-V_{OUT})/L$ , by storing energy in a magnetic field. During the second part of each cycle, the controller turns the PFET switch off, blocking current flow from the input, and then turns the NFET (N-channel MOSFET) synchronous rectifier on. In response, the inductor's magnetic field collapses, generating a voltage that forces current from ground through the synchronous rectifier to the output filter capacitor and load. As the stored energy is transferred back into the circuit and depleted, the inductor current ramps down with a slope around  $V_{OUT}/L$ . The output filter capacitor stores charge when the inductor current is going high, and releases it when inductor current is going low, smoothing the voltage across the load.

The output voltage is regulated by modulating the PFET switch on time to control the average current sent to the load. The effect is identical to sending a duty-cycle modulated rectangular wave formed by the switch and synchronous rectifier at SW to a low-pass filter formed by the inductor and output filter capacitor. The output voltage is equal to the average voltage at the SW pin.

#### PWM Mode

While in PWM (Pulse Width Modulation) mode, the output voltage is regulated by switching at a constant frequency and then modulating the energy per cycle to control power to the load. Energy per cycle is set by modulating the PFET switch on-time pulse width to control the peak inductor current. This is done by comparing the signal from the PFET drain current to a slope-compensated reference current generated by the error amplifier. At the beginning of each cycle, the clock turns on the PFET switch, causing the inductor current to ramp up. When the current sense signal ramps past the error amplifier signal, the PWM comparator turns off the PFET switch and turns on the NFET synchronous rectifier, ending the first part of the cycle. If an increase in load pulls the output down, the error amplifier output increases, which allows the inductor current to ramp higher before the comparator turns off the PFET. This increases the average current sent to the output and adjusts for the increase in the load. Before appearing at the PWM comparator, a slope compensation ramp from the oscillator is subtracted from the error signal for stability of the current feedback loop. The minimum on-time of PFET in PWM mode is 50 ns (typ).

#### Bypass Mode

The LM3200 contains an internal PFET switch for bypassing the PWM DC-DC converter during Bypass mode. In Bypass mode, this PFET is turned on to power the PA directly from the battery for maximum RF output power. When the part operates in the Bypass mode, the output voltage will be the input voltage less the voltage drop across the resistance of the bypass PFET. Bypass mode is more efficient than operating in PWM mode at 100% duty cycle because the resistance of the bypass PFET is less than the series resistance of the PWM PFET and inductor. This translates into higher voltage available on the output in Bypass mode, for a given battery voltage. The part can be placed in bypass mode by sending BYP pin high. This is called Forced Bypass Mode and it remains in bypass mode until BYP pin goes low.

Alternatively the part can go into Bypass mode automatically. This is called Auto-bypass mode or Automatic Bypass mode. The bypass switch turns on when the difference between the input voltage and programmed output voltage is less than 250 mV (typ.) for more than the bypass delay time of 15  $\mu$ s (typ.). The bypass switch turns off when the input voltage is higher than the programmed output voltage by 450 mV (typ.) for longer than the bypass delay time. The bypass delay time is provided to prevent false triggering into Automatic Bypass mode by either spikes or dips in V<sub>IN</sub>. This method is very system resource friendly in that the Bypass PFET is turned on automatically when the input voltage gets close to the output voltage, typical scenario of a discharging battery. It is also turned off automatically when the input voltage causing Bypass PFET to turn on and off automatically. It is recommended to connect BYPOUT pin directly to the output capacitor with a separate trace and not to the FB pin.

#### **Operating Mode Selection Control**

The BYP digital input pin is used to select between PWM/Auto-bypass and Bypass operating mode. Setting BYP pin high (>1.2V) places the device in Forced Bypass mode. Setting BYP pin low (<0.4V) or leaving it floating places the device in PWM/Auto-bypass mode.

Bypass and PWM operation overlap during the transition between the two modes. This transition time is approximately 31  $\mu$ s when changing from PWM to Bypass mode, and 15  $\mu$ s when changing from Bypass to PWM mode. This helps prevent under or overshoots during the transition period between PWM and Bypass modes.

#### Shutdown Mode

Setting the EN digital pin low (<0.4V) places the LM3200 in a 0.1  $\mu$ A (typ.) Shutdown mode. During shutdown, the PFET switch, NFET synchronous rectifier, reference voltage source, control and bias circuitry of the LM3200 are turned off. Setting EN high (>1.2V) enables normal operation.

www.ti.com

EN should be set low to turn off the LM3200 during power-up and under voltage conditions when the power supply is less than the 2.7V minimum operating voltage. The LM3200 is designed for compact portable applications, such as mobile phones. In such applications, the system controller determines power supply sequencing and requirements for small package size outweigh the benefit of including UVLO (Under Voltage Lock-Out) circuitry.

#### Dynamically Adjustable Output Voltage

The LM3200 features dynamically adjustable output voltage to eliminate the need for external feedback resistors. The output can be set from 0.8V to 3.6V by changing the voltage on the analog  $V_{CON}$  pin. This feature is useful in PA applications where peak power is needed only when the handset is far away from the base station or when data is being transmitted. In other instances, the transmitting power can be reduced. Hence the supply voltage to the PA can be reduced, promoting longer battery life. See Setting the Output Voltage for further details.

#### **Over Voltage Protection**

The LM3200 has an over voltage comparator that prevents the output voltage from rising too high. If the output voltage rises to 330 mV over its target, the OVP comparator inhibits PWM operation to skip pulses until the output voltage returns to the target. Typically the OVP comparator may be activated during  $V_{CON}$  steps particularly steps from a high to a low voltage. During the over voltage protection mode, both the PWM PFET and the NFET synchronous rectifier are off. When the part comes out of the over voltage protection mode, the NFET synchronous rectifier remains off for approximately 3.5  $\mu$ s to avoid inductor current going negative.

#### Internal Synchronous Rectification

While in PWM mode, the LM3200 uses an internal NFET as a synchronous rectifier to reduce rectifier forward voltage drop and associated power loss. Synchronous rectification provides a significant improvement in efficiency whenever the output voltage is relatively low compared to the voltage drop across an ordinary rectifier diode.

With medium and heavy loads, the internal NFET synchronous rectifier is turned on during the inductor current down slope in the second part of each cycle. The synchronous rectifier is turned off prior to the next cycle. There is no zero cross detect, which means that the NFET can conduct current in both directions and inductor current is always continuous. The advantage of this method is that the part remains in PWM mode at light loads or no load conditions. The NFET has a current limit. The NFET is designed to conduct through its intrinsic body diode during transient intervals before it turns on, eliminating the need for an external diode.

## **Current Limiting**

A current limit feature allows the LM3200 to protect itself and external components during overload conditions. In PWM mode, a 940 mA (max.) cycle-by-cycle current limit is normally used. If an excessive load pulls the output voltage down to below approximately 0.375V, indicating a possible short to ground, then the device switches to a timed current limit mode. In timed current limit mode, the internal PFET switch is turned off after the current comparator trips, and the beginning of the next cycle is inhibited for 3.5 µs to force the instantaneous inductor current to ramp down to a safe value. After the 3.5 µs interval, the internal PFET is turned on again. This cycle is repeated until the load is reduced and the output voltage exceeds approximately 0.375V. Therefore, the device may not startup if an excessive load is connected to the output when the device is enabled. The synchronous rectifier is off in the timed current limit mode. Timed current limit prevents the loss of current control seen in some products when the output voltage is pulled low in serious overload conditions.

A current limit is also provided for the NFET. This is approximately -500 mA. Both the NFET and the PFET are turned off in negative current limit until the PFET is turned on again at the beginning of the next cycle. The negative current limit inhibits buildup of excessive inductor current. In the Bypass mode, the bypass current limit is 1000 mA(typ). The output voltage drops when the bypass current limit kicks in.

#### Thermal Overload Protection

The LM3200 has a thermal overload protection function that operates to protect the device from short-term misuse and overload conditions. When the junction temperature exceeds around 150°C, the device inhibits operation. Both the PFET and the NFET are turned off in PWM mode, and the Bypass PFET is turned off in Bypass mode. When the temperature drops below 130°C, normal operation resumes. Prolonged operation in thermal overload conditions may damage the device and is considered bad practice.

#### Application Information

#### SETTING THE OUTPUT VOLTAGE

The LM3200 features a pin-controlled variable output voltage to eliminate the need for external feedback resistors. It can be programmed for an output voltage from 0.8V to 3.6V by setting the voltage on the  $V_{CON}$  pin, as in the following formula:

$$V_{OUT} = 3 \times V_{CON}$$

When V<sub>CON</sub> is between 0.267V and 1.20V, the output voltage will follow proportionally by 3 times of V<sub>CON</sub>.

If  $V_{CON}$  is over 1.20V ( $V_{OUT}$  = 3.6V), sub-harmonic oscillation may occur because of insufficient slope compensation.

If  $V_{CON}$  voltage is less than 0.267V ( $V_{OUT} = 0.8V$ ), the output voltage may not be regulated due to the required on-time being less than the minimum on-time (50ns). The output voltage can go lower than 0.8V providing a limited  $V_{IN}$  range is used. Refer to Typical Performance Characteristics (Low  $V_{CON}$  Voltage vs Output Voltage curve) for details. This curve is for a typical part and there could be part to part variation for output voltages less than 0.8V over the limited  $V_{IN}$  range. In addition, if  $V_{CON}$  is less than approx. 0.15V, the LM3200 output is turned off, but the internal bias circuits are still active.

#### INDUCTOR SELECTION

A 2.2  $\mu$ H inductor with saturation current rating over 940 mA is recommended for almost all applications. The inductor resistance should be less than 0.3 $\Omega$  for better efficiency. Table 1 lists suggested inductors and suppliers.

| Model             | Size (WxLxH) [mm] | Vendor    |  |  |  |  |  |  |  |

|-------------------|-------------------|-----------|--|--|--|--|--|--|--|

| DO3314-222MX      | 3.3 x 3.3 x 1.4   | Coilcraft |  |  |  |  |  |  |  |

| VLF3010AT-2R2M1R0 | 2.6 x 2.8 x 1.0   | TDK       |  |  |  |  |  |  |  |

| MIPW3226D2R2M     | 3.2 x 2.6 x 1.0   | FDK       |  |  |  |  |  |  |  |

| LPO3310-222MX     | 3.3 x 3.3 x 1.0   | Coilcraft |  |  |  |  |  |  |  |

Table 1. Suggested Inductors and Suppliers

If a higher value inductor is used the LM3200 may become unstable and exhibit large under or over shoot during line, load and  $V_{CON}$  transients. If smaller inductance value is used, slope compensation maybe insufficient causing sub-harmonic oscillations. The device has been tested with inductor values in the range 1.55µH to 3.1µH to account for inductor tolerances.

For low-cost applications, an unshielded bobbin inductor can be used. For noise-critical applications, an unshielded or shielded-bobbin inductor should be used. A good practice is to layout the board with footprints accommodating both types for design flexibility. This allows substitution of an unshielded inductor, in the event that noise from low-cost bobbin models is unacceptable. Saturation occurs when the magnetic flux density from current through the windings of the inductor exceeds what the inductor's core material can support with a corresponding magnetic field. This can cause poor efficiency, regulation errors or stress to a DC-DC converter like the LM3200.

#### CAPACITOR SELECTION

The LM3200 is designed to be used with ceramic capacitors. Use a 10  $\mu$ F ceramic capacitor for the input and a 4.7  $\mu$ F ceramic capacitor for the output. Ceramic capacitors such as X5R, X7R and B are recommended for both filters. These provide an optimal balance between small size, cost, reliability and performance for cell phones and similar applications. Table 2 lists suggested capacitors and suppliers.

| Model          | Vendor      |

|----------------|-------------|

| LMK212BJ475MG  | Taiyo-Yuden |

| C2012X5R1A475K | ТDК         |

| GRM188R61A475K | Murata      |

| C3216X5R1A106K | ТDК         |

#### Table 2. Suggested Capacitors and Suppliers

SNVS319C-NOVEMBER 2004-REVISED APRIL 2013

(1)

www.ti.com

The DC bias characteristics of the capacitor must be considered when making the selection. If smaller case size such as 0603 is selected, the dc bias could reduce the cap value by as much as 40%, in addition to the 20% tolerances and 15% temperature coefficients. Request dc bias curves from manufacturer when making selection. The device has been designed to be stable with output capacitors as low as 3  $\mu$ F to account for capacitor tolerances. This value includes dc bias reduction, manufacturing tolerences and temp coefficients.

The input filter capacitor supplies AC current drawn by the PFET switch of the LM3200 in the first part of each cycle and reduces the voltage ripple imposed on the input power source. The output filter capacitor absorbs the AC inductor current, helps maintain a steady output voltage during transient load changes and reduces output voltage ripple. These capacitors must be selected with sufficient capacitance and sufficiently low ESR (Equivalent Series Resistance) to perform these functions. The ESR of the filter capacitors is generally a major factor in voltage ripple.

#### DSBGA PACKAGE ASSEMBLY AND USE

Use of the DSBGA package requires specialized board layout, precision mounting and careful re-flow techniques, as detailed in TI Application Note 1112 (SNVA009). Refer to the section *Surface Mount Technology (SMD) Assembly Considerations*. For best results in assembly, alignment ordinals on the PC board should be used to facilitate placement of the device. The pad style used with DSBGA package must be the NSMD (non-solder mask defined) type. This means that the solder-mask opening is larger than the pad size. This prevents a lip that otherwise forms if the solder-mask and pad overlap, from holding the device off the surface of the board and interfering with mounting. See Application Note 1112 (SNVA009) for specific instructions how to do this. The 10-Bump package used for the LM3200 has 300 micron solder balls and requires 10.82 mil pads for mounting on the circuit board. The trace to each pad should enter the pad with a 90° entry angle to prevent debris from being caught in deep corners. Initially, the trace to each pad should be 6-7 mil wide, for a section approximately 6 mil long or longer, as a thermal relief. Then each trace should neck up or down to its optimal width. The important criterion is symmetry. This ensures the solder bumps on the LM3200 re-flow evenly and that the device solders level to the board. In particular, special attention must be paid to the pads for bumps B3, C3 and D3. Because PGND and  $PV_{IN}$  are typically connected to large copper planes, inadequate thermal relief can result in inadequate re-flow of these bumps.

The DSBGA package is optimized for the smallest possible size in applications with red or infrared opaque cases. Because the DSBGA package lacks the plastic encapsulation characteristic of larger devices, it is vulnerable to light. Backside metalization and/or epoxy coating, along with front-side shading by the printed circuit board, reduce this sensitivity. However, the package has exposed die edges. In particular, DSBGA devices are sensitive to light, in the red and infrared range, shining on the package's exposed die edges.

Do not use or power-up the LM3200 while subjecting it to high intensity red or infrared light; otherwise degraded, unpredictable or erratic operation may result. Examples of light sources with high red or infrared content include the sun and halogen lamps. Place the device in a case opaque to red or infrared light.

#### BOARD LAYOUT CONSIDERATIONS

PC board layout is an important part of DC-DC converter design. Poor board layout can disrupt the performance of a DC-DC converter and surrounding circuitry by contributing to EMI, ground bounce, and resistive voltage loss in the traces. These can send erroneous signals to the DC-DC converter, resulting in poor regulation or instability. Poor layout can also result in re-flow problems leading to poor solder joints between the DSBGA package and board pads. Poor solder joints can result in erratic or degraded performance. Good layout for the LM3200 can by implemented by following a few simple design rules.

- 1. Place the LM3200 on 10.82 mil pads. As a thermal relief, connect to each pad with a 7 mil wide, approximately 7 mil long traces, and when incrementally increase each trace to its optimal width. The important criterion is symmetry to ensure the solder bumps on the LM3200 re-flow evenly (see DSBGA Package Assembly and Use).

- Place the LM3200, inductor and filter capacitors close together and make the trace short. The traces between these components carry relatively high switching currents and act as antennas. Following this rule reduces radiated noise. Place the capacitors and inductor close to the LM3200. The input capacitor should be placed right next to the device between PV<sub>IN</sub> and PGND pin.

- 3. Arrange the components so that the switching current loops curl in the same direction. During the first half of each cycle, current flows from the input filter capacitor, through the LM3200 and inductor to the output filter capacitor and back through ground, forming a current loop. In the second half of each cycle, current is pulled up from ground, through the LM3200 by the inductor, to the output filter capacitor and then back through the through the inductor.

ground, forming a second current loop. Routing these loops so the current curls in the same direction, prevents magnetic field reversal between the two half-cycles and reduces radiated noise.

- 4. Connect the ground pins of the LM3200, and filter capacitors together using generous component side copper fill as a pseudo-ground plane. Then connect this to the ground-plane (if one is used) with several vias. This reduces ground plane noise by preventing the switching currents from circulating through the ground plane. It also reduces ground bounce at the LM3200 by giving it a low impedance ground connection.

- 5. Use wide traces between the power components and for power connections to the DC-DC converter circuit. This reduces voltage errors caused by resistive losses across the traces.

- 6. Route noise sensitive traces, such as the voltage feedback trace, away from noisy traces and components. The voltage feedback trace must remain close to the LM3200 circuit and should be routed directly from FB pin to V<sub>OUT</sub> at the output capacitor. A good approach is to route the feedback trace on another layer and to have a ground plane between the top layer and the layer on which the feedback trace is routed. This reduces EMI radiation on to the DC-DC converter's own voltage feedback trace.

- 7. It is recommended to connect BYPOUT pin to V<sub>OUT</sub> at the output capacitor using a separate trace, instead of connecting it directly to the FB pin for better noise immunity.

| Cł | nanges from Revision B (April 2013) to Revision C P | age  |

|----|-----------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format  | . 17 |

www.ti.com

8-Oct-2015

## PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|--------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                |              | (4/5)          |         |

| LM3200TL/NOPB    | ACTIVE | DSBGA        | YPA     | 10   | 250     | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -25 to 85    | SCUB           | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(<sup>6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OPTION ADDENDUM

8-Oct-2015

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

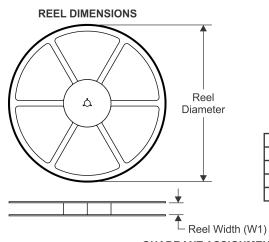

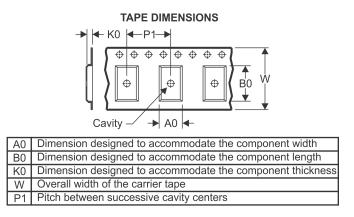

#### TAPE AND REEL INFORMATION

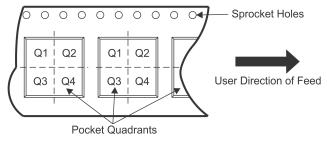

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |

|-----------------------------|

|-----------------------------|

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM3200TL/NOPB | DSBGA           | YPA                | 10 | 250 | 178.0                    | 8.4                      | 1.96       | 2.31       | 0.76       | 4.0        | 8.0       | Q1               |

TEXAS INSTRUMENTS

www.ti.com

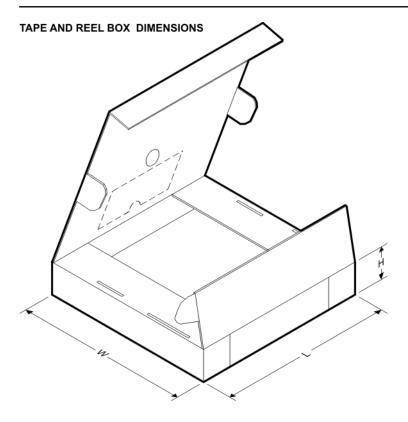

# PACKAGE MATERIALS INFORMATION

2-Sep-2015

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|-----|-------------|------------|-------------|

| LM3200TL/NOPB | DSBGA        | YPA             | 10   | 250 | 210.0       | 185.0      | 35.0        |

# YPA0010

B. This drawing is subject to change without notice.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |  |  |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|--|--|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |  |  |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |  |  |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |  |  |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |  |  |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |  |  |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |  |  |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |  |  |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |  |  |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |  |  |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |  |  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |  |  |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |  |  |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |  |  |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated