SBVS049D - MAY 2004 - REVISED AUGUST 2010

# Dual 250 mA Output, UltraLow Noise, High PSRR, Low-Dropout Linear Regulator

Check for Samples: TPS71202, TPS71219, TPS71229, TPS71247, TPS71256, TPS71257

## **FEATURES**

- Dual 250 mA High-Performance RF LDOs

- Available in Fixed and Adjustable Voltage Options (1.2 V to 5.5 V)

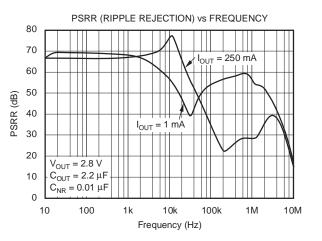

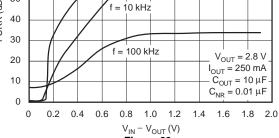

- High PSRR: 65 dB at 10 kHz

- UltraLow Noise: 32 µVrms

- Fast Start-Up Time: 60 μs

- Stable with 2.2 µF Ceramic Capacitor

- Excellent Load/Line Transient Response

- Very Low Dropout Voltage: 125 mV at 250 mA

- Independent Enable Pins

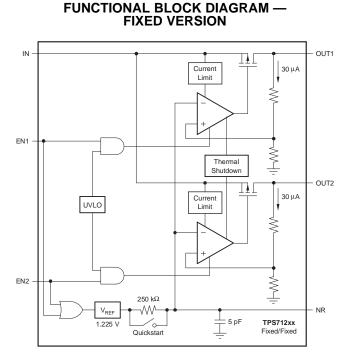

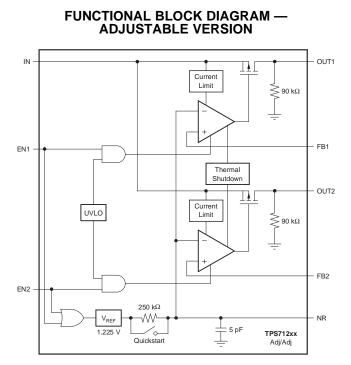

- Thermal Shutdown and Independent Current Limit

- Available in Thermally-Enhanced SON Package: 3mm x 3mm x 1mm

## **APPLICATIONS**

- Cellular and Cordless Phones

- Wireless PDA/Handheld Products

- PCMCIA/Wireless LAN Applications

- Digital Camera/Camcorder/Internet Audio

- DSP/FPGA/ASIC/Controllers and Processors

## DESCRIPTION

The TPS712xx family of low-dropout (LDO) voltage regulators is tailored to noise-sensitive and RF applications. These products feature dual 250 mA LDOs with ultralow noise, high power-supply rejection ratio (PSRR), and fast transient and start-up response. Each regulator output is stable with low-cost 2.2 µF ceramic output capacitors and features very low dropout voltages (125 mV typical at 250 mA). Each regulator achieves fast start-up times (approximately 60 µs with a 0.001 µF bypass capacitor) while consuming very low quiescent current (300 µA typical with both outputs enabled). When the device is placed in standby mode, the supply current is reduced to less than 0.3 µA typical. Each regulator exhibits approximately 32 µVrms of output voltage noise with  $V_{OUT}$  = 2.8 V and a 0.01  $\mu$ F noise reduction (NR) capacitor. Applications with analog components that are noise-sensitive, such as portable RF electronics, will benefit from high PSRR, low noise, and fast line and load transient features. The TPS712 family is offered in a thin 3mm x 3mm SON package and is fully specified from -40°C to +125°C (T<sub>J</sub>).

DRC PACKAGE 3mm x 3mm SON (TOP VIEW) 10 IN 11 EN1 NC FB1/NC 9 2 OUT1 3 EN2 8 OUT2 4 7 FB2/NC GND 51 6 NR

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## TPS71202, TPS71219 TPS71229, TPS71247 TPS71256, TPS71257 SBVS049D - MAY 2004 - REVISED AUGUST 2010

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

ODDEDING INFORMATION(1)

| ORDERING INFORMATION ** |                   |                   |                      |                                        |                    |                    |                              |  |  |  |  |  |

|-------------------------|-------------------|-------------------|----------------------|----------------------------------------|--------------------|--------------------|------------------------------|--|--|--|--|--|

|                         | VOLTA             | GE (V)            | PACKAGE-             | SPECIFIED                              |                    |                    |                              |  |  |  |  |  |

| PRODUCT                 | V <sub>OUT1</sub> | V <sub>OUT2</sub> | LEAD<br>(DESIGNATOR) | TEMPERATURE<br>RANGE (T <sub>J</sub> ) | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |  |  |  |  |  |

| TD074000                | Adjustable        | Adjustable        |                      | 10°C to 1125°C                         |                    | TPS71202DRCT       | Tape and Reel, 250           |  |  |  |  |  |

| TPS71202                | Adjustable        | Adjustable        | SON-10 (DRC)         | -40°C to +125°C                        | ARQ                | TPS71202DRCR       | Tape and Reel, 3000          |  |  |  |  |  |

| TD074040                | 1.0.1/            | Adjustable        |                      | 10°C to 1125°C                         |                    | TPS71219DRCT       | Tape and Reel, 250           |  |  |  |  |  |

| TPS71219 1.             | 1.8 V             | Adjustable        | SON-10 (DRC)         | -40°C to +125°C                        | ARW                | TPS71219DRCR       | Tape and Reel, 3000          |  |  |  |  |  |

| TPS71229                | 2.8 V             | Adjustable        | SON-10 (DRC)         | -40°C to +125°C                        | ARU                | TPS71229DRCT       | Tape and Reel, 250           |  |  |  |  |  |

| 195/1229                | 2.0 V             | Adjustable        | 30N-10 (DRC)         | -40 C 10 + 125 C                       | ARU                | TPS71229DRCR       | Tape and Reel, 3000          |  |  |  |  |  |

| TD074047                | 4.0.1/            | 0.05.1/           |                      | 10°C to 1105°C                         | 400                | TPS71247DRCT       | Tape and Reel, 250           |  |  |  |  |  |

| TPS71247                | 1.8 V             | 2.85 V            | SON-10 (DRC)         | -40°C to +125°C                        | ARS                | TPS71247DRCR       | Tape and Reel, 3000          |  |  |  |  |  |

| TD074050                | 2.0.1/            | 0.0.1/            |                      | 10°C to 1105°C                         |                    | TPS71256DRCT       | Tape and Reel, 250           |  |  |  |  |  |

| TPS71256                | 2.8 V             | 2.8 V             | SON-10 (DRC)         | -40°C to +125°C                        | ARV                | TPS71256DRCR       | Tape and Reel, 3000          |  |  |  |  |  |

| TD074057                |                   | 0.05.1/           |                      | 10°C to 1105°C                         | ADT                | TPS71257DRCT       | Tape and Reel, 250           |  |  |  |  |  |

| TPS71257                | 2.85 V            | 2.85 V            | SON-10 (DRC)         | -40°C to +125°C                        | ART                | TPS71257DRCR       | Tape and Reel, 3000          |  |  |  |  |  |

(1) For the most current package and ordering information, see the Package Ordering Addendum located at the end of this data sheet.

## **ABSOLUTE MAXIMUM RATINGS**

over operating junction temperature range unless otherwise noted<sup>(1)</sup>

|                                            | TPS712xx                      | UNIT |

|--------------------------------------------|-------------------------------|------|

| V <sub>IN</sub> range                      | -0.3 to 6.0                   | V    |

| V <sub>EN1</sub> , V <sub>EN2</sub> range  | -0.3 to V <sub>IN</sub> + 0.3 | V    |

| V <sub>OUT</sub> range                     | -0.3 to 6.0                   | V    |

| Peak output current                        | Internally limited            |      |

| Output short-circuit duration              | Indefinite                    |      |

| Continuous total power dissipation         | See Dissipation Ratings Ta    | ble  |

| Junction temperature range, T <sub>J</sub> | -40 to +150                   | °C   |

| Storage temperature range                  | -65 to +150                   | °C   |

| ESD rating, HBM                            | 2                             | kV   |

| ESD rating, CDM                            | 500                           | V    |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under the Electrical Characteristics is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

|                         | THERMAL METRIC <sup>(1)(2)</sup>             | TPS712xx      |       |

|-------------------------|----------------------------------------------|---------------|-------|

|                         |                                              | DRC (10 PINS) | UNITS |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 49.6          |       |

| $\theta_{\text{JCtop}}$ | Junction-to-case (top) thermal resistance    | 70.0          |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 17.8          | °C/M  |

| ΨJT                     | Junction-to-top characterization parameter   | 0.6           | °C/W  |

| Ψјв                     | Junction-to-board characterization parameter | 15.2          |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance | 5.2           |       |

For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

For thermal estimates of this device based on PCB copper area, see the TI PCB Thermal Calculator.

2 Submit Documentation Feedback

Product Folder Link(s): TPS71202 TPS71219 TPS71229 TPS71247 TPS71256 TPS71257

www.ti.com

#### **ELECTRICAL CHARACTERISTICS**

Over operating temperature range ( $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ),  $V_{IN} =$  highest  $V_{OUT(nom)} + 1.0$  V or 2.7 V (whichever is greater),  $I_{OUT} = 1$  mA,  $V_{EN1, 2} = 1.2$  V,  $C_{OUT} = 10 \,\mu$ F,  $C_{NR} = 0.01 \,\mu$ F, and adjustable LDOs are tested at  $V_{OUT} = 3.0$  V, unless otherwise noted. Typical values are at  $T_J = +25^{\circ}C$ .

|                                           | PARAMETER                                                            |                                                                                              | TE                                                            | EST CONDITIONS                                           | MIN                  | TYP   | MAX                 | UNIT |  |  |

|-------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|----------------------|-------|---------------------|------|--|--|

| V <sub>IN</sub>                           | Input voltage range <sup>(1)</sup>                                   |                                                                                              |                                                               |                                                          | 2.7                  |       | 5.5                 | V    |  |  |

| V <sub>FB</sub>                           | Internal reference (adjusta                                          | able LDOs)                                                                                   |                                                               |                                                          | 1.200                | 1.225 | 1.250               | V    |  |  |

|                                           | Output voltage range (adjustable LDOs)                               |                                                                                              |                                                               |                                                          | V <sub>FB</sub>      | 5.    | 5 - V <sub>DO</sub> | V    |  |  |

| V <sub>OUT</sub>                          |                                                                      | Nominal                                                                                      | T <sub>J</sub> = +25°C, I <sub>OUT</sub> = 0 mA               |                                                          | -1.5                 |       | +1.5                |      |  |  |

|                                           | Accuracy <sup>(1)</sup>                                              | $\begin{array}{l} \text{Over } V_{\text{IN}}, \\ I_{\text{OUT}}, \text{ and } T \end{array}$ | $V_{OUT}$ + 1.0 V<br>0 $\mu$ A $\leq$ I <sub>OUT</sub> $\leq$ | -3                                                       | ±1                   | +3    | %                   |      |  |  |

| ΔV <sub>OUT</sub> %/ΔV <sub>IN</sub>      | Line regulation <sup>(1)</sup>                                       |                                                                                              | V <sub>OUT</sub> + 1.0 V                                      | $\leq V_{IN} \leq 5.5 V$                                 |                      | 0.05  |                     | %/V  |  |  |

| ΔV <sub>OUT</sub> %/ΔI <sub>OU</sub><br>τ | Load regulation                                                      |                                                                                              | 0 μA ≤ I <sub>OUT</sub> ≤                                     | 250 mA                                                   |                      | 0.8   |                     | %/mA |  |  |

| V <sub>DO</sub>                           | Dropout voltage <sup>(2)</sup><br>( $V_{IN} = V_{OUT(nom)} - 0.1V$ ) | 2.8 V,<br>2.85 V<br>Adjustable                                                               | I <sub>OUT1</sub> = I <sub>OUT2</sub> = 250 mA                |                                                          |                      | 125   | 230                 | mV   |  |  |

| I <sub>CL</sub>                           | Output current limit                                                 | į                                                                                            | $V_{OUT} = 0.9 \times$                                        | V <sub>OUT(nom)</sub>                                    | 400                  | 600   | 800                 | mA   |  |  |

| I <sub>GND</sub>                          | Crowned min comment                                                  | One LDO<br>enabled                                                                           | I <sub>OUT</sub> = 1 mA (enabled channel)                     |                                                          |                      | 190   | 250                 | ٨    |  |  |

|                                           | Ground pin current                                                   | Both LDOs<br>enabled                                                                         | $I_{OUT1} = I_{OUT2}$                                         | = 1 mA to 250 mA                                         |                      | 300   | 600                 | μA   |  |  |

| I <sub>SHDN</sub>                         | Shutdown current <sup>(3)</sup>                                      |                                                                                              | $V_{EN} \le 0.4 \text{ V}, 0.4 \text{ V}$                     |                                                          | 0.3                  | 2.0   | μA                  |      |  |  |

| I <sub>FB</sub>                           | FB pin current (adjustable                                           | LDOs)                                                                                        |                                                               |                                                          |                      | 0.1   | 1                   | μA   |  |  |

| V <sub>n</sub>                            | Output noise voltage,                                                |                                                                                              | No C <sub>NR</sub> , I <sub>OUT</sub>                         | 80.0                                                     | ) × V <sub>OUT</sub> |       | μVrms               |      |  |  |

| ۷n                                        | BW = 10 Hz - 100 kHz                                                 |                                                                                              | C <sub>NR</sub> = 0.01 μl                                     | 11.8                                                     | 3 × V <sub>OUT</sub> |       | μνττισ              |      |  |  |

| PSRR                                      | Power-supply rejection ra                                            | tio                                                                                          | $f = 100 \text{ Hz}, I_{C}$                                   | <sub>DUT</sub> = 250 mA                                  |                      | 65    |                     | dB   |  |  |

| FORK                                      | (ripple rejection)                                                   |                                                                                              | $f = 10 \text{ kHz}, I_{O}$                                   | f = 10 kHz, I <sub>OUT</sub> = 250 mA                    |                      |       |                     | uВ   |  |  |

| t <sub>STR</sub>                          | Startup time                                                         |                                                                                              | V <sub>OUT</sub> = 2.85 \                                     | /, R <sub>L</sub> = 30Ω, C <sub>NR</sub> = 0.001 $\mu$ F |                      | 60    |                     | μS   |  |  |

| VIH                                       | Enable threshold high (EN                                            | N1, EN2)                                                                                     |                                                               |                                                          | 1.2                  |       | $V_{\text{IN}}$     | V    |  |  |

| VIL                                       | Enable threshold low (EN                                             | 1, EN2)                                                                                      |                                                               |                                                          | 0                    |       | 0.4                 | V    |  |  |

| I <sub>EN</sub>                           | Enable pin current (EN1,                                             | EN2)                                                                                         | $V_{IN} = V_{EN} = 5$                                         | 5.5 V                                                    | -1                   |       | 1                   | μA   |  |  |

| т                                         | Thormal abutdown tomas                                               | roturo                                                                                       | Shutdown                                                      | Temp increasing                                          |                      | +160  | °C                  |      |  |  |

| T <sub>SD</sub>                           | Thermal shutdown tempe                                               | laule                                                                                        | Reset                                                         | Temp decreasing                                          |                      | +140  |                     | -0   |  |  |

| UVLO                                      | Undervoltage lockout thre                                            | shold                                                                                        | V <sub>IN</sub> rising                                        | 2.25                                                     |                      | 2.65  | V                   |      |  |  |

|                                           | Undervoltage lockout hys                                             | teresis                                                                                      | V <sub>IN</sub> falling                                       |                                                          |                      | 100   |                     | mV   |  |  |

(1)

(2)

(3) For the adjustable version, this applies only after V<sub>IN</sub> is applied; then V<sub>EN</sub> transitions from high to low.

SBVS049D - MAY 2004 - REVISED AUGUST 2010

## Table 1. TERMINAL FUNCTIONS

| TERM   | IINAL  | DECODIDITION                                                                                                                                                                         |

|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | DRC    | DESCRIPTION                                                                                                                                                                          |

| IN     | 1      | Unregulated input supply. A small 0.1 $\mu$ F capacitor should be connected from IN to GND.                                                                                          |

| GND    | 5, Pad | Ground                                                                                                                                                                               |

| OUT1   | 3      | Output of the regulator. A small 2.2 $\mu\text{F}$ ceramic capacitor is required from this pin to ground to assure stability.                                                        |

| OUT2   | 4      | Same as OUT1 but for LDO2.                                                                                                                                                           |

| EN1    | 10     | Driving the enable pin (EN) high turns on LDO1. Driving this pin low puts LDO1 into shutdown mode, reducing operating current. The enable pin should be connected to IN if not used. |

| EN2    | 8      | Same as EN1 but controls LDO2.                                                                                                                                                       |

| FB1/NC | 9      | Feedback for CH1 adjustable version; no connection for non-adjustable CH1.                                                                                                           |

| FB2/NC | 7      | Feedback for CH2 adjustable version; no connection for non-adjustable CH2.                                                                                                           |

| NR     | 6      | Noise reduction pin; connect an external bypass capacitor to reduce LDO output noise.                                                                                                |

| NC     | 2      | No connection.                                                                                                                                                                       |

4

Copyright © 2004–2010, Texas Instruments Incorporated

Product Folder Link(s): TPS71202 TPS71219 TPS71229 TPS71247 TPS71256 TPS71257

www.ti.com

SBVS049D - MAY 2004 - REVISED AUGUST 2010

#### www.ti.com

EXAS

**NSTRUMENTS**

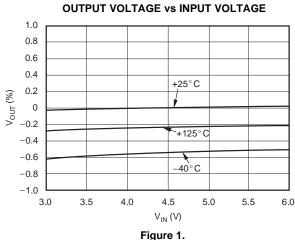

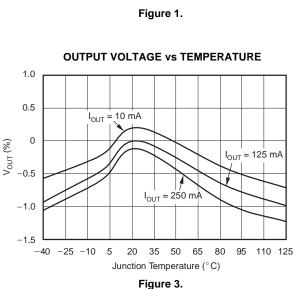

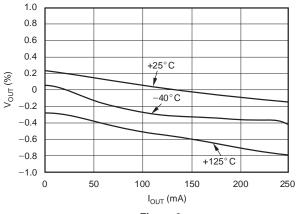

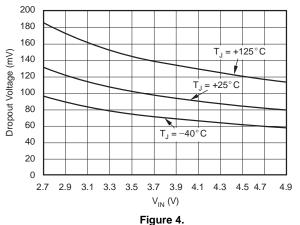

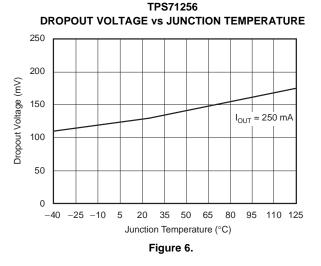

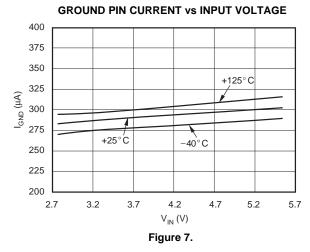

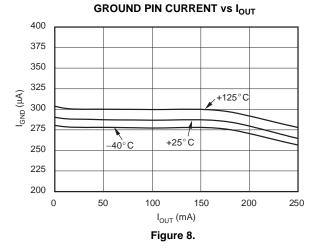

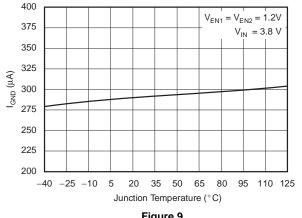

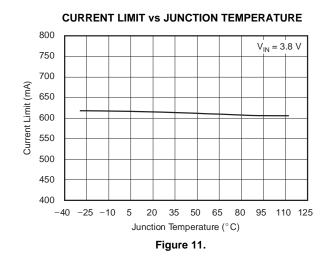

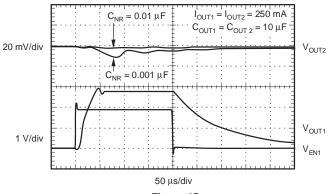

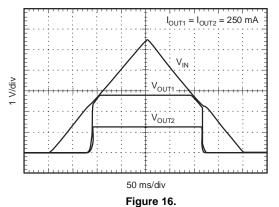

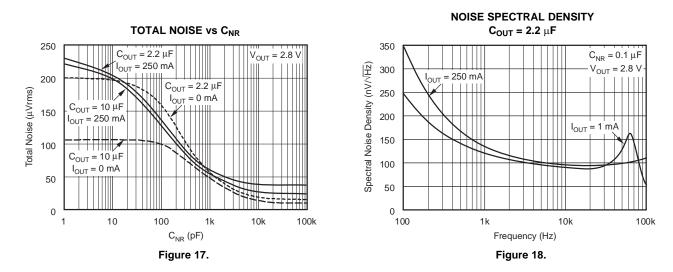

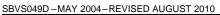

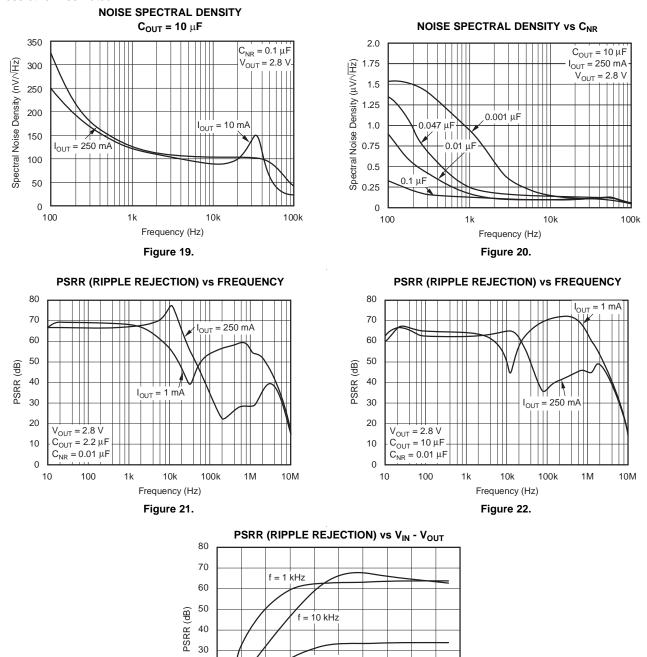

#### **TYPICAL CHARACTERISTICS**

For all voltage versions at  $T_J = 25^{\circ}$ C,  $V_{IN} = V_{OUT(nom)} + 1$  V,  $I_{OUT} = 1$  mA,  $V_{EN} = 1.2$  V,  $C_{OUT} = 2.2$   $\mu$ F, and  $C_{NR} = 0.01$   $\mu$ F, unless otherwise noted.

**OUTPUT VOLTAGE vs OUTPUT CURRENT**

Figure 2.

**DROPOUT VOLTAGE vs INPUT VOLTAGE** (ADJUSTABLE VERSION)

**TPS71256 DROPOUT VOLTAGE vs OUTPUT CURRENT** 200 T<sub>J</sub> = +125°C Dropout Voltage (mV) 150 100  $T_{\rm d}$ -40° C = +25°C T, 50 0 0 50 250 100 150 200 I<sub>OUT</sub> (mA) Figure 5.

Copyright © 2004–2010, Texas Instruments Incorporated

Product Folder Link(s): TPS71202 TPS71219 TPS71229 TPS71247 TPS71256 TPS71257

SBVS049D - MAY 2004 - REVISED AUGUST 2010

www.ti.com

## **TYPICAL CHARACTERISTICS (continued)**

For all voltage versions at  $T_J = 25^{\circ}$ C,  $V_{IN} = V_{OUT(nom)} + 1$  V,  $I_{OUT} = 1$  mA,  $V_{EN} = 1.2$  V,  $C_{OUT} = 2.2$   $\mu$ F, and  $C_{NR} = 0.01$   $\mu$ F, unless otherwise noted.

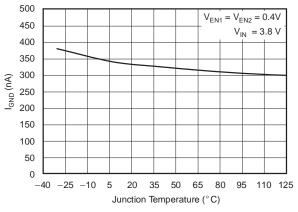

#### **GROUND PIN CURRENT vs JUNCTION TEMPERATURE**

Figure 9.

**GROUND PIN CURRENT vs JUNCTION TEMPERATURE** (DISABLED)

Figure 12.

Submit Documentation Feedback

Product Folder Link(s): TPS71202 TPS71219 TPS71229 TPS71247 TPS71256 TPS71257

TPS71202, TPS71219 TPS71229, TPS71247 TPS71256, TPS71257 SBVS049D - MAY 2004 - REVISED AUGUST 2010

www.ti.com

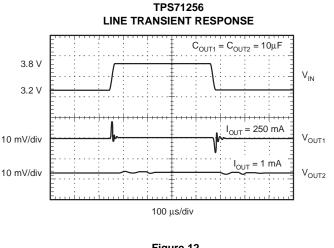

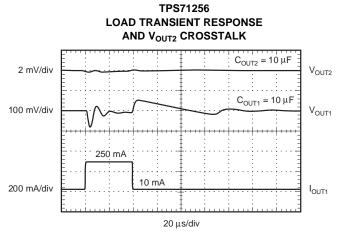

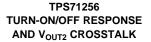

#### **TYPICAL CHARACTERISTICS (continued)**

For all voltage versions at  $T_J = 25^{\circ}C$ ,  $V_{IN} = V_{OUT(nom)} + 1$  V,  $I_{OUT} = 1$  mA,  $V_{EN} = 1.2$  V,  $C_{OUT} = 2.2$   $\mu$ F, and  $C_{NR} = 0.01$   $\mu$ F, unless otherwise noted.

#### Figure 13.

CHANNEL-TO-CHANNEL ISOLATION vs FREQUENCY 60 50 Channel Isolation (dB) 40 30 20  $C_{OUT1} = C_{OUT2} = 10 \ \mu F$ 10  $I_{OUT1} = 0$  mA to 500 mA Sinusoidal Load  $I_{OUT2} = 25 \text{ mA}$ 0 0.1 1 10 100 1k Frequency (Hz) Figure 14.

**TPS71256**

TPS71229 POWER-UP/POWER-DOWN

Copyright © 2004–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TPS71202 TPS71219 TPS71229 TPS71247 TPS71256 TPS71257

7

www.ti.com

## **TYPICAL CHARACTERISTICS (continued)**

For all voltage versions at  $T_J = 25^{\circ}$ C,  $V_{IN} = V_{OUT(nom)} + 1$  V,  $I_{OUT} = 1$  mA,  $V_{EN} = 1.2$  V,  $C_{OUT} = 2.2$   $\mu$ F, and  $C_{NR} = 0.01$   $\mu$ F, unless otherwise noted.

Figure 23.

8

Product Folder Link(s): TPS71202 TPS71219 TPS71229 TPS71247 TPS71256 TPS71257

www.ti.com

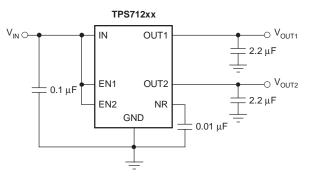

#### **APPLICATION INFORMATION**

The TPS712xx family of dual low-dropout (LDO) regulators has been optimized for use in noise-sensitive battery-operated equipment. The device features extremely low dropout, high PSRR, ultralow output noise, and low quiescent current (190  $\mu$ A typical per channel). When both outputs are disabled, the supply currents are reduced to less than 2  $\mu$ A. A typical application circuit is shown in Figure 24.

# Figure 24. Typical Application Circuit (fixed-voltage versions)

#### INPUT AND OUTPUT CAPACITOR REQUIREMENTS

A 0.1  $\mu$ F or larger ceramic input bypass capacitor, connected between IN and GND and located close to the TPS712xx, is required for stability. It improves transient response, noise rejection, and ripple rejection. A higher-value input capacitor may be necessary if large, fast-rise-time load transients are anticipated and the device is located several inches from the power source.

The TPS712xx requires an output capacitor connected between the outputs and GND to stabilize the internal control loops. The minimum recommended output capacitor is 2.2  $\mu$ F. If an output voltage of

1.8 V or less is chosen, the minimum recommended output capacitor is 4.7  $\mu$ F. Any ceramic capacitor that meets the minimum output capacitor requirements is suitable. Capacitors with higher ESR may be used, provided the ESR is less than 1 $\Omega$ .

## OUTPUT NOISE

The internal voltage reference is a key source of noise in an LDO regulator. The TPS712xx has an NR pin that is connected to the voltage reference through a 250 k $\Omega$  internal resistor. The 250 k $\Omega$  internal resistor, in conjunction with an external ceramic bypass capacitor connected to the NR pin, creates a low-pass filter to reduce the voltage reference noise and, therefore, the noise at the regulator output. To achieve a fast startup, the 250 k $\Omega$  internal resistor is shorted for 400  $\mu$ s after the device is enabled.

Because the primary noise source is the internal voltage reference, the output noise will be greater for higher output voltage versions. For the case where no noise reduction capacitor is used, the typical noise ( $\mu$ Vrms) over 10 Hz to 100 kHz is 80 times the output voltage. If a 0.01  $\mu$ F capacitor is used from the NR pin to ground, the noise ( $\mu$ Vrms) drops to 11.8 times the output voltage. For example, the TPS71256 exhibits only 33  $\mu$ Vrms of output voltage noise using a 0.01  $\mu$ F ceramic bypass capacitor and a 2.2  $\mu$ F ceramic output capacitor.

## STARTUP CHARACTERISITCS

To minimize startup overshoot, the TPS712xx will initially target an output voltage that is approximately 80% of the final value. To avoid a delayed startup time, noise reduction capacitors of 0.01  $\mu$ F or less are recommended. Larger noise reduction capacitors will cause the output to hold at 80% until the voltage on the noise reduction capacitor exceeds 80% of the bandgap voltage. The typical startup time with a 0.001  $\mu$ F noise reduction capacitor is 60  $\mu$ s. Once one of the output voltages is present, the startup time of the other output will not be affected by the noise reduction capacitor.

9

SBVS049D - MAY 2004 - REVISED AUGUST 2010

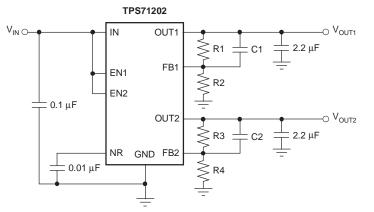

#### PROGRAMMING THE TPS71202 ADJUSTABLE LDO REGULATOR

The output voltage of the TPS71202 dual adjustable regulator is programmed using an external resistor divider, as shown in Figure 25. The output voltage is calculated using Equation 1:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R1}{R2}\right)$$

(1)

where  $V_{REF} = 1.225$  V (the internal reference voltage).

Resistors R2 and R4 should be chosen for approximately a 40  $\mu$ A divider current. Lower value resistors can be used for improved noise performance, but will consume more power. Higher values should be avoided because leakage current at FB increases the output voltage error. The recommended design procedure is to choose R2 = 30.1 k $\Omega$  to set the divider current at 40  $\mu$ A, and then calculate R1 using Equation 2:

$$R1 = \left(\frac{V_{OUT}}{V_{REF}} - 1\right) \times R2$$

(2)

To improve the stability and noise performance of the adjustable version, a small compensation capacitor can be placed between OUT and FB.

For voltages  $\leq$  1.8 V, the value of this capacitor should be 100 pF. For voltages > 1.8 V, the approximate value of this capacitor can be calculated as Equation 3:

$C1 = \frac{(3 \times 10^{5}) \times (R1 + R2)}{(R1 \times R2)} \qquad (pF)$ (3)

The suggested value of this capacitor for several resistor ratios is shown in Figure 25. If this capacitor is not used (such as in a unity-gain configuration) or if an output voltage  $\leq 1.8$  V is chosen, then the minimum recommended output capacitor is 4.7  $\mu$ F instead of 2.2  $\mu$ F.

#### DROPOUT VOLTAGE

The TPS712xx uses a PMOS pass transistor to achieve extremely low dropout. When  $(V_{IN} - V_{OUT})$  is less than the dropout voltage ( $V_{DO}$ ), the PMOS pass device is in its linear region of operation and the input-to-output resistance is the  $R_{DS, ON}$  of the PMOS pass element. Dropout voltages at lower currents can be approximated by calculating the effective R<sub>DS. ON</sub> of the pass element and multiplying that resistance by the load current.  $R_{DS, ON}$  of the pass element can be obtained by dividing the dropout voltage by the rated output current. For the TPS71256, the R<sub>DS. ON</sub> of the pass element is 84 m $\Omega$ . The dropout voltage of the TPS712xx will be less for higher output voltage versions. This is because the PMOS pass element will have lower on-resistance due to increased gate drive.

| V <sub>OUT</sub> | R1/R3   | R2/R4   | C1/C2  |

|------------------|---------|---------|--------|

| 1.225 V          | Short   | Open    | Open   |

| 1.5 V            | 7.15 kΩ | 30.1 kΩ | 100 pF |

| 2.5 V            | 31.6 kΩ | 30.1 kΩ | 22 pF  |

| 3.0 V            | 43.2 kΩ | 30.1 kΩ | 15 pF  |

| 3.3 V            | 49.9 kΩ | 30.1 kΩ | 15 pF  |

| 4.75 V           | 86.6 kΩ | 30.1 kΩ | 15 pF  |

**Output Voltage Programming Guide**

#### Figure 25. TPS71202 Adjustable LDO Regulator Programming

www.ti.com

10

#### www.ti.com

#### **TRANSIENT RESPONSE**

As with any regulator, increasing the size of the output capacitor will reduce over/undershoot magnitude but increase duration of the transient response. In the adjustable version, the addition of a capacitor,  $C_{FB}$ , from the output to the feedback pin will also improve stability and transient response. The transient response of the TPS712xx is enhanced with an active pull-down that engages when the output is over-voltaged. The active pull-down decreases the output recovery time when the load is removed. Figure 13 in the *Typical Characteristics* section shows the output transient response.

#### SHUTDOWN

Both enable pins are active high and are compatible with standard TTL-CMOS levels. The device is only completely disabled when both EN1 and EN2 are logic low. In this state, the LDO is completely off and the ground pin current drops to approximately 100 nA. With one output disabled, the ground pin current is slightly greater than half the nominal value. When shutdown capability is not required, the enable pins should be connected to the input supply.

#### INTERNAL CURRENT LIMIT

The TPS712xx internal current limit helps protect the regulator during fault conditions. During current limit, the output will source a fixed amount of current that is largely independent of the output voltage.

The TPS712xx PMOS-pass transistors have a built-in back diode that conducts reverse current when the input voltage drops below the output voltage (that is, during power-down). Current is conducted from the output to the input and is not internally limited. If extended reverse voltage operation is anticipated, external limiting may be appropriate.

#### THERMAL PROTECTION

Thermal protection disables both outputs when the junction temperature of either channel rises to approximately +160°C, allowing the device to cool. When the junction temperature cools to approximately +140°C, the output circuitry is again

enabled. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This limits the dissipation of the regulator, protecting it from damage due to overheating.

Any tendency to activate the thermal protection circuit indicates excessive power dissipation or an inadequate heatsink. For reliable operation, junction temperature should be limited to +125°C maximum. To estimate the margin of safety in a complete design heatsink), increase (including the ambient temperature until the thermal protection is triggered; use worst-case loads and signal conditions. For good reliability, thermal protection should trigger at least +35°C above the maximum expected ambient condition of your application. This produces a worst-case junction temperature of +125°C at the hiahest expected ambient temperature and worst-case load.

The internal protection circuitry of the TPS712xx was designed to protect against overload conditions. It was not intended to replace proper heatsinking. Continuously running the TPS712xx into thermal shutdown will degrade device reliability.

#### POWER DISSIPATION

The ability to remove heat from the die is different for each package type, presenting different considerations in the PCB layout. The PCB area around the device that is free of other components moves the heat from the device to the ambient air. Performance data for a JEDEC high-K board is shown in the Dissipation Ratings table. Using heavier copper will increase the effectiveness in removing heat from the device. The addition of plated through-holes to heat-dissipating layers will also improve the heat-sink effectiveness.

Power dissipation depends on input voltage and load conditions. Power dissipation ( $P_D$ ) is equal to the product of the output current times the voltage drop across the output pass element ( $V_{IN}$  to  $V_{OUT}$ ):

$$\mathsf{P}_{\mathsf{D}} = (\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}) \times \mathsf{I}_{\mathsf{OUT}} \tag{4}$$

Power dissipation can be minimized by using the lowest possible input voltage necessary to assure the required output voltage.

SBVS049D - MAY 2004 - REVISED AUGUST 2010

www.ti.com

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | hanges from Revision C (July, 2005) to Revision D                         | Page |

|----|---------------------------------------------------------------------------|------|

| •  | Replaced the Dissipation Ratings table with the Thermal Information table | 3    |

30-Sep-2014

## **PACKAGING INFORMATION**

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)            | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|-------------------------|---------|

| TPS71202DRCR     | ACTIVE        | VSON         | DRC                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARQ                     | Samples |

| TPS71202DRCRG4   | ACTIVE        | VSON         | DRC                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARQ                     | Samples |

| TPS71202DRCT     | ACTIVE        | VSON         | DRC                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARQ                     | Samples |

| TPS71202DRCTG4   | ACTIVE        | VSON         | DRC                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARQ                     | Samples |

| TPS71219DRCR     | ACTIVE        | VSON         | DRC                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARW                     | Samples |

| TPS71219DRCRG4   | ACTIVE        | VSON         | DRC                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARW                     | Samples |

| TPS71219DRCT     | ACTIVE        | VSON         | DRC                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARW                     | Samples |

| TPS71219DRCTG4   | ACTIVE        | VSON         | DRC                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARW                     | Samples |

| TPS71229DRCR     | ACTIVE        | VSON         | DRC                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARU                     | Samples |

| TPS71229DRCT     | ACTIVE        | VSON         | DRC                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARU                     | Samples |

| TPS71229DRCTG4   | ACTIVE        | VSON         | DRC                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARU                     | Samples |

| TPS71247DRCR     | ACTIVE        | VSON         | DRC                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARS                     | Samples |

| TPS71247DRCRG4   | ACTIVE        | VSON         | DRC                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARS                     | Samples |

| TPS71247DRCT     | ACTIVE        | VSON         | DRC                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARS                     | Samples |

| TPS71256DRCR     | OBSOLETE      | VSON         | DRC                | 10   |                | TBD                        | Call TI          | Call TI             | -40 to 125   | ARV                     |         |

| TPS71256DRCRG4   | OBSOLETE      | VSON         | DRC                | 10   |                | TBD                        | Call TI          | Call TI             | -40 to 125   |                         |         |

| TPS71256DRCT     | ACTIVE        | VSON         | DRC                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARV                     | Samples |

| TPS71256DRCTG4   | ACTIVE        | VSON         | DRC                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | ARV                     | Samples |

30-Sep-2014

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)            | Lead/Ball Finish<br>(6) | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|----------------------------|-------------------------|---------------------|--------------|-------------------------|---------|

| TPS71257DRCR     | ACTIVE        | VSON         | DRC                | 10   | 3000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU               | Level-2-260C-1 YEAR | -40 to 125   | ART                     | Samples |

| TPS71257DRCT     | ACTIVE        | VSON         | DRC                | 10   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU               | Level-2-260C-1 YEAR | -40 to 125   | ART                     | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

# PACKAGE OPTION ADDENDUM

30-Sep-2014

#### OTHER QUALIFIED VERSIONS OF TPS71202 :

Enhanced Product: TPS71202-EP

NOTE: Qualified Version Definitions:

• Enhanced Product - Supports Defense, Aerospace and Medical Applications

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

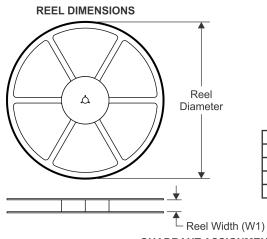

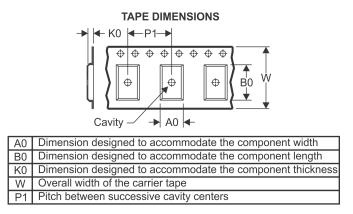

## TAPE AND REEL INFORMATION

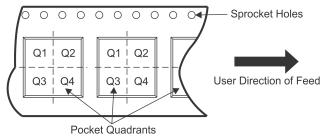

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| All dimensions are nomina |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|---------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                    | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS71202DRCR              | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS71202DRCT              | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS71219DRCR              | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS71219DRCT              | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS71229DRCR              | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS71229DRCT              | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS71247DRCR              | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS71247DRCT              | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS71256DRCT              | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS71257DRCR              | VSON            | DRC                | 10 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| TPS71257DRCT              | VSON            | DRC                | 10 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

Texas Instruments

www.ti.com

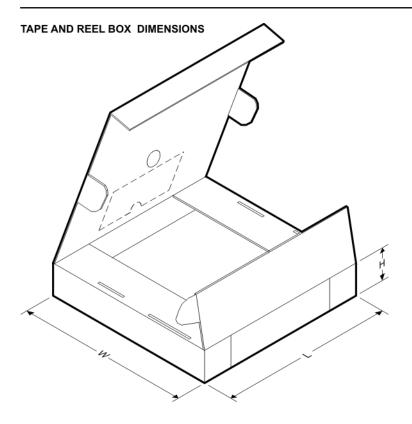

# PACKAGE MATERIALS INFORMATION

24-Jul-2015

| *All dimensions are nominal |              |                 |      |      |             |            |             |

|-----------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TPS71202DRCR                | VSON         | DRC             | 10   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS71202DRCT                | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| TPS71219DRCR                | VSON         | DRC             | 10   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS71219DRCT                | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| TPS71229DRCR                | VSON         | DRC             | 10   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS71229DRCT                | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| TPS71247DRCR                | VSON         | DRC             | 10   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS71247DRCT                | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| TPS71256DRCT                | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| TPS71257DRCR                | VSON         | DRC             | 10   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS71257DRCT                | VSON         | DRC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

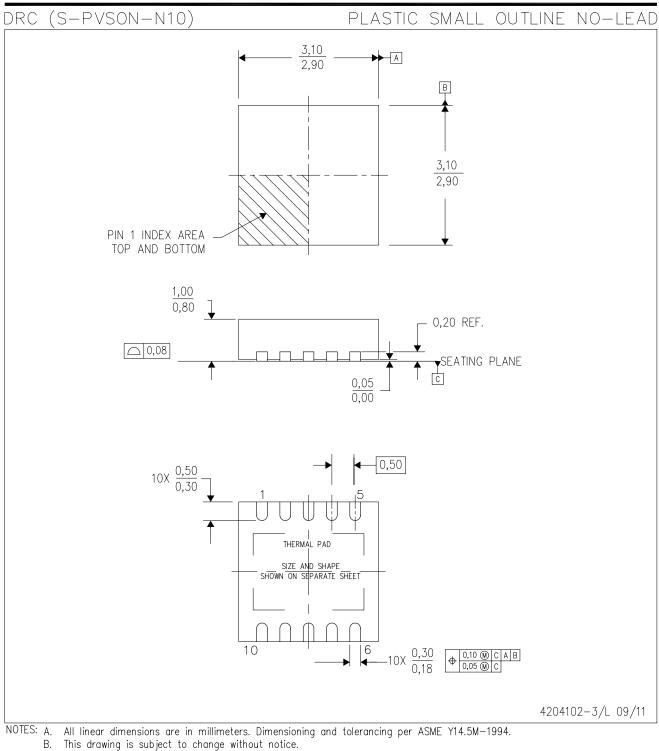

# **MECHANICAL DATA**

- C. Small Outline No-Lead (SON) package configuration.

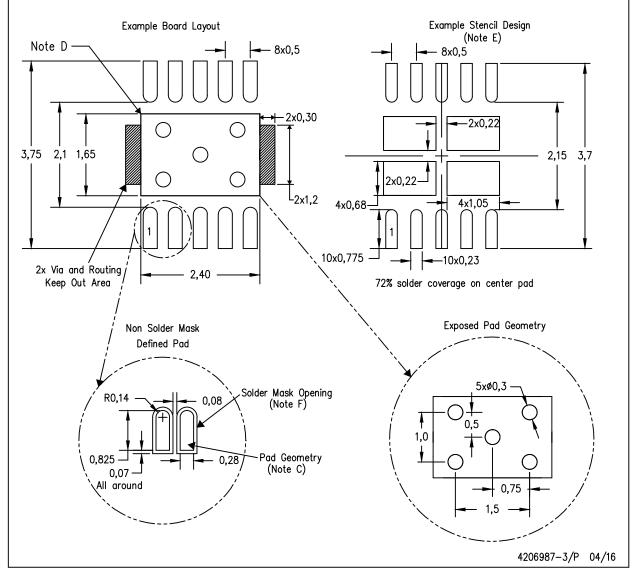

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance, if present.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features

- and dimensions, if present

## DRC (S-PVSON-N10)

## PLASTIC SMALL OUTLINE NO-LEAD

#### THERMAL INFORMATION

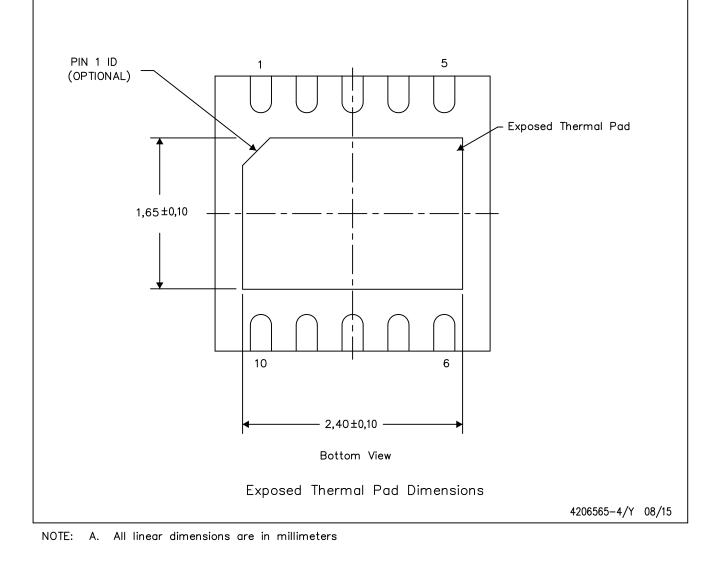

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

DRC (S-PVSON-N10) PLASTIC SMALL OUTLINE NO-LEAD

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-SM-782 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat-Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ctivity                       |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated