# 4:1 HDMI/DVI Switch with Equalization, DDC/CEC Buffers and EDID Replication

### **Data Sheet**

# ADV3002

#### **FEATURES**

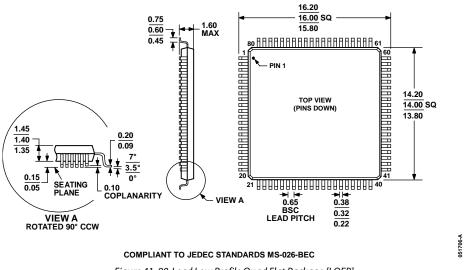

4 inputs, 1 output HDMI/DVI links ±8 kV ESD protection on input pins HDMI 1.4a receive and transmit compliant Supports 250 Mbps to 2.25 Gbps data rates and beyond Supports 25 MHz to 225 MHz pixel clocks and beyond Fully buffered unidirectional inputs/outputs Switchable 50  $\Omega$  on-chip input terminations with manual or automatic control on channel switch Equalized inputs with low added jitter compensate for more than 20 meters of HDMI cable at 2.25 Gbps Loss of signal (LOS) detect circuit on TMDS clock Output disable feature for reduced power dissipation **Bidirectional DDC buffers (SDA and SCL)** EDID replication reduces component count, while enabling simultaneous access to all HDMI sources 5 V combiner provides power to EDID replicator and CEC buffer when local system power is off **Bidirectional buffered CEC line with integrated pull-up** resistors (26 kΩ) Hot plug detect pulse low on channel switch with programmable pulse width or direct manual control Standards compatible: HDMI, DVI, HDCP, I<sup>2</sup>C 80-lead, 14 mm × 14 mm LQFP RoHS-compliant package

#### APPLICATIONS

Advanced television (HDTV) sets Projectors A/V receivers Set-top boxes

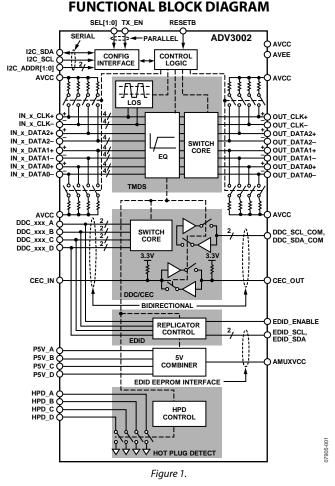

#### **GENERAL DESCRIPTION**

The ADV3002 is a complete HDMI<sup>™</sup>/DVI link switch featuring equalized transition minimized differential signaling (TMDS) inputs, ideal for systems with long cable runs. The ADV3002 includes bidirectional buffering for the DDC bus and CEC line, with integrated pull-up resistors for the CEC line. Additionally, the ADV3002 includes an EDID replication function that enables one EDID EEPROM to be shared for all four HDMI ports.

The ADV3002 is provided in a space-saving, 80-lead LQFP surface-mount, Pb-free plastic package and is specified to operate over the 0°C to 85°C temperature range.

#### **PRODUCT HIGHLIGHTS**

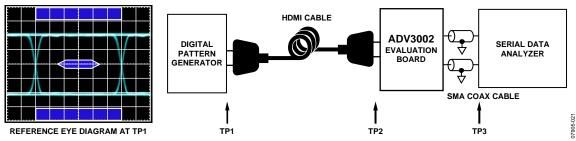

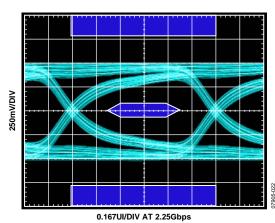

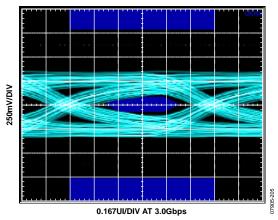

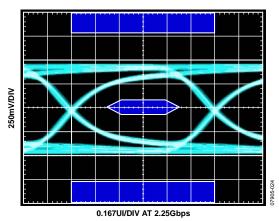

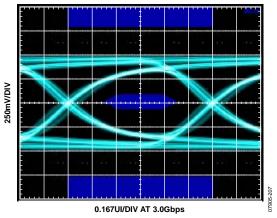

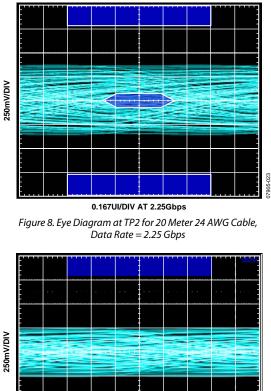

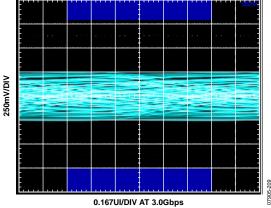

- 1. Input cable equalizer enables use of long cables at the input. For a 24 AWG cable, the ADV3002 compensates for more than 20 meters at data rates of up to 2.25 Gbps.

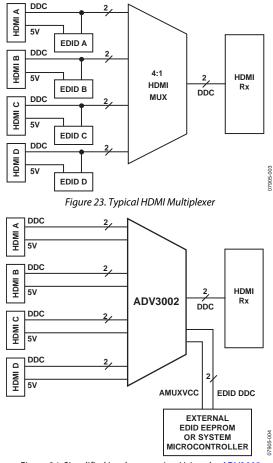

- 2. Auxiliary multiplexer isolates and buffers the DDC bus and the CEC line, increasing total system capacitance limit.

- 3. EDID replication eliminates the need for multiple EDID EEPROMs. EDID can be loaded from a single external EEPROM or from a system microcontroller.

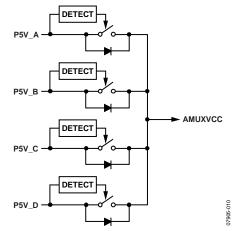

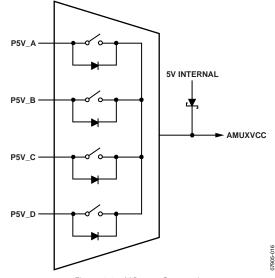

- 4. 5 V power combiner powers the EDID replicator and CEC buffer when local system power is off.

- 5. Integrated hot plug detect pulse low on channel switch with programmable pulse width or direct manual control.

Advanced Television Solutions by Analog Devices Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### ADV3002\* Product Page Quick Links

Last Content Update: 11/01/2016

### Comparable Parts

View a parametric search of comparable parts

### Evaluation Kits

• ADV3002 Evaluation Board

### Documentation 🖵

#### Data Sheet

• ADV3002: 4:1 HDMI/DVI Switch with Equalization DDC/ CEC Buffers and EDID Replication Data Sheet

### Design Resources 🖵

- ADV3002 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### Discussions 🖵

View all ADV3002 EngineerZone Discussions

### Sample and Buy

Visit the product page to see pricing options

### Technical Support

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

### TABLE OF CONTENTS

| Features                                      |

|-----------------------------------------------|

| Applications1                                 |

| General Description                           |

| Functional Block Diagram 1                    |

| Product Highlights 1                          |

| Revision History 2                            |

| Specifications                                |

| TMDS Performance Specifications               |

| Auxiliary Channel Performance Specifications  |

| Power Supply and Control Logic Specifications |

| Absolute Maximum Ratings                      |

| Thermal Resistance 5                          |

| ESD Caution                                   |

| Pin Configuration and Function Descriptions   |

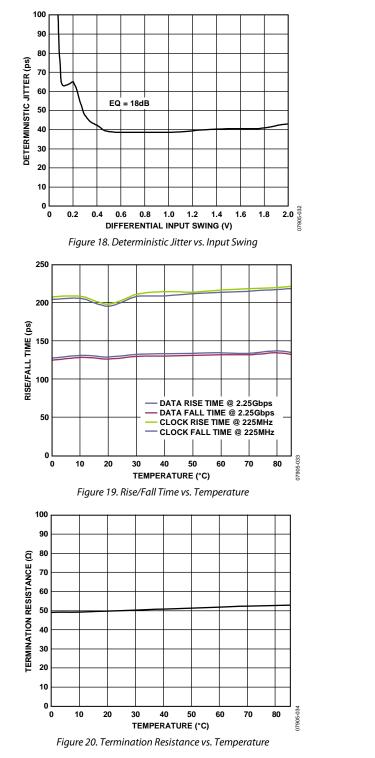

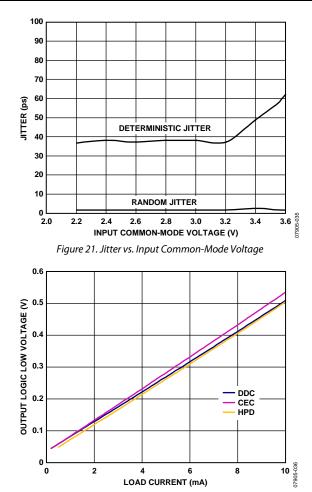

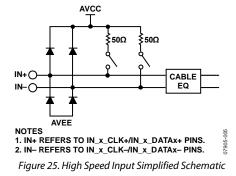

| Typical Performance Characteristics           |

| Theory of Operation12                         |

| TMDS Input Channels12                         |

| TMDS Output Channels12                        |

#### **REVISION HISTORY**

| 8/12—Rev. A to Rev. B                                       |    |

|-------------------------------------------------------------|----|

| Changed Data Rate = 3 Gbps to                               |    |

| Data Rate = 2.25 Gbps Throughout                            | ıt |

| Changes to Features Section and Product Highlights Section  | 1  |

| Changes to Table 1                                          | 3  |

| Changes to specifications statements in Typical Performance |    |

| Characteristics Section                                     | 8  |

| Changes to Theory of Operation Section1                     | 2  |

| Changes to Cable Lengths and Equalization Section and       |    |

| PCB Layout Guidelines Section                               | 4  |

| Added Unused DDC/CEC Buffers Section                        | 6  |

|                                                             |    |

| DDC Buffers                      | 13 |

|----------------------------------|----|

| EDID Replication                 |    |

| 5 V Combiner                     | 15 |

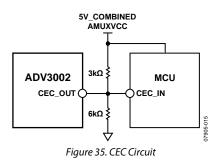

| CEC Buffer                       | 16 |

| Hot Plug Detect Control          | 16 |

| Loss of Signal Detect            | 16 |

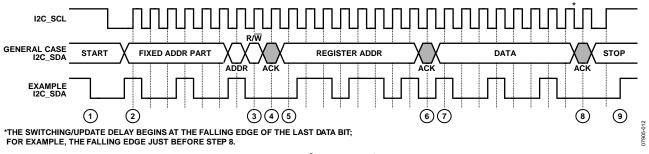

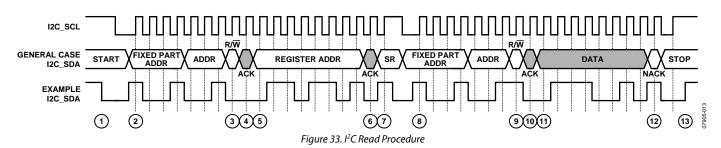

| Serial Control Interface         | 17 |

| Reset                            | 17 |

| Write Procedure                  | 17 |

| Read Procedure                   |    |

| Register Map                     | 19 |

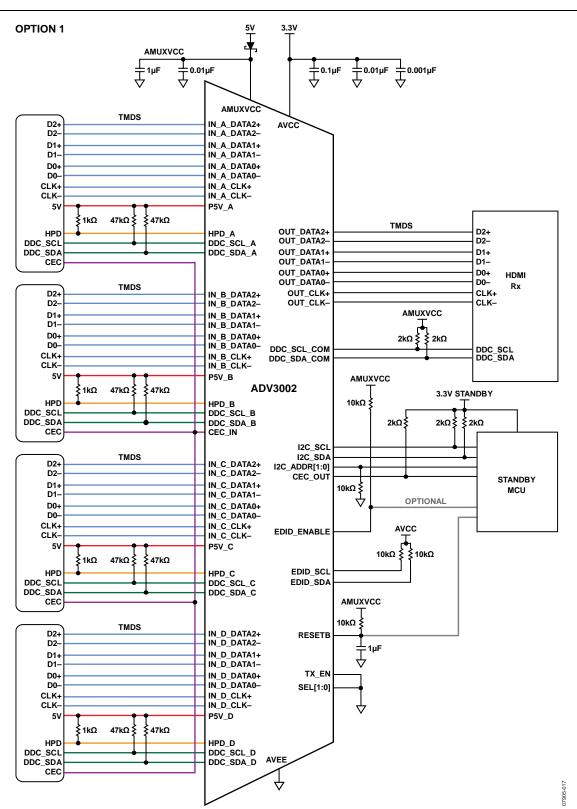

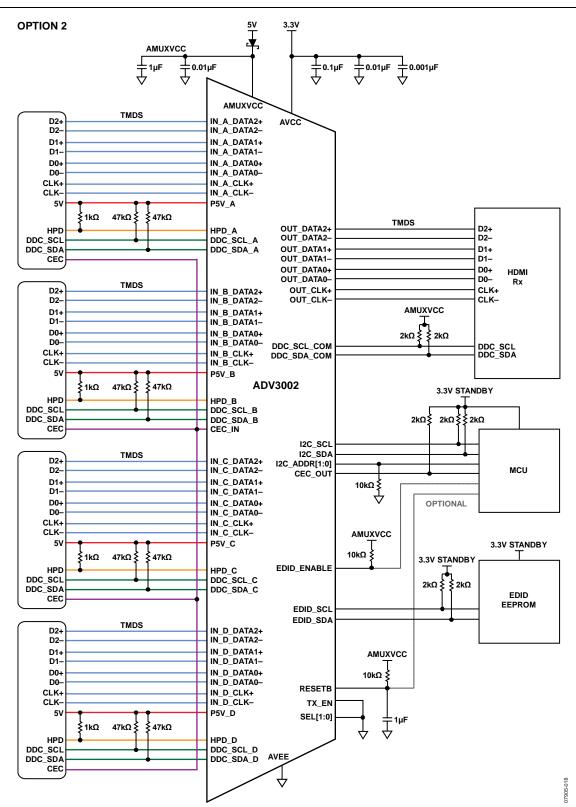

| Applications Information         |    |

| HDMI Multiplexer for Advanced TV |    |

| Cable Lengths and Equalization   |    |

| PCB Layout Guidelines            |    |

| Outline Dimensions               |    |

| Ordering Guide                   | 27 |

|                                  |    |

#### 8/11—Rev. 0 to Rev. A

| Changed Data Rate = 2.25 Gbps to                           |    |

|------------------------------------------------------------|----|

| Data Rate = 3 Gbps Throughout                              | ıt |

| Changes to Features Section and Product Highlights Section | 1  |

| Changes to Table 1                                         | 3  |

| Changes to Figure 4 Caption and Figure 6 Caption           | 8  |

| Added Figure 5 and Figure 7; Renumbered Sequentially       | 8  |

| Moved Figure 8 and Figure 10                               | 9  |

| Changes to Figure 8 Caption and Figure 10 Caption          | 9  |

| Added Figure 9 and Figure 11                               | 9  |

| Changes to Figure 12 and Figure 15 1                       | 0  |

| Changes to TMDS Input Channels Section and TMDS Output     |    |

| Channels Section 1                                         | 2  |

| Changes to Figure 31 1                                     | 6  |

| Changes to Cable Lengths and Equalization Section 2        | 4  |

|                                                            |    |

12/08—Revision 0: Initial Version

### **SPECIFICATIONS**

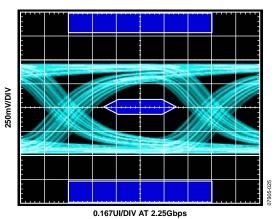

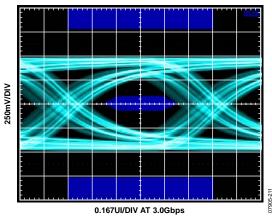

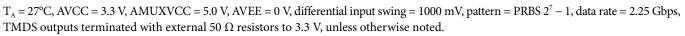

$T_A = 27^{\circ}$ C, AVCC = 3.3 V, AMUXVCC = 5 V, AVEE = 0 V, data rate = 2.25 Gbps, differential input swing = 1000 mV, TMDS outputs terminated with external 50  $\Omega$  resistors to 3.3 V, unless otherwise noted.

#### **TMDS PERFORMANCE SPECIFICATIONS**

| Table 1.                                      |                                                       |            |            |                  |        |

|-----------------------------------------------|-------------------------------------------------------|------------|------------|------------------|--------|

| Parameter                                     | Test Conditions/Comments                              | Min        | Тур        | Max              | Unit   |

| DYNAMIC PERFORMANCE                           |                                                       |            |            |                  |        |

| Maximum Data Rate (DR) per Channel            | NRZ                                                   | 2.25       |            |                  | Gbps   |

| Maximum Clock Rate                            |                                                       | 225        |            |                  | MHz    |

| Bit Error Rate (BER)                          | PRBS 2 <sup>23</sup> – 1                              |            |            | 10 <sup>-9</sup> |        |

| Added Data Jitter                             | $DR \le 2.25 \text{ Gbps}, PRBS 2^7 - 1$              |            | 40         |                  | ps p-p |

| Added Clock Jitter                            |                                                       |            | 1          |                  | ps rms |

| Differential Intrapair Skew                   | At output                                             |            | 1          |                  | ps     |

| Differential Interpair Skew                   | At output                                             |            | 35         |                  | ps     |

| EQUALIZATION PERFORMANCE                      |                                                       |            |            |                  |        |

| High Frequency Gain                           | Boost frequency = 1.5 GHz                             |            | 16         |                  | dB     |

| INPUT CHARACTERISTICS                         |                                                       |            |            |                  |        |

| Input Voltage Swing                           | Differential                                          | 150        |            | 1200             | mV     |

| Input Common-Mode Voltage (V <sub>ICM</sub> ) |                                                       | AVCC – 800 |            | AVCC             | mV     |

| OUTPUT CHARACTERISTICS                        |                                                       |            |            |                  |        |

| High Voltage Level                            | Single-ended high speed channel                       | AVCC – 200 |            | AVCC + 10        | mV     |

| Low Voltage Level                             | Single-ended high speed channel                       | AVCC – 600 | AVCC – 600 |                  | mV     |

| Rise/Fall time (20% to 80%)                   | DR = 2.25 Gbps                                        | 75         |            | 190              | ps     |

| TERMINATION                                   |                                                       |            |            |                  |        |

| Input Termination Resistance                  | Single-ended                                          |            | 50         |                  | Ω      |

| Output Termination Resistance                 | Single-ended                                          |            | 50         |                  | Ω      |

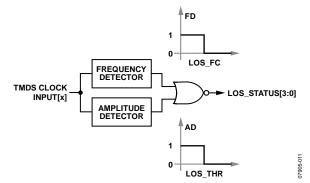

| LOSS OF SIGNAL (LOS) DETECT                   |                                                       |            |            |                  |        |

| Frequency Cutoff                              | LOS_FC (see Figure 31)                                | 5          |            |                  | MHz    |

| Amplitude Threshold                           | Clock rate = 225 MHz, LOS_THR = 00<br>(see Figure 31) |            | 35         |                  | mV     |

#### **AUXILIARY CHANNEL PERFORMANCE SPECIFICATIONS**

Table 2.

| Parameter                           | Test Conditions/Comments                                                   | Min                  | Тур  | Max | Unit |

|-------------------------------------|----------------------------------------------------------------------------|----------------------|------|-----|------|

| DDC CHANNELS                        |                                                                            |                      |      |     |      |

| Input Capacitance, C <sub>AUX</sub> | DC bias = 2.5 V, ac voltage = 3.5 V p-p, f = 100 kHz                       |                      | 5    | 15  | рF   |

| Input Low Voltage, V <sub>IL</sub>  |                                                                            |                      |      | 0.5 | V    |

| Input High Voltage, V <sub>⊮</sub>  |                                                                            | $0.7 \times AMUXVCC$ |      |     | V    |

| Output Low Voltage, V <sub>oL</sub> | $I_{OL} = 5 \text{ mA}$                                                    |                      | 0.25 | 0.4 | V    |

| Rise Time                           | 10% to 90%, $C_{LOAD} = 50$ pF, $R_{PULL-UP} = 2$ k $\Omega$               |                      | 1.45 |     | μs   |

| Fall Time                           | 90% to 10%, $C_{LOAD} = 50 \text{ pF}$ , $R_{PULL-UP} = 2 \text{ k}\Omega$ |                      | 20   | 250 | ns   |

| Leakage                             | $V_{IN} = 5.0 V$                                                           |                      |      | 10  | μΑ   |

| Parameter                            | Test Conditions/Comments                                                                                                           | Min | Тур  | Max | Unit |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| CEC CHANNEL                          |                                                                                                                                    |     |      |     |      |

| Input Capacitance, C <sub>AUX</sub>  | DC bias = 1.65 V, ac voltage = 2.5 V p-p, f = 100 kHz                                                                              |     | 5    | 15  | рF   |

| Input Low Voltage, V $_{\rm L}$      |                                                                                                                                    |     |      | 0.8 | V    |

| Input High Voltage, V <sub>IH</sub>  |                                                                                                                                    | 2.0 |      |     | V    |

| Output Low Voltage, V <sub>OL</sub>  | $I_{OL} = 3 \text{ mA}$                                                                                                            |     | 0.1  | 0.6 | V    |

| Output High Voltage, V <sub>он</sub> |                                                                                                                                    | 2.5 |      |     | V    |

| Rise Time                            | 10% to 90%, C <sub>LOAD</sub> = 1500 pF, R <sub>PULL-UP</sub> = 27 kΩ; or C <sub>LOAD</sub> = 7200 pF, R <sub>PULL-UP</sub> = 3 kΩ |     | 75   | 250 | μs   |

| Fall Time                            | 90% to 10%, $C_{LOAD}$ = 1500 pF, $R_{PULL-UP}$ = 27 kΩ; or $C_{LOAD}$ = 7200 pF, $R_{PULL-UP}$ = 3 kΩ                             |     | 0.2  | 50  | μs   |

| Pull-Up Resistance                   |                                                                                                                                    |     | 26   |     | kΩ   |

| Leakage                              | Off-leakage test conditions <sup>1</sup>                                                                                           |     |      | 1.8 | μA   |

| HOT PLUG DETECT                      |                                                                                                                                    |     |      |     |      |

| Output Low Voltage, V <sub>OL</sub>  | $R_{PU} = 800 \Omega$                                                                                                              |     | 0.25 | 0.4 | V    |

<sup>1</sup> Off leakage test conditions are described in the HDMI Compliance Test Specification 1.3c Section 8, Test ID 8-14. To measure CEC leakage, connect the CEC line to 3.63 V via 26 k $\Omega\pm$  5 % resistor with an ammeter in series and with the power mains disabled.

#### POWER SUPPLY AND CONTROL LOGIC SPECIFICATIONS

| Parameter                                                   | Test Conditions/Comments                        |       |      | Max | Unit |  |

|-------------------------------------------------------------|-------------------------------------------------|-------|------|-----|------|--|

| POWER SUPPLY                                                |                                                 |       | Тур  |     |      |  |

| AVCC                                                        | Operating range (3.3 V $\pm$ 10%)               | 3.0   | 3.3  | 3.6 | v    |  |

| P5V_x                                                       |                                                 | 4.7   | 5    | 5.5 | v    |  |

| AMUXVCC                                                     | Output voltage, total load <sup>1</sup> = 50 mA | 4.0   | 5    | 5.5 | v    |  |

| QUIESCENT CURRENT                                           |                                                 |       |      |     |      |  |

| AVCC                                                        | Outputs disabled                                |       | 40   | 60  | mA   |  |

|                                                             | Outputs enabled                                 |       | 170  | 150 | mA   |  |

| P5V_x                                                       | Main power on                                   |       | 0.5  | 10  | mA   |  |

|                                                             | Main power off                                  |       | 20   | 30  | mA   |  |

| AMUXVCC                                                     | Main power on                                   |       | 20   | 30  | mA   |  |

|                                                             | Main power off                                  |       | 0.5  | 10  | mA   |  |

| POWER DISSIPATION                                           |                                                 |       |      |     |      |  |

|                                                             | Outputs disabled                                |       | 232  | 381 | mW   |  |

|                                                             | Outputs enabled                                 |       | 661  | 885 | mW   |  |

| I <sup>2</sup> C <sup>®</sup> AND LOGIC INPUTS <sup>2</sup> |                                                 |       |      |     |      |  |

| Input High Voltage, V <sub>IH</sub>                         |                                                 | 2.4   |      |     | V    |  |

| Input Low Voltage, $V_{IL}$                                 |                                                 | 1.    |      | 1.0 | V    |  |

| I <sup>2</sup> C AND LOGIC OUTPUTS <sup>2</sup>             |                                                 |       |      |     |      |  |

| Output High Voltage, V <sub>он</sub>                        | $I_{OH} = -2 \text{ mA}$                        |       | AVCC |     | V    |  |

| Output Low Voltage, V <sub>ol</sub>                         | $I_{OI} = +2 \text{ mA}$                        | 0.4 V |      |     | V    |  |

<sup>1</sup> The total load current includes current drawn by the ADV3002 as well as external devices powered from the AMUXVCC supply. <sup>2</sup> The ADV3002 I<sup>2</sup>C control and logic input pins are listed as Control in the Type column in Table 6. I<sup>2</sup>C pins are 5 V tolerant and based on the 3.3 V I<sup>2</sup>C bus specification.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 4.

| Parameter                                                                         | Rating                                                                         |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| AVCC to AVEE                                                                      | 3.7 V                                                                          |

| P5V_x                                                                             | 5.8 V                                                                          |

| AMUXVCC                                                                           | AVCC – 0.3 V < AMUXVCC < 5.8 V                                                 |

| Internal Power Dissipation                                                        | 1.2 W                                                                          |

| TMDS Single-Ended Input<br>Voltage                                                | $AVCC - 1.4 V < V_{IN} < AVCC + 0.3 V$                                         |

| TMDS Differential Input<br>Voltage                                                | 2.0 V                                                                          |

| Voltage at TMDS Output                                                            | V <sub>OUT</sub> < 3.7 V                                                       |

| DDC Input Voltage                                                                 | $AVEE - 0.3 V < V_{IN} < AMUXVCC + 0.3 V$                                      |

| CEC Input Voltage                                                                 | $AVEE - 0.3 V < V_{IN} < 4.0 V$                                                |

| I <sup>2</sup> C Logic Input Voltage<br>(EDID_SCL, EDID_SDA,<br>I2C_SCL, I2C_SDA) | AVEE – $0.3 \text{ V} < \text{V}_{\text{IN}} < 4.0 \text{ V}$                  |

| Parallel Input Voltage<br>(I2C_ADDR[1:0],<br>RESETB)                              | AVEE – $0.3 \text{ V} < \text{V}_{\text{IN}} < \text{AMUXVCC} + 0.3 \text{ V}$ |

| Parallel Input Voltage<br>(SEL[1:0], TX_EN)                                       | $AVEE - 0.3V < V_{IN} < AVCC + 0.3V$                                           |

| Storage Temperature Range                                                         | –65°C to +125°C                                                                |

| Operating Temperature<br>Range                                                    | 0°C to +85°C                                                                   |

| Junction Temperature                                                              | 150°C                                                                          |

| ESD Protection (HBM) on<br>HDMI Input Pins                                        | ±8 kV                                                                          |

| ESD Protection (HBM) on<br>All Other Pins                                         | ±2.5 kV                                                                        |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

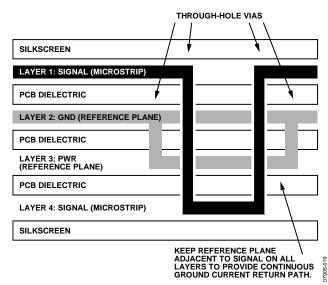

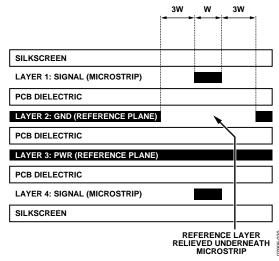

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions; a device soldered in a 4-layer JEDEC circuit board for surface-mount packages.  $\theta_{JC}$  is specified for the exposed pad soldered to the circuit board with no airflow.

#### **Table 5. Thermal Resistance**

| Package Type           | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|------------------------|-----------------|-----------------|------|

| 80-Lead LQFP (ST-80-2) | 51.3            | 15.3            | °C/W |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. Pin Configuration

| Table 6. Pin Function Descriptions |             |         |                                           |  |  |  |

|------------------------------------|-------------|---------|-------------------------------------------|--|--|--|

| Pin No.                            | Mnemonic    | Туре    | Description                               |  |  |  |

| 1                                  | IN_B_CLK-   | TMDS    | High Speed TMDS Input B Clock Complement. |  |  |  |

| 2                                  | IN_B_CLK+   | TMDS    | High Speed TMDS Input B Clock.            |  |  |  |

| 3                                  | HPD_B       | HPD     | Hot Plug Detect Output B.                 |  |  |  |

| 4                                  | IN_B_DATA0- | TMDS    | High Speed TMDS Input B Data Complement.  |  |  |  |

| 5                                  | IN_B_DATA0+ | TMDS    | High Speed TMDS Input B Data.             |  |  |  |

| 6                                  | HPD_A       | HPD     | Hot Plug Detect Output A.                 |  |  |  |

| 7                                  | IN_B_DATA1- | TMDS    | High Speed TMDS Input B Data Complement.  |  |  |  |

| 8                                  | IN_B_DATA1+ | TMDS    | High Speed TMDS Input B Data.             |  |  |  |

| 9, 18, 33, 43, 52                  | AVCC        | Power   | Positive Analog Supply 3.3 V.             |  |  |  |

| 10                                 | IN_B_DATA2- | TMDS    | High Speed TMDS Input B Data Complement.  |  |  |  |

| 11                                 | IN_B_DATA2+ | TMDS    | High Speed TMDS Input B Data.             |  |  |  |

| 12                                 | SELO        | Control | Channel Select Parallel Control LSB.      |  |  |  |

| 13                                 | IN_A_CLK-   | TMDS    | High Speed TMDS Input A Clock Complement. |  |  |  |

| 14                                 | IN_A_CLK+   | TMDS    | High Speed TMDS Input A Clock.            |  |  |  |

| 15                                 | SEL1        | Control | Channel Select Parallel Control MSB.      |  |  |  |

| 16                                 | IN_A_DATA0- | TMDS    | High Speed TMDS Input A Complement.       |  |  |  |

| 17                                 | IN_A_DATA0+ | TMDS    | High Speed TMDS Input A Data.             |  |  |  |

| 19                                 | IN_A_DATA1- | TMDS    | High Speed TMDS Input A Data Complement.  |  |  |  |

| 20                                 | IN_A_DATA1+ | TMDS    | High Speed TMDS Input A Data.             |  |  |  |

| 21, 30, 46                         | AVEE        | Power   | Negative Analog Supply 0.0 V.             |  |  |  |

| 22                                 | IN_A_DATA2- | TMDS    | High Speed TMDS Input A Data Complement.  |  |  |  |

| 23                                 | IN_A_DATA2+ | TMDS    | High Speed TMDS Input A Data.             |  |  |  |

|                                    |             | Re      | N B Page 6 of 28                          |  |  |  |

#### **Table 6. Pin Function Descriptions** Ρ

| Pin No.     Memonic     Type     Description       24     T.C.EN     Control     TMOS Curput Enable Parallel Control.       25     OUT_DATA2-     TMOS     High Speed TMOS Output. Enable Active Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pin No. | Mnemonic    | Type    | Description                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|---------|--------------------------------------------------------|

| 55 OUT_DATA2- TMDS High Speed TMDS Output.   26 OUT_DATA1- TMDS High Speed TMDS Output.   27 OUT_DATA1+ TMDS High Speed TMDS Output.   29 OUT_DATA1- TMDS High Speed TMDS Output.   31 OUT_DATA1- TMDS High Speed TMDS Output.   32 OUT_DATA0- TMDS High Speed TMDS Output.   34 OUT_CLK- TMDS High Speed TMDS Output.   35 OUT_CLK- TMDS High Speed TMDS Output.   36 RESETB Control Configuration Registers Reset. Active low.   37 IN_D_CLK- TMDS High Speed TMDS Input D Clock.   38 IN D CLK TMDS High Speed TMDS Input D Clock.   39 IZC_ADDRI Control Serial Control Intain Input/Output.   41 IN_D_DATA0- TMDS High Speed TMDS Input D Data.   42 IN_D_DATA0- TMDS High Speed TMDS Input D Data.   43 IN_D_DATA0- TMDS High Speed TMDS Input D Data.   44 IN_D_DATA2- TMDS High Speed TMDS Input D Data.   45 IN_D_DATA2- TMDS High Speed TMDS Input D Data.   46 IN_D_DATA2- TMDS High Speed TMDS Input C Da                                                                                                                                                                                                                                                                                                                                                                 |         |             |         |                                                        |

| 66 OUT_DATA1+ TMDS High Speed TMDS Output Complement.   77 IZC_SCL Control Seid Control Cock Input.   78 OUT_DATA1+ TMDS High Speed TMDS Output.   79 OUT_DATA0+ TMDS High Speed TMDS Output.   71 OUT_DATA0+ TMDS High Speed TMDS Output.   72 OUT_DATA0+ TMDS High Speed TMDS Output.   74 OUT_CLK+ TMDS High Speed TMDS Output.   75 OUT_CLK+ TMDS High Speed TMDS Output.   76 OUT_CLK+ TMDS High Speed TMDS Input D Clock.   76 IN_D_CLK- TMDS High Speed TMDS Input D Clock.   77 IN_D_CLK- TMDS High Speed TMDS Input D Clock.   78 IN_D_CLK- TMDS High Speed TMDS Input D Otack.   79 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   74 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   74 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   74 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   74 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   74 IN_D_DATA0+ TMDS High Speed TMDS Input C Data.                                                                                                                                                                                                                                                                                                                                                                      |         |             |         |                                                        |

| 27 IZ.SCL Control Serial Control Clock Imput.   28 OUT_DATA1+ TMDS High Speed TMDS Output.   29 OUT_DATA+ TMDS High Speed TMDS Output.   31 OUT_DATA+ TMDS High Speed TMDS Output.   32 OUT_DATA+ TMDS High Speed TMDS Output.   34 OUT_CLK+ TMDS High Speed TMDS Output. Clock.   35 OUT_CLK- TMDS High Speed TMDS Output. Clock.   36 RESETB Control Configuration Registers Reset. Active low.   37 IN.D_CLK+ TMDS High Speed TMDS Input D Clock. Complement.   38 IN.D_LCK+ TMDS High Speed TMDS Input D Clock.   40 IZ_CADDR Control Serial Control External Address MSB.   41 IN.D_DATA- TMDS High Speed TMDS Input D Data   42 IN.D_DATA- TMDS High Speed TMDS Input D Data   43 IN.D_DATA- TMDS High Speed TMDS Input D Data   44 IN.D_DATA- TMDS High Speed TMDS Input D Data   45 IN.D_DATA- TMDS High Speed TMDS Input D Data   46 IN.D_DATA- TMDS High Speed TMDS Input D Data   47 IN.D_DATA- TMDS High                                                                                                                                                                                                                                                                                                                                                                  |         |             |         |                                                        |

| 28 OUT_DATA1+ TMDS High Speed TMDS Output.   29 OUT_DATA0+ TMDS High Speed TMDS Output. Complement.   31 OUT_DATA0+ TMDS High Speed TMDS Output. Complement.   32 OUT_CLK+ TMDS High Speed TMDS Output. Complement.   34 OUT_CLK+ TMDS High Speed TMDS Output. Clock. Complement.   36 RESTB Control Configuration Registers Rest. Active low.   37 IN_D_CLK+ TMDS High Speed TMDS Input D Clock. Complement.   38 IN_D_CLK+ TMDS High Speed TMDS Input D Clock.   39 IZ_ADDRI Control Serial Control Data Input/Output.   40 IZ_SDA Control Serial Control Data Input/Output.   41 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   42 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   43 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   44 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   45 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   46 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   47 IN_D_DATA0+ TMDS High Speed TMDS Input D Data. <td< td=""><td></td><td>_</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                     |         | _           |         |                                                        |

| 99OUT_DATA1-<br>OUT_DATA0+TMDSHigh Speed TMDS Output Complement.31OUT_DATA0+TMDSHigh Speed TMDS Output Cock32OUT_DATA0-TMDSHigh Speed TMDS Output Clock34OUT_CLK+TMDSHigh Speed TMDS Output Clock35OUT_CLK-TMDSHigh Speed TMDS Output Clock36RESETBControlConfiguration Registers Reset. Active low.37IN_D_CLK+TMDSHigh Speed TMDS Input D Clock38IN_D_CLK+TMDSHigh Speed TMDS Input D Clock.39IZ_ADDR1ControlSerial Control Data Input/Output.41IN_D_DATA0-TMDSHigh Speed TMDS Input D Data.42IN_D_DATA0+TMDSHigh Speed TMDS Input D Data.43IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.44IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.45IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.46IN_D_DATA2+TMDSHigh Speed TMDS Input C Data Complement.47IN_D_DATA2+TMDSHigh Speed TMDS Input C Data.48IN_D_DATA2+TMDSHigh Speed TMDS Input C Data.49IZ_CADDR0ControlSerial Control Bata Complement.51IN_C_CLK+TMDSHigh Speed TMDS Input C Data.53HP_D_CHPDHigh Speed TMDS Input C Data.54IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.55HPD_CHPDHot Plug Detect Output D.56IN_C                                                                                                                                                                                                                |         |             |         |                                                        |

| 31 OUT_DATA0+ TMDS High Speed TMDS Output Complement.   32 OUT_DATA0- TMDS High Speed TMDS Output Cock.   34 OUT_CLK+ TMDS High Speed TMDS Output Clock.   35 OUT_CLK+ TMDS High Speed TMDS Output Clock.   36 RESTB Configuration Registers. Resct. Active low.   37 IN_D_CLK+ TMDS High Speed TMDS Input D Clock.   38 IN_D_CLK+ TMDS High Speed TMDS Input D Clock.   39 IZC_ADDR1 Control Serial Control External Address MS8.   40 IZC_SDA Control Serial Control External Address MS8.   41 IN_D_DATA0+ TMDS High Speed TMDS Input D Data.   42 IN_D_DATA1+ TMDS High Speed TMDS Input D Data.   43 IN_D_DATA2- TMDS High Speed TMDS Input D Data.   44 IN_D_DATA2- TMDS High Speed TMDS Input D Data.   45 IN_D_DATA2- TMDS High Speed TMDS Input D Data.   46 IN_C_CLK+ TMDS High Speed TMDS Input C Data.   47 IN_D_DATA2- TMDS High Speed TMDS Input C Data.   48 IN_D_DATA2- TMDS High Speed TMDS Input C Data.   51 IN_C_CLK+ TMDS<                                                                                                                                                                                                                                                                                                                                       |         |             |         |                                                        |

| 32OUT_DATAD-<br>OUT_CLK+TMDSHigh Speed TMDS Output Conplement.34OUT_CLK+TMDSHigh Speed TMDS Output Clock Complement.35OUT_CLK+TMDSHigh Speed TMDS Input D Clock Complement.36RESTBControlConfiguration Registers Reset. Active low.37IN.D_CLK+TMDSHigh Speed TMDS Input D Clock Complement.38IN_D_CLK+TMDSHigh Speed TMDS Input D Clock.39I2C_ADDR1ControlSerial Control Data Input/Output.41IN_D_DATAD-TMDSHigh Speed TMDS Input D Data.42IN_D_DATAD-TMDSHigh Speed TMDS Input D Data.43IN_D_DATAT-TMDSHigh Speed TMDS Input D Data.44IN_D_DATAT-TMDSHigh Speed TMDS Input D Data.45IN_D_DATAT-TMDSHigh Speed TMDS Input D Data.46IN_D_DATAT-TMDSHigh Speed TMDS Input D Data.47IN_D_DATAT-TMDSHigh Speed TMDS Input C Clock.58IN_C_CLK+TMDSHigh Speed TMDS Input C Clock.59IN_C_CLK+TMDSHigh Speed TMDS Input C Data.51IN_C_CLK+TMDSHigh Speed TMDS Input C Data.53HPD_DHPDHot Plug Detect Output C54IN_C_DATA+TMDSHigh Speed TMDS Input C Data.55HPD_CHPDHot Plug Detect Output C56IN_C_DATA+TMDSHigh Speed TMDS Input C Data.57IN_C_DATA+TMDSHigh Speed TMDS Input C Data.5                                                                                                                                                                                                       |         |             |         |                                                        |

| 94OUT_CLK+TMDSHigh Speed TMDS Output Clock.35OUT_CLK-TMDSHigh Speed TMDS Output Clock. Complement.36RESETBControlConfiguration Registers Reset. Active low.37IN_D_CLK+TMDSHigh Speed TMDS Input D Clock.38IN_D_CLK+TMDSHigh Speed TMDS Input D Clock.39IZ_ADDR1ControlSerial Control External Address MSB.40IZ_SDAControlSerial Control Data Input/Output.41IN_D_DATA0+TMDSHigh Speed TMDS Input D Data Complement.42IN_D_DATA0+TMDSHigh Speed TMDS Input D Data Complement.43IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.44IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.45IN_D_DATA2+TMDSHigh Speed TMDS Input Clock.46IN_D_DATA2+TMDSHigh Speed TMDS Input Clock.47IN_D_DATA2+TMDSHigh Speed TMDS Input Clock.48IN_C_CLK+TMDSHigh Speed TMDS Input Clock.59IN_C_CLK+TMDSHigh Speed TMDS Input Clock.51IN_C_CLK+TMDSHigh Speed TMDS Input Clock.53HPD_DHIPHot Plug Detect Output D.54IN_C_DATA2+TMDSHigh Speed TMDS Input Clock.55HPD_CHPDHot Plug Detect Output D.56IN_C_DATA2+TMDSHigh Speed TMDS Input Clock.57IN_C_DATA2+TMDSHigh Speed TMDS Input ClotaComplement.58 <t< td=""><td></td><td></td><td></td><td></td></t<>                                                                                                                                                         |         |             |         |                                                        |

| 35OUT_CLK-TMDSHigh Speed TMDS Output Clock Complement.36RESETBControlConfiguration Registers Reset, Active low.37IN.D. CLK-TMDSHigh Speed TMDS Input D Clock Complement.38IN.D. CLK+TMDSHigh Speed TMDS Input D Clock Complement.39IZCADDR1ControlSerial Control Data Input/Output.40IZC_SDAControlSerial Control Data Input/Output.41IN.D. DATA0+TMDSHigh Speed TMDS Input D Data42IN.D. DATA0+TMDSHigh Speed TMDS Input D Data.44IN.D. DATA1+TMDSHigh Speed TMDS Input D Data.47IN.D. DATA2+TMDSHigh Speed TMDS Input D Data.48IN.D. DATA2+TMDSHigh Speed TMDS Input D Data.49IZC_ADDR0ControlSerial Control External Address LSB.50IN.C. CLK+TMDSHigh Speed TMDS Input C Clock Complement.51IN.C. DATA0+TMDSHigh Speed TMDS Input C Data.53IN.C. DATA1+TMDSHigh Speed TMDS Input C Data54IN.C. DATA1+TMDSHigh Speed TMDS Input C Data55IN.C. DATA1+TMDSHigh Speed TMDS Input C Data56IN.C. DATA1+TMDSHigh Speed TMDS Input C Data57IN.C. DATA2+TMDSHigh Speed TMDS Input C Data58HPD.CHPDHor Pure Detect Output C.59IN.C. DATA2+TMDSHigh Speed TMDS Input C Data60IN.C. DATA2+TMDSHigh Speed TM                                                                                                                                                                                    |         |             |         |                                                        |

| 36REST BControlConfiguration Registers Reset. Active low.37IN_D_CLK-TMDSHigh Speed TMDS Input D Clock.38IN_D_CLK+TMDSSerial Control External Address MSR.40IZC_SDAControlSerial Control External Address MSR.41IN_D_DATA0-TMDSHigh Speed TMDS Input D Data Complement.42IN_D_DATA0+TMDSHigh Speed TMDS Input D Data Complement.43IN_D_DATA1+TMDSHigh Speed TMDS Input D Data Complement.44IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.45IN_D_DATA2+TMDSHigh Speed TMDS Input D Data46IN_D_DATA2+TMDSHigh Speed TMDS Input D Data47IN_D_DATA2+TMDSHigh Speed TMDS Input D Data48IN_D_DATA2+TMDSHigh Speed TMDS Input D Data49IZC_ADDR0ControlSerial Control External Address LSR.50IN_C_CLK+TMDSHigh Speed TMDS Input C Data51IN_C_CLK+TMDSHigh Speed TMDS Input C Data53IN_C_DATA0+TMDSHigh Speed TMDS Input C Data54IN_C_DATA0+TMDSHigh Speed TMDS Input C Data55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA2+TMDSHigh Speed TMDS Input C Data57IN_C_DATA2+TMDSHigh Speed TMDS Input C Data58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2+TMDSHigh Speed TMDS Input C Data60<                                                                                                                                                                                                      |         |             |         |                                                        |

| 37IN_D_CLK+TMDSHigh Speed TMDS Input D Clock Complement.38IN_D_CLK+TMDSHigh Speed TMDS Input D Clock39IZC_ADDR1ControlSerial Control Data Input/Output.40IZC_SDAControlSerial Control Data Input/Output.41IN_D_DATA0+TMDSHigh Speed TMDS Input D Data Complement.42IN_D_DATA0+TMDSHigh Speed TMDS Input D Data Complement.43IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.44IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.45IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.46IN_D_DATA2+TMDSHigh Speed TMDS Input C Data.47IN_D_DATA2+TMDSHigh Speed TMDS Input C Clock Complement.48IN_D_DATA2+TMDSHigh Speed TMDS Input C Clock Complement.51IN_C_CLK+TMDSHigh Speed TMDS Input C Clock.53IN_C_DATA0+TMDSHigh Speed TMDS Input C Clock.54IN_C_DATA1+TMDSHigh Speed TMDS Input C Clock.55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output D.59IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.60IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.61EDID_SDAControlExternal EDID EPROM Serial Interfa                                                                                                                                                                                    |         |             |         |                                                        |

| 38IN_D_CLK+TMDSHigh Speed TMDS Input D Clock.39IZC_ADDRIControlSerial Control External Address MSB.40IZC_SDAControlSerial Control Data Input/Output.41IN_D_DATA0-TMDSHigh Speed TMDS Input D Data Complement.42IN_D_DATA0+TMDSHigh Speed TMDS Input D Data.43IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.44IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.47IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.48IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.50IN_C_CLK+TMDSHigh Speed TMDS Input C Clock Complement.51IN_C_CLK+TMDSHigh Speed TMDS Input C Clock.53IN_C_CLK+TMDSHigh Speed TMDS Input C Data.54IN_C_DATA0+TMDSHigh Speed TMDS Input C Data.55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EPROM Serial Interface Clock.62EDID_SADControlExternal EDID EERPONS Serial Interface Clock.63EDID_SCLControlExternal EDID EERPONS Serial Interface Clock.64AMUXVCCPowerPositive Power Supply 50V.                                                                                                                                                                                    |         |             |         |                                                        |

| 39I2C_ADDR1ControlSerial Control External Address MS8.40I2C_SDAControlSerial Control Data Input/Output.41IN_D_DATA0-TMDSHigh Speed TMDS Input D Data.42IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.43IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.44IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.45IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.46IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.47IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.48IN_D_DATA2+TMDSHigh Speed TMDS Input C Clock Complement.50IN_C_CLK+TMDSHigh Speed TMDS Input C Clock Complement.51IN_C_DATA0-TMDSHigh Speed TMDS Input C Clock.53IN_C_DATA0+TMDSHigh Speed TMDS Input C Data.56IN_C_DATA1-TMDSHigh Speed TMDS Input C Data.57IN_C_DATA1-TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA1-TMDSHigh Speed TMDS Input C Data.61EDID_SDAControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Clock.63EDID_SDAControlExternal EDID EEPROM Serial Interface Clock.64AMUXVCPowerPower Supply 5.0.V.65CEC_INCECConsumer Electronics Contro                                                                                                                                                                                    | 37      |             |         |                                                        |

| 40I2C_SDAControlSerial Control Data Input/Output.41IN_D_DATAO-TMDSHigh Speed TMDS Input D Data.42IN_D_DATAI-TMDSHigh Speed TMDS Input D Data.43IN_D_DATAI-TMDSHigh Speed TMDS Input D Data Complement.44IN_D_DATAI-TMDSHigh Speed TMDS Input D Data Complement.45IN_D_DATA2-TMDSHigh Speed TMDS Input D Data Complement.46IN_D_DATA2-TMDSHigh Speed TMDS Input D Data.47IN_C_CLK-TMDSHigh Speed TMDS Input D Data.49IDC_ADDROControlSerial Control External Address LSB.50IN_C_CLK+TMDSHigh Speed TMDS Input C Data.51IN_C_DATAO-TMDSHigh Speed TMDS Input C Data.53IN_C_DATAO+TMDSHigh Speed TMDS Input C Data.54IN_C_DATAO+TMDSHigh Speed TMDS Input C Data.55HPD_DHPDHPD Hot Plug Detect Output D.56IN_C_DATAI+TMDSHigh Speed TMDS Input C Data.57IN_C_DATAI+TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHPD Hot Plug Detect Output C.59IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Clock.63EDID_ENABLEControlExternal EDID EEPROM Serial Interface Clock.64AMUXYCCPowerPost                                                                                                                                                                                    | 38      | IN_D_CLK+   | TMDS    |                                                        |

| 41IN_D_DATA0-TMDSHigh Speed TMDS Input D Data Complement.42IN_D_DATA0+TMDSHigh Speed TMDS Input D Data.43IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.44IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.47IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.48IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.49IZC_ADDR0ControlSerial Control External Address LS8.50IN_C_CLK+TMDSHigh Speed TMDS Input C Clock.51IN_C_DATA0+TMDSHigh Speed TMDS Input C Clock.53IN_C_DATA0+TMDSHigh Speed TMDS Input C Data Complement.54IN_C_DATA0+TMDSHigh Speed TMDS Input C Data Complement.55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data Complement.57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data Complement.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2+TMDSHigh Speed TMDS Input C Data Complement.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data Complement.61EDD_SDAControlExternal EDD EPRNOM Serial Interface Clock.62EDD_DABLEControlExternal EDDI EPRNOM Serial Interface Clock.63EDD_SDAControlExternal EDDI EPRNOM Serial Interface Clock.64AMUXVCCPowerPositi Power Southol Spialy Data Channel Serial Clock Input/Out                                                                                                                                       | 39      |             | Control |                                                        |

| 42IN_D_DATA0+TMDSHigh Speed TMDS Input D Data.44IN_D_DATA1-TMDSHigh Speed TMDS Input D Data.45IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.47IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.48IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.49IZ_ADDROControlSerial Control External Address LSB.50IN_C_CLK-TMDSHigh Speed TMDS Input C Clock.51IN_C_DATA0+TMDSHigh Speed TMDS Input C Data.53IN_C_DATA0+TMDSHigh Speed TMDS Input C Data.54IN_C_DATA0+TMDSHigh Speed TMDS Input C Data.55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.58HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.57IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDD_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDD_SACControlExternal EDID EEPROM Serial Interface Clock.63EDD_SACControlExternal EDID EEPROM Serial Interface Clock.64AMUXYCCPowerPositive Power Supply 5.0V.65CEC_OUTCECConsume Electronics Control Input.67                                                                                                                                                                                                           | 40      | I2C_SDA     |         |                                                        |

| 44IN_D_DATA1-TMDSHigh Speed TMDS Input D Data Complement.45IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.47IN_D_DATA2-TMDSHigh Speed TMDS Input D Data.48IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.49IZC_ADDR0ControlSerial Control External Address ISB.50IN_C_CLK+TMDSHigh Speed TMDS Input C Clock.51IN_C_CLK+TMDSHigh Speed TMDS Input C Clock.53IN_C_DATA0+TMDSHigh Speed TMDS Input C Data Complement.54IN_C_DATA0+TMDSHigh Speed TMDS Input C Data55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2+TMDSHigh Speed TMDS Input C Data60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data61EDID_SDAControlExternal EDID EPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EPROM Serial Interface Clock.63EDID_SDAControlExternal EDID EPROM Serial Interface Clock.64AMUXVCCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_UTCECConsumer Electronics Control Output.67DDC_SDA_CDMDDCDisplay Data Channel Serial Iclock                                                                                                                                                                                    | 41      | IN_D_DATA0- | TMDS    | High Speed TMDS Input D Data Complement.               |

| 45IN_D_DATA1+TMDSHigh Speed TMDS Input D Data.47IN_D_DATA2+TMDSHigh Speed TMDS Input D Data Complement.48IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.49I2C_ADDR0ControlSerial Control External Address LS8.50IN_C_CLK+TMDSHigh Speed TMDS Input C Clock Complement.51IN_C_CLK+TMDSHigh Speed TMDS Input C Clock Complement.53IN_C_DATA0-TMDSHigh Speed TMDS Input C Data.54IN_C_DATA0+TMDSHigh Speed TMDS Input C Data55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2+TMDSHigh Speed TMDS Input C Data60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data61EDID_SCLControlExternal EDID EPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EPROM Serial Interface Clock.63EDID_ENABLEControlExternal EDID EPROM Serial Interface Data.64AMUXVCCPowerPositive Power Supply S.0.V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Input.67DDC_SCL_OMDDCDisplay Data Channel Serial Interface Idock Input/Output.68DDC_SDA_DDDC <t< td=""><td>42</td><td>IN_D_DATA0+</td><td>TMDS</td><td>High Speed TMDS Input D Data.</td></t<>                                                                                | 42      | IN_D_DATA0+ | TMDS    | High Speed TMDS Input D Data.                          |

| 47IN_D_DATA2-TMDSHigh Speed TMDS Input D Data Complement.48IN_D_DATA2+TMDSHigh Speed TMDS Input D Data49I2C_ADDROControlSerial Control External Address LSB.50IN_C_CLK+TMDSHigh Speed TMDS Input C Clock Complement.51IN_C_DATA0-TMDSHigh Speed TMDS Input C Clock.53IN_C_DATA0-TMDSHigh Speed TMDS Input C Data Complement.54IN_C_DATA0+TMDSHigh Speed TMDS Input C Data.55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data Complement.61EDID_SCLControlExternal EDID EDROM Serial Interface Clock.62EDID_SDAControlExternal EDID EPROM Serial Interface Clock.63EDID_ENABLEControlExternal EDID EPROM Serial Interface Data.64AMUXVCCPowerPositive Power Supply 5.0V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INDDCDisplay Data Channel Serial Clock Input/Output.71DDC_SCL_COMDDCDisplay Data Channel Serial Data Input/Output.72DDC_SDA_COMDDCDisplay Data Channel Serial Data Input/Output C.73<                                                                                                                                                         | 44      | IN_D_DATA1- | TMDS    | High Speed TMDS Input D Data Complement.               |

| 48IN_D_DATA2+TMDSHigh Speed TMDS Input D Data.49IDC_ADDR0ControlSerial Control External Address LSB.50IN_C_CLK-TMDSHigh Speed TMDS Input C Clock. Complement.51IN_C_DATA0-TMDSHigh Speed TMDS Input C Data Complement.54IN_C_DATA0+TMDSHigh Speed TMDS Input C Data.55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.60IN_C_DATA2-TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Clock.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Input.67DDC_SCL_CDDDCDisplay Data Channel Serial Data Input/Output.68DDC_SDA_COMDDCDisplay Data Channel Serial Clock Input/Output.69DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output.71DDC_SCL_CDDCDisplay Data Channel Serial Data Input/Output C.73DDC_SCL_C </td <td>45</td> <td>IN_D_DATA1+</td> <td>TMDS</td> <td>High Speed TMDS Input D Data.</td>                                                                         | 45      | IN_D_DATA1+ | TMDS    | High Speed TMDS Input D Data.                          |

| 49I2C_ADDR0ControlSerial Control External Address LSB.50IN_C_CLK-TMDSHigh Speed TMDS Input C Clock Complement.51IN_C_DATA0-TMDSHigh Speed TMDS Input C Clock.53IN_C_DATA0+TMDSHigh Speed TMDS Input C Data Complement.54IN_C_DATA0+TMDSHigh Speed TMDS Input C Data.55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data Complement.57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data Complement.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2+TMDSHigh Speed TMDS Input C Data Complement.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Clock.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply 5.0V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Output.67DDC_SDA_COMDDCDisplay Data Channel Serial Clock Input/Output.68DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output.71DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output D.72DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output C. <td>47</td> <td>IN_D_DATA2-</td> <td>TMDS</td> <td>High Speed TMDS Input D Data Complement.</td>                                          | 47      | IN_D_DATA2- | TMDS    | High Speed TMDS Input D Data Complement.               |

| 50IN_C_CLK-TMDSHigh Speed TMDS Input C Clock Complement.51IN_C_CLK+TMDSHigh Speed TMDS Input C Clock.53IN_C_DATA0-TMDSHigh Speed TMDS Input C Data.54IN_C_DATA0+TMDSHigh Speed TMDS Input C Data.55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data Complement.57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2-TMDSHigh Speed TMDS Input C Data Complement.60IN_C_DATA2-TMDSHigh Speed TMDS Input C Data Complement.61EDID_SCLControlExternal EDID EPROM Serial Interface Clock.62EDID_DAControlExternal EDID EPROM Serial Interface Clock.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply 5.0V.65CEC_OUTCECConsumer Electronics Control Input.66DC_SCL_COMDCDisplay Data Channel Serial Data Common Input/Output.67DDC_SCL_CDDDCDisplay Data Channel Serial Data Input/Output D.71DDC_SCL_CDDCDisplay Data Channel Serial Data Input/Output D.72DC_SDA_DDDCDisplay Data Channel Serial Data Input/Output D.73DDC_SCL_GDDCDisplay Data Channel Serial Data Input/Output D.74DDC_SDA_BDDCDisplay Data Channel Serial Data Input/Outp                                                                                                                                       | 48      | IN_D_DATA2+ | TMDS    | High Speed TMDS Input D Data.                          |

| 51IN_C_CLK+TMDSHigh Speed TMDS Input C Clock.53IN_C_DATA0-TMDSHigh Speed TMDS Input C Data Complement.54IN_C_DATA0-TMDSHigh Speed TMDS Input C Data.55HPD_DHPDHOT Plug Detect Output D.56IN_C_DATA1-TMDSHigh Speed TMDS Input C Data.57IN_C_DATA1-TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2-TMDSHigh Speed TMDS Input C Data.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_ENABLEControlExternal EDID EEPROM Serial Interface Clock.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_OUTCECDosumer Electronics Control Input.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock Input/Output.68DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output.69DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output.61DDC_SCL_COMDDCDisplay Data Channel Serial Clock Input/Output.62DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output D.71 </td <td>49</td> <td>I2C_ADDR0</td> <td>Control</td> <td>Serial Control External Address LSB.</td>                                                        | 49      | I2C_ADDR0   | Control | Serial Control External Address LSB.                   |

| 53IN_C_DATAO-TMDSHigh Speed TMDS Input C Data Complement.54IN_C_DATAO+TMDSHigh Speed TMDS Input C Data.55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1+TMDSHigh Speed TMDS Input C Data Complement.57III_C_DATA1+TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output C.59III_C_DATA2-TMDSHigh Speed TMDS Input C Data Complement.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Clock.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECDisplay Data Channel Serial Clock Common Input/Output.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock Input/Output.68DDC_SA_DDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output C.71DDC_SCL_CDDCDisplay Data Channel Serial Data Input/Output C.72DDC_SDA_DDDCDisplay Data Channel Serial Data Input/Output C.73DDC_SCL_CDDCDisplay Data Channel Serial Data Input/Output C.74DDC_SCL_CDDCDisplay Data                                                                                                                                        | 50      | IN_C_CLK-   | TMDS    | High Speed TMDS Input C Clock Complement.              |

| 54IN_C_DATA0+TMDSHigh Speed TMDS Input C Data.55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1-TMDSHigh Speed TMDS Input C Data Complement.57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Clock.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply S.OV.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Input.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock Common Input/Output.68DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output D.71DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output C.72DDC_SDA_CDDCDisplay Data Channel Serial Data Input/Output C.73DDC_SCL_ADDCDisplay Data Channel Serial Data Input/Output C.74DDC_SDA_BDDCDisplay Data Channel Serial Data Input/Output C.75DDC_SCL_ADDCDisplay Data Channel Serial Data                                                                                                                                       | 51      | IN_C_CLK+   | TMDS    | High Speed TMDS Input C Clock.                         |

| 55HPD_DHPDHot Plug Detect Output D.56IN_C_DATA1-TMDSHigh Speed TMDS Input C Data Complement.57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2-TMDSHigh Speed TMDS Input C Data Complement.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Data.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply S.OV.65CEC_OUTCECConsumer Electronics Control Input.66CEC_INCECDisplay Data Channel Serial Clock Common Input/Output.67DDC_SCL_DDDCDisplay Data Channel Serial Clock Input/Output.68DDC_SDA_COMDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output D.71DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output C.73DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output B.74DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output B.75DDC_SCL_ADDCDisplay Data Channel Serial Clock Input/Output A.76DDC_SDA_ADDCDisplay Data Channel Serial Data Input/Output A.75DDC_SDA_ADDC </td <td>53</td> <td>IN_C_DATA0-</td> <td>TMDS</td> <td>High Speed TMDS Input C Data Complement.</td>                          | 53      | IN_C_DATA0- | TMDS    | High Speed TMDS Input C Data Complement.               |

| 56IN_C_DATA1-TMDSHigh Speed TMDS Input C Data Complement.57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2-TMDSHigh Speed TMDS Input C Data Complement.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Data.63EDID_ENABLEControlExternal EDID EEPROM Serial Interface Data.64AMUXVCCPowerPositive Power Supply S.V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Output.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock Common Input/Output.68DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SDA_CDDCDisplay Data Channel Serial Clock Input/Output D.71DDC_SDA_CDDCDisplay Data Channel Serial Data Input/Output C.72DDC_SDA_BDDCDisplay Data Channel Serial Clock Input/Output C.73DDC_SDA_BDDCDisplay Data Channel Serial Clock Input/Output B.74DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output B.75DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output B.76DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output B.<                                                                                                        | 54      | IN_C_DATA0+ | TMDS    | High Speed TMDS Input C Data.                          |

| 57IN_C_DATA1+TMDSHigh Speed TMDS Input C Data.58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2-TMDSHigh Speed TMDS Input C Data Complement.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Data.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCCCConsumer Electronics Control Output.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock Common Input/Output.68DDC_SDA_COMDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SCL_DDDCDisplay Data Channel Serial Clock Input/Output D.71DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output C.72DDC_SDA_CDDCDisplay Data Channel Serial Data Input/Output C.73DDC_SCL_BDDCDisplay Data Channel Serial Clock Input/Output B.74DDC_SDA_BDDCDisplay Data Channel Serial Clock Input/Output B.75DDC_SCL_ADDCDisplay Data Channel Serial Clock Input/Output B.76DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output B.77PSV_DPowerS V HDMI Supply from Source D.78PSV_CPo                                                                                                                              | 55      | HPD_D       | HPD     | Hot Plug Detect Output D.                              |

| 58HPD_CHPDHot Plug Detect Output C.59IN_C_DATA2-TMDSHigh Speed TMDS Input C Data Complement.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Data.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Input.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock formon Input/Output.68DDC_SDA_CDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SCL_DDDCDisplay Data Channel Serial Clock Input/Output D.71DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output D.72DDC_SDA_CDDCDisplay Data Channel Serial Clock Input/Output C.73DDC_SCL_BDDCDisplay Data Channel Serial Clock Input/Output B.74DDC_SDA_BDDCDisplay Data Channel Serial Clock Input/Output B.75DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output A.76DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output A.77PSV_DPowerSV HDMI Supply from Source D.78PSV_CPowerSV HDMI Supply from Source C.79PSV_BPower<                                                                                                                                   | 56      | IN_C_DATA1- | TMDS    | High Speed TMDS Input C Data Complement.               |

| 59IN_C_DATA2-TMDSHigh Speed TMDS Input C Data Complement.60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Data.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Input.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock Common Input/Output.68DDC_SCL_DDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SCL_DDDCDisplay Data Channel Serial Clock Input/Output D.71DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output C.72DDC_SDA_CDDCDisplay Data Channel Serial Clock Input/Output C.73DDC_SCL_BDDCDisplay Data Channel Serial Clock Input/Output C.74DDC_SDA_BDDCDisplay Data Channel Serial Clock Input/Output B.75DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output B.76DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output B.77DDC_SDA_BDDCDisplay Data Channel Serial Clock Input/Output B.76DDC_SDA_BDDCDisplay Data Channel Serial Clock Input/Output B.77PSV_DPowerS V HDMI Supply from Source D. </td <td>57</td> <td>IN_C_DATA1+</td> <td>TMDS</td> <td>High Speed TMDS Input C Data.</td> | 57      | IN_C_DATA1+ | TMDS    | High Speed TMDS Input C Data.                          |

| 60IN_C_DATA2+TMDSHigh Speed TMDS Input C Data.61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Data.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Output.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock Common Input/Output.68DDC_SDA_COMDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output D.71DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output C.72DDC_SDA_CDDCDisplay Data Channel Serial Clock Input/Output C.73DDC_SCL_BDDCDisplay Data Channel Serial Data Input/Output B.74DDC_SDA_ADDCDisplay Data Channel Serial Data Input/Output B.75DDC_SCL_ADDCDisplay Data Channel Serial Clock Input/Output B.76DDC_SDA_ADDCDisplay Data Channel Serial Data Input/Output B.76DDC_SDA_ADDCDisplay Data Channel Serial Data Input/Output B.76DDC_SDA_ADDCDisplay Data Channel Serial Data Input/Output B.77PSV_DPowerS V HDMI Supply from Source D.78PSV_CPowerS V HDMI Supply from Source C.7                                                                                                            | 58      | HPD_C       | HPD     | Hot Plug Detect Output C.                              |

| 61EDID_SCLControlExternal EDID EEPROM Serial Interface Clock.62EDID_SDAControlExternal EDID EEPROM Serial Interface Data.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Input.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock Common Input/Output.68DDC_SDA_COMDDCDIsplay Data Channel Serial Clock Input/Output D.69DDC_SCL_DDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output D.71DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output C.72DDC_SDA_CDDCDisplay Data Channel Serial Clock Input/Output C.73DDC_SCL_BDDCDisplay Data Channel Serial Clock Input/Output B.74DDC_SDA_BDDCDisplay Data Channel Serial Clock Input/Output B.75DDC_SCL_ADDCDisplay Data Channel Serial Clock Input/Output B.76DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output A.77PSV_DPowerS V HDMI Supply from Source D.78PSV_CPowerS V HDMI Supply from Source C.79PSV_BPowerS V HDMI Supply from Source B.                                                                                                                                                                            | 59      | IN_C_DATA2- | TMDS    | High Speed TMDS Input C Data Complement.               |

| 62EDID_SDAControlExternal EDID EEPROM Serial Interface Data.63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Input.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock Common Input/Output.68DDC_SDA_COMDDCDisplay Data Channel Serial Clock Input/Output D.69DDC_SCL_DDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SDA_DDDCDisplay Data Channel Serial Clock Input/Output D.71DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output C.73DDC_SDA_CDDCDisplay Data Channel Serial Clock Input/Output B.74DDC_SDA_BDDCDisplay Data Channel Serial Data Input/Output B.75DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output B.76DDC_SDA_ADDCDisplay Data Channel Serial Data Input/Output B.77PSV_DPowerS V HDMI Supply from Source D.78PSV_CPowerS V HDMI Supply from Source C.79PSV_BPowerS V HDMI Supply from Source B.                                                                                                                                                                                                                                                                                                          | 60      | IN_C_DATA2+ | TMDS    | High Speed TMDS Input C Data.                          |

| 63EDID_ENABLEControlEDID Replication Enable.64AMUXVCCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Input.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock Common Input/Output.68DDC_SDA_COMDDCDisplay Data Channel Serial Clock Input/Output D.69DDC_SCL_DDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output D.71DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output C.72DDC_SDA_CDDCDisplay Data Channel Serial Clock Input/Output C.73DDC_SCL_BDDCDisplay Data Channel Serial Clock Input/Output C.74DDC_SDA_BDDCDisplay Data Channel Serial Clock Input/Output B.75DDC_SCL_ADDCDisplay Data Channel Serial Clock Input/Output B.76DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output A.77PSV_DPowerSV HDMI Supply from Source D.78PSV_CPowerSV HDMI Supply from Source C.79PSV_BPowerSV HDMI Supply from Source B.                                                                                                                                                                                                                                                                                                        | 61      | EDID_SCL    | Control | External EDID EEPROM Serial Interface Clock.           |

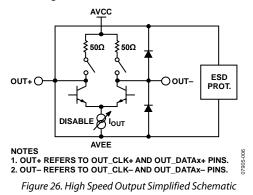

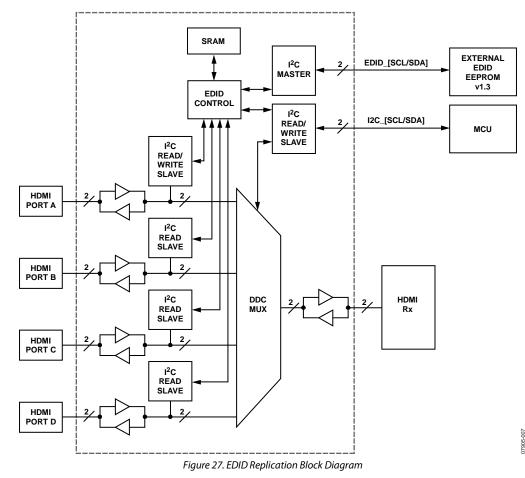

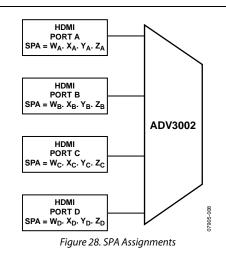

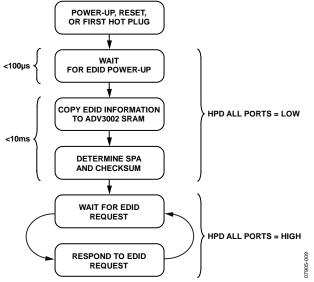

| 64AMUXVCCPowerPositive Power Supply 5.0 V.65CEC_OUTCECConsumer Electronics Control Output.66CEC_INCECConsumer Electronics Control Input.67DDC_SCL_COMDDCDisplay Data Channel Serial Clock Common Input/Output.68DDC_SDA_COMDDCDisplay Data Channel Serial Data Common Input/Output.69DDC_SCL_DDDCDisplay Data Channel Serial Clock Input/Output D.70DDC_SDA_DDDCDDC71DDC_SCL_CDDCDisplay Data Channel Serial Clock Input/Output C.72DDC_SDA_CDDCDisplay Data Channel Serial Clock Input/Output C.73DDC_SCL_BDDCDisplay Data Channel Serial Clock Input/Output B.74DDC_SDA_BDDCDisplay Data Channel Serial Clock Input/Output B.75DDC_SCL_ADDCDisplay Data Channel Serial Clock Input/Output B.76DDC_SDA_ADDCDisplay Data Channel Serial Clock Input/Output A.77PSV_DPowerS V HDMI Supply from Source D.78PSV_CPowerS V HDMI Supply from Source C.79PSV_BPowerS V HDMI Supply from Source B.                                                                                                                                                                                                                                                                                                                                                                                           | 62      | EDID_SDA    | Control | External EDID EEPROM Serial Interface Data.            |