LM3263

SNVS837B - JUNE 2013-REVISED APRIL 2016

# LM3263 High-Current Step-Down DC-DC Converter With MIPI® RF Front-End **Control Interface for RF Power Amplifiers**

#### **Features**

- MIPI® RFFE Digital Control Interface

- Operates from a Single Li-Ion Cell: 2.7 V to 5.5 V

- Dynamically Adjustable Output Voltage: 0.4 V to 3.6 V (Typical) in PFM and PWM Modes

- High-Efficiency PFM and PWM Modes With Internal Seamless Transition

- 2.5-A Maximum Load Current in PWM Mode

- 2.7 MHz (Typical) Switching Frequency

- ACB (Reduces Inductor Requirements and Size)

- Internal Compensation

- Current and Thermal Overload Protection

- Very Small Solution Size: Approximately 9.1 mm<sup>2</sup>

### **Applications**

- **Smartphones**

- RF PC Cards

- Tablets, eBook Readers

- Handheld Radios

- Battery-Powered RF Devices

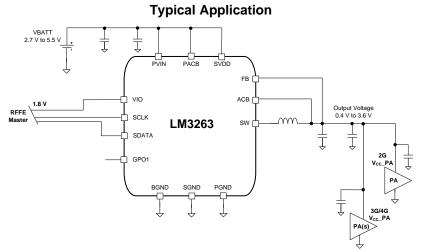

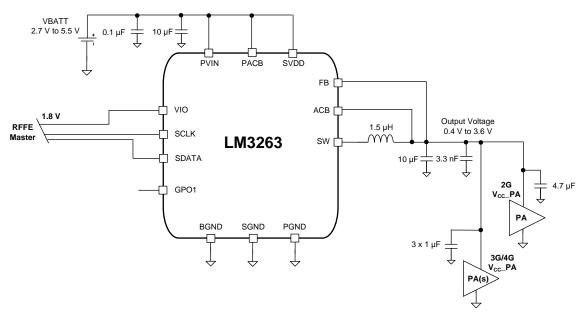

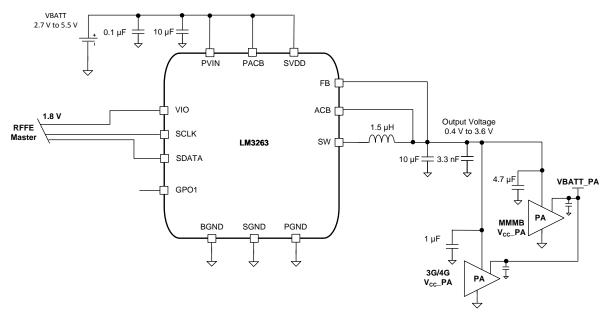

### 3 Description

The LM3263 is a DC-DC converter optimized for powering multi-mode multi-band RF power amplifiers (PAs) from a single lithium-ion cell. The LM3263 steps down an input voltage from 2.7 V to 5.5 V to a dynamically adjustable output voltage of 0.4 V to 3.6 V. The output voltage is externally programmed through the RFFE Digital Control Interface and is set to ensure efficient operation at all power levels of the RF PA.

When operating in pulse width modulated (PWM) mode, the LM3263 produces a small and predictable amount of output voltage ripple thus meeting the power and stringent spectral-compliance needs of RF PAs with minimal filtering and minimal excess headroom. When operating in PFM mode, the LM3263 enables the lowest current consumption across PA output power level settings and therefore maximizes system efficiency.

The LM3263 has a unique Active Current assist and analog Bypass (ACB) feature to minimize inductor size without any loss of output regulation for the entire battery voltage and RF output power range, until dropout. ACB provides a parallel current path, when needed, to limit the maximum inductor current to 1.45 A (typical) while still driving a 2.5-A load. The ACB feature also enables operation with minimal dropout voltage.

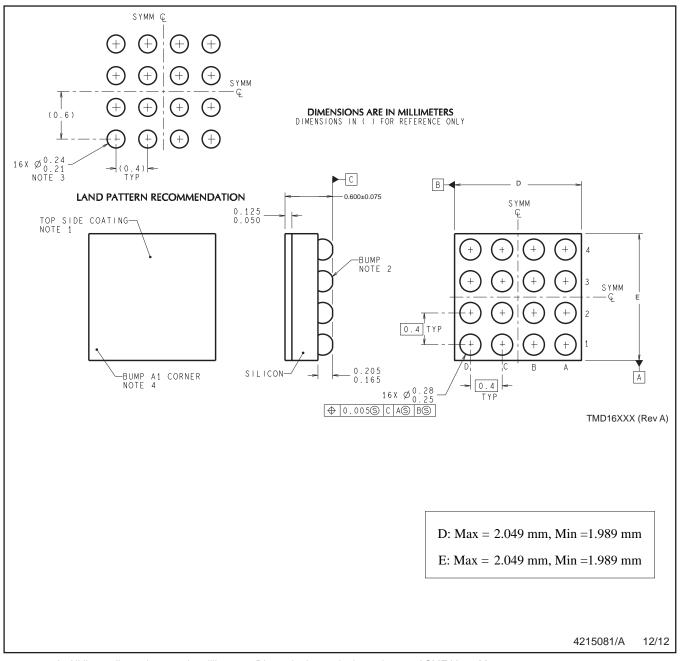

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (MAX)     |

|-------------|------------|---------------------|

| LM3263      | DSBGA (16) | 2.049 mm × 2.049 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

Copyright © 2016, Texas Instruments Incorporated

# **Table of Contents**

| 1 | Features 1                           | 7.5 Programming1                                    |

|---|--------------------------------------|-----------------------------------------------------|

| 2 | Applications 1                       | 7.6 Register Map2                                   |

| 3 | Description 1                        | 8 Application Information 24                        |

| 4 | Revision History2                    | 8.1 Application Information2                        |

| 5 | Pin Configuration and Functions      | 8.2 Typical Application2                            |

| 6 | Specifications4                      | 9 Power Supply Recommendations 2                    |

| • | 6.1 Absolute Maximum Ratings         | 10 Layout Considerations 2                          |

|   | 6.2 ESD Ratings                      | 10.1 Layout Guidelines2                             |

|   | 6.3 Recommended Operating Conditions | 10.2 4. Layout Examples2                            |

|   | 6.4 Thermal Information              | 10.3 DSBGA Package Assembly and Use 3               |

|   | 6.5 Electrical Characteristics       | 11 Device and Documentation Support 3               |

|   | 6.6 System Characteristics6          | 11.1 Device Support                                 |

|   | 6.7 Typical Characteristics          | 11.2 Documentation Support 3                        |

| 7 | Detailed Description 12              | 11.3 Community Resources3                           |

|   | 7.1 Overview                         | 11.4 Trademarks                                     |

|   | 7.2 Functional Block Diagram         | 11.5 Electrostatic Discharge Caution3               |

|   | 7.3 Feature Description              | 11.6 Glossary3                                      |

|   | 7.4 Device Functional Modes          | 12 Mechanical, Packaging, and Orderable Information |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision A (August 2013) to Revision B                                                                                                                                                                                                                                                         | Page |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Added Device Information and Pin Configuration and Functions sections, ESD Ratings and Feature Description, Device Functional Modes, Application and Implementation, Power Supply Recommendations, Layout, Device and Documentation Support, and Mechanical, Packaging, and Orderable Information sections | 1    |

| • | Added <i>Thermal Information</i> table with revised R <sub>θJA</sub> value (from 50°C/W to 77.1°C/W) and additional thermal values.                                                                                                                                                                        | 4    |

| С | Changes from Original (June 2013) to Revision A                                                                                                                                                                                                                                                            | Page |

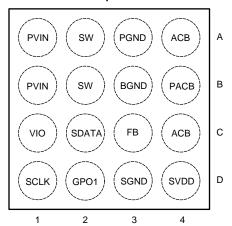

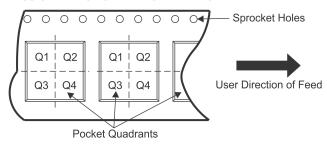

# 5 Pin Configuration and Functions

#### YFQ Package 16-Pin DSBGA Bottom View

#### **Pin Functions**

|        | PIN    | TVDE                    | DECODIDATION                                                                                                                                                                                 |  |  |

|--------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NUMBER | ITPE                    | DESCRIPTION                                                                                                                                                                                  |  |  |

| ACB    | A4     | Output                  | ACR and applied hypose output. Connect to the output at the output filter conscitor.                                                                                                         |  |  |

| ACB    | C4     | Output                  | Digital Digital control interface RFFE bus data input/output. Typically connected to RFFE                                                                                                    |  |  |

| BGND   | В3     | Ground                  | ACB, analog bypass ground, and digital ground.                                                                                                                                               |  |  |

| FB     | C3     | Input                   | Feedback analog input. Connect to the output at the output filter capacitor.                                                                                                                 |  |  |

| GPO1   | D2     | Output                  | General purpose output. Also used to reconfigure USID.                                                                                                                                       |  |  |

| PACB   | B4     | Power                   | ACB power supply input                                                                                                                                                                       |  |  |

| PGND   | A3     | Ground                  | Power ground to the internal NFET switch                                                                                                                                                     |  |  |

| DV/INI | A1     |                         | Davier augusts valtage input to the internal DEET quitch                                                                                                                                     |  |  |

| PVIN   | B1     | Power                   | rower supply voltage input to the internal FFET Switch                                                                                                                                       |  |  |

| SCLK   | D1     | Digital/Input           |                                                                                                                                                                                              |  |  |

| SDATA  | C2     | Digital<br>Input/Output |                                                                                                                                                                                              |  |  |

| SGND   | D3     | Ground                  | Signal analog ground (low current)                                                                                                                                                           |  |  |

| SVDD   | D4     | Power                   | Analog power supply voltage                                                                                                                                                                  |  |  |

| CW     | A2     | A = =   = =             | Switching node connection to the internal PFET switch and NFET synchronous                                                                                                                   |  |  |

| SW B2  |        | Analog                  | rectifier.                                                                                                                                                                                   |  |  |

| VIO    | C1     | Input                   | VIO functions as the RFFE interface reference voltage. VIO also functions as reset and enable input to the LM3263. Typically connected to voltage regulator controlled by RF or baseband IC. |  |  |

Copyright © 2013–2016, Texas Instruments Incorporated

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                            | MIN                | MAX                | UNIT |

|------------------------------------------------------------|--------------------|--------------------|------|

| VBATT pins to GND (PVIN, SVDD, PACB to PGND, SGND, BGND)   | -0.2               | 6                  | V    |

| FB, SW, GPO1, ACB, VIO, SDATA, SCLK                        | GND - 0.2 V        | See <sup>(3)</sup> | V    |

| Continuous power dissipation (4)                           | Internally limited |                    |      |

| Maximum operating junction temperature, T <sub>J-MAX</sub> |                    | 150                | °C   |

| Maximum lead temperature (soldering 10 seconds)            |                    | 260                | °C   |

| Storage temperature, T <sub>stg</sub>                      | -65                | 150                | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltages are with respect to the potential at the GND pins.

- 3) Abs Max for FB, SW, GPO1, ACB, VIO, SDATA, SCLK is the lessor of V<sub>IN</sub> + 0.2 V, or 6 V.

- (4) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 150°C (typical) and disengages at T<sub>J</sub> = 125°C (typical).

### 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V                  | Clastrostatia diseberge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±1000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±250  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                    | MIN  | MAX  | UNIT |

|----------------------------------------------------|------|------|------|

| Input voltage range PVIN, SVDD, PACB               | 2.7  | 5.5  | V    |

| Input voltage range VIO                            | 1.65 | 1.95 | V    |

| Recommended current load                           | 0    | 2.5  | Α    |

| Junction temperature, T <sub>J</sub>               | -30  | 125  | °C   |

| Ambient temperature, T <sub>A</sub> <sup>(1)</sup> | -30  | 90   | °C   |

<sup>(1)</sup> In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be de-rated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to ambient thermal resistance of the part/package in the application (R<sub>BJA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (R<sub>BJA</sub> × P<sub>D-MAX</sub>). At higher power levels duty cycle usage is assumed to drop (that is, maximum power 12.5% usage is assumed) for GSM/GPRS mode.

#### 6.4 Thermal Information

|                        |                                              | LM3263      |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | YFQ (DSBGA) | UNIT |

|                        |                                              | 16 PINS     |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 77.1        | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 0.4         | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 15.4        | °C/W |

| Ψлт                    | Junction-to-top characterization parameter   | 2.0         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 15.1        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

Unless otherwise noted, all limits apply to the *Typical Application* with V<sub>BATT</sub> = 3.8 V (= PVIN = SVDD = PACB), VIO = 1.8 V,  $T_J = 25^{\circ}C.^{(1)(2)(3)}$

|                             | PARAMETER                                | TEST CONDITIONS                                                                                                                                                                                                             | MIN       | TYP         | MAX          | UNIT |

|-----------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|--------------|------|

|                             | Facility and conditions and              | VSET[7:0] = 1Bh, SMPS_CFG[5] = 1b                                                                                                                                                                                           |           | 0.4         |              |      |

| $V_{FB,MIN}$                | Feedback voltage at minimum setting      | VSET[7:0] = 1Bh, SMPS_CFG[5] = 1b<br>-30°C ≤ $T_J = T_A ≤ 90$ °C                                                                                                                                                            | 0.35      |             | 0.45         | V    |

|                             | Feedback voltage at                      | $VSET[7:0] = F0h, V_{BATT} = 3.9 V, SMPS\_CFG[5] = 0b$                                                                                                                                                                      |           | 3.6         |              |      |

| $V_{FB,MAX}$                | maximum setting                          | $\begin{split} & \text{VSET[7:0]} = \text{F0h, V}_{\text{BATT}} = 3.9 \text{ V,} \\ & \text{SMPS\_CFG[5]} = 0b \\ & -30^{\circ}\text{C} \leq \text{T}_{\text{J}} = \text{T}_{\text{A}} \leq 90^{\circ}\text{C} \end{split}$ | 3.492     |             | 3.708        | V    |

|                             |                                          | SW = 0 V, VIO = 0 V <sup>(4)</sup>                                                                                                                                                                                          |           | 0.02        |              |      |

| I <sub>SHDN</sub>           | Shutdown supply current                  | SW = 0 V, VIO = 0 V <sup>(4)</sup><br>-30°C $\leq$ T <sub>J</sub> = T <sub>A</sub> $\leq$ 90°C                                                                                                                              |           |             | 4            | μA   |

| I <sub>L-PWR</sub>          | Low-power mode supply current            | VSET[7:0] = 00h                                                                                                                                                                                                             |           | 0.225       |              | μΑ   |

|                             | PFM mode supply current                  | No switching <sup>(5)</sup> , SMPS_CFG[5] = 1b                                                                                                                                                                              |           | 360         |              |      |

| I <sub>Q-PFM</sub>          | into SVDD                                | No switching <sup>(5)</sup> , SMPS_CFG[5] = 1b<br>-30°C $\leq$ T <sub>J</sub> = T <sub>A</sub> $\leq$ 90°C                                                                                                                  |           |             | 425          | μA   |

|                             |                                          | No switching <sup>(5)</sup> , SMPS_CFG[5] = 0b                                                                                                                                                                              |           | 1240        |              |      |

| I <sub>Q PWM</sub>          | PWM mode supply current                  | No switching <sup>(5)</sup> , SMPS_CFG[5] = 0b<br>-30°C $\leq$ T <sub>J</sub> = T <sub>A</sub> $\leq$ 90°C                                                                                                                  |           |             | 1400         | μA   |

|                             | Positive transient peak                  | $VSET[7:0] = 64h^{(6)}$                                                                                                                                                                                                     |           | 1.9         |              |      |

| LIM, PFET Transient         | current limit                            | $VSET[7:0] = 64h^{(6)}$<br>-30°C \le T <sub>J</sub> = T <sub>A</sub> \le 90°C                                                                                                                                               |           |             | 2.1          | Α    |

| l                           | Positive steady-state neak               | VSET[7:0] = 64h <sup>(6)</sup>                                                                                                                                                                                              |           | 1.45        |              | Ī.   |

| ILIM, PFET Steady-<br>State | Positive steady-state peak current limit | $VSET[7:0] = 64h^{(6)}$<br>-30°C \leq T <sub>J</sub> = T <sub>A</sub> \leq 90°C                                                                                                                                             | 1.35      |             | 1.65         | Α    |

|                             | Positive active current assist           | VSET[7:0] = 64h <sup>(6)</sup>                                                                                                                                                                                              |           | 1.7         |              |      |

| I <sub>LIM, P-ACB</sub>     | peak current limit                       | VSET[7:0] = $64h^{(6)}$<br>-30°C $\leq$ T <sub>J</sub> = T <sub>A</sub> $\leq$ 90°C                                                                                                                                         | 1.4       |             | 2            | Α    |

| I <sub>LIM,NFET</sub>       | NFET current limit                       | VSET[7:0] = A7h <sup>(6)</sup>                                                                                                                                                                                              |           | <b>-1.5</b> |              | Α    |

| _                           | Average Internal oscillator              | VSET[7:0] = A7h                                                                                                                                                                                                             |           | 2.7         |              |      |

| fosc                        | frequency                                | VSET[7:0] = A7h<br>$-30^{\circ}$ C ≤ T <sub>J</sub> = T <sub>A</sub> ≤ 90°C                                                                                                                                                 | 2.43      |             | 2.97         | MHz  |

| I <sub>VIO-IN</sub>         | VIO voltage average input current        | Average during a 26-MHz write                                                                                                                                                                                               |           |             | 1.25         | mA   |

| V <sub>IORST</sub>          | RFFE I/O voltage reset voltage           | VIO toggled low                                                                                                                                                                                                             |           |             | 0.45         | V    |

| I <sub>INVIO</sub>          | VIO reset current                        | VIO = 0.45 V                                                                                                                                                                                                                | -1        |             | 1            | μΑ   |

| I <sub>IN</sub>             | SDATA, SCLK input current                | VIO = 1.95 V                                                                                                                                                                                                                | -1        |             | 1            | μΑ   |

| V <sub>IH</sub>             | Input high-level threshold SDATA, SCLK   |                                                                                                                                                                                                                             | 0.4 × VIO |             | 0.7 ×<br>VIO | V    |

| $V_{IL}$                    | Input low-level threshold SDATA, SCLK    |                                                                                                                                                                                                                             | 0.3 × VIO |             | 0.6 ×<br>VIO | V    |

| V <sub>IH-GPO</sub>         | Input high-level threshold GPO1          | $-30$ °C $\leq T_J = T_A \leq 90$ °C                                                                                                                                                                                        | 1.35      |             |              | V    |

| V <sub>IL-GPO</sub>         | Input low-level threshold GPO1           | $-30$ °C $\leq T_J = T_A \leq 90$ °C                                                                                                                                                                                        |           |             | 0.67         | V    |

|                             |                                          |                                                                                                                                                                                                                             |           |             |              |      |

<sup>(1)</sup> All voltages are with respect to the potential at the GND pins.(2) Minimum and Maximum limits are specified by design, test, or statistical analysis.

The parameters in *Electrical Characteristics* are tested under open loop conditions at PVIN = SVDD = PACB = 3.8 V.

<sup>(4)</sup> Shutdown current includes leakage current of PFET.

IQ specified here is when the part is not switching.

Current limit is built-in, fixed, and not adjustable.

### **Electrical Characteristics (continued)**

Unless otherwise noted, all limits apply to the *Typical Application* with  $V_{BATT} = 3.8 \text{ V}$  (= PVIN = SVDD = PACB), VIO = 1.8 V,  $T_{.I} = 25^{\circ}\text{C}.^{(1)(2)(3)}$

|                      | PARAMETER                         | TEST CONDITIONS              | MIN        | TYP MAX       | UNIT |

|----------------------|-----------------------------------|------------------------------|------------|---------------|------|

| V <sub>OH</sub>      | Output high-level threshold SDATA | I <sub>SDATA</sub> = 2 mA    | VIO × 0.8  | VIO +<br>0.01 | ٧    |

| V <sub>OL</sub>      | Output low-level threshold SDATA  | I <sub>SDATA</sub> = -2 mA   |            | VIO ×<br>0.2  | V    |

| V <sub>OH-GPO</sub>  | Output high-level threshold GPO   |                              | VIO – 0.15 | VIO +<br>0.1  | V    |

| V <sub>OL-GPO</sub>  | Output low-level threshold GPO    | - I <sub>OUT</sub> = ±200 μA | -0.4       | 0.3           | V    |

| V <sub>SET-LSB</sub> | Output voltage LSB                | VSET[7:0] = A7h to A8h       |            | 15            | mV   |

### 6.6 System Characteristics

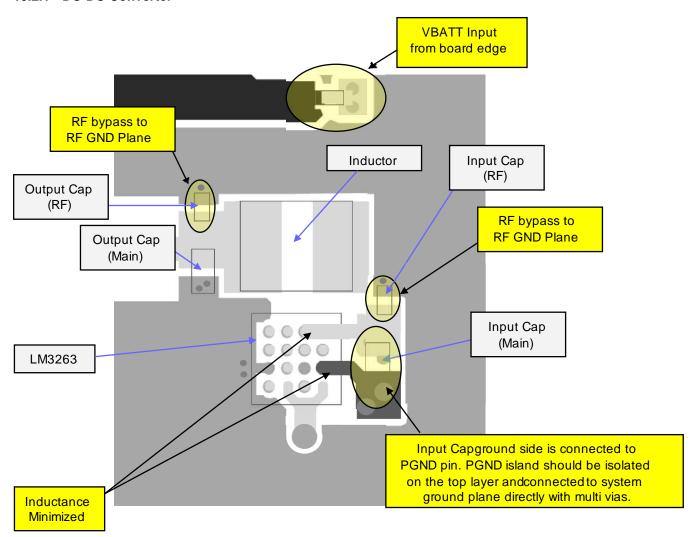

The following spec table entries are specified by design and verifications providing the component values in the *Typical Application* are used (L = 1.5  $\mu$ H, DCR = 120 m $\Omega$ , TOKO DFE201610MT-1R5N, C<sub>IN</sub> = 10  $\mu$ F, 6.3 V, 0402, Samsung CL05A106MP5NUN, C<sub>OUT</sub> = 10  $\mu$ F + 4.7  $\mu$ F + 3 × 1  $\mu$ F; 10 V, 0402, Samsung CL05A106MP5NUN, CL05A475MPNRN; 6.3 V, 0201, TDK, C0603X5R0J105M). *These parameters are not verified by production testing.* Minimum and maximum values are specified over the ambient temperature range T<sub>A</sub> = -30°C to +90°C. Typical values are specified at V<sub>BATT</sub> = 3.8 V (= PVIN = SVDD = PACB), VIO = 1.8 V, SMPS\_CFG = 20h, and T<sub>A</sub> = 25°C, unless otherwise stated.

|                       | PARAMETER                                                                                                   | TEST CONDITIONS                                                                                             | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| T <sub>ON</sub>       | Turnon time (time for output to reach 95% of 3.4-V value from the end of the SCLK pulse)                    | $V_{BATT} = 4.2 \text{ V, VSET[7:0]} = 00 \text{h to E3h, VSET} = 3.4 \text{ V, } I_{OUT} \le 1 \text{ mA}$ |     |     | 50  | μs   |

|                       | Time for $V_{OUT}$ to rise from 0.09 V to 3.4 V (3.07 V, 90% of delta $V_{OUT}$ from the end of SCLK pulse) | $V_{BATT} = 3.8 \text{ V}, R_{LOAD} = 68 \Omega$<br>VSET[7:0] = 06h to E3h<br>SMPS_CFG[5] = 0b/1b           |     |     | 15  |      |

|                       | Time for $V_{OUT}$ to fall from 3.4 V to 0.09 V (0.42 V, 10% of delta $V_{OUT}$ from the end of SCLK pulse) | $V_{BATT} = 3.8 \text{ V}, R_{LOAD} = 68 \Omega$<br>VSET[7:0] = E3h  to  06h<br>$SMPS\_CFG[5] = 0b/1b$      |     |     | 15  |      |

|                       | Time for $V_{OUT}$ to rise from 0.8 V to 3.3 V (3.05V, 90% of delta $V_{OUT}$ from the end of SCLK pulse)   | $V_{BATT} = 3.8 \text{ V}, R_{LOAD} = 20 \Omega$<br>VSET[7:0] =36h to DCh                                   |     | 7.4 | 12  |      |

| _                     | Time for $V_{OUT}$ to fall from 3.3 V to 0.8 V (1.05 V, 10% of delta $V_{OUT}$ from the end of SCLK pulse)  | $V_{BATT} = 3.8 \text{ V}, R_{LOAD} = 20 \Omega$<br>VSET[7:0] = DCh to 36h                                  |     | 6.8 | 12  |      |

| T <sub>RESPONSE</sub> | Time for $V_{OUT}$ to rise from 1.4 V to 3.4 V (3.2 V, 90% of delta $V_{OUT}$ from the end of SCLK pulse)   | $V_{BATT} = 3.8 \text{ V}, R_{LOAD} = 6.8 \Omega$<br>VSET[7:0] = 5Eh to E3h                                 |     |     | 10  | μs   |

|                       | Time for $V_{OUT}$ to fall from 3.4 V to 1.4 V (1.6 V, 10% of delta $V_{OUT}$ from the end of SCLK pulse)   | $V_{BATT} = 3.8 \text{ V}, R_{LOAD} = 6.8 \Omega$<br>VSET[7:0] = E3h to 5Eh                                 |     |     | 10  |      |

|                       | Time for $V_{OUT}$ to rise from 1.8 V to 2.8 V (2.7 V, 90% of delta $V_{OUT}$ from the end of SCLK pulse)   | $V_{BATT}=3.8$ V, $R_{LOAD}=2.2$ $\Omega$ VSET[7:0] = 78h to BBh SMPS_CFG[5] = 0b                           |     |     | 15  |      |

|                       | Time for $V_{OUT}$ to fall from 2.8 V to 1.8 V (1.9 V, 10% of delta $V_{OUT}$ from the end of SCLK pulse)   | $V_{BATT}=3.8$ V, $R_{LOAD}=2.2$ $\Omega$ VSET[7:0] = BBh to 78h SMPS_CFG[5] = 0b                           |     |     | 15  |      |

| T <sub>Bypass</sub>   | Time for VSET to rise from 0.09V to PVIN after BYPASS transition (90%)                                      | $V_{BATT} = 3.6 \text{ V}, I_{OUT} \le 1 \text{ mA},$<br>VSET[7:0] = 06h to FFh                             |     |     | 20  | μs   |

| R <sub>tot-drop</sub> | Total dropout resistance in bypass mode                                                                     | VSET[7:0] = FAh, Max value at $V_{BATT}$ = 3.1 V, Inductor DCR ≤ 151 mΩ                                     |     | 45  | 55  | mΩ   |

### **System Characteristics (continued)**

The following spec table entries are specified by design and verifications providing the component values in the *Typical Application* are used (L = 1.5  $\mu$ H, DCR = 120 m $\Omega$ , TOKO DFE201610MT-1R5N, C<sub>IN</sub> = 10  $\mu$ F, 6.3 V, 0402, Samsung CL05A106MP5NUN, C<sub>OUT</sub> = 10  $\mu$ F + 4.7  $\mu$ F + 3 × 1  $\mu$ F; 10 V, 0402, Samsung CL05A106MP5NUN, CL05A475MPNRN; 6.3 V, 0201, TDK, C0603X5R0J105M). *These parameters are not verified by production testing.* Minimum and maximum values are specified over the ambient temperature range T<sub>A</sub> = -30°C to +90°C. Typical values are specified at V<sub>BATT</sub> = 3.8 V (= PVIN = SVDD = PACB), VIO = 1.8 V, SMPS\_CFG = 20h, and T<sub>A</sub> = 25°C, unless otherwise stated.

|                              | PARAMETER                                           | TEST CONDITIONS                                                                                                                                                                                      | MIN  | TYP | MAX | UNIT      |

|------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-----------|

| l <sub>out</sub>             | Maximum load current in PWM mode                    | Switcher + ACB                                                                                                                                                                                       | 2.5  |     |     |           |

| I <sub>OUT, PU</sub>         | Maximum output transient pullup current limit       | Switcher + ACB <sup>(1)</sup>                                                                                                                                                                        | 3    |     |     | Α         |

| I <sub>OUT, PD,</sub><br>PWM | PWM maximum output transient pulldown current limit | Switcher + ACB <sup>(1)</sup>                                                                                                                                                                        |      |     | -3  |           |

| I <sub>OUT,</sub><br>MAX_PFM | Maximum output load current in PFM mode             | V <sub>BATT</sub> = 3.8 V, VSET = 3.2 V                                                                                                                                                              | 60   |     |     | mA        |

|                              | Linearity in control range of VSET =                | $V_{BATT} = 3.9 V^{(2)}$ , Monotonic in nature;                                                                                                                                                      | -3%  |     | 3%  |           |

| Linearity                    | 0.4 V to 3.6 V                                      | VSET[7:0] = 1Bh to F0h,<br>SMPS_CFG[5] = 0b                                                                                                                                                          | -50  |     | 50  | mV        |

| η                            |                                                     | $V_{BATT} = 3.8 \text{ V, VSET} = 0.5 \text{ V,}$<br>$I_{OUT} = 5\text{mA}$                                                                                                                          | 52%  | 56% |     |           |

|                              |                                                     | $V_{BATT}$ = 3.8 V, VSET= 1.8 V, $I_{OUT}$ = 10 mA                                                                                                                                                   | 78%  | 82% |     |           |

|                              |                                                     | $V_{BATT} = 3.8 \text{ V, VSET} = 1.6 \text{ V,} $<br>$I_{OUT} = 130 \text{ mA}$                                                                                                                     | 83%  | 89% |     |           |

|                              | Efficiency                                          | V <sub>BATT</sub> = 3.8 V, VSET = 2.5 V,<br>I <sub>OUT</sub> = 250 mA                                                                                                                                | 90%  | 94% |     |           |

|                              |                                                     | V <sub>BATT</sub> = 3.8 V, VSET = 3.4 V,<br>I <sub>OUT</sub> = 550 mA                                                                                                                                | 93%  | 95% |     |           |

|                              |                                                     | V <sub>BATT</sub> = 3.8 V, VSET = 1 V,<br>I <sub>OUT</sub> = 400 mA, SMPS_CFG[5] = 0b                                                                                                                | 81%  | 85% |     |           |

|                              |                                                     | V <sub>BATT</sub> = 3.8 V, VSET = 3.5 V,<br>I <sub>OUT</sub> = 1900 mA, SMPS_CFG[5] = 0b                                                                                                             | 89%  | 92% |     |           |

|                              | 2.7-MHz PWM normal operation ripple                 | $V_{\rm BATT} = 3.2 \ V \ {\rm to} \ 4.3 \ V, \ {\rm VSET} = 0.4 \ V \ {\rm to} \ 3.6 \ V, \ {\rm R}_{\rm LOAD} = 1.9 \ \Omega^{(3)} \ {\rm SMPS\_CFG[5]} = 0 {\rm b}$                               |      | 1   | 3   |           |

|                              | Ripple voltage at pulse skipping condition          | $V_{BATT}=3.2$ V, VSET = 3 V, R <sub>LOAD</sub> = 1.9 $\Omega$ <sup>(3)</sup> SMPS_CFG[5]= 0b                                                                                                        |      |     | 8   |           |

| V <sub>RIPPLE</sub>          |                                                     | V <sub>BATT</sub> = 3.2 V, VSET = 3 V,<br>I <sub>OUT</sub> = 40 mA                                                                                                                                   |      |     | 50  | $mV_{pp}$ |

|                              | PFM ripple voltage                                  | V <sub>BATT</sub> = 3.2 V, VSET = 2.5 V,<br>I <sub>OUT</sub> = 10 mA                                                                                                                                 |      |     | 50  |           |

|                              |                                                     | $V_{BATT}$ = 3.2 V, VSET< 0.5 V, $I_{OUT}$ = 5 mA                                                                                                                                                    |      |     | 50  |           |

| Line_tr                      | Line transient response                             | $\begin{aligned} & V_{BATT} = 3.6 \text{ V to } 4.2 \text{ V}, \\ & T_R = T_F = 10  \mu\text{s}, \\ & V\text{SET} = 3.2 \text{ V}, \\ & I_{OUT} = 500 \text{ mA} \end{aligned}$                      |      | 50  |     | $mV_{pk}$ |

| Load_tr                      | Load transient response                             | $ \begin{array}{l} \text{VSET} = 3 \text{ V}, \\ \text{T}_{R} = \text{T}_{F} = 10  \mu\text{s}, \\ \text{I}_{OUT} = 0 \text{ A to } 1.2 \text{ A}, \\ \text{SMPS\_CFG[5]} = 0 \text{b} \end{array} $ |      | 60  |     | $mV_{pk}$ |

| Max Duty<br>Cycle            | Maximum duty cycle                                  |                                                                                                                                                                                                      | 100% |     |     |           |

- (1) Current limit is built-in, fixed, and not adjustable.

- (2) Linearity limits are ±3% or ±50 mV whichever is larger.

- (3) Ripple voltage must be measured at C<sub>OUT</sub> electrode on a well-designed PC board using suggested inductor and capacitors.

Copyright © 2013–2016, Texas Instruments Incorporated

### **System Characteristics (continued)**

The following spec table entries are specified by design and verifications providing the component values in the *Typical Application* are used (L = 1.5  $\mu$ H, DCR = 120 m $\Omega$ , TOKO DFE201610MT-1R5N, C<sub>IN</sub> = 10  $\mu$ F, 6.3 V, 0402, Samsung CL05A106MP5NUN, C<sub>OUT</sub> = 10  $\mu$ F + 4.7  $\mu$ F + 3 × 1  $\mu$ F; 10 V, 0402, Samsung CL05A106MP5NUN, CL05A475MPNRN; 6.3 V, 0201, TDK, C0603X5R0J105M). *These parameters are not verified by production testing.* Minimum and maximum values are specified over the ambient temperature range T<sub>A</sub> = -30°C to +90°C. Typical values are specified at V<sub>BATT</sub> = 3.8 V (= PVIN = SVDD = PACB), VIO = 1.8 V, SMPS\_CFG = 20h, and T<sub>A</sub> = 25°C, unless otherwise stated.

|                      | PARAMETER                                                  | TEST CONDITIONS                                                              | MIN | TYP | MAX | UNIT |

|----------------------|------------------------------------------------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

| PFM_Freq             | Minimum PFM frequency                                      | $V_{BATT} = 3.2 \text{ V, VSET} = 1 \text{ V,}$<br>$I_{OUT} = 10 \text{ mA}$ | 100 | 160 |     | KHz  |

|                      | Millimum Privi frequency                                   | $V_{BATT}$ = 3.2 V, VSET = 0.5 V,<br>$I_{OUT}$ = 5 mA                        | 34  | 55  |     | KΠZ  |

| N <sub>SET</sub>     | VSET DAC number of bits                                    | Monotonic                                                                    | 8   |     |     | Bits |

| T <sub>SETUP</sub>   | Power-up time (time for RFFE bus active after VIO applied) | VIO = Low to 1.65 V                                                          |     |     | 50  | ns   |

| T <sub>VIO-RST</sub> | VIO supply reset timing                                    | VIO = 0.45 V                                                                 | 10  |     |     | μs   |

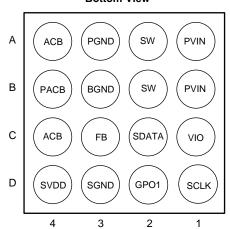

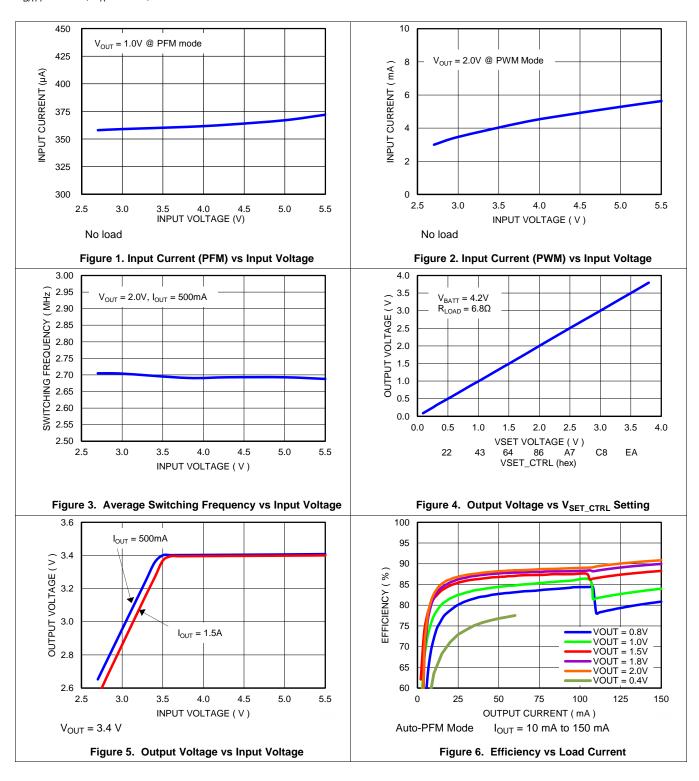

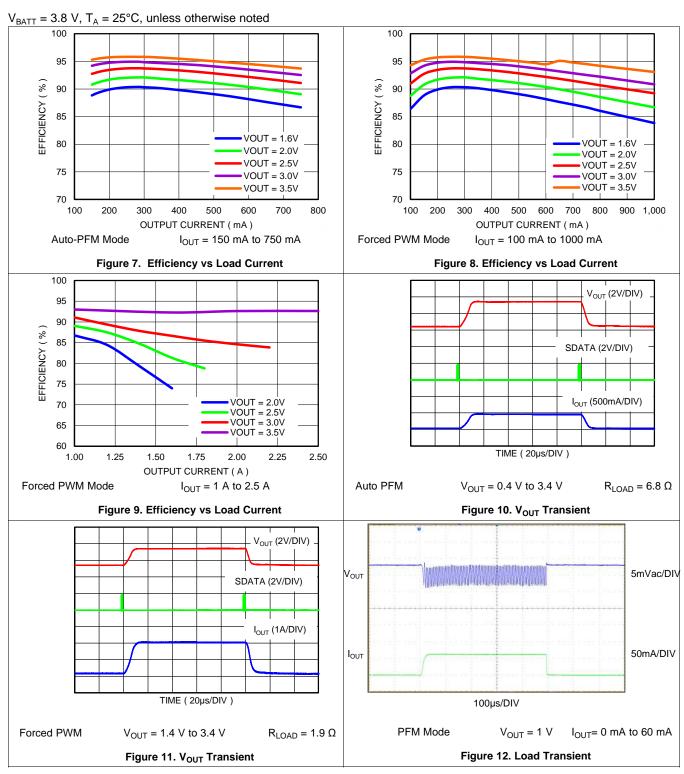

### 6.7 Typical Characteristics

$V_{BATT} = 3.8 \text{ V}, T_A = 25^{\circ}\text{C}, \text{ unless otherwise noted}$

Copyright © 2013–2016, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

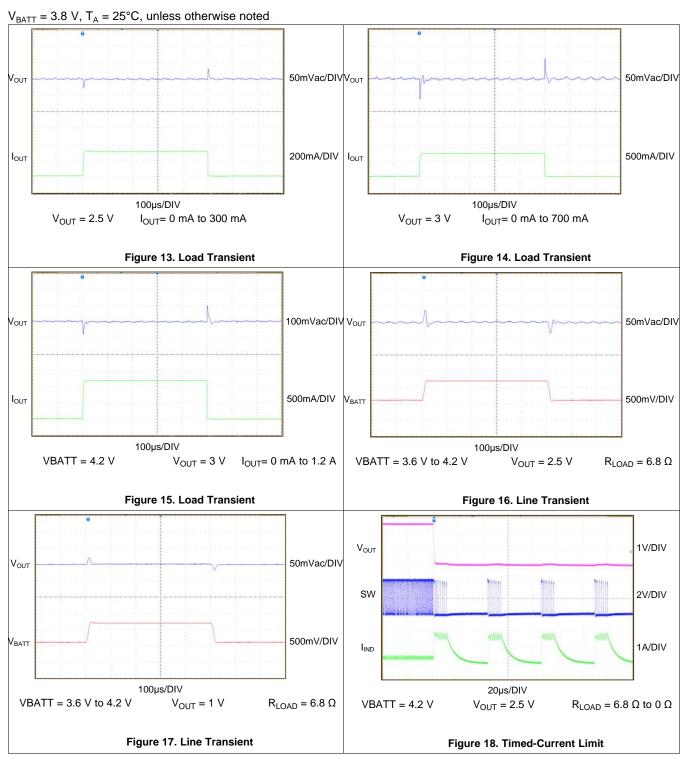

### **Typical Characteristics (continued)**

# Typical Characteristics (continued)

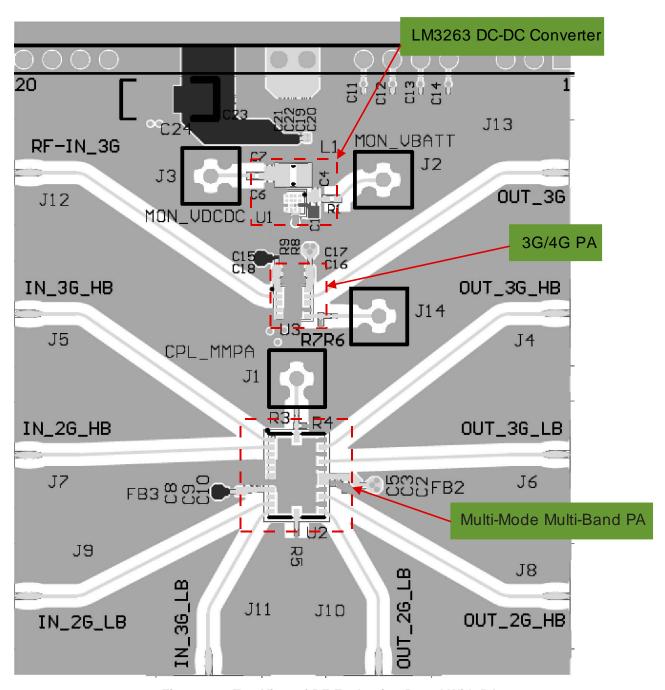

### 7 Detailed Description

#### 7.1 Overview

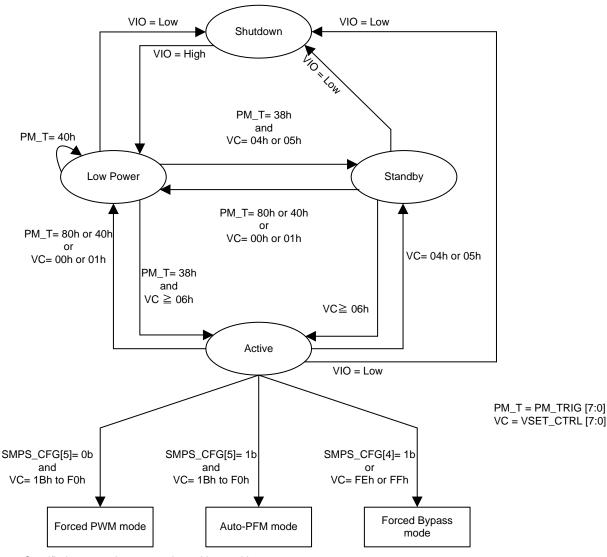

The LM3263 is a high-efficiency step-down DC-DC converter optimized to power the RF power amplifier (PA) in cell phones, portable communication devices, or battery-powered RF devices with a single litium-lon battery. It operates in modulated-frequency pulsed width modulation (PWM) mode for 2G transmissions (with MODE = Forced PWM (PWM only), register 01h SMPS\_CFG [5] set to 0b), automatic mode transition between pulse frequency modulation (PFM) and PWM for 3G/4G RF PA operation (with MODE = Auto-PFM (PFM/PWM), SMPS\_CFG bit 5 set to 1b), or forced-bypass mode (with SMPS\_CFG [4] set to 1b or REGISTER\_0 [6:0] set to 7Fh or register 03h VSET\_CTRL [7:0] set to FEh-FFh). Power states are also in provided shutdown, low power, standby, and active modes. The DC-DC converter operates at active mode. Please see Figure 21 and *Register Map*.

PWM mode provides high efficiency and very low output-voltage ripple. In PWM-mode operation, the modulated switching frequency helps to reduce RF transmit noise. In PFM mode, the converter operates with reduced switching frequencies and lower supply current to maintain high efficiencies. The forced-bypass mode allows the user to drive the output directly from the input supply through a bypass FET. The shutdown mode turns the LM3263 off and reduces current consumption to 0.02 µA (typical).

In the PWM and PFM modes of operation, the output voltage of the LM3263 can be dynamically programmed from 0.4 V to 3.6 V (typical) by setting the VSET register. Current overload protection and thermal overload protection are also provided.

The LM3263 was engineered with Active Current assist and analog Bypass (ACB). This unique feature allows the converter to support maximum load currents of 2.5 A (minimum) while keeping a small footprint inductor and meeting all of the transient behaviors required for operation of a multi-mode RF PA. The ACB circuit provides an additional current path when the load current exceeds 1.45 A (typical) or as the switcher approaches dropout. Similarly, the ACB circuit allows the converter to respond with faster VSET output voltage transition times by providing extra output current on rising and falling output edges. The ACB circuit also performs the function of analog bypass. Depending upon the input voltage, output voltage, and load current, the ACB circuit automatically and seamlessly transitions the converter into analog bypass, while maintaining output voltage regulation and low output voltage ripple. Full bypass (100% duty cycle operation) occurs if the total dropout resistance in bypass mode ( $R_{tot drop} = 45 \text{ m}\Omega$ ) is insufficient to regulate the output voltage.

The device 16-pin DSBGA package is the best solution for space-constrained applications such as cell phones and other hand-held devices. The high switching frequency, 2.7 MHz (typical) in PWM mode, reduces the size of input capacitors, output capacitor, and of the inductor. Use of a DSBGA package is best suited for opaque case applications and requires special design considerations for implementation (see *Layout Considerations*).

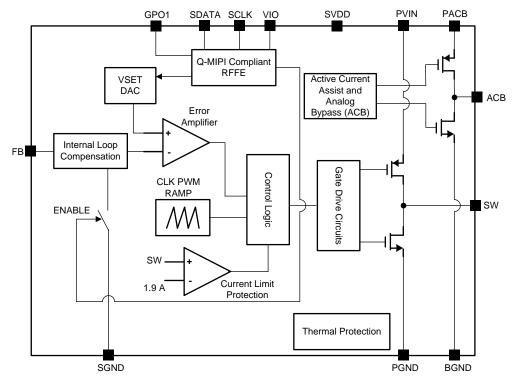

#### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

### 7.3 Feature Description

### 7.3.1 PWM Operation

The LM3263 operates in PWM mode when forced-PWM mode operation is selected (SMPS\_CFG [5] set to 0b). The switching frequency is modulated, and the switcher regulates the output voltage by changing the energy per cycle to support the load required. During the first portion of each switching cycle, the control block in the LM3263 turns on the internal PFET switch. This allows current to flow from the input through the inductor and to the output filter capacitor and load. The inductor limits the current to a ramp with a slope of (V<sub>BATT</sub> – VSET)/L, by storing energy in its magnetic field.

During the second portion of each cycle, the control block turns the PFET switch off, blocking current flow from the input, and then turns the NFET synchronous rectifier on. The inductor draws current from ground through the NFET and to the output filter capacitor and load, which ramps the inductor current down with a slope of –VSET/L. The output filter capacitor stores charge when the inductor current is greater than the load current and releases it when the inductor current is less than the load current, smoothing the voltage across the load.

At the next rising edge of the clock, the cycle repeats. An increase of load pulls the output voltage down, increasing the error signal. As the error signal increases, the peak inductor current becomes higher therefore increasing the average inductor current. The output voltage is therefore regulated by modulating the PFET switch on time to control the average current sent to the load. The circuit generates a duty-cycle modulated rectangular signal that is averaged using a low pass filter formed by the inductor and output capacitor. The output voltage is equal to the average of the duty-cycle modulated rectangular signal.

### **Feature Description (continued)**

#### 7.3.2 PFM Operation

When auto-PFM mode operation is selected (SMPS\_CFG [5] set to 1b), the LM3263 automatically transitions from PWM operation into PFM operation if the average inductor current is less than 60 mA (minimum) and the difference between  $V_{BATT} - VSET \ge 0.6 \text{ V}$ . The switcher regulates the fixed output voltage by transferring a fixed amount of energy during each cycle and modulating the frequency to control the total power delivered to the output. The converter switches only as needed to support the demand of the load current, therefore maximizing efficiency. If there is an increase in load current during PFM mode to more than 120 mA (typical), the part automatically transitions into PWM mode. A 20 mA (typical) hysteresis window exists between PFM and PWM transitions. After a transient event, the part temporarily operates in PWM mode to quickly charge or discharge the output. This is true for start-up conditions or if the mode operation is changed from forced-PWM to auto-PFM mode (SMPS\_CFG [5] toggled from 0b to 1b). Once the output reaches its target output voltage, and the load is less than 60 mA (minimum), then the device seamlessly transitions into PFM mode (assuming the device is not in forced-bypass condition).

#### 7.3.3 Active Current Assist and Analog Bypass (ACB)

The 3GPP time mask requirement for 2G requires high current to be sourced by the LM3263. These high currents are required for a small time during transients or under a heavy load. Overrating the switching inductor for these higher currents increases the solution size and is not an optimum solution. Thus, to allow an optimal inductor size for such a load, an alternate current path is provided from the input supply through the ACB pin. Once the switcher current limit I<sub>LIM,PFET,SteadyState</sub> is reached, the ACB circuit starts providing the additional current required to support the load. The ACB circuit also minimizes the dropout voltage by having the analog bypass FET in parallel with VSET. The LM3263 can provide up to 2.5 A (minimum) of current in bypass mode.

### 7.3.4 Bypass Operation

The bypass circuit provides an analog bypass function with very low dropout resistance ( $R_{tot\_drop} = 45 \text{ m}\Omega$  typical). When SMPS\_CFG [4] is set to 0b, the part is in automatic bypass mode which automatically determines the amount of bypass needed to maintain voltage regulation. When the input supply voltage to the LM3263 is lowered to a level where the commanded duty cycle is higher than what the converter is capable of providing, the part goes into pulse-skipping mode. The switching frequency is reduced to maintain a low and well behaved output voltage ripple. The analog bypass circuit allows the converter to stay in regulation until full bypass is reached (100% duty cycle operation). The converter comes out of full bypass and back into analog bypass regulation mode with a similar reverse process.

To operate the device at the Forced-Bypass mode, set REGISTER\_0 to 7Fh or VSET\_CTRL to FEh-FFh.

### 7.3.5 Dynamic Adjustment of Output Voltage

The LM3263 can be dynamically programmed to an output voltage from 0.4 V to 3.6 V with 30 mV or 15 mV steps. REGISTER\_0 [6:0] is set to 0Dh to 78h with 30-mV output voltage steps, and VSET\_CTRL [7:0] is set to 1Bh to F0h with 15-mV steps. Although the output voltage can be programmed lower than 0.4 V and higher than 3.6 V by setting the registers, the device might suffer from larger output ripple voltage, higher current limit operation, and decreased linearity.

### 7.3.6 DC-DC Operating Mode Selection

Programming SMPS\_CFG [5] changes the state of the converter to one of the two allowed modes of operation. SMPS\_CFG [5] default is 0b, and the device operates in forced-PWM mode (PWM only). Setting the register bit to 1b sets the device for automatic transition between PFM/PWM mode operation. In this mode, the converter operates in PFM mode to maintain the output voltage regulation at very light loads and transitions into PWM mode at loads exceeding 120 mA (typical). Setting the register bit to 0b sets the device for PWM mode operation. The switching operation is in PWM mode only, and the switching frequency is also 2.7 MHz (typical). The device operates in forced-bypass mode when SMPS\_CFG [4] is set to 1b.

For typical operation mode is set to auto-PFM and auto-bypass modes by setting SMPS CFG = 20h.

Table 1 shows the LM3263 parameters for the given modes.

### **Feature Description (continued)**

Table 1. Parameters Under Different Modes Of Operation

| SMPS_CFG [5] MODE | SMPS_CFG [4] BYPS | I <sub>OUT</sub> CONDITIONS       | OPERATION MODE |

|-------------------|-------------------|-----------------------------------|----------------|

| 0                 | 0                 | X                                 | Forced PWM     |

| X <sup>(1)</sup>  | 1                 | X                                 | Forced bypass  |

| 1                 | 0                 | I <sub>OUT</sub> ≤ 60 mA          | PFM            |

| 1                 | 0                 | 60 mA < I <sub>OUT</sub> ≤ 120 mA | PFM or PWM     |

| 1                 | 0                 | I <sub>OUT</sub> > 120 mA         | PWM            |

<sup>(1)</sup> don't care

### 7.3.7 Internal Synchronous Rectification

The LM3263 uses an internal NFET as a synchronous rectifier to reduce rectifier forward voltage drop, thus increasing efficiency. The reduced forward voltage drop in the internal NFET synchronous rectifier significantly improves efficiency for low output voltage operation. The NFET is designed to conduct through its intrinsic body diode during the transient intervals, eliminating the need of an external diode.

#### 7.3.8 Current Limit

The LM3263 current limit feature protects the converter during current overload conditions. Both SW and ACB pins have positive and negative current limits. The positive and negative current limits bound the SW and ACB currents in both directions. The SW pin has two positive current limits. The I<sub>LIM,PFET,SteadyState</sub> current limit triggers the ACB circuit. Once the peak inductor current exceeds I<sub>LIM,PFET,SteadyState</sub>, the ACB circuit starts assisting the switcher and provides just enough current to keep the inductor current from exceeding I<sub>LIM,PFET,SteadyState</sub> allowing the switcher to operate at maximum efficiency. Transiently a second current limit (I<sub>LIM,PFET,Transient</sub>) of 1.9 A (typical, 2.1 A maximum) limits the maximum peak inductor current possible. The output voltage falls out of regulation only after both SW and ACB output pin currents reach their respective current limits of I<sub>LIM,PFET,Transient</sub> and I<sub>LIM,P-ACB</sub>.

#### 7.3.9 Timed Current Limit

If the load or output short-circuit pulls the output voltage to 0.3 V or lower, and the peak inductor current sustains  $I_{LIM,PFET,SteadyState}$  more than 10 µs, the LM3263 switches to a timed current limit mode. In this mode, the internal PFET switch is turned off. After approximately 30 µs, the device returns to the normal operation.

#### 7.3.10 Thermal Overload Protection

The LM3263 device has a thermal overload protection that protects itself from short-term misuse and overload conditions. If the junction temperature exceeds 150°C, the LM3263 shuts down. Normal operation resumes after the temperature drops below 125°C. Prolonged operation in thermal overload condition may damage the device and is therefore not recommended.

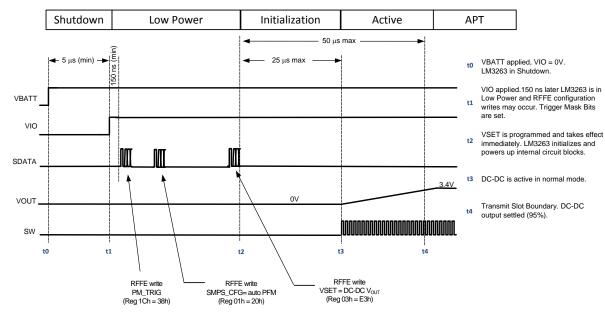

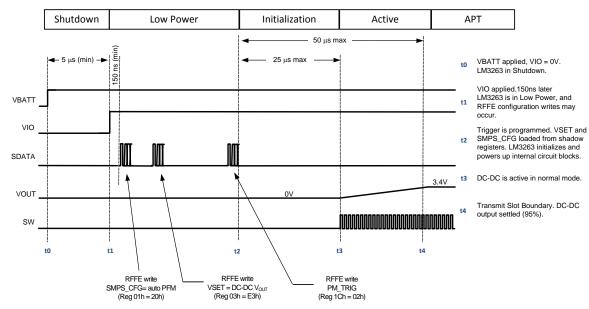

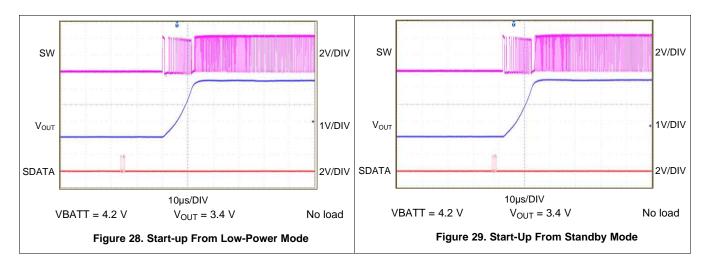

#### 7.3.11 Start-Up

The waveform in Figure 19 shows the start-up sequence and sample conditions. First, VBATT (=PVIN=SVDD=PACB) must take on a value from 2.7 V to 5.5 V. After VBATT is ensured to be beyond 2.7 V, VIO can be set 1.8 V. Next, setting PM\_TRIG [7:6] to 38h enables active mode. Finally, VSET can be programmed to a value that corresponds to the desired output voltage. The LM3263 output voltage then goes to the programmed VSET value. To optimize the start-up time and behavior of the output voltage, the LM3263 starts up in PWM mode even when the operating mode selected is auto-PFM mode (SMPS\_CFG [5] set to 1b) if the output load current is  $\leq$  60 mA (minimum), the LM3263 then seamlessly transitions into PFM mode.

Figure 19. Non-Triggered Start-Up Sequence

Figure 20. Triggered Start-Up Sequence

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

#### 7.4 Device Functional Modes

#### 7.4.1 Shutdown Mode

Shutdown mode is entered whenever the voltage on the VIO pin is 0 V. The communications and the controls are not powered. In this mode, the current consumption is 0.02 µA (typical).

#### 7.4.2 Low-Power Mode

Low-power mode is the initial default state when VIO is applied. In this mode, the DC-DC is disabled, and its SW is tri-state. The current consumption is minimized 0.225  $\mu$ A (typical). This mode can be entered by programming any one of three registers below:

- Register 00h REGISTER\_0 [6:0] to 00h;

- Register 03h VSET\_CTRL[7:0] to 00h or 01h;

- Register 1Ch PM\_TRIG [7:6] to 10b.

### 7.4.3 Standby Mode

In standby mode, switching is stopped, and the output power FETs are placed are tri-state. The standby mode can be entered by setting PM\_TRIG [7:6] and REGISTER\_0 or VSET\_CTRL registers.

- Register 00h REGISTER\_0 [6:0] to 02h;

- Register 03h VSET\_CTRL [7:0] to 04h or 05h;

- Register 1Ch PM\_TRIG [7:6] to 00b.

#### 7.4.4 Active Mode

The active mode is a DC-DC converter operating mode that allows the device to function, process RFFE commands, and respond to RFFE commands. This mode can be entered by setting register 1Ch PM\_TRIG [7:6] to 00b. Once the device is the active Mode, the DC-DC converter operating mode and the output voltage can be programmed by using REGISTER\_0 [6:0] and VSET\_CTRL[7:0] registers.

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: *LM3263*

### **Device Functional Modes (continued)**

#### 7.4.5 User States

Specified output voltage range is 0.4 V to 3.6 V.

Writing to and reading back from REGISTER\_0 and VSET\_CTRL access the same internal VSET register. Writing to VSET\_CTRL programs the full 8 bits VSET value. Writing to REGISTER\_0 programs 7 MSB of VSET with LSB set to zero. When REGISTER\_0 is written, the internal VSET register LSB bit[0] always takes a value of 0 and subsequent read of VSET\_CTRL bit[0] is read back as 0.

Figure 21. LM3263 User State Diagram

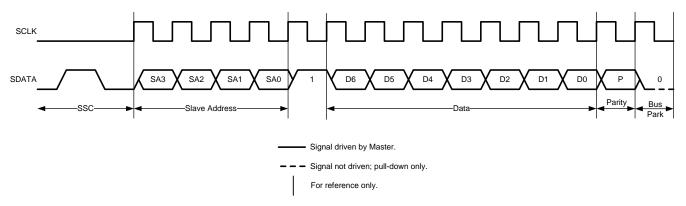

### 7.5 Programming

#### 7.5.1 RFFE Interface

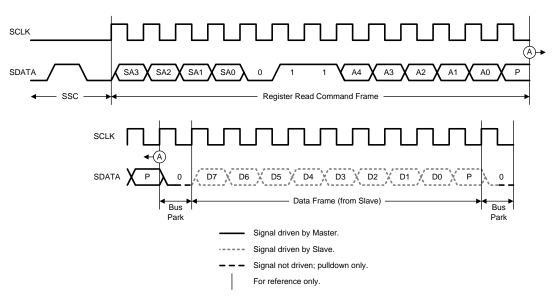

The digital control serial bus interface provides MIPI RF front-end control Interface compatible access to the programmable functions and registers on the device. The LM3263 uses a three-pin digital interface: two for bidirectional communications between the IC's connected to the bus, along with an interface voltage reference VIO that also acts as asynchronous enable and reset. When VIO voltage supply is applied to the bus, it enables the Slave interface and resets the user-defined Slave registers to the default settings. The LM3263 can be set to shutdown mode via the asynchronous VIO signal or low-power mode by setting the appropriate register via the serial bus interface. The two communication lines are serial data (SDATA), and clock (SCLK). SCLK and SDATA must be held low until VIO is present. The LM3263 connects as slave on a single-master serial bus interface.

The SDATA signal is bidirectional, driven by the Master or a Slave. Data is written on the rising edge (transition from logical level zero to logical level one) of the SCLK signal by both Master and Slaves. Master and Slave both read the data on the falling edge (transition from logical level one to logical level zero) of the SCLK signal. A logic-low level applied to VIO signal powers off the digital interface.

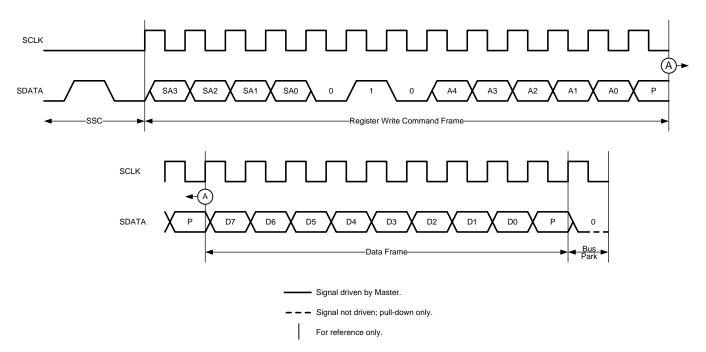

### 7.5.2 Supported Command Sequences

Figure 22. Register 0 Write

Figure 23. Register Write

### **Programming (continued)**

Figure 24. Register Read

#### 7.5.3 Device Enumeration

The interface component recognizes broadcast Slave Address (SID) of 0000b and is configured, via internal interface signals, with a unique SID address (USID) and a group SID address (GSID). The USID is set to 0100b and GSID set to 0000b. The register-set component typically sets the USID to a fixed value; however, it is also possible to select a second pre-set USID if a second LM3263 device is needed on the board. This second User ID can be set by forcing a voltage > 1.36 V at the GPO1 pin for USID = 0101b. Refer to *GPO1* for detailed usage and programmability of the USID. The USID can also be re-programmed via the standard protocol for programming the RFFE as defined in the RFFE spec. The USID must not be programmed to the reserved broadcast slave id of 0000b. A value of 0000b is ignored by the device.

#### 7.5.4 GPO1

GPO1 has two functions. The first function is an input to select the default USID, and the second function is to be a general purpose output.

The state of the GPO1 pin at start-up determines the default USID. If the GPO1 pin is low or left floating at start-up, the USID is 0100b. If the GPO1 pin is high at start-up, the USID is 0101b. One method to set the GPO1 pin high is to place a pullup resistor (39  $K\Omega$ ) on the GPO1 pin.

When the GPO1 pin is used as the general purpose output, GPO\_CTRL [6] must be set to 1b. Once it has been enabled as the general purpose output, GPO\_CTRL [7] determines the state driven to the GPO1 pin. The pullup resistor must be placed either as an external pullup on the board or through an internal pullup on the general purpose input which is tied to the GPO1 pin.

The GPO1 pin can be left floating if unused.

Submit Documentation Feedback

#### 7.5.5 Trigger Registers

Trigger registers are indicated in the RFFE register map by the *Trigger* column. All trigger registers are tied to each of the TRIG\_0-2 register bits. When a trigger register is written directly across the RFFE interface, the new value is not loaded into the register until one of the TRIG0-2 register bits is written with a 1 and the associated TRIG\_MSK\_x bit for that TRIG\_x is not set. (Triggers are ignored when their associated masking bit is set.) When all 3 TRIG\_MSK\_0-2 bits are set (all triggers are masked) the trigger feature is disabled, and any trigger registers are loaded directly at the time of the write operation to that register rather than waiting for a trigger event to update.

# **Programming (continued)**

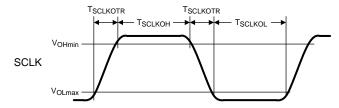

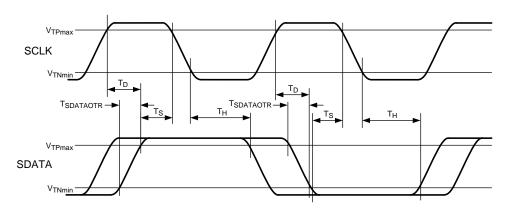

# 7.5.6 Control Interface Timing Parameters

Figure 25. Clock Timing

Figure 26. Setup and Hold Timing

|                        | PARAMETER                                        | MIN   | TYP MAX | UNIT |

|------------------------|--------------------------------------------------|-------|---------|------|

| T <sub>CLK</sub>       | Clock time period                                | 38.5  |         | ns   |

| T <sub>SCLKOH</sub>    | Clock high time                                  | 11.25 |         | ns   |

| T <sub>SCLKOL</sub>    | Clock low time                                   | 11.25 |         | ns   |

| T <sub>S</sub>         | Data setup time                                  | 1     |         | ns   |

| T <sub>H</sub>         | Data hold time                                   | 5     |         | ns   |

| T <sub>D-Forward</sub> | Time for data output valid from SCLK rising edge |       | 10.2    | 5 ns |

| T <sub>D-Reverse</sub> | Time for data output valid from SCLK rising edge |       | 2       | 2 ns |

| T <sub>SDATAOTR</sub>  | SDATA output transition (rise/fall) time         | 2.1   | 6.      | 5 ns |

Copyright © 2013–2016, Texas Instruments Incorporated

# 7.6 Register Map

| Addr |      |                |         | ter Conten                                                  | ts        |                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|------|------|----------------|---------|-------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 00h  |      |                |         | REC                                                         | SISTER _0 |                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|      | Bits | Function       | Default | Trigger*                                                    | R/W       | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|      | 7    | RSVD           | 0       | N/A                                                         | N/A       | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|      | 6:0  | VSET[7:1]      | 00h     | Yes                                                         | R/W       | Register 00h interacts with Register 03h. DC-DC converter mode and output voltage control bits 00h: Low-power mode 01h: Reserved 02h: Standby mode 03h to 7Eh: active mode, setting output voltage is enabled. Output voltage can be set 0.4 V to 3.6 V by 0Dh to 78h with 30-mV steps 7Fh: Forced-bypass mode VSET[7:1] (dec) = Desired V <sub>OUT</sub> / 0.03 (round up decimals), then converts a decimal number to hexadecimal. |  |  |

| 01h  |      |                |         |                                                             | IPS_CFG   | Т                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|      | Bits | Function       | Default | Trigger*                                                    | R/W       | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|      | 7:6  | RSVD           | 0       | N/A                                                         | N/A       | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|      | 5    | MODE           | 0       | Yes                                                         | R/W       | Switching mode select bit<br>0: Forced-PWM mode (PWM only)<br>1: Auto-PFM mode (PFM/PWM)                                                                                                                                                                                                                                                                                                                                             |  |  |

|      | 4    | BYPS           | 0       | Forced bypass bit 0: Auto-bypass mode 1: Forced-bypass mode |           |                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|      | 3:0  | RSVD           | 0h      | N/A                                                         | N/A       | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 02h  |      |                |         | GP                                                          | O_CTRL    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|      | Bits | Function       | Default | Trigger*                                                    | R/W       | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|      | 7    | GPO1_OUT       | 0       | Yes                                                         | R/W       | GPO1 output control 0: Low state 1: High state                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|      | 6    | GPO1_MODE      | 0       | Yes                                                         | R/W       | GPO1 Mode Selection 0 : General Purpose Output disabled 1 : General Purpose output driven by GPO1_OUT                                                                                                                                                                                                                                                                                                                                |  |  |

|      | 5:0  | RSVD           | 00h     | N/A                                                         | N/A       | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 03h  |      |                |         | VS                                                          | ET_CTRL   |                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|      | Bits | Function       | Default | Trigger*                                                    | R/W       | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|      | 7:0  | VSET[7:0]      | 00h     | Yes                                                         | R/W       | DC-DC converter mode and output voltage fine control bits  00h-01h: Low-power mode  02h-03h: Reserved  04h-05h: Standby mode  06h to FDh: Active mode, setting output voltage is enabled. Output voltage can be set 0.4 V to 3.6 V by 1Bh to F0h with 15-mV steps  FEh-FFh: Forced bypass mode  VSET[7:0] (dec) = Desired V <sub>OUT</sub> / 0.015 (round up decimals), then converts a decimal number to hexadecimal.               |  |  |

| 1Ah  |      |                |         | RFFI                                                        | E_STATUS  | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|      | Bits | Function       | Default | Trigger*                                                    | R/W       | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|      | 7    | SWRESET        | 0       | No                                                          |           | Software Reset. A write to 1 causes all registers except for USID to be reset. Always reads back 0.                                                                                                                                                                                                                                                                                                                                  |  |  |

|      | 6    | CMD_FRAME_PERR | 0       | No                                                          |           | Set if parity error detected in command frame. Cleared on read. Write has no effect on this bit.                                                                                                                                                                                                                                                                                                                                     |  |  |

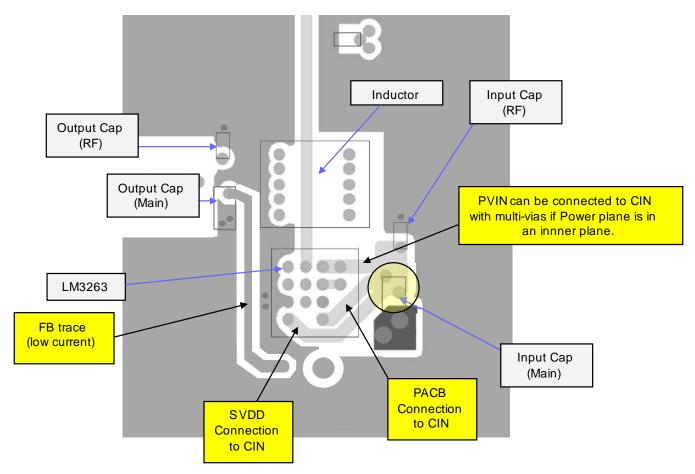

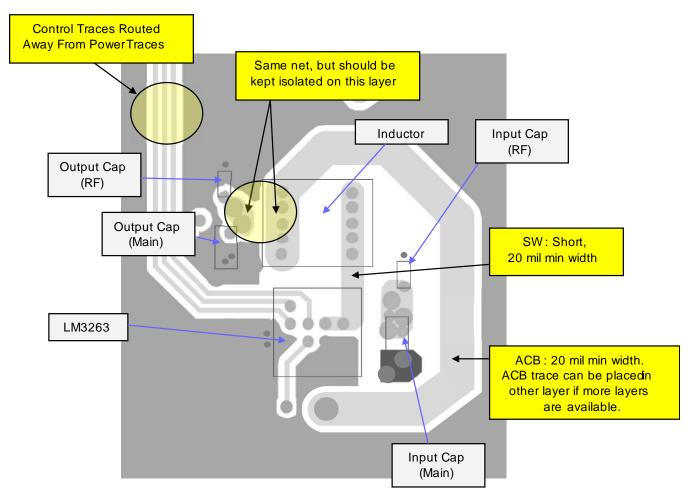

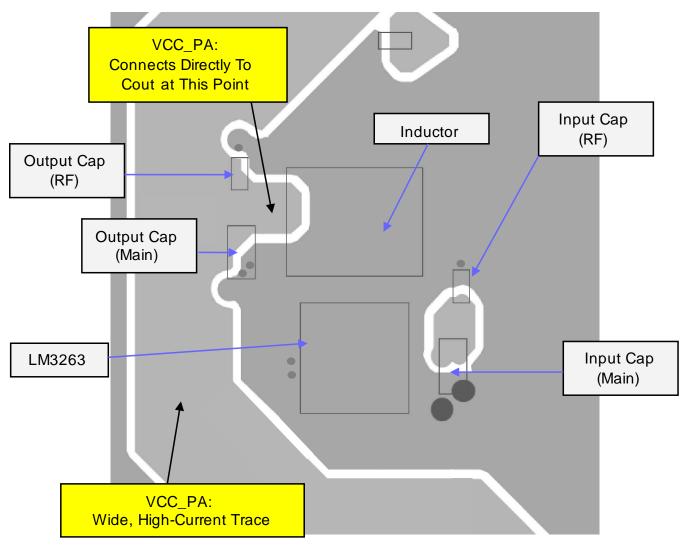

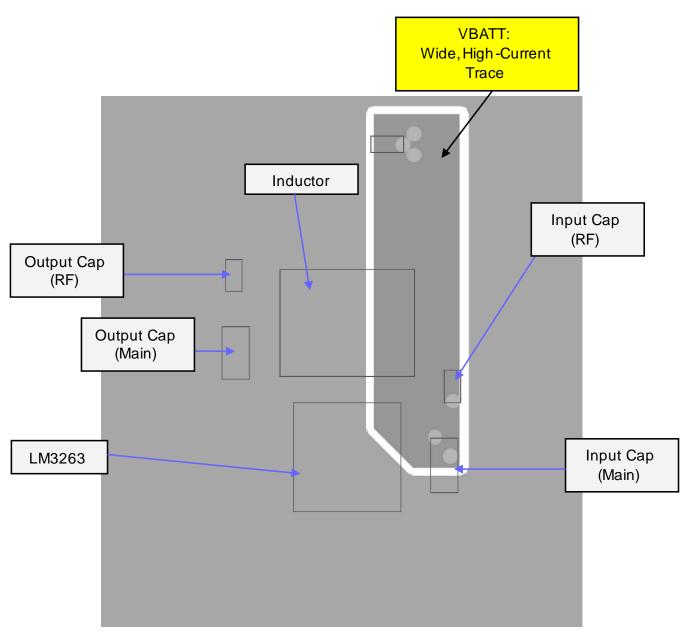

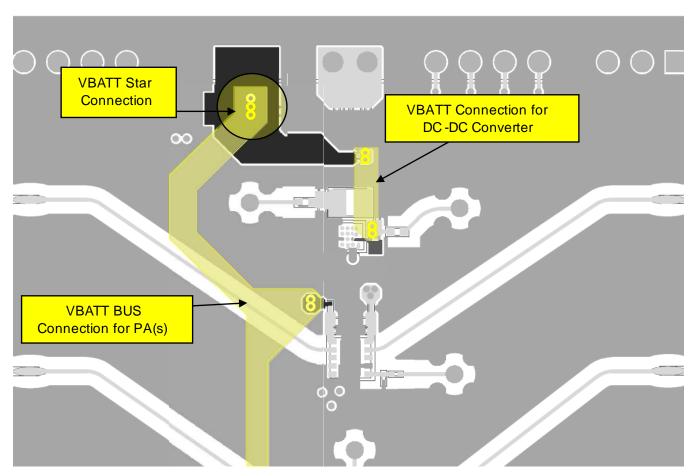

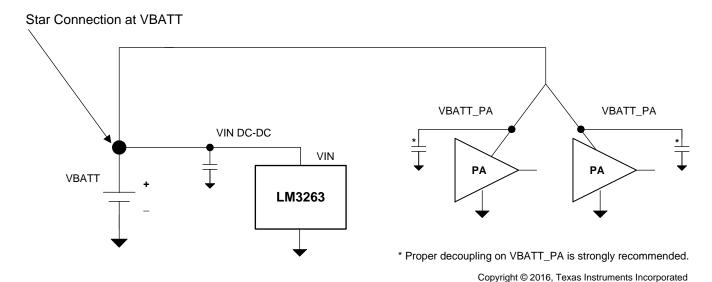

|      | 5    | CMD_LENGTH_ERR | 0       | No                                                          |           | Error when transaction interrupted by new SSC. Cleared on read. Write has no effect on this bit.                                                                                                                                                                                                                                                                                                                                     |  |  |