SLVS692E-SEPTEMBER 2006-REVISED MAY 2008

# 8-CHANNEL POWER-SUPPLY SEQUENCER AND MONITOR

### **FEATURES**

- Single Supply Voltage: 3.3 V

- Low Power Consumption

- Sequences and Monitors up to Eight Voltage Rails

- Rail Voltages Sampled Every 50 μs With 3.2-mV Resolution

- Four Configurable Digital Outputs for Power-On Reset and Other Functions

- Configurable Rail-Enable Output Polarity

- Flexible Rail Sequencing: Timeline (ms), Parent Rail Regulation Window, Parent Rail Achieving Defined Threshold

- Under- and Overvoltage Thresholds: Settable

Per-Rail

- Regulation Expiration Time: Settable Per-Rail

- Flexible Rail Shutdown: Parent Rail Shutdown Can Shut Down Child Rails, Independent Rail Configuration

- Per-Rail Alarm Conditions, With Timestamp: Under- and Overvoltage Glitch, Sustained Under- and/or Overvoltage, Rail Did Not Start

- I<sup>2</sup>C Interface for Configuration and Monitoring

- Microsoft<sup>®</sup> Windows<sup>®</sup> GUI for Configuration and Monitoring

### APPLICATIONS

- Telecommunications Switches

- Servers

- Networking Equipment

- Test Equipment

- Any System Requiring Sequencing of Multiple Voltage Rails

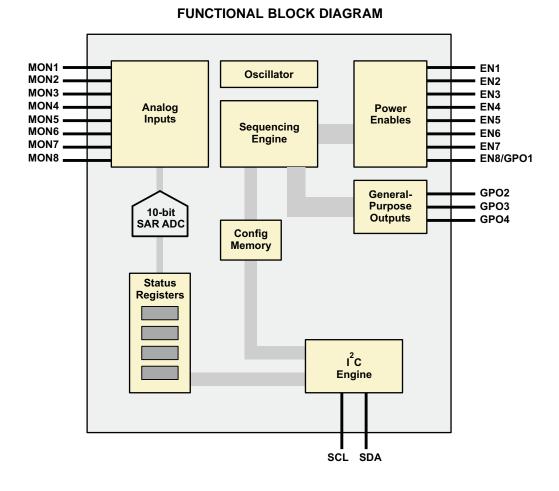

### DESCRIPTION

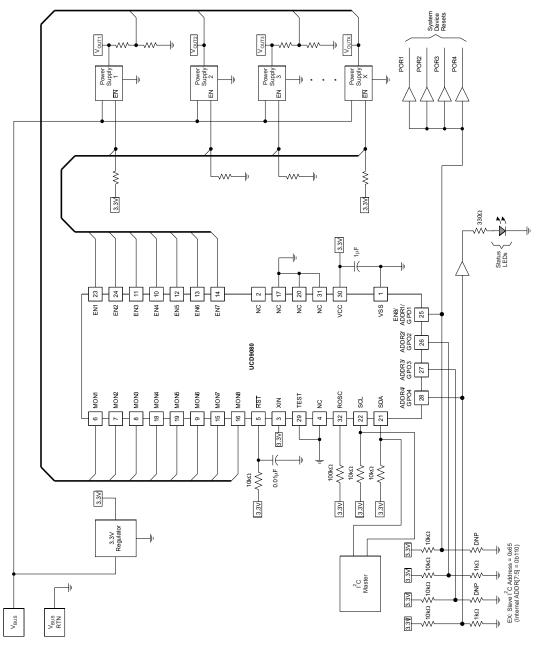

The UCD9080 power-supply sequencer controls the enable sequence of up to eight independent voltage rails and provides four general-purpose digital outputs. The device operates from a 3.3-V supply, provides 3.2-mV resolution of voltage rails, and requires no external memory or clock. The UCD9080 monitors the voltage rails independently at more than a 20-kHz rate and has a high degree of rail sequence error-response and rail configurability. The sequencing of rails can be based on time or on time in conjunction with other rails achieving regulation or a voltage threshold. In addition, each rail is monitored for undervoltage and overvoltage glitches and thresholds. Each rail the UCD9080 monitors can be configured to shut down a user-defined set of other rails, and alarm conditions are monitored on a per-rail basis.

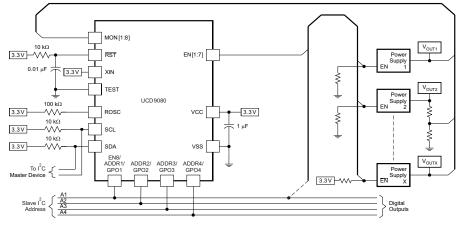

Figure 1 shows the UCD9080 power-supply sequencer in a typical application.

Figure 1. Typical Application Diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TMS320 is a trademark of Texas Instruments.

ÆΑ

Microsoft, Windows are registered trademarks of Microsoft Corporation. All other trademarks are the property of their respective owners.

# UCD9080

SLVS692E-SEPTEMBER 2006-REVISED MAY 2008

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### ORDERING INFORMATION

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

|                  |                                           | VALUE                         | UNIT |

|------------------|-------------------------------------------|-------------------------------|------|

|                  | Voltage applied from VCC to VSS           | -0.3 to 4.1                   | V    |

|                  | Voltage applied to any pin <sup>(2)</sup> | –0.3 to V <sub>CC</sub> + 0.3 | V    |

|                  | Diode current at any device terminal      | ±2                            | mA   |

| T <sub>stg</sub> | Storage temperature                       | -40 to 85                     | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages referenced to VSS.

### **RECOMMENDED OPERATING CONDITIONS**

|                 |                                             | MIN | NOM | MAX | UNIT |

|-----------------|---------------------------------------------|-----|-----|-----|------|

| V               | Supply voltage during operation             | 3   | 3.3 | 3.6 | V    |

| V <sub>CC</sub> | Supply voltage during configuration changes | 3   | 3.3 | 3.6 | v    |

| T <sub>A</sub>  | Operating free-air temperature range        | -40 |     | 85  | °C   |

### **ELECTRICAL CHARACTERISTICS**

These specifications are over recommended ranges of supply voltage and operating free-air temperature, unless otherwise noted

|                  | PARAMETER                                                        | PARAMETER TEST CONDITIONS         |                      |   |                       | UNIT |  |  |  |  |

|------------------|------------------------------------------------------------------|-----------------------------------|----------------------|---|-----------------------|------|--|--|--|--|

| SUPPLY CURRENT   |                                                                  |                                   |                      |   |                       |      |  |  |  |  |

| I <sub>S</sub>   | Supply current into V <sub>CC</sub> , excluding external current | $T_A = 25^{\circ}C$               |                      | 3 | 4                     | mA   |  |  |  |  |

| I <sub>C</sub>   | Supply current during configuration                              | 3.6 V                             | 3                    |   | 7                     | mA   |  |  |  |  |

| STAND            | ARD INPUTS (RST, TEST)                                           |                                   | L                    |   |                       |      |  |  |  |  |

| V <sub>IL</sub>  | Low-level input voltage                                          | V <sub>CC</sub> = 3 V             | V <sub>SS</sub>      |   | V <sub>SS</sub> + 0.6 | V    |  |  |  |  |

| VIH              | High-level input voltage                                         | V <sub>CC</sub> = 3 V             | 0.8 V <sub>CC</sub>  |   | V <sub>CC</sub>       | V    |  |  |  |  |

| SCHMIT           | T TRIGGER INPUTS (SDA, SCL, EN1, EN2, EN                         | 3, EN4, EN5, EN6, EN7, EN8/ADDR1, | ADDR2, ADDR3, ADDR4) |   |                       |      |  |  |  |  |

| V <sub>IT+</sub> | Positive-going input threshold voltage                           | V <sub>CC</sub> = 3 V             | 1.5                  |   | 1.9                   | V    |  |  |  |  |

| V <sub>IT-</sub> | Negative-going input threshold voltage                           | V <sub>CC</sub> = 3 V             | 0.9                  |   | 1.3                   | V    |  |  |  |  |

| V <sub>hys</sub> | Input-voltage hysteresis, (V <sub>IT+</sub> – V <sub>IT-</sub> ) | V <sub>CC</sub> = 3 V             | 0.5                  |   | 1                     | V    |  |  |  |  |

| l <sub>ikg</sub> | High-impedance leakage current                                   |                                   |                      |   | ±50                   | nA   |  |  |  |  |

**EXAS INSTRUMENTS**

www.ti.com

### ELECTRICAL CHARACTERISTICS (continued)

These specifications are over recommended ranges of supply voltage and operating free-air temperature, unless otherwise noted

|                                  | PARAMETER                                     | TEST CONDITIONS                                                                                                                     | MIN             | NOM                      | MAX                   | UNIT   |

|----------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|-----------------------|--------|

| ANALOG I                         | NPUTS (MON1, MON2, MON3, MON4, MON5           | 5, MON6, MON7, MON8, ROSC)                                                                                                          |                 |                          |                       |        |

| V <sub>CC</sub>                  | Analog supply voltage                         | V <sub>SS</sub> = 0 V                                                                                                               | 3               |                          | 3.6                   | V      |

|                                  |                                               | Internal voltage reference                                                                                                          | 0               |                          | 2.5                   |        |

| V <sub>(R&lt;18&gt;)</sub>       | Analog input voltage                          | External voltage reference<br>(V <sub>CC</sub> = 3.3 V used as reference)                                                           | 0               |                          | V <sub>CC</sub>       | V      |

| C <sub>1</sub> <sup>(1)</sup>    | Input capacitance                             | Only one terminal can be selected at a time (MON1–MON8)                                                                             |                 |                          | 27                    | pF     |

| R <sub>I</sub> <sup>(1)</sup>    | Input MUX ON resistance                       | $0 \text{ V} \leq \text{V}_{(MONx)} \leq \text{VCC}, \text{ V}_{CC} = 3 \text{ V}$                                                  |                 |                          | 2000                  | Ω      |

| l <sub>ikg</sub>                 | High-impedance leakage current                | MON1-MON8                                                                                                                           |                 |                          | ±50                   | nA     |

| VREF+                            | Positive internal reference voltage output    | $\begin{array}{l} REF2\_5V = 1 \text{ for } 2.5 \text{ V } I_{(VREF+)} \leq \\ I_{(VREF+)} max, \ V_{CC} = 3 \text{ V} \end{array}$ | 2.35            | 2.5                      | 2.65                  | V      |

| ) (                              | VCC minimum voltage, positive built-in        | REF2_5V = 1, I <sub>(VREF+)</sub> ≤ 0.5 mA                                                                                          | 3               |                          |                       | V      |

| V <sub>CC</sub> (min)            | reference active                              | $REF2\_5V = 1, \ I_{(VREF+)} \le 1 \ mA$                                                                                            | 3               |                          |                       | V      |

|                                  | Accuracy of voltage compling from rolls       | Internal reference (2.5 V)                                                                                                          | ±6.8            | ±12                      | ±17.4                 |        |

| V <sub>(acc)</sub>               | Accuracy of voltage sampling from rails       | External reference (3.3 V/V <sub>CC</sub> )                                                                                         | ±0.2            | ±1.6                     | ±6.8                  | mV     |

| T <sub>REF+</sub> <sup>(1)</sup> | Temperature coefficient of built-in reference | $I_{(VREF+)}$ is a constant in the range of<br>0 mA $\leq I_{(VREF+)} \leq$ 1 mA, VCC = 3 V                                         |                 |                          | ±100                  | ppm/°C |

| MISCELLA                         | NEOUS                                         |                                                                                                                                     |                 |                          |                       |        |

| t <sub>retention</sub>           | Retention of configuration parameters         | $T_J = 25^{\circ}C$                                                                                                                 | 100             |                          |                       | Years  |

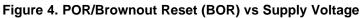

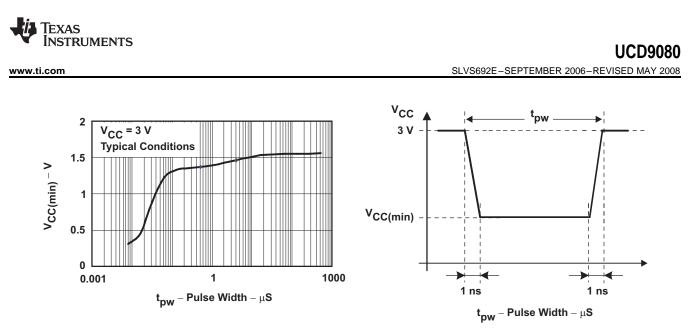

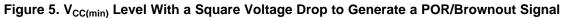

| POR, Brow                        | vnout, Reset <sup>(2) (3)</sup>               |                                                                                                                                     |                 |                          |                       |        |

| t <sub>d(BOR)</sub>              |                                               |                                                                                                                                     |                 |                          | 2000                  | μs     |

| VCC <sub>(start)</sub>           |                                               |                                                                                                                                     |                 | 0.7×V <sub>(B_IT-)</sub> |                       | V      |

| V <sub>(B_IT-)</sub>             | Brownout                                      | VCC/dt ≤ 3 V/s                                                                                                                      |                 |                          | 1.71                  | V      |

| V <sub>hys(B_IT-)</sub>          |                                               |                                                                                                                                     | 70              | 130                      | 180                   | mV     |

| t <sub>(reset)</sub>             |                                               | Pulse length needed at RST pin to accept reset internally, V <sub>CC</sub> = 3 V                                                    | 2               |                          |                       | μs     |

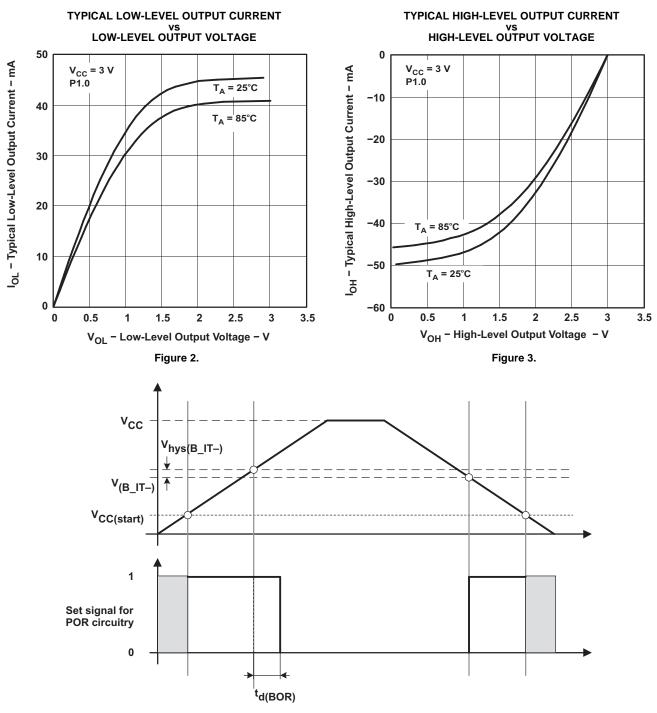

| DIGITAL O                        | UTPUTS (EN8/GPO1, GPO2, GPO3, GPO4,           | EN1, EN2, EN3, EN4, EN5, EN6, EN7, SDA, SC                                                                                          | )L)             |                          |                       |        |

| V                                | High lovel output veltage                     | $I_{OH}(max) = -1.5 \text{ mA},^{(4)} \text{ V}_{CC} = 3 \text{ V}$                                                                 | $V_{CC} - 0.25$ |                          | V <sub>CC</sub>       | V      |

| V <sub>OH</sub>                  | High-level output voltage                     | $I_{OH}(max) = -6 \text{ mA},^{(5)} V_{CC} = 3 \text{ V}$                                                                           | $V_{CC} - 0.6$  |                          | V <sub>CC</sub>       | v      |

| V                                | Low-level output voltage                      | $I_{OH}(max) = -1.5 \text{ mA}$ , <sup>(4)</sup> $V_{CC} = 3 \text{ V}$                                                             | V <sub>SS</sub> |                          | $V_{SS} + 0.25$       | V      |

| V <sub>OL</sub>                  |                                               | $I_{OH}(max) = -6 \text{ mA},^{(5)} V_{CC} = 3 \text{ V}$                                                                           | V <sub>SS</sub> |                          | V <sub>SS</sub> + 0.6 | v      |

| l <sub>lkg</sub>                 | High-impedance leakage current                | $V_{CC} = 3 V$                                                                                                                      |                 |                          | ±50                   | nA     |

Not production tested. Limits verified by design. (1)

The current consumption of the brownout module is already included in the I<sub>CC</sub> current-consumption data. (2)

(3)

During power up, device initialization starts subsequent to a period of  $t_{d(BOR)}$  after  $V_{CC} = V_{(B_{-}IT-)} + V_{hys(B_{-}IT-)}$ . The maximum total current,  $I_{OH}$ max and  $I_{OL}$ max, for all outputs combined, should not exceed ±12 mA to hold the maximum voltage drop (4) specified.

The maximum total current, I<sub>OH</sub>max and I<sub>OL</sub>max, for all outputs combined, should not exceed ±48 mA to hold the maximum voltage drop (5) specified.

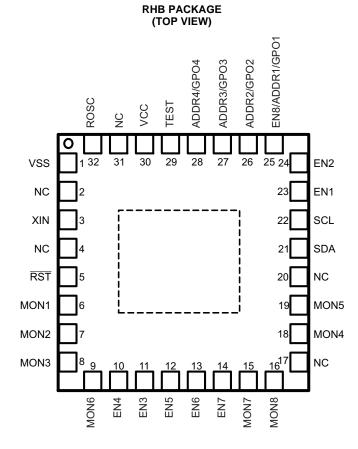

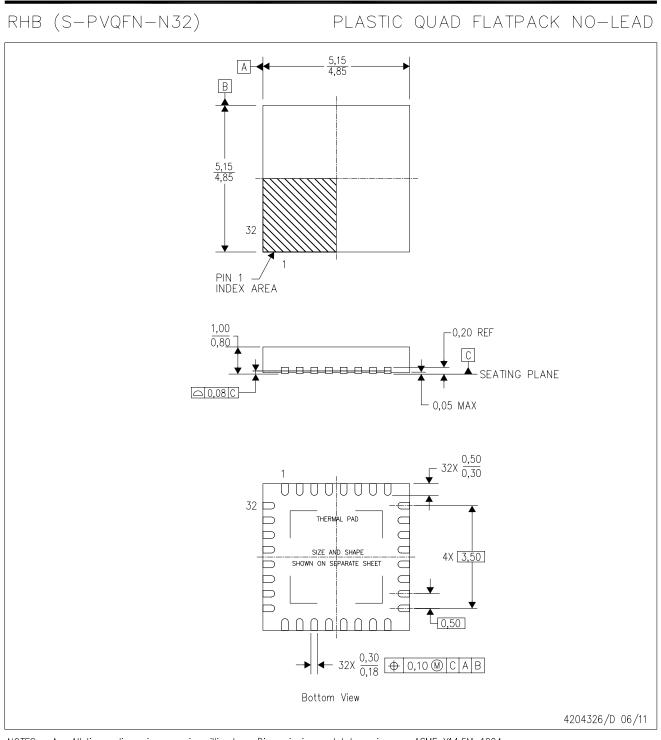

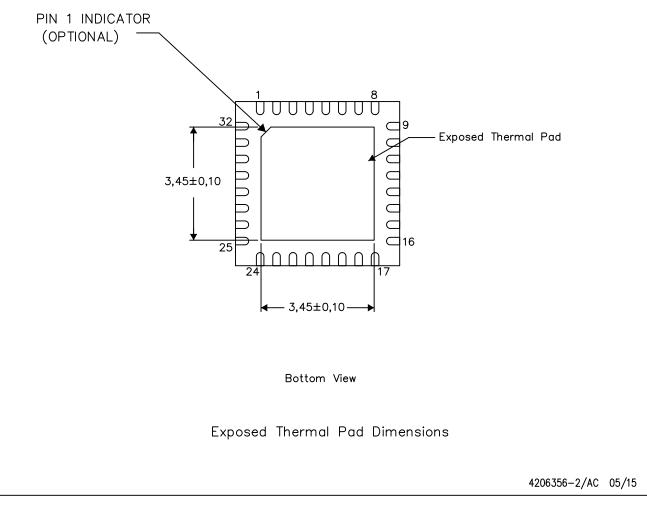

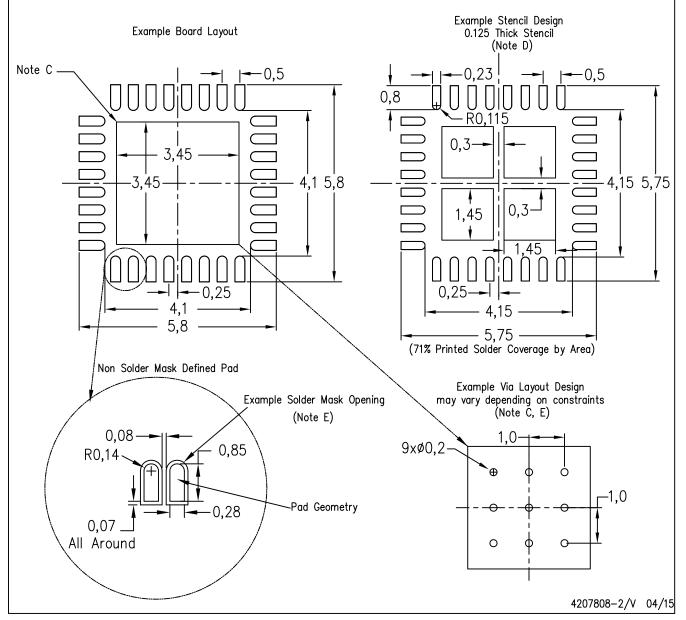

The UCD9080 is compatible with 3.3-V IO ports of microcontrollers, TMS320<sup>™</sup> DSP family as well as ASICs. The UCD9080 is available in a plastic 32-pin QFN package (RHB).

### DIGITAL OUTPUTS (Only One Output Loaded at a Time)

Figure 6. V<sub>CC(min)</sub> Level With a Triangle Voltage Drop to Generate a POR/Brownout Signal

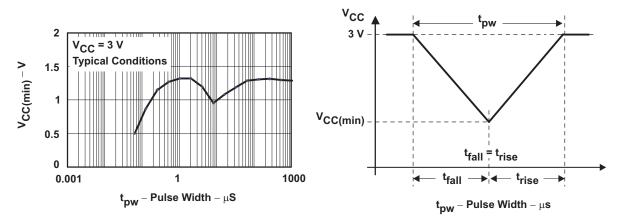

### I<sup>2</sup>C TIMING

The UCD9080 supports the same timing parameters as standard-mode  $I^2C$ . See the following timing diagram and timing parameters for more information.

**NSTRUMENTS**

EXAS

### TIMING PARAMETERS FOR I<sup>2</sup>C INTERFACE

|                     | PARAMETER                                                                                             | MIN              | MAX                 | UNIT |

|---------------------|-------------------------------------------------------------------------------------------------------|------------------|---------------------|------|

| t <sub>of</sub>     | Output fall time from $V_{OH}$ to $V_{OL}$ <sup>(1)</sup> with a bus capacitance from 10 pF to 400 pF |                  | 250 <sup>(2)</sup>  | ns   |

| CI                  | Capacitance for each pin.                                                                             |                  | 10                  | pF   |

| f <sub>SCL</sub>    | SCL clock frequency                                                                                   | 10               | 100                 | kHz  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated.          | 4                |                     | μs   |

| t <sub>HD;DAT</sub> | Data hold time                                                                                        | 0 <sup>(3)</sup> | 3.45 <sup>(4)</sup> | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                           | 4.7              |                     | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                          | 4                |                     | μs   |

| t <sub>SU;STA</sub> | Set-up time for repeated start condition                                                              | 4.7              |                     | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                                                                       | 250              |                     | ns   |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                                                                 |                  | 1000                | ns   |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                                                                 |                  | 300                 | ns   |

| t <sub>SU;STO</sub> | Setup time for STOP condition                                                                         | 4                |                     | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                                      | 4.7              |                     | μs   |

| C <sub>(b)</sub>    | Capacitive load for each bus line                                                                     |                  | 400                 | pF   |

| V <sub>nL</sub>     | Noise margin at the LOW level for each connected device (including hysteresis)                        | 0.1 VDD          |                     | V    |

| V <sub>nH</sub>     | Noise margin at the HIGH level for each connected device (including hysteresis)                       | 0.2 VDD          |                     | V    |

(1) See the *Electrical Characteristics* section of this data sheet.

(2) The maximum t<sub>f</sub> for the SDA and SCL bus lines (300 ns) is longer than the specified maximum t<sub>of</sub> for the output stages (250 ns). This allows series protection resistors (R<sub>s</sub>) to be connected between the SDA/SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

(3) A device must internally provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL.

(4) The maximum t<sub>HD:DAT</sub> must only be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal.

### Table 1. TERMINAL FUNCTIONS

| TERMIN             | AL              |     |                                                                                                                                                  |

|--------------------|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | NO.             | I/O | DESCRIPTION                                                                                                                                      |

| ADDR2/GPO2         | 26              | I/O | I <sup>2</sup> C address select 2, general-purpose digital output 2                                                                              |

| ADDR3/GPO3         | 27              | I/O | I <sup>2</sup> C address select 3, general-purpose digital output 3                                                                              |

| ADDR4/GPO4         | 28              | I/O | I <sup>2</sup> C address select 4, general-purpose digital output 4                                                                              |

| EN1                | 23              | I/O | Voltage rail 1 enable (digital output)                                                                                                           |

| EN2                | 24              | I/O | Voltage rail 2 enable (digital output)                                                                                                           |

| EN3                | 11              | I/O | Voltage rail 3 enable (digital output)                                                                                                           |

| EN4                | 10              | I/O | Voltage rail 4 enable (digital output)                                                                                                           |

| EN5                | 12              | I/O | Voltage rail 5 enable (digital output)                                                                                                           |

| EN6                | 13              | I/O | Voltage rail 6 enable (digital output)                                                                                                           |

| EN7                | 14              | I/O | Voltage rail 7 enable (digital output)                                                                                                           |

| EN8/ADDR1/<br>GPO1 | 25              | I/O | Voltage rail 8 enable (digital output), I <sup>2</sup> C address select 1, general-purpose digital output 1                                      |

| MON1               | 6               | I   | Analog input for voltage rail 1                                                                                                                  |

| MON2               | 7               | I   | Analog input for voltage rail 2                                                                                                                  |

| MON3               | 8               | I   | Analog input for voltage rail 3                                                                                                                  |

| MON4               | 18              | I   | Analog input for voltage rail 4                                                                                                                  |

| MON5               | 19              | I   | Analog input for voltage rail 5                                                                                                                  |

| MON6               | 9               | I   | Analog input for voltage rail 6                                                                                                                  |

| MON7               | 15              | I   | Analog input for voltage rail 7                                                                                                                  |

| MON8               | 16              | I   | Analog input for voltage rail 8                                                                                                                  |

| NC                 | 2               |     | Do not connect.                                                                                                                                  |

| NC                 | 4,17,<br>20, 31 |     | Not connected internally. Connect to VSS.                                                                                                        |

| ROSC               | 32              |     | Internal oscillator frequency adjust. Must use 100-k $\Omega$ pullup to VCC for minimum drift and maximum frequency when sampling voltage rails. |

| RST                | 5               | I   | Reset input                                                                                                                                      |

| SCL                | 22              | I/O | I <sup>2</sup> C clock. A pullup rwesistor to 3.3 V is required.                                                                                 |

| SDA                | 21              | I/O | l <sup>2</sup> C data (bidirectional). A pullup resistor to 3.3 V is required.                                                                   |

| TEST               | 29              | I   | Connect to VSS                                                                                                                                   |

| VCC                | 30              |     | Supply voltage                                                                                                                                   |

| VSS                | 1               |     | Ground reference                                                                                                                                 |

| XIN                | 3               |     | Connect to VCC                                                                                                                                   |

**INSTRUMENTS**

Texas

### FUNCTIONAL DESCRIPTION

#### POWER-SUPPLY SEQUENCING

The UCD9080 can be configured to sequence the power rails using the enable signals or the general-purpose outputs in one of three ways.

The first way is to specify a delay time after a UCD9080 RESET. The enable/GPO is asserted after the UCD9080 RESET plus a specified delay.

The second way is to specify a delay time after another (parent) rail has achieved regulation (that is,  $V_{RAIL}$  is within the specified under- and overvoltage settings). The enable/GPO is asserted after the (parent) rail is in regulation plus specified delay.

The third way is to specify a (parent) rail voltage. The enable/GPO is asserted after the (parent) rail voltage is greater than or equal to the specified voltage.

Of course, a rail does not have to be sequenced, as in the case of a backplane voltage that is not under the control of the UCD9080, but is being monitored.

#### POWER-SUPPLY ENABLES

The UCD9080 can sequence up to eight power supplies using the ENx (EN1 to EN8) signals. These signals can be configured as active-high or active-low, supporting power supplies with either polarity.

EN8 can also be configured as a GPO (GPO1). EN8/ADDR1/GPO1 is also used for I<sup>2</sup>C address selection (ADDR1).

#### **GENERAL-PURPOSE OUTPUTS**

The UCD9080 can control up to four general-purpose digital outputs using the same sequencing mechanisms as described in the *Power-Supply Enables* section. These general-purpose outputs (referred to as GPO1–GPO4) can be used for digital signals such as RESET or status. Note that these signals are multiplexed with other functions (primarily I<sup>2</sup>C address selection). See the *Terminal Functions* table to ensure that these signals are used properly by the application. Also note that the GPO1 signal is multiplexed with EN8, so both of these cannot be used at the same time.

### EXTERNAL CONSIDERATIONS FOR EN AND GPO PINS

During the UCD9080 RESET interval, all ENx and GPOx pins become Schmitt-trigger Inputs. A UCD9080 RESET occurs under the following conditions:

- External RST pin is driven low.

- Power is applied to the device (power-on reset) or power is cycled.

- A sequence event occurs as a result of a configured rail-alarm event.

- The RESTART register is written with a value of 0 over the I<sup>2</sup>C bus.

All ENx and GPOx pins must be externally terminated to one of the following Schmitt-trigger input-logic states for proper sequencer operation.

- EN or GPO pin configured for ACTIVE-LOW polarity: the external resistor network must default the corresponding EN or GPO pin to a voltage greater than or equal to 1.9 V (V<sub>IT+</sub>, MAX, positive-going input threshold voltage) during device reset.

- EN or GPO pin configured for ACTIVE-HIGH polarity: the external resistor network must default the corresponding EN or GPO pin to a voltage less than or equal to 0.9 V (V<sub>IT-</sub>, MIN, negative-going input threshold voltage) during device reset.

#### NOTE:

The external resistor networks should not derive their voltage from a sequenced power supply, as this may cause the voltage level presented to the ENx or GPOx pin to be at the wrong level during device reset. It is best to use the UCD9080 VCC supply for the external resistor networks.

SLVS692E-SEPTEMBER 2006-REVISED MAY 2008

www.ti.com

The user must consider GPO polarity usage when programming the UCD9080 I<sup>2</sup>C address using the external GPOx (ADDRx) resistor networks. Acceptable ADDRx bit voltage levels are set according to Schmitt-trigger input specifications. The following GPOx/ADDRx combinations are acceptable:

- GPOx = Active-low polarity: Corresponding ADDRx bit set to Schmitt-trigger input logic level = 1

- GPOx = Active-high polarity: Corresponding ADDRx bit set to Schmitt-trigger input logic level = 0

### VOLTAGE REFERENCE

**UCD9080**

The UCD9080 has a voltage reference that is selectable via the  $I^2C$  interface and parameter configuration section. The voltage reference can either be an internally generated 2.5-V reference or an external 3.3-V reference. If the external voltage reference is selected, then the 3.3-V reference is from the V<sub>CC</sub> supply to the UCD9080.

Depending on the voltage reference that is being used, the accuracy of reading voltages is affected. The internal reference is not as accurate as the external reference and affects the accuracy of the sampled voltages of the monitored rails. See the *Electrical Characteristics* for information on voltage reading accuracy for use with each of the references.

The *Configuring the UCD9080* section details how to select the internal or external voltage reference.

### VOLTAGE MONITORING

The UCD9080 can monitor eight voltage rails through the MONx terminals of the device (MON1–MON8). The UCD9080 samples these eight input channels using either the internal 2.5-V reference or  $V_{CC}$  (3.3 V) as a voltage reference to convert the voltage to digital values. The eight digitally monitored voltage values are accessible via the  $I^2C$  interface.

When monitoring a voltage rail that has a nominal voltage larger than 2.5 V (internal reference) or 3.3 V (external reference), a resistor divider network is typically used. The design must ensure that the source impedance of that resistor network is not too high, because it causes the UCD9080 analog-to-digital converter (ADC) to take longer to perform the sample-and-hold conversion. The extended conversion time causes the frequency of the sampling of voltage rails to slow below 20 kHz.

Using a higher-valued resistor network lowers the overall power dissipation of the solution, which is desirable. In order to keep the source impedance low, a buffer circuit is typically used. The UCD9080 analog inputs require that a source impedance of less than 20 k $\Omega$  be used in order to maintain the high sampling rate of the voltages.

The UCD9080 allows specification of overvoltage threshold, undervoltage threshold, and out-of-regulation or glitch duration for each monitored rail.

Each voltage rail can also be marked so that it is not monitored, in which case all checks and alarm conditions are disabled.

### RAIL SHUTDOWN

Rail shutdown is the act of setting the ENx pin associated with that rail to a state which disables the power supply output. Each UCD9080 rail can be configured to shut down based on a monitored alarm event (sustained overvoltage, sustained undervoltage, or rail did not start) and in a configurable manner.

The options for rail shutdown are as follows:

- Ignore

- Log only

- Sequence

- Retry 1 time

- Retry 0 times

If the system does not care whether a monitored rail enters a sustained error condition, the UCD9080 can be configured to either ignore or log the error event and take no subsequent action.

The UCD9080 can also be configured to sequence the entire system in response to a sustained error condition. When the UCD9080 monitors an alarm event on the configured rail, UCD9080 RESET occurs (all ENx and GPOx outputs go to the high-impedance state for ~4–5 ms). Next, a sequence of all configured enables and GPOs occurs, as defined by the current sequencer configuration. Note that for this configuration, a shutdown according to the values in the UnsequenceTime register does not occur prior to UCD9080 RESET.

The UCD9080 can also be configured to attempt to restart a rail once in response to a sustained error condition. When the UCD9080 monitors an alarm event on a configured rail, the rail is momentarily disabled and then re-enabled. The rail remains enabled according to the RampTime register setting (time), and if the rail does not properly achieve regulation, the system (rail and dependent rails) is shut down as defined by the current sequencer configuration (UnsequenceTime register).

The last option that the UCD9080 supports is to shut down (if specified as a dependency) and disable (Retry 0 times) a configured rail in response to a sustained error condition. When the UCD9080 monitors an alarm event on the configured rail, the system (dependent rails and GPOs) is shut down as defined by the current sequencer configuration (UnsequenceTime register). Only rails and GPOs marked as dependencies of the configured rail are shut down. If there are no rails or GPO dependencies marked, the configured rail is just disabled in response to the sustained error condition.

Each UCD9080 ENx and GPOx output can be marked to sequence after shutdown (as defined by the current sequencer configuration) if specified as a dependency in the DependencyMasks register. For example, if rail 1 is configured to sequence after shutdown (RESEQ bit set), and rail 2 has rail 1 set in its dependency mask, then if/when rail 2 is shut down, rail 1 shuts down and the system resequences.

### BROWNOUT

The brownout circuit is implemented to provide the proper internal reset signal to the device during power on and power off.

### I<sup>2</sup>C INTERFACE

The UCD9080 power-supply sequencer has a 100-kHz, slave-mode  $I^2C$  interface for communication with an  $I^2C$  master. The  $I^2C$  master uses this interface to configure and monitor the UCD9080.

#### I<sup>2</sup>C Address Selection

The UCD9080 supports 7-bit I<sup>2</sup>C addressing. The UCD9080 selects an I<sup>2</sup>C address by sampling the logic level of the four digital inputs to the device (ADDR1–ADDR4) during the UCD9080 RESET interval. When the UCD9080 is released from RESET, the ADDRx logic levels are latched and the I<sup>2</sup>C address is assigned as shown in Figure 8.

| A7 = 1 | A6 = 1 | A5 = 0 | A4 = ADDR4/GPO4 | A3 = ADDR3/GPO3 | A2 = ADDR2/GPO2 | A1 = EN8/ADDR1/GPO1 |

|--------|--------|--------|-----------------|-----------------|-----------------|---------------------|

|--------|--------|--------|-----------------|-----------------|-----------------|---------------------|

#### Figure 8. I<sup>2</sup>C ADDRESS = 0x60–0x6F

External pullup/pulldown resistors are required to configure the I<sup>2</sup>C address; the UCD9080 does not have internal bias resistors. Note that the 7-bit I<sup>2</sup>C address refers to the address bits only, not the read/write (8<sup>th</sup>) bit in the first byte of the I<sup>2</sup>C protocol. The base I<sup>2</sup>C address is 0x60 and the I<sup>2</sup>C general-call address (0x00) is not supported.

After the initialization process of the UCD9080 is complete, these four pins can be used as general-purpose outputs (GPOs). They can be programmed and sequenced as described in the *Configuring the UDC9080* section. GPO polarity must consider the external I<sup>2</sup>C address resistors as described in the *External Considerations for EN and GPO Pins* section.

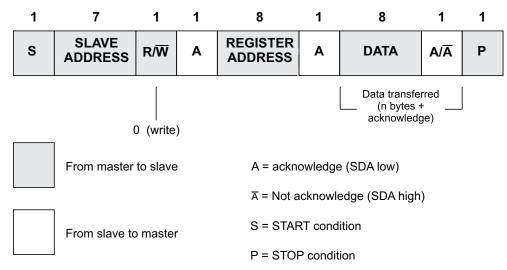

#### I<sup>2</sup>C Transactions

The UCD9080 can be configured and monitored via  $I^2C$  memory-mapped registers. Registers that are configurable (can be written) via an  $I^2C$  write operation are implemented using an  $I^2C$  unidirectional data transfer, from the master to slave, with a stop bit between transactions.

Copyright © 2006–2008, Texas Instruments Incorporated

**UCD9080**

SLVS692E-SEPTEMBER 2006-REVISED MAY 2008

www.ti.com

#### PC Unidirectional Transfer

Figure 9. I<sup>2</sup>C Register Access With START/STOP

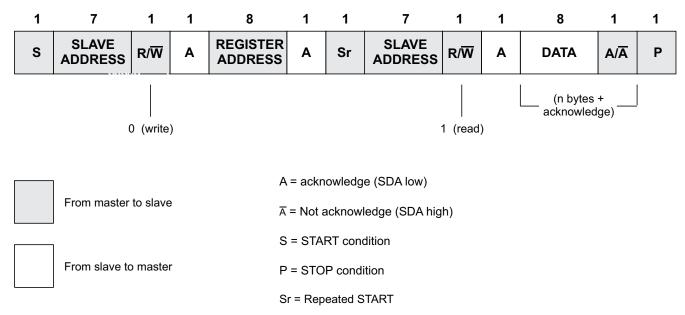

Registers that can be read are implemented using an I<sup>2</sup>C read operation, which uses the I<sup>2</sup>C combined format that changes data direction during the transaction. This transaction uses an I<sup>2</sup>C repeated START during the direction change.

### PC Combined Format

### Figure 10. I<sup>2</sup>C Register Access With Repeated START

The UCD9080 also supports a feature that auto-increments the register address pointer for increased efficiency when accessing sequential blocks of data. It is not necessary to issue separate I<sup>2</sup>C transactions.

### CONFIGURING AND MONITORING THE UCD9080

The UCD9080 supports both configuration and monitoring using its I<sup>2</sup>C slave interface. A Microsoft Windows GUI is available for configuring and monitoring the UCD9080. See the UCD9080 Power Supply Sequencer and Monitor EVM user's guide (SLVU184).

For monitoring the sequencer, an I<sup>2</sup>C memory map allows an I<sup>2</sup>C host to perform memory-mapped reads (and in some cases writes) to obtain status information from the UCD9080. For instance, all rails can report their voltage through the I<sup>2</sup>C memory map. For information on which parameters are available via the I<sup>2</sup>C memory map, see the *Monitoring the UCD9080* section.

To change configuration parameters of the sequencer, a different mechanism is used. The entire set of configuration parameters must be written to the device at one time as one large transaction over the  $I^2C$  interface to ensure that the configuration of the device is consistent at any given time. The process for configuring the UCD9080 is described in the *Configuring the UDC9080* section.

### MONITORING THE UCD9080

#### **Register Map**

The UCD9080 allows all monitoring of the system through the  $I^2C$  interface on the device. The following is the memory map of the supported registers in the system. The detail of each of these registers is given in the next section as well.

Note that the UCD9080 supports functionality to increment the I<sup>2</sup>C register address value automatically when a register is being accessed, to access blocks of like registers more efficiently. The following table also shows the amount that the register address is incremented for each register access.

| REGISTER NAME | ADDRESS | ACCESS | ADJUSTMENT AFTER ACCESS |

|---------------|---------|--------|-------------------------|

| RAIL1H        | 0x00    | r      | +1 (0x01)               |

| RAIL1L        | 0x01    | r      | +1 (0x02)               |

| RAIL2H        | 0x02    | r      | +1 (0x03)               |

| RAIL2L        | 0x03    | r      | +1 (0x04)               |

| RAIL3H        | 0x04    | r      | +1 (0x05)               |

| RAIL3L        | 0x05    | r      | +1 (0x06)               |

| RAIL4H        | 0x06    | r      | +1 (0x07)               |

| RAIL4L        | 0x07    | r      | +1 (0x08)               |

| RAIL5H        | 0x08    | r      | +1 (0x09)               |

| RAIL5L        | 0x09    | r      | +1 (0x0A)               |

| RAIL6H        | 0x0A    | r      | +1 (0x0B)               |

| RAIL6L        | 0x0B    | r      | +1 (0x0C)               |

| RAIL7H        | 0x0C    | r      | +1 (0x0D)               |

| RAIL7L        | 0x0D    | r      | +1 (0x0E)               |

| RAIL8H        | 0x0E    | r      | +1 (0x0F)               |

| RAIL8L        | 0x0F    | r      | -15 (0x00)              |

| ERROR1        | 0x20    | r      | +1 (0x21)               |

| ERROR2        | 0x21    | r      | +1 (0x22)               |

| ERROR3        | 0x22    | r      | +1 (0x23)               |

| ERROR4        | 0x23    | r      | +1 (0x24)               |

| ERROR5        | 0x24    | r      | +1 (0x25)               |

| ERROR6        | 0x25    | r      | -5 (0x20)               |

| STATUS        | 0x26    | r      | 0 (0x26)                |

| VERSION       | 0x27    | r      | 0 (0x27)                |

| RAILSTATUS1   | 0x28    | r      | +1 (0x29)               |

| RAILSTATUS2   | 0x29    | r      | -1 (0x28)               |

| FLASHLOCK     | 0x2E    | rw     | 0 (0x2E)                |

| RESTART       | 0x2F    | w      | 0 (0x2F)                |

| WADDR1        | 0x30    | rw     | +1 (0x31)               |

| WADDR2        | 0x31    | rw     | -1 (0x30)               |

Copyright © 2006–2008, Texas Instruments Incorporated

UCD9080

SLVS692E-SEPTEMBER 2006-REVISED MAY 2008

www.ti.com

| REGISTER NA | ME ADDRESS | ACCESS | ADJUSTMENT AFTER ACCESS |

|-------------|------------|--------|-------------------------|

| WDATA1      | 0x32       | rw     | +1 (0x33)               |

| WDATA2      | 0x33       | rw     | -1 (0x32)               |

#### **Register Descriptions**

The following are the detailed descriptions of each of the UCD9080 I<sup>2</sup>C registers.

The following register bit conventions are used. Each register is shown with a key indicating the accessibility of each bit, and the initial condition after device initialization.

| KEY    | ACCESS                         |

|--------|--------------------------------|

| rw     | Read/write                     |

| r      | Read-only                      |

| rO     | Read as 0                      |

| r1     | Read as 1                      |

| W      | Write-only                     |

| w0     | Write as 0                     |

| w1     | Write as 1                     |

| rc     | Read clears bit after read     |

| rs     | Read sets bit after read       |

| -0, -1 | Condition after initialization |

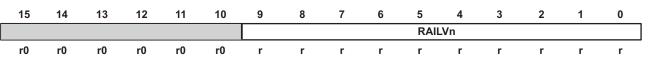

### RAIL

For each of eight voltage rails, the UCD9080 has two registers that contain the rolling average voltage for the associated rail as measured by the device. This average voltage is maintained in real-time by the UCD9080 and is calculated as the output of a 4-TAP FIR filter. There are two registers for each voltage rail. One holds the least-significant 8 bits of the voltage and the other the most-significant 2 bits of the voltage. This is shown in the following table.

| Register Name | Address | Register Contents       |

|---------------|---------|-------------------------|

| RAIL1H        | 0x00    | RAIL1 voltage, bits 9:8 |

| RAIL1L        | 0x01    | RAIL1 voltage, bits 7:0 |

| RAIL2H        | 0x02    | RAIL2 voltage, bits 9:8 |

| RAIL2L        | 0x03    | RAIL2 voltage, bits 7:0 |

| RAIL3H        | 0x04    | RAIL3 voltage, bits 9:8 |

| RAIL3L        | 0x05    | RAIL3 voltage, bits 7:0 |

| RAIL4H        | 0x06    | RAIL4 voltage, bits 9:8 |

| RAIL4L        | 0x07    | RAIL4 voltage, bits 7:0 |

| RAIL5H        | 0x08    | RAIL5 voltage, bits 9:8 |

| RAIL5L        | 0x09    | RAIL5 voltage, bits 7:0 |

| RAIL6H        | 0x0A    | RAIL6 voltage, bits 9:8 |

| RAIL6L        | 0x0B    | RAIL6 voltage, bits 7:0 |

| RAIL7H        | 0x0C    | RAIL7 voltage, bits 9:8 |

| RAIL7L        | 0x0D    | RAIL7 voltage, bits 7:0 |

| RAIL8H        | 0x0E    | RAIL8 voltage, bits 9:8 |

| RAIL8L        | 0x0F    | RAIL8 voltage, bits 7:0 |

(1)

A rail voltage is read with a 16-bit access. The auto-increment feature of the UCD9080 allows multiple rail voltages to be read with a single access.

A rail voltage is provided as a 10-bit value in an unsigned format:

The following formulas can be used to calculate the actual measured rail voltage:

Without external voltage divider:

$$V_{RAILn} = \frac{RAILVn}{1024} \times V_{REF}$$

With external voltage divider:

$$V_{RAILn} = \frac{RAILVn}{1024} \times V_{REF} \times \frac{R_{PULLDOWN} + R_{PULLUP}}{R_{PULLDOWN}}$$

(2)

# UCD9080

SLVS692E-SEPTEMBER 2006-REVISED MAY 2008

ſ

### ERROR

Error conditions are logged by the UCD9080 and are accessible to the user via reading the ERROR register. This is a 6-byte register with the following format:

| 0x20                       |                                                                                                         |     |   |      |   |   |   |                          |                                                            |                              | 0x                            | 21      |        |      |   |

|----------------------------|---------------------------------------------------------------------------------------------------------|-----|---|------|---|---|---|--------------------------|------------------------------------------------------------|------------------------------|-------------------------------|---------|--------|------|---|

| 7                          | 6                                                                                                       | 5   | 4 | 3    | 2 | 1 | 0 | 7                        | 6                                                          | 5                            | 4                             | 3       | 2      | 1    | 0 |

| Err                        | or Co                                                                                                   | ode |   | RAIL |   |   |   | Data                     | (dep                                                       | ender                        | nt on e                       | error o | code)  |      |   |

| r                          | r                                                                                                       | r   | r | r    | r | r | r | r                        | r                                                          | r                            | r                             | r       | r      | r    | r |

| RAIL Meaning               |                                                                                                         |     |   |      |   |   |   |                          | Rail #                                                     | ‡(n) – <sup>-</sup>          | 1, RAI                        | L = 0   | throug | gh 7 |   |

| Error Codes Meaning        |                                                                                                         |     |   |      |   |   |   |                          | Data                                                       |                              |                               |         |        |      |   |

| 0<br>0<br>0<br>1<br>1<br>1 | 000Null alarm001Supply did not start010Sustained overvoltage detected011Sustained undervoltage detected |     |   |      |   |   |   | Avera<br>Avera<br>Glitch | age vo<br>age vo<br>age vo<br>n voltag<br>n voltag<br>rved | ltage o<br>ltage o<br>ge lev | on rail<br>on rail<br>el on l | rail    |        |      |   |

**NOTE:** When error code = *Null Alarm*, then the Hours, Minutes, Seconds, and Milliseconds fields are zero.

|   |   |   | 0x2     | 23 |   |   |   |   |   |   | 0x2      | 22      |   |   |   |

|---|---|---|---------|----|---|---|---|---|---|---|----------|---------|---|---|---|

| 7 | 6 | 5 | 4       | 3  | 2 | 1 | 0 | 7 | 6 | 5 | 4        | 3       | 2 | 1 | 0 |

|   |   |   | Ho      | ur |   |   |   |   |   |   | Minu     | ites    |   |   |   |

| r | r | r | r       | r  | r | r | r | r | r | r | r        | r       | r | r | r |

|   |   |   |         |    |   |   |   |   |   |   |          |         |   |   |   |

|   |   |   | 0x      | 25 |   |   |   |   |   |   | 0x2      | 24      |   |   |   |

| 7 | 6 | 5 | 0x<br>4 |    | 2 | 1 | 0 | 7 | 6 | 5 | 0x2<br>4 | 24<br>3 | 2 | 1 | 0 |

| 7 | 6 | 5 | 4       |    | 2 | 1 | 0 | 7 | 6 |   |          | 3       |   | 1 | 0 |

Error conditions encountered during processing post error logs to this register with some exceptions. This register is internally managed as a FIFO (with a depth of 8). Errors are posted to the FIFO as they occur, and read out of the FIFO via I<sup>2</sup>C access. Due to the unknown latency of host extraction of the FIFO data, the UCD9080 only posts to the FIFO if there is room to write. There is no real-time impact to processing in the UCD9080 if this FIFO is full and cannot be posted to.

The values in registers 0x22 through 0x25 are reset to a value of 0 during UCD9080 RESET.

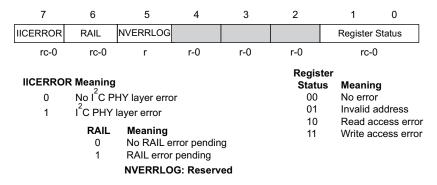

STATUS is an 8-bit read-only register. This register provides real-time status information about the state of the UCD9080. The following bits are defined.

Reading of the STATUS register clears the register except for the NVERRLOG bit, which is maintained until the device is reset. Descriptions of the different errors follow.

The IICERROR bit is set when an I<sup>2</sup>C access fails. This is most often a case where the user has accessed an invalid address or performed an illegal number of operations for a given register (for example, reading 3 bytes from a 2-byte register). In the event of an I<sup>2</sup>C error when IICERROR is set, bits 1:0 of the STATUS register further define the nature of the error as shown in the preceding figure.

The RAIL error bit is set to alert the user to an issue with one of the voltage rails. When this bit is set, the user is advised to query the RAILSTATUS register to further ascertain which RAIL input(s) have an issue. The user may then query the ERROR registers to get further information about the nature of the error condition.

The NVERRLOG bit is reserved for future use.

When the IICERROR bit is set, the register status bits provide further information about the type of I<sup>2</sup>C error that has been detected, as indicated previously.

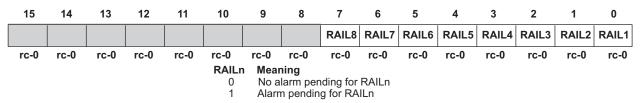

#### RAILSTATUS

The RAILSTATUS1 and RAILSTATUS2 registers are two 8-bit read-only registers that provide a bit mask to represent the error status of the rails as indicated in the following diagram. The RAILSTATUS1 register is reserved.

Bits 15:8 are RAILSTATUS1 and bits 7:0 are RAILSTATUS2. These are read as two 8-bit registers or as a single 16-bit register.

If a bit is set in these registers, then the ERROR register is read to further ascertain the specific error. Bits in the RAILSTATUS1 and RAILSTATUS2 registers are cleared when read.

UCD9080

SLVS692E-SEPTEMBER 2006-REVISED MAY 2008

### FLASHLOCK

The FLASHLOCK register is used to lock and unlock the configuration memory on the UCD9080 when updating the configuration. The *Configuring the UDC9080* section details this process.

The format for the FLASHLOCK register is as follows:

| 7     | 6                      | 5         | 4         | 3        | 2    | 1    | 0    |  |  |

|-------|------------------------|-----------|-----------|----------|------|------|------|--|--|

|       |                        |           | FLASH     | ILOCK    |      |      |      |  |  |

| rw-0  | rw-0                   | rw-0      | rw-0      | rw-0     | rw-0 | rw-0 | rw-0 |  |  |

| FLASH | LOCK                   |           |           |          |      |      |      |  |  |

| 0x00  | Lock fla               | ish (defa | ult)      |          |      |      |      |  |  |

| 0x01  | Flash is being updated |           |           |          |      |      |      |  |  |

| 0x02  | Unlock                 | flash (be | fore conf | iguratio | n)   |      |      |  |  |

#### RESTART

The RESTART register provides the capability for the  $I^2C$  host to force a re-initialization and restart of the UCD9080. This is an 8-bit register, and when a value of 0 is written to the register, the UCD9080 is restarted and the rails are resequenced.

Note that in order to respond to this  $l^2C$  request properly, there is a 50- $\mu$ s delay before the system is restarted, so that the  $l^2C$  ACK can take place.

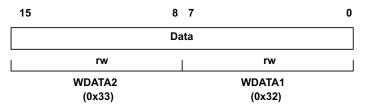

#### WADDR and WDATA

In order to update the configuration on the UCD9080, four registers are provided: WADDR2 (address bits 8–15), WADDR1 (address bits 0–7), WDATA2 (data bits 8–15), and WDATA1 (data bits 0–7). WADDR2 and WADDR1 specify the 16-bit memory address and WDATA2 and WDATA1 specify the 16-bit data written to or read from that memory address.

The format for the WADDR register is as follows:

| 15 |         | 8 7     | 0 |

|----|---------|---------|---|

|    |         | Address |   |

|    | rw-0x00 | rw-0x00 | ) |

|    | WADDR2  | WADDR   | 1 |

|    | (0x31)  | (0x30)  |   |

To set the address of the memory that will be accessed, write the LSB of the address to the WADDR1 register and the MSB of the address to the WADDR2 register. For example, to write the address 0x1234 to the device, set WADDR1 = 0x34 and WADDR2 = 0x12. Note that because these addresses support the auto-increment feature, the user can perform a single 16-bit write to WADDR1 to write the entire address.

The format for the WDATA register is as follows:

To set the value of the data that will be written, write the LSB of the data to the WDATA1 register and the MSB of the data to the WDATA2 register. For example, to write the data 0xBEEF to the device, set WDATA1 = 0xEF and WDATA2 = 0xBE. Note that because these addresses support the auto-increment feature, the user can perform a single 16-bit write to WDATA1 to write the entire data. To read the value of the data at the specified address, read the LSB from WDATA1 and the MSB from WDATA2.

These registers are used for updating the UCD9080 configuration as explained in the *Configuring the UDC9080* section.

### CONFIGURING THE UCD9080

The UCD9080 has many different configurable parameters, such as sequencing policies, shutdown policies and dependency masks. The UCD9080 can configure all of its parameters via the I<sup>2</sup>C interface while the device is operational. Sequencing, shutdown, and rail monitoring are not performed during device configuration time.

#### NOTE:

During runtime, if the UCD9080 is configured, there is a delay in voltage monitoring while the new configuration parameters are applied to the device.

To configure the UCD9080, a large block of configuration information is sent to the device via the  $I^2C$  interface. This block is 512 bytes and contains all the configuration information that the device requires for any function of the UCD9080.

This 512-byte block of configuration information is sent to the device in multiple segments. The segment size can range from 2 to 32 bytes at one time, and must be a power of 2 bytes. That is, a master can send 256 2-byte segments or 32 16-byte segments, and so on. All the segments must be sent back-to-back in the proper sequence, and this operation must be completed by sending the last segment so that the last byte of the 512-byte block is written. If this is not done, the UCD9080 is in an unknown state and does not function as designed.

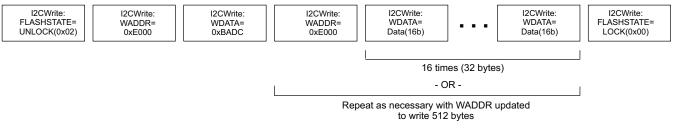

The process for sending the configuration information to the UCD9080 is as shown in Figure 11:

Figure 11. Configuration Information

As shown in Figure 11, the process for updating the configuration of the UCD9080 is as follows:

- 1. Unlock flash memory by writing the FLASHLOCK register with a value of 0x02.

- 2. Write the address of the configuration section of memory (WADDR =  $0 \times E000$ ).

- 3. Write the constant 0xBADC to update memory (WDATA = 0xBADC).

- 4. Write the address of the configuration section of memory again (WADDR =  $0 \times E000$ ).

- 5. Write the data (WDATA = <varies>). Repeat steps 4 and 5 as necessary, depending on the data segment size used, to write 512 bytes. Increment the address as necessary.

- 6. Lock flash memory after the last byte of the last segment is written by writing the FLASHLOCK register with a value of 0x00.

At the conclusion of this process, the configuration of the UCD9080 is updated with the configuration changes, as represented by the values from the data segments. The UCD9080 can then be reset by writing the RESTART register with a value of 0. The new sequencer configuration then starts.

The memory map for the 512-byte configuration segment is defined in the *Configuration Parameters Detail* section.

#### User Data

User data (128 bytes) can be stored in the UCD9080 user-data area at memory location 0x1080 to 0x10FF. Access to the user-data area occurs by following the procedure outlined in the *Configuring the UCD9080* section.

#### **Configuration Parameters Memory Map**

Table 2 shows the 512-byte configuration parameters memory map. User-configurable bytes in bold are described in the *Configuration Parameters Detail* section; adjacent groups of user-configurable bytes are distinguished in the table by alternating use of italics. **Other bytes must remain exactly as shown in Table 2**.

| ADDRESS | +0   | +1   | +2   | +3   | +4   | +5   | +6   | +7   |

|---------|------|------|------|------|------|------|------|------|

| 0xE000  | 0x00 |

| 0xE008  | 0x00 |

| 0xE010  | 0x00 |

| 0xE018  | 0x00 |

| 0xE020  | 0x00 |

| 0xE028  | 0x00 |

| 0xE030  | 0x00 |

| 0xE038  | 0x00 |

| 0xE040  | 0x00 |

| 0xE048  | 0xFF | 0xFF | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 |

| 0xE050  | 0x00 |

| 0xE058  | 0xFF | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0xC0 | 0x02 |

| 0xE060  | 0x00 | 0x00 | 0x00 | 0x0F | 0x00 | 0x02 | 0x00 | 0x02 |

| 0xE068  | 0xFF | 0x0F | 0x00 | 0x50 | 0x00 | 0x00 | 0x00 | 0x00 |

| 0xE070  | 0x00 | 0x00 | 0xC0 | 0x20 | 0x00 | 0x00 | 0x00 | 0x00 |

| 0xE078  | 0x00 | 0x00 | 0x00 | 0x00 | 0x00 | 0xA8 | 0xDC | 0xBA |

| 0xE080  | 0x50 | 0x51 | 0x52 | 0x53 | 0x54 | 0x55 | 0x56 | 0x57 |

| 0xE088  | 0x00 | 0x49 | 0x4A | 0x4B | 0x01 | 0x00 | 0x01 | 0x04 |

| 0xE090  | 0x01 | 0x04 | 0x05 | 0x06 | 0x00 | 0x00 | 0x00 | 0x00 |

| 0xE098  | 0x05 | 0xE0 | 0x05 | 0xA0 | 0x32 | 0xE0 | 0x33 | 0xE0 |

| 0xE0A0  | 0x33 | 0xE0 | 0x35 | 0xE0 | 0x35 | 0xE0 | 0x00 | 0x00 |

| 0xE0A8  | 0x00 |

| 0xE0B0  | 0xFF | 0x7F | 0xFF | 0x7F | 0xFF | 0x7F | 0xFF | 0x7F |

| 0xE0B8  | 0xFF | 0x7F | 0xFF | 0x7F | 0xFF | 0x7F | 0xFF | 0x7F |

| 0xE0C0  | 0x00 |

| 0xE0C8  | 0x00 |

| 0xE0D0  | 0x00 |

| 0xE0D8  | 0x00 |

| 0xE0E0  | 0x00 |

#### **Table 2. Configuration Parameters Memory Map**

Table 2. Configuration Parameters Memory Map (continued)

| ADDRESS | +0   | +1   | +2   | +3   | +4   | +5   | +6   | +7   |

|---------|------|------|------|------|------|------|------|------|

| 0xE0E8  | 0x00 |

| 0xE0F0  | 0x00 |

| 0xE0F8  | 0x00 |

| 0xE100  | 0x7F | 0x00 | 0x01 | 0x00 | 0x02 | 0x00 | 0x04 | 0x00 |

| 0xE108  | 0x08 | 0x00 | 0x10 | 0x00 | 0x20 | 0x00 | 0x40 | 0x00 |

| 0xE110  | 0x00 |

| 0xE118  | 0x00 |

| 0xE120  | 0x00 | 0x04 | 0x00 | 0x04 | 0x00 | 0x04 | 0x00 | 0x04 |

| 0xE128  | 0x00 | 0x04 | 0x00 | 0x04 | 0x00 | 0x04 | 0x00 | 0x04 |

| 0xE130  | 0xA0 | 0x0F | 0xA0 | 0x0F | 0xA0 | 0x0F | 0xA0 | 0x0F |

| 0xE138  | 0xA0 | 0x0F | 0xA0 | 0x0F | 0xA0 | 0x0F | 0xA0 | 0x0F |

| 0xE140  | 0x10 | 0x00 | 0x10 | 0x00 | 0x10 | 0x00 | 0x10 | 0x00 |

| 0xE148  | 0x10 | 0x00 | 0x10 | 0x00 | 0x10 | 0x00 | 0x10 | 0x00 |

| 0xE150  | 0xFF | 0xC0 | 0xFF | 0xC1 | 0xFF | 0xC2 | 0xFF | 0xC3 |

| 0xE158  | 0xFF | 0xC4 | 0xFF | 0xC5 | 0xFF | 0xC6 | 0xFF | 0xC7 |

| 0xE160  | 0x00 | 0x00 | 0x00 | 0xC0 | 0x00 | 0xC0 | 0x00 | 0xC0 |

| 0xE168  | 0x04 | 0x20 | 0x08 | 0x20 | 0x04 | 0x18 | 0x02 | 0x18 |

| 0xE170  | 0x08 | 0x18 | 0x10 | 0x18 | 0x20 | 0x18 | 0x10 | 0x20 |

| 0xE178  | 0x00 | 0x20 | 0x20 | 0x20 | 0x40 | 0x20 | 0x80 | 0x20 |

| 0xE180  | 0x00 | 0x00 | 0x00 | 0x04 | 0x94 | 0x02 | 0xF2 | 0x08 |

| 0xE188  | 0x10 | 0x03 | 0x05 | 0xC0 | 0x40 | 0x00 | 0xFF | 0x08 |

| 0xE190  | 0x05 | 0x00 |

| 0xE198  | 0x00 |

| 0xE1A0  | 0x00 |

| 0xE1A8  | 0x00 |

| 0xE1B0  | 0x00 |

| 0xE1B8  | 0x00 |

| 0xE1C0  | 0x00 |

| 0xE1C8  | 0x00 |

| 0xE1D0  | 0x00 |

| 0xE1D8  | 0x00 |

| 0xE1E0  | 0x00 |

| 0xE1E8  | 0x00 |

| 0xE1F0  | 0x00 |

| 0xE1F8  | 0x00 |

### **CONFIGURATION PARAMETERS DETAIL**

The following sections detail the format and meaning of the configuration parameters from the Configuration Parameters Memory Map, Table 2.

#### SequenceEventParameters

The SequenceEventParameters field in the configuration parameters specifies the rail identification, monitoring status, and sequencing options for each rail. The address map for these registers is as follows:

| ADDRESS | SIZE | DEFAULT VALUE | DESCRIPTION                                                      |

|---------|------|---------------|------------------------------------------------------------------|

| 0xE080  | 1    | 0x50          | Rail 1 identification, monitoring status and sequencing options  |

| 0xE081  | 1    | 0x51          | Rail 2 identification, monitoring status, and sequencing options |

| 0xE082  | 1    | 0x52          | Rail 3 identification, monitoring status, and sequencing options |

| 0xE083  | 1    | 0x53          | Rail 4 identification, monitoring status, and sequencing options |

| 0xE084  | 1    | 0x54          | Rail 5 identification, monitoring status, and sequencing options |

| 0xE085  | 1    | 0x55          | Rail 6 identification, monitoring status, and sequencing options |

| 0xE086  | 1    | 0x56          | Rail 7 identification, monitoring status, and sequencing options |

| 0xE087  | 1    | 0x57          | Rail 8 identification, monitoring status, and sequencing options |

| 0xE088  | 1    | 0x00          | GPO1 identification, sequencing options                          |

| 0xE089  | 1    | 0x49          | GPO2 identification, sequencing options                          |

| 0xE08A  | 1    | 0x4A          | GPO3 identification, sequencing options                          |

| 0xE08B  | 1    | 0x4B          | GPO4 identification, sequencing options                          |

The format of each register is as follows:

| 7   | 6    | 5 | 4   | 3 | 2    | 1    | 0 |

|-----|------|---|-----|---|------|------|---|

| ENA | ABLE | 0 | MON |   | RAIL | /GPO |   |

RAIL

Rail #(n) – 1, RAIL = 0 through 7

| GPO |               |            |            |

|-----|---------------|------------|------------|

|     | GPO #(n) + 7, | GPO = 8, 9 | , 0xA, 0xB |

| MON Meaning | g |

|-------------|---|

|-------------|---|

0 Do not monitor rail status (for event sequencing of GPOs) 1 Monitor rail status

#### ENABLE 00

| Ξ | Meaning              |

|---|----------------------|

|   | Sequence is disabled |

- 01 Sequence is triggered after delay after sequence event

- 10 Sequence is triggered after parent rail achieves voltage level

- 11 Sequence is triggered after delay after parent rail achieves voltage regulation

#### SequenceEventLink

The SequenceEventLink field allows a parent rail (monitored input) to be specified for each ENx and GPOx output. The RESEQ bit (sequence after shutdown) allows an enable or GPO to be marked to sequence the system (as defined by the current sequencer configuration) after it has been shut down. The address map for these registers is as follows:

| ADDRESS | SIZE | DEFAULT VALUE | DESCRIPTION                                            |

|---------|------|---------------|--------------------------------------------------------|

| 0xE08C  | 1    | 0x01          | Rail 1 parent rail identifier and resequence indicator |

| 0xE08D  | 1    | 0x00          | Rail 2 parent rail identifier and resequence indicator |

| 0xE08E  | 1    | 0x01          | Rail 3 parent rail identifier and resequence indicator |

| 0xE08F  | 1    | 0x04          | Rail 4 parent rail identifier and resequence indicator |

| 0xE090  | 1    | 0x01          | Rail 5 parent rail identifier and resequence indicator |

| 0xE091  | 1    | 0x04          | Rail 6 parent rail identifier and resequence indicator |

| 0xE092  | 1    | 0x05          | Rail 7 parent rail identifier and resequence indicator |

| 0xE093  | 1    | 0x06          | Rail 8 parent rail identifier and resequence indicator |

| 0xE094  | 1    | 0x00          | GPO1 parent rail identifier and resequence indicator   |

| 0xE095  | 1    | 0x00          | GPO2 parent rail identifier and resequence indicator   |

| 0xE096  | 1    | 0x00          | GPO3 parent rail identifier and resequence indicator   |

| 0xE097  | 1    | 0x00          | GPO4 parent rail identifier and resequence indicator   |

The format of each register is as follows:

| 7 | 6     | 5 | 4 | 3 | 2      | 1    | 0 |

|---|-------|---|---|---|--------|------|---|

| 0 | RESEQ | 0 | 0 |   | PARENT | RAIL |   |

| RESEQ | Meaning                        |

|-------|--------------------------------|

| 0     | Do not sequence after shutdown |

| Do not sequence after shutdown. |

|---------------------------------|

| Conversion offer also tales as  |

Sequence after shutdown.

#### PARENTRAIL Meaning

| 0x0000 | Sequence is dependent on RAIL1 achieving the specified event. |

|--------|---------------------------------------------------------------|

| 0x0001 | Sequence is dependent on RAIL2 achieving the specified event. |

| 0x0010 | Sequence is dependent on RAIL3 achieving the specified event. |

| 0x0011 | Sequence is dependent on RAIL4 achieving the specified event. |

| 0x0100 | Sequence is dependent on RAIL5 achieving the specified event. |

| 0x0101 | Sequence is dependent on RAIL6 achieving the specified event. |

| 0x0110 | Sequence is dependent on RAIL7 achieving the specified event. |

| 0x0111 | Sequence is dependent on RAIL8 achieving the specified event. |

# UCD9080

www.ti.com

### SequenceEventData

The SequenceEventData field in the configuration parameters specifies the rail and GPO sequencing and shutdown parameters. The address map for these registers is as follows:

| ADDRESS | SIZE | DEFAULT VALUE | DESCRIPTION                               |

|---------|------|---------------|-------------------------------------------|

| 0xE098  | 2    | 0xE005        | Rail 1 sequencing and shutdown parameters |

| 0xE09A  | 2    | 0xA005        | Rail 2 sequencing and shutdown parameters |

| 0xE09C  | 2    | 0xE032        | Rail 3 sequencing and shutdown parameters |

| 0xE09E  | 2    | 0xE033        | Rail 4 sequencing and shutdown parameters |

| 0xE0A0  | 2    | 0xE033        | Rail 5 sequencing and shutdown parameters |

| 0xE0A2  | 2    | 0xE035        | Rail 6 sequencing and shutdown parameters |

| 0xE0A4  | 2    | 0xE035        | Rail 7 sequencing and shutdown parameters |

| 0xE0A6  | 2    | 0x0000        | Rail 8 sequencing and shutdown parameters |

| 0xE0A8  | 2    | 0x0000        | GPO1 sequencing and shutdown parameters   |

| 0xE0AA  | 2    | 0x0000        | GPO2 sequencing and shutdown parameters   |

| 0xE0AC  | 2    | 0x0000        | GPO3 sequencing and shutdown parameters   |

| 0xE0AE  | 2    | 0x0000        | GPO4 sequencing and shutdown parameters   |

The format for each register is as follows. The value in the ENABLE field of the SequenceEventParameters register determines the measure represented by the value in the RAILDATA field of the SequenceEventData register.

| 15 | 14     | 13         | 12   | 11                 | 10 | 9 | 8   | 7        | 6      | 5       | 4   | 3           | 2          | 1    | 0          |

|----|--------|------------|------|--------------------|----|---|-----|----------|--------|---------|-----|-------------|------------|------|------------|

| s  | EQPARA | ۹M         | 0    |                    |    |   |     | F        | RAILDA | TA      |     |             |            |      |            |

|    | SE     | QPARA      | M Me | eaning             |    |   | (5) | Eequence |        | -       | rc) | RAILDA      | TA Mea     | ning |            |

|    |        | 000        |      | og only            |    |   | (00 | quence   |        | aramete | ,   | "           |            | ,    |            |

|    |        | 001        |      | equence            |    |   |     |          | 01     |         |     | Delay (in i |            |      |            |

|    |        | 010        |      | eserved            |    |   |     |          | 10     |         |     |             |            |      | 024 volts) |

|    |        | 011<br>100 |      | eserved<br>eserved |    |   |     |          | 11     |         | l   | Delay (in i | units of i | ms)  |            |

101

110

111

Retry 1 times Retry 0 times

Reserved

#### DependencyMasks

The DependencyMasks field in the configuration parameters defines the rail dependency masks used for rail and GPO shutdown. This mask represents the set of other rails and GPOs that should be shut down when this rail shuts down. Note that because only rails are monitored, the table only has entries for the shutdown of rails. In the dependency mask itself, there are bits that allow for GPO shutdown.

| ADDRESS | SIZE | DEFAULT VALUE | DESCRIPTION                |

|---------|------|---------------|----------------------------|

| 0xE100  | 2    | 0x007F        | Dependency mask for rail 1 |

| 0xE102  | 2    | 0x0001        | Dependency mask for rail 2 |

| 0xE104  | 2    | 0x0002        | Dependency mask for rail 3 |

| 0xE106  | 2    | 0x0004        | Dependency mask for rail 4 |

| 0xE108  | 2    | 0x0008        | Dependency mask for rail 5 |

| 0xE10A  | 2    | 0x0010        | Dependency mask for rail 6 |

| 0xE10C  | 2    | 0x0020        | Dependency mask for rail 7 |

| 0xE10E  | 2    | 0x0040        | Dependency mask for rail 8 |

The address map for these registers is as follows:

The format for each register is as follows:

| 15 | 14 | 13 | 12 | 11   | 10   | 9    | 8    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----|----|----|----|------|------|------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0  | 0  | 0  | 0  | GPO4 | GPO3 | GPO2 | GPO1 | RAIL8 | RAIL7 | RAIL6 | RAIL5 | RAIL4 | RAIL3 | RAIL2 | RAIL1 |

**RAILn or GPOn**

1

0

Meaning

Shutdown of this rail does not shut down RAILn or GPOn. Shutdown of this rail shuts down RAILn or GPOn.

#### **UnderVoltageThresholds**

The UnderVoltageThresholds field in the configuration parameters specifies each rail undervoltage threshold that is used when monitoring this rail. The address map for these registers is as follows:

| ADDRESS | SIZE | DEFAULT VALUE | DESCRIPTION                       |

|---------|------|---------------|-----------------------------------|

| 0xE110  | 2    | 0x0000        | Undervoltage threshold for rail 8 |

| 0xE112  | 2    | 0x0000        | Undervoltage threshold for rail 7 |

| 0xE114  | 2    | 0x0000        | Undervoltage threshold for rail 6 |

| 0xE116  | 2    | 0x0000        | Undervoltage threshold for rail 5 |

| 0xE118  | 2    | 0x0000        | Undervoltage threshold for rail 4 |

| 0xE11A  | 2    | 0x0000        | Undervoltage threshold for rail 3 |

| 0xE11C  | 2    | 0x0000        | Undervoltage threshold for rail 2 |

| 0xE11E  | 2    | 0x0000        | Undervoltage threshold for rail 1 |

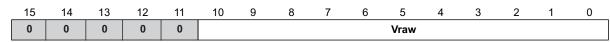

The format for each register is as follows:

The voltage conversion is dependent upon the configured voltage reference, and the pullup/pulldown resistors used on the board for each rail. The voltage reference is selected as either 2.5 V (internal) or V<sub>CC</sub> (external). The formula to convert the desired rail UnderVoltageThreshold to Vraw follows:

Without external rail voltage divider:

$$Vraw = \frac{1024 \times V_{RAILUV}}{V_{REF}}$$

(3)

With external rail voltage divider:

$$Vraw = \frac{1024 \times V_{RAILUV}}{V_{REF}} \times \frac{R_{PULLDOWN}}{R_{PULLDOWN} + R_{PULLUP}}$$

#### **OverVoltageThresholds**

The OverVoltageThreholds field in the configuration parameters specifies each rail overvoltage threshold that is used when monitoring this rail. The address map for these registers is as follows:

| ADDRESS | SIZE | DEFAULT VALUE | DESCRIPTION                      |

|---------|------|---------------|----------------------------------|

| 0xE120  | 2    | 0x0400        | Overvoltage threshold for rail 8 |

| 0xE122  | 2    | 0x0400        | Overvoltage threshold for rail 7 |

| 0xE124  | 2    | 0x0400        | Overvoltage threshold for rail 6 |

| 0xE126  | 2    | 0x0400        | Overvoltage threshold for rail 5 |

| 0xE128  | 2    | 0x0400        | Overvoltage threshold for rail 4 |

| 0xE12A  | 2    | 0x0400        | Overvoltage threshold for rail 3 |

| 0xE12C  | 2    | 0x0400        | Overvoltage threshold for rail 2 |

| 0xE12E  | 2    | 0x0400        | Overvoltage threshold for rail 1 |

The format for each register is as follows:

| 15 | 14    | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5    | 4 | 3 | 2 | 1 | 0 |   |

|----|-------|----|----|----|----|---|---|---|---|------|---|---|---|---|---|---|

| 0  | 0     | 0  | 0  | 0  |    |   |   |   |   | Vraw |   |   |   |   |   |   |

|    |       |    |    |    |    |   |   |   |   |      |   |   |   |   |   | 1 |

|    | conve |    |    |    |    |   |   |   |   |      |   |   |   |   |   |   |

Copyright © 2006–2008, Texas Instruments Incorporated

ΤI S used on the board for each rail. The voltage reference is selected as either 2.5 V (internal) or V<sub>CC</sub> (external). The formula to convert the desired rail OverVoltageThreshold to Vraw follows:

Without external rail voltage divider:

$$Vraw = \frac{1024 \times V_{RAILOV}}{V_{REF}}$$

(5)

With external voltage divider:

$$Vraw = \frac{1024 \times V_{RAILOV}}{V_{REF}} \times \frac{R_{PULLDOWN}}{R_{PULLDOWN} + R_{PULLUP}}$$

(6)

#### RampTime

26

The RampTime field in the configuration parameters specifies the maximum amount of time for each rail to achieve regulation. The address map for these registers is as follows:

|     | •    |     |    |        | •                                          |                                        |                                      |          |          |        |         |   |   |   |   |  |  |

|-----|------|-----|----|--------|--------------------------------------------|----------------------------------------|--------------------------------------|----------|----------|--------|---------|---|---|---|---|--|--|

| ADD | RESS | SIZ | ZE | DEFAUL | T VALUE                                    |                                        |                                      |          |          | DESC   | RIPTION | I |   |   |   |  |  |