#### 查询ICS85222AMLF供应商

#### 专业PCB打样工厂,24小时加急出货

Integrated Circuit Systems, Inc.

## ICS85222

**DUAL LVCMOS / LVTTL-TO-**DIFFERENTIAL LVHSTL TRANSLATOR

#### GENERAL DESCRIPTION

The ICS85222 is a Dual LVCMOS / LVTTL-to-Differential LVHSTL Translator and a member of the HiPerClocks™ family of High Performance Clock Solutions from ICS. The ICS85222 has two single ended clock inputs. The single ended clock

input accepts LVCMOS or LVTTL input levels and translates them to LVHSTL levels. The small outline 8-pin SOIC package makes this device ideal for applications where space, high performance and low power are important. For optimum performance, both output pairs need to be terminated, even if one output pair is unused.

#### **F**EATURES

- 2 differential LVHSTL outputs

- Selectable CLK0, CLK1 LVCMOS clock inputs

- CLK0 and CLK1 can accept the following input levels: LVCMOS or LVTTL

- · Maximum output frequency: 350MHz

- Part-to-part skew: 350ps (maximum)

- Propagation delay: 1.3ns (maximum)

- V<sub>OH</sub>: 1.2V (maximum)

- 3.3V and 2.5V operating supply

- 0°C to 70°C ambient operating temperature

- Industrial temperature information available upon request

- Lead-Free package fully RoHS compliant

## **BLOCK DIAGRAM**

### PIN ASSIGNMENT

#### ICS85222

8-Lead SOIC 3.90mm x 4.92mm x 1.37mm body package M Package Top View

# DUAL LVCMOS / LVTTL-TO-DIFFERENTIAL LVHSTL TRANSLATOR

TABLE 1. PIN DESCRIPTIONS

| Number | Name            | Туре   |                                                        | Description                                        |

|--------|-----------------|--------|--------------------------------------------------------|----------------------------------------------------|

| 1, 2   | Q0, nQ0         | Output |                                                        | Differential output pair. LVHSTL interface levels. |

| 3, 4   | Q1, nQ1         | Output | out Differential output pair. LVHSTL interface levels. |                                                    |

| 5      | GND             | Power  |                                                        | Power supply ground.                               |

| 6      | CLK1            | Input  | Pulldown                                               | LVCMOS / LVTTL clock input.                        |

| 7      | CLK0            | Input  | Pulldown                                               | LVCMOS / LVTTL clock input.                        |

| 8      | V <sub>DD</sub> | Power  |                                                        | Positive supply pin.                               |

NOTE: Pulldown refers to internal input resistors. See Table 2, Pin Characteristics, for typical values.

NOTE: Unused output pairs must be terminated. Refer to Application Information section for a schematic layout.

#### TABLE 2. PIN CHARACTERISTICS

| Symbol                | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------------|-------------------------|-----------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance       |                 |         | 4       |         | pF    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor   |                 |         | 51      |         | kΩ    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor |                 |         | 51      |         | kΩ    |

# DUAL LVCMOS / LVTTL-TO-DIFFERENTIAL LVHSTL TRANSLATOR

#### ABSOLUTE MAXIMUM RATINGS

Supply Voltage, V<sub>DD</sub> 4.6V

Inputs,  $V_{I}$  -0.5V to  $V_{DD}$  + 0.5V

Outputs, I<sub>O</sub>

Continuous Current 50mA Surge Current 100mA

Package Thermal Impedance,  $\theta_{_{JA}} - 112.7^{\circ}\text{C/W}$  (0 lfpm)

Storage Temperature, T<sub>STG</sub> -65°C to 150°C

NOTE: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics* or *AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

Table 3A. Power Supply DC Characteristics,  $V_{DD} = 3.3V \pm 5\%$ ,  $V_{DD} = 2.5V \pm 5\%$ ,  $T_{A} = 0^{\circ}C$  to  $70^{\circ}C$

| Symbol          | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|-------------------------|-----------------|---------|---------|---------|-------|

| V <sub>DD</sub> | Positive Supply Voltage |                 | 3.135   | 3.3     | 3.465   | V     |

| V <sub>DD</sub> | Positive Supply Voltage |                 | 2.375   | 2.5     | 2.625   | V     |

| I <sub>DD</sub> | Power Supply Current    |                 |         |         | 45      | mA    |

Table 3B. LVCMOS / LVTTL DC Characteristics,  $V_{DD} = 3.3V \pm 5\%$ ,  $V_{DD} = 2.5V \pm 5\%$ , Ta = 0°C to 70°C

| Symbol          | Parameter          |            | Test Conditions                                           | Minimum | Typical | Maximum               | Units |

|-----------------|--------------------|------------|-----------------------------------------------------------|---------|---------|-----------------------|-------|

| V <sub>IH</sub> | Input High Voltage | CLK0, CLK1 |                                                           | 2       |         | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub> | Input Low Voltage  | CLK0, CLK1 |                                                           | -0.3    |         | 1.3                   | V     |

| I <sub>IH</sub> | Input High Current | CLK0, CLK1 | $V_{DD} = V_{IN} = 3.465V,$<br>$V_{DD} = V_{IN} = 2.625V$ |         |         | 150                   | μΑ    |

| I               | Input Low Current  | CLK0, CLK1 | $V_{DD} = V_{IN} = 3.465V,$<br>$V_{DD} = V_{IN} = 2.625V$ | -5      |         |                       | μΑ    |

Table 3C. LVHSTL DC Characteristics,  $V_{DD} = 3.3V \pm 5\%$ ,  $V_{DD} = 2.5V \pm 5\%$ , Ta = 0°C to 70°C

| Symbol             | Parameter                                  | Test Conditions         | Minimum | Typical | Maximum | Units |

|--------------------|--------------------------------------------|-------------------------|---------|---------|---------|-------|

| V <sub>OH</sub>    | Output High Voltage; NOTE 1                |                         | 1       |         | 1.2     | V     |

| V                  | V <sub>OL</sub> Output Low Voltage; NOTE 1 | $V_{DD} = 3.3V \pm 5\%$ | 0       |         | 0.4     | V     |

| V <sub>OL</sub>    |                                            | $V_{DD} = 2.5V \pm 5\%$ | 0       |         | 0.55    | V     |

| V                  | Dook to Dook Output Voltage Swing          | $V_{DD} = 3.3V \pm 5\%$ | 0.6     |         | 1.2     | V     |

| V <sub>SWING</sub> | Peak-to-Peak Output Voltage Swing          | $V_{DD} = 2.5V \pm 5\%$ | 0.45    |         | 1.2     | V     |

NOTE 1: Outputs terminated with  $50\Omega$  to GND.

# DUAL LVCMOS / LVTTL-TO-DIFFERENTIAL LVHSTL TRANSLATOR

Table 4A. AC Characteristics,  $V_{DD} = 3.3V \pm 5\%$ , Ta = 0°C to 70°C

| Symbol           | Parameter                    | Test Conditions         | Minimum | Typical | Maximum | Units |

|------------------|------------------------------|-------------------------|---------|---------|---------|-------|

| f <sub>MAX</sub> | Output Frequency             |                         |         |         | 350     | MHz   |

| t <sub>PD</sub>  | Propagation Delay; NOTE 1    | $f \leq 350 \text{MHz}$ | 750     | 950     | 1150    | ps    |

| tsk(pp)          | Part-to-Part Skew; NOTE 2, 3 |                         |         |         | 350     | ps    |

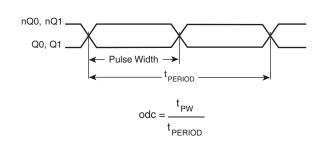

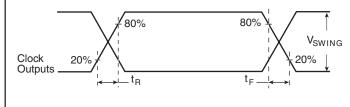

| t <sub>R</sub>   | Output Rise Time             | 20% to 80%              | 150     |         | 800     | ps    |

| t <sub>F</sub>   | Output Fall Time             | 20% to 80%              | 150     |         | 800     | ps    |

|                  |                              | <i>f</i> ≤ 150MHz       | 48      |         | 52      | %     |

| odc              | Output Duty Cycle            | 150 < <i>f</i> ≤ 250MHz | 47      |         | 53      | %     |

|                  |                              | 250 < <i>f</i> ≤ 350MHz | 45      |         | 55      | %     |

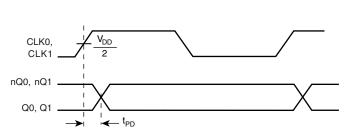

NOTE 1: Measured from  $V_{DD}/2$  of the input to the differential output crossing point.

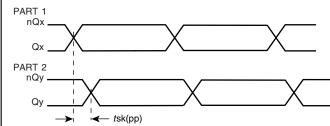

NOTE 2: Defined as skew between outputs on different devices operating at the same supply voltages and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at the differential cross points.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65.

Table 4B. AC Characteristics,  $V_{DD} = 2.5V \pm 5\%$ , Ta = 0°C to 70°C

| Symbol           | Parameter                    | Test Conditions         | Minimum | Typical | Maximum | Units |

|------------------|------------------------------|-------------------------|---------|---------|---------|-------|

| f <sub>MAX</sub> | Output Frequency             |                         |         |         | 350     | MHz   |

| t <sub>PD</sub>  | Propagation Delay; NOTE 1    | <i>f</i> ≤ 350MHz       | 850     | 1075    | 1300    | ps    |

| tsk(pp)          | Part-to-Part Skew; NOTE 2, 3 |                         |         |         | 450     | ps    |

| t <sub>R</sub>   | Output Rise Time             | 20% to 80%              | 150     |         | 800     | ps    |

| t <sub>F</sub>   | Output Fall Time             | 20% to 80%              | 150     |         | 800     | ps    |

| ada              | Output Duty Cycle            | <i>f</i> ≤ 150MHz       | 45      |         | 55      | %     |

| odc              | Output Duty Cycle            | 150 < <i>f</i> ≤ 350MHz | 40      |         | 60      | %     |

NOTE 1: Measured from  $V_{DD}/2$  of the input to the differential output crossing point. NOTE 2: Defined as skew between outputs on different devices operating at the same supply voltages and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at the differential cross points.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65.

DUAL LVCMOS / LVTTL-TO-DIFFERENTIAL LVHSTL TRANSLATOR

# PARAMETER MEASUREMENT INFORMATION

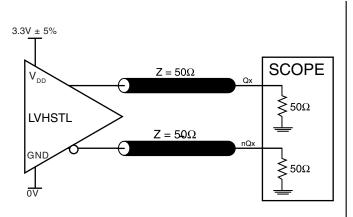

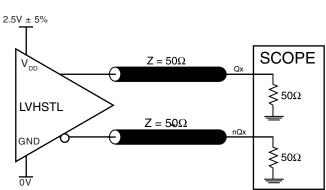

#### 3.3V CORE/3.3V OUTPUT LOAD AC TEST CIRCUIT

#### 2.5V CORE/2.5V OUTPUT LOAD AC TEST CIRCUIT

#### PROPAGATION DELAY

#### PART-TO-PART SKEW

#### OUTPUT DUTY CYCLE/PULSE WIDTH/PERIOD

**OUTPUT RISE/FALL TIME**

## **APPLICATION INFORMATION**

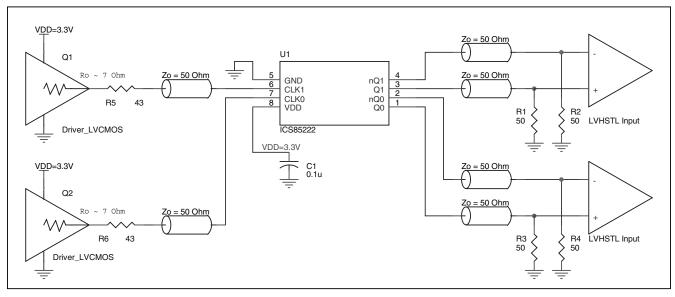

#### SCHEMATIC EXAMPLE

Figure 1 shows a schematic example of ICS85222. In this example, the inputs are driven by  $7\Omega$  output LVCMOS drivers with series terminations. The decoupling capacitors should be physically located near the power pin. For ICS85222, the unused output need to be terminated.

FIGURE 1. ICS85222 LVHSTL BUFFER SCHEMATIC EXAMPLE

# DUAL LVCMOS / LVTTL-TO-DIFFERENTIAL LVHSTL TRANSLATOR

#### POWER CONSIDERATIONS

This section provides information on power dissipation and junction temperature for the ICS85222. Equations and example calculations are also provided.

#### 1. Power Dissipation.

The total power dissipation for the ICS85222 is the sum of the core power plus the power dissipated in the load(s). The following is the power dissipation for  $V_{DD} = 3.3V + 5\% = 3.465V$ , which gives worst case results.

**NOTE:** Please refer to Section 3 for details on calculating power dissipated in the load.

- Power (core)<sub>MAX</sub> = V<sub>DD MAX</sub> \* I<sub>DD MAX</sub> = 3.465V \* 45mA = 155.9mW

- Power (outputs)<sub>MAX</sub> = 78.9mW/Loaded Output pair

If all outputs are loaded, the total power is 2 \* 78.9mW = 157.8mW

Total Power MAX (3.465V, with all outputs switching) = 155.9mW + 157.8mW = 313.7mW

#### 2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad and directly affects the reliability of the device. The maximum recommended junction temperature for HiPerClockS $^{TM}$  devices is 125 $^{\circ}$ C.

The equation for Tj is as follows: Tj =  $\theta_{JA}$  \* Pd\_total + T<sub>A</sub>

Tj = Junction Temperature

$\theta_{\text{\tiny JA}}$  = Junction-to-Ambient Thermal Resistance

Pd\_total = Total Device Power Dissipation (example calculation is in Section 1 above)

$T_{\Delta}$  = Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance  $\theta_{\rm JA}$  must be used. Assuming a moderate air flow of 200 linear feet per minute and a multi-layer board, the appropriate value is 103.3°C/W per Table 5 below. Therefore, Tj for an ambient temperature of 70°C with all outputs switching is:

$70^{\circ}\text{C} + 0.314\text{W} * 103.3^{\circ}\text{C/W} = 102.4^{\circ}\text{C}$ . This is well below the limit of 125°C

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow, and the type of board (single layer or multi-layer).

Table 5. Thermal Resistance  $\theta_{\text{JA}}$  for 8-Pin SOIC, Forced Convection

# $\theta_{JA}$ by Velocity (Linear Feet per Minute)

O

200

500

Single-Layer PCB, JEDEC Standard Test Boards

153.3°C/W

128.5°C/W

115.5°C/W

Multi-Layer PCB, JEDEC Standard Test Boards

112.7°C/W

103.3°C/W

97.1°C/W

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

TORRELL STATE OF THE PROPERTY OF THE PROPERTY

# DUAL LVCMOS / LVTTL-TO-DIFFERENTIAL LVHSTL TRANSLATOR

#### 3. Calculations and Equations.

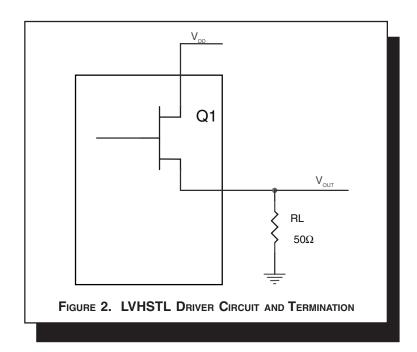

The purpose of this section is to derive the power dissipated into the load.

LVHSTL output driver circuit and termination are shown in Figure 2.

To calculate worst case power dissipation into the load, use the following equations which assume a  $50\Omega$  load.

Pd\_H is power dissipation when the output drives high.

Pd\_L is the power dissipation when the output drives low.

$$\begin{split} & Pd\_H = (V_{OH\_MAX}/R_L) * (V_{DD\_MAX} - V_{OH\_MAX}) \\ & Pd\_L = (V_{OL\_MAX}/R_L) * (V_{DD\_MAX} - V_{OL\_MAX}) \end{split}$$

$$Pd_H = (1.2V/50\Omega) * (3.465V - 1.2V) =$$

**54.4mW**  $Pd_L = (0.4V/50\Omega) * (3.465V - 0.4V) =$ **24.52mW**

Total Power Dissipation per output pair = Pd\_H + Pd\_L = 78.9mW

August com/avadusts/hinavalgaka html

# DUAL LVCMOS / LVTTL-TO-DIFFERENTIAL LVHSTL TRANSLATOR

# RELIABILITY INFORMATION

# Table 6. $\theta_{\text{JA}} \text{vs. Air Flow Table for 8 Lead SOIC}$

# $\boldsymbol{\theta}_{_{JA}}$ by Velocity (Linear Feet per Minute)

|                                              | 0         | 200       | 500       |

|----------------------------------------------|-----------|-----------|-----------|

| Single-Layer PCB, JEDEC Standard Test Boards | 153.3°C/W | 128.5°C/W | 115.5°C/W |

| Multi-Layer PCB, JEDEC Standard Test Boards  | 112.7°C/W | 103.3°C/W | 97.1°C/W  |

NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs.

#### TRANSISTOR COUNT

The transistor count for ICS85222 is: 443

ununu isat sam/ayadusta/hinayaladka html

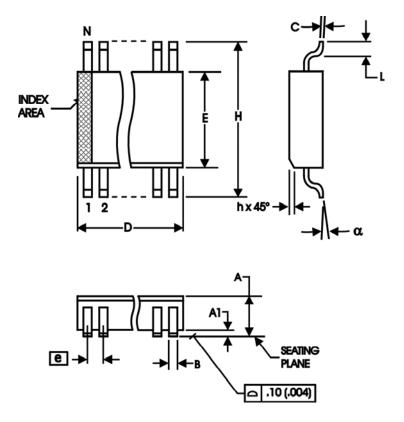

#### PACKAGE OUTLINE - M SUFFIX FOR 8 LEAD SOIC

TABLE 7. PACKAGE DIMENSIONS

| CVMDOL | Millin  | neters  |

|--------|---------|---------|

| SYMBOL | MINIMUM | MAXIMUM |

| N      |         | 8       |

| Α      | 1.35    | 1.75    |

| A1     | 0.10    | 0.25    |

| В      | 0.33    | 0.51    |

| С      | 0.19    | 0.25    |

| D      | 4.80    | 5.00    |

| E      | 3.80    | 4.00    |

| е      | 1.27    | BASIC   |

| Н      | 5.80    | 6.20    |

| h      | 0.25    | 0.50    |

| L      | 0.40    | 1.27    |

| α      | 0°      | 8°      |

Reference Document: JEDEC Publication 95, MS-012

# ICS85222 DUAL LVCMOS / LVTTL-TODIFFERENTIAL LVHSTL TRANSLATOR

#### TABLE 8. ORDERING INFORMATION

| Part/Order Number | Marking  | Package                 | Shipping Package | Temperature |

|-------------------|----------|-------------------------|------------------|-------------|

| ICS85222AM        | 85222AM  | 8 Lead SOIC             | tube             | 0°C to 70°C |

| ICS85222AMT       | 85222AM  | 8 Lead SOIC             | 2500 tape & reel | 0°C to 70°C |

| ICS85222AMLF      | 85222AML | 8 Lead "Lead-Free" SOIC | tube             | 0°C to 70°C |

| ICS85222AMLFT     | 85222AML | 8 Lead "Lead-Free" SOIC | 2500 tape & reel | 0°C to 70°C |

NOTE: Parts that are ordered with an "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

Acceptable and the second seco

# ICS85222 DUAL LVCMOS / LVTTL-TO-DIFFERENTIAL LVHSTL TRANSLATOR

|     | REVISION HISTORY SHEET |              |                                                                                                                                                                                                            |         |  |  |

|-----|------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Rev | Table                  | Page         | Description of Change                                                                                                                                                                                      | Date    |  |  |

| В   | T2<br>T8               | 1<br>2<br>12 | Features section - add Lead-Free bullet. Pin Characteristics table - changed C <sub>IN</sub> 4pF max. to 4pF typical. Ordering Information Table - added Lead-Free part number. Updated data sheet format. | 3/31/05 |  |  |

|     |                        |              |                                                                                                                                                                                                            |         |  |  |