# MOS INTEGRATED CIRCUIT $\mu PD72852$

# IEEE1394a-2000 COMPLIANT 400 Mbps TWO-PORT PHY LSI

The  $\mu$ PD72852 is a two-port physical layer LSI that complies with the IEEE1394a-2000 specifications. The  $\mu$ PD72852 supports transfers of up to 400 Mbps and consumes less power than the  $\mu$ PD72850B. The  $\mu$ PD72852 is suitable for battery systems with an IEEE1394 interface.

#### **FEATURES**

- The two-port physical layer LSI complies with IEEE1394a-2000

- Fully interoperable with IEEE1394 std 1394 Link (FireWire™, i.LINK™)

- Meets Intel<sup>™</sup> Mobile Power Guideline 2000

- Full IEEE1394a-2000 support includes: Suspend/Resume, connection debounce, arbitrated short bus reset, multispeed concatenation, arbitration acceleration, fly-by concatenation

- · Fully compliant with OHCI requirements

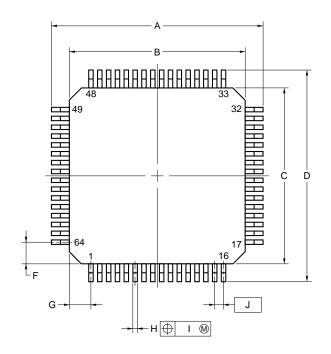

- Small package: 64-pin plastic LQFP

- Super low power: 68 mA (Operating mode)

- : 115 μA (Suspend mode)

- Data rate: 400/200/100 Mbps

- · Supports PHY pinging and remote PHY access packets

- 3.3 V single power supply (if power not supplied via node: 3.0 V single power supply)

- 24.576 MHz crystal clock generation, 393.216 MHz PLL multiplying frequency

- · 64-bit flexible register incorporated in PHY register

- · Electrically isolated Link interface

- Supports LPS/Link-on as part of PHY/Link interface

- External filter capacitors for PLL not required

- Extended Resume signaling for compatibility with legacy DV devices

- · System power management by signaling of node power class information

- Cable power monitor (CPS) is equipped

#### ORDERING INFORMATION

| Part number    | Package                       |  |

|----------------|-------------------------------|--|

| μPD72852GB-8EU | 64-pin plastic LQFP (10 x 10) |  |

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

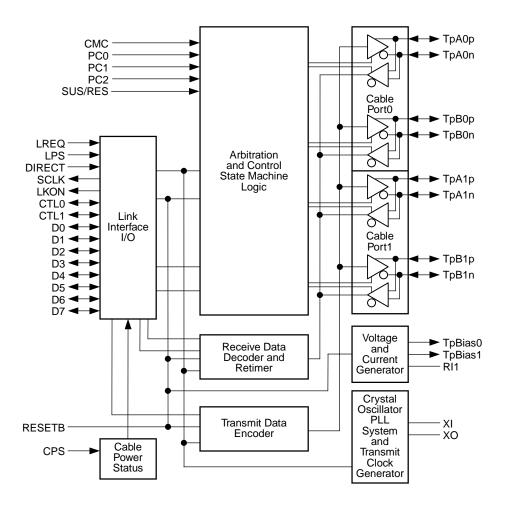

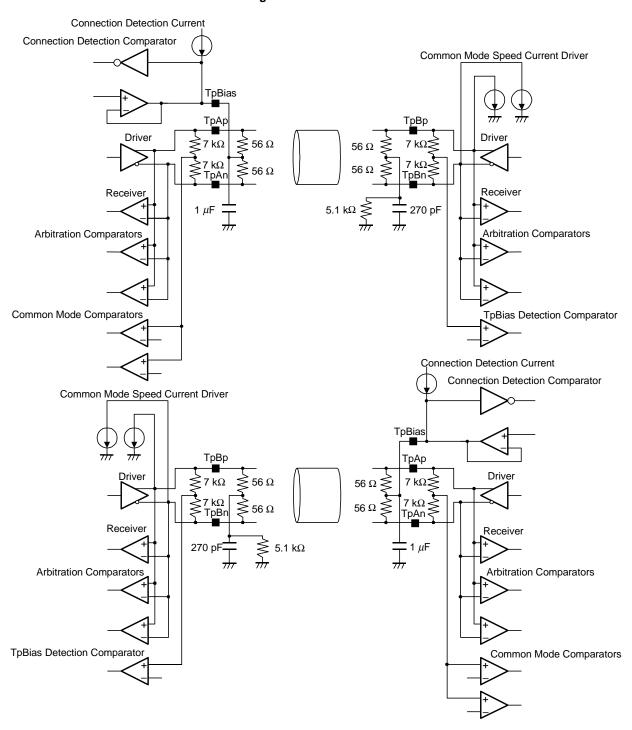

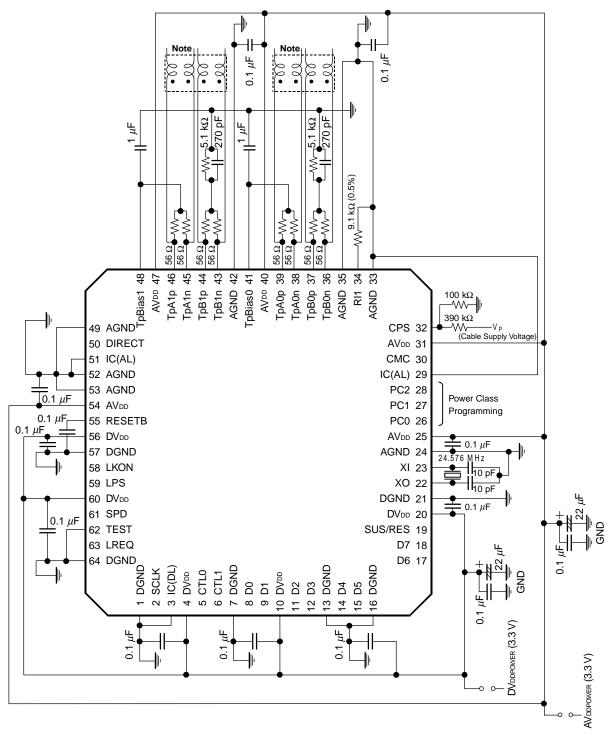

## **BLOCK DIAGRAM**

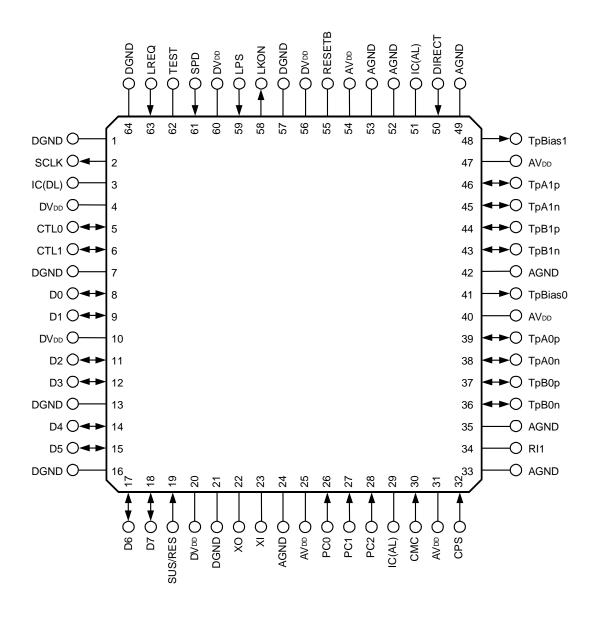

# PIN CONFIGURATION (Top View)

• μPD72852GB-8EU

64-pin plastic LQFP (10 x 10)

Data Sheet S14920EJ3V0DS

#### **PIN NAME**

AGND : Analog GND AVDD : Analog Power

CMC : Configuration Manager Capable

CPS : Cable Power Status

CTL0 : Link Interface Control (bit 0)

CTL1 : Link Interface Control (bit 1)

D0-D7 : Data Input/Output

DGND : Digital GND

DIRECT : PHY/Link Isolation Barrier Control Input

DVDD : Digital VDD

IC(AL) : Internally Connected (Low Clamped)

IC(DL) : Internally Connected (Low Clamped)

LKON : Link-on Signal Output

LPS : Link Power Status Input

LREQ : Link Request Input

PC0-PC2 : Power Class Set Input

RESETB : Power-on Reset Input

RI1 : Reference Power Set, Connect Resistor 1

SCLK : Link Control Output Clock

SPD : Speed Select

SUS/RES : Suspend/Resume Function Select

TEST : Test Pin (Low Clamped)

TpA0n : Port 0 Twisted Pair Cable A Negative Phase I/O : Port 0 Twisted Pair Cable A Positive Phase I/O TpA0p TpA1n : Port 1 Twisted Pair Cable A Negative Phase I/O TpA1p : Port 1 Twisted Pair Cable A Positive Phase I/O TpB0n : Port 0 Twisted Pair Cable B Negative Phase I/O TpB0p : Port 0 Twisted Pair Cable B Positive Phase I/O TpB1n : Port 1 Twisted Pair Cable B Negative Phase I/O TpB1p : Port 1 Twisted Pair Cable B Positive Phase I/O

TpBias0 : Port 0 Twisted Pair Output

TpBias1 : Port 1 Twisted Pair Output

XI : Crystal Oscillator Connection XI

XO : Crystal Oscillator Connection XO

# **CONTENTS**

| 1. | PIN             | FUNCTIONS                                                        | 7    |

|----|-----------------|------------------------------------------------------------------|------|

|    | 1.1             | Cable Interface Pins                                             | 7    |

|    | 1.2             | Link Interface Pins                                              | 7    |

|    | 1.3             | Control Pins                                                     | 8    |

|    | 1.4             | IC                                                               | 8    |

|    | 1.5             | Power Supply Pins                                                | 8    |

|    | 1.6             | Other Pins                                                       | 8    |

|    |                 |                                                                  |      |

| 2. |                 | Y REGISTERS                                                      |      |

|    | 2.1             | Complete Structure for PHY Registers                             | 9    |

|    |                 | Port Status Page (Page 000)                                      |      |

|    | 2.3             | Vendor ID Page (Page 001)                                        | . 13 |

|    | 2.4             | Vendor Dependent Page (Page 111 : Port_select 0001)              | . 13 |

|    |                 |                                                                  |      |

| 3. |                 | ERNAL FUNCTION                                                   |      |

|    | 3.1             | Link Interface                                                   |      |

|    |                 | 3.1.1 Connection Method                                          |      |

|    |                 | 3.1.2 LPS (Link Power Status)                                    |      |

|    |                 | 3.1.3 LREQ, CTL0, CTL1 and D0-D7 Pins                            |      |

|    |                 | 3.1.4 SCLK                                                       |      |

|    |                 | 3.1.5 LKON                                                       |      |

|    |                 | 3.1.6 DIRECT                                                     |      |

|    |                 | 3.1.7 Isolation Barrier                                          |      |

|    | 3.2             | Cable Interface                                                  |      |

|    |                 | 3.2.1 Connections                                                |      |

|    |                 | 3.2.2 Cable Interface Circuit                                    |      |

|    |                 | 3.2.3 Unused Ports                                               |      |

|    |                 | 3.2.4 CPS                                                        |      |

|    | 3.3             | Suspend/Resume                                                   |      |

|    |                 | 3.3.1 Suspend/Resume On Mode (SUS/RES = "H")                     |      |

|    |                 | 3.3.2 Suspend/Resume Off Mode (SUS/RES = "L")                    |      |

|    | 3.4             | PLL and Crystal Oscillation Circuit                              |      |

|    |                 | 3.4.1 Crystal Oscillation Circuit                                |      |

|    |                 | 3.4.2 PLL                                                        |      |

|    |                 | CMC                                                              |      |

|    |                 | PC0-PC2                                                          |      |

|    |                 | RESETB                                                           |      |

|    | 3.8             | RI1                                                              | . 19 |

| 4  | рЦ              | Y/LINK INTERFACE                                                 | 20   |

| 4. |                 | Initialization of Link Power Status (LPS) and PHY/Link Interface |      |

|    |                 | Link-on Indication                                               |      |

|    |                 | PHY/Link Interface Operation (CTL0, CTL1, LREQ, D0-D7)           |      |

|    | <del>+</del> .3 | 4.3.1 CTL0, CTL1                                                 |      |

|    |                 | 4.3.2 LREQ                                                       |      |

|    |                 | 4.3.3 SCLK Timing                                                |      |

|    |                 | 1.0.0 OOLIX TITIITIY                                             | (    |

|    |     | Acceleration Control             |    |

|----|-----|----------------------------------|----|

|    | 4.5 | Transmit Status                  | 28 |

|    | 4.6 | Transmit                         | 29 |

|    | 4.7 | Cancel                           | 30 |

|    | 4.8 | Receive                          | 31 |

| 5. | CAB | BLE PHY PACKET                   | 32 |

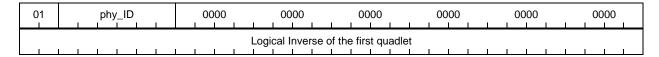

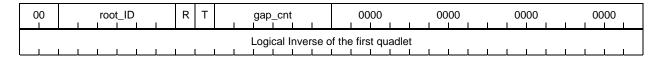

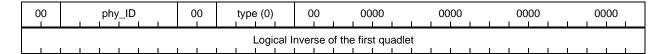

|    | 5.1 | Self_ID Packet                   | 32 |

|    | 5.2 | Link-on Packet                   | 33 |

|    | 5.3 | PHY Configuration Packet         | 33 |

|    | 5.4 | Extended PHY Packet              | 33 |

|    |     | 5.4.1 Ping Packet                | 34 |

|    |     | 5.4.2 Remote Access Packet       | 34 |

|    |     | 5.4.3 Remote Reply Packet        | 35 |

|    |     | 5.4.4 Remote Command Packet      | 35 |

|    |     | 5.4.5 Remote Confirmation Packet | 36 |

|    |     | 5.4.6 Resume Packet              | 36 |

| 6. | ELE | CTRICAL SPECIFICATIONS           | 37 |

| 7. | APP | LICATION CIRCUIT EXAMPLE         | 42 |

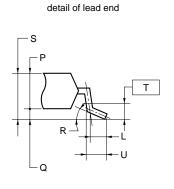

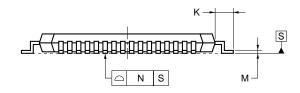

| 8. | PAC | KAGE DRAWING                     | 43 |

| 9. | REC | OMMENDED SOLDERING CONDITIONS    | 44 |

# 1. PIN FUNCTIONS

# 1.1 Cable Interface Pins

| Name    | Pin No. | I/O | Function                                                                                                 |  |  |

|---------|---------|-----|----------------------------------------------------------------------------------------------------------|--|--|

| ТрА0р   | 39      | I/O | Port 0 twisted pair cable A positive phase I/O                                                           |  |  |

| TpA0n   | 38      | I/O | Port 0 twisted pair cable A negative phase I/O                                                           |  |  |

| ТрВ0р   | 37      | I/O | Port 0 twisted pair cable B positive phase I/O                                                           |  |  |

| TpB0n   | 36      | I/O | Port 0 twisted pair cable B negative phase I/O                                                           |  |  |

| TpA1p   | 46      | I/O | Port 1 twisted pair cable A positive phase I/O                                                           |  |  |

| TpA1n   | 45      | I/O | Port 1 twisted pair cable A negative phase I/O                                                           |  |  |

| ТрВ1р   | 44      | I/O | Port 1 twisted pair cable B positive phase I/O                                                           |  |  |

| TpB1n   | 43      | I/O | Port 1 twisted pair cable B negative phase I/O                                                           |  |  |

| SUS/RES | 19      | - 1 | Suspend/Resume function select                                                                           |  |  |

|         |         |     | 1: Suspend/Resume on (IEEE1394a-2000 compliant)                                                          |  |  |

|         |         |     | 0: Suspend/Resume off (P1394a draft 1.3 compliant)                                                       |  |  |

| CPS     | 32      | I   | Cable power status                                                                                       |  |  |

|         |         |     | Connect to the cable through a 390 k $\!\Omega$ resistor and to GND through a 100 k $\!\Omega$ resistor. |  |  |

|         |         |     | 0: Cable power fail                                                                                      |  |  |

|         |         |     | 1: Cable power on                                                                                        |  |  |

# 1.2 Link Interface Pins

| Name                                                 | Pin No. | I/O                                      | Function                                                                                    |  |  |

|------------------------------------------------------|---------|------------------------------------------|---------------------------------------------------------------------------------------------|--|--|

| D0                                                   | 8       | I/O                                      | Data input/output (bit 0)                                                                   |  |  |

| D1                                                   | 9       | I/O                                      | Data input/output (bit 1)                                                                   |  |  |

| D2                                                   | 11      | I/O                                      | Data input/output (bit 2)                                                                   |  |  |

| D3                                                   | 12      | I/O                                      | Data input/output (bit 3)                                                                   |  |  |

| D4                                                   | 14      | I/O                                      | Data input/output (bit 4)                                                                   |  |  |

| D5                                                   | 15      | I/O                                      | Data input/output (bit 5)                                                                   |  |  |

| D6                                                   | 17      | I/O                                      | Data input/output (bit 6)                                                                   |  |  |

| D7                                                   | 18      | I/O                                      | Data input/output (bit 7)                                                                   |  |  |

| CTL0                                                 | 5       | I/O                                      | Link interface control (bit 0)                                                              |  |  |

| CTL1                                                 | 6       | I/O                                      | Link interface control (bit 1)                                                              |  |  |

| LREQ                                                 | 63      | 1                                        | Link request input                                                                          |  |  |

| SCLK                                                 | 2       | 0                                        | Link control output clock                                                                   |  |  |

|                                                      |         |                                          | LPS 1: 49.152 MHz output                                                                    |  |  |

|                                                      |         |                                          | LPS 0: Clamp to 0 (The clock signal will be output within 25 $\mu$ sec after change to "0") |  |  |

| LPS                                                  | 59      | - 1                                      | Link power status input                                                                     |  |  |

|                                                      |         |                                          | 0: Link power off                                                                           |  |  |

|                                                      |         |                                          | 1: Link power on (PHY/Link direct connection)                                               |  |  |

| LKON                                                 | 58      | 0                                        | Link-on signal output                                                                       |  |  |

|                                                      |         |                                          | Link-on signal is 6.144 MHz clock output.                                                   |  |  |

|                                                      |         |                                          | Please refer to 4.2 Link-on Indication.                                                     |  |  |

| DIRECT 50 I PHY/Link isolation barrier control input |         | PHY/Link isolation barrier control input |                                                                                             |  |  |

| 0: Isolation barrier                                 |         |                                          | 0: Isolation barrier                                                                        |  |  |

|                                                      |         |                                          | 1: PHY/Link direct connection                                                               |  |  |

Data Sheet S14920EJ3V0DS

# 1.3 Control Pins

| Name   | Pin No. | I/O | Function                                                                            |  |

|--------|---------|-----|-------------------------------------------------------------------------------------|--|

| PC0    | 26      | - 1 | Power class set input                                                               |  |

| PC1    | 27      | I   | This pin status will be loaded to Pwr_class bit which allocated to PHY register 4H. |  |

| PC2    | 28      | I   | IEEE1394a-2000 chapter [4.3.4.1]                                                    |  |

| CMC    | 30      | - 1 | Configuration manager capable setting                                               |  |

|        |         |     | This pin status will be loaded to Contender bit which allocated to PHY register 4H. |  |

|        |         |     | 0: Non contender                                                                    |  |

|        |         |     | 1: Contender                                                                        |  |

| RESETB | 55      | ı   | Power-on reset input                                                                |  |

|        |         |     | Connect to GND through a 0.1 $\mu$ F capacitor.                                     |  |

|        |         |     | 0: Reset                                                                            |  |

|        |         |     | 1: Normal                                                                           |  |

| SPD    | 61      | I   | Speed select                                                                        |  |

|        |         |     | 0: MAX. \$200                                                                       |  |

|        |         |     | 1: MAX. S400                                                                        |  |

# 1.4 IC

| Name   | Pin No. | I/O | Function                           |  |

|--------|---------|-----|------------------------------------|--|

| IC(AL) | 29, 51  | -   | Internally Connected (Low Clamped) |  |

|        |         |     | Connect to GND.                    |  |

| IC(DL) | 3       | -   | nternally Connected (Low Clamped)  |  |

|        |         |     | Connect to GND.                    |  |

# 1.5 Power Supply Pins

| Name             | Pin No.                    | I/O | Function     |

|------------------|----------------------------|-----|--------------|

| AV <sub>DD</sub> | 25, 31, 40, 47, 54         | -   | Analog power |

| AGND             | 24, 33, 35, 42, 49, 52, 53 | -   | Analog GND   |

| DV <sub>DD</sub> | 4, 10, 20, 56, 60          | -   | Digital VDD  |

| DGND             | 1, 7, 13, 16, 21, 57, 64   | -   | Digital GND  |

# 1.6 Other Pins

| Name    | Pin No. | I/O | Function                                                 |  |

|---------|---------|-----|----------------------------------------------------------|--|

| TpBias0 | 41      | 0   | Port 0 twisted pair output                               |  |

| TpBias1 | 48      | 0   | Port 1 twisted pair output                               |  |

| RI1     | 34      | -   | Resistor connection pin1 for reference current generator |  |

|         |         |     | Connect to GND through a 9.1 $k\Omega$ resistor.         |  |

| XI      | 23      | -   | Crystal oscillator connection XI                         |  |

| XO      | 22      | -   | Crystal oscillator connection XO                         |  |

| TEST    | 62      | -   | est pin                                                  |  |

|         |         |     | Internally connected (Low clamped).                      |  |

|         |         |     | Connect to GND.                                          |  |

# 2. PHY REGISTERS

# 2.1 Complete Structure for PHY Registers

Figure 2-1. Complete Structure of PHY Registers

|      | 0                       | 1                       | 2    | 3            | 4           | 5          | 6          | 7          |  |

|------|-------------------------|-------------------------|------|--------------|-------------|------------|------------|------------|--|

| 0000 |                         |                         | Phys | ical_ID      |             |            | R          | PS         |  |

| 0001 | RHB                     | IBR                     |      |              | Gap_        | count      |            |            |  |

| 0010 |                         | Extended (7)            |      | Reserved     |             | Total_     | _ports     |            |  |

| 0011 |                         | Max_speed               |      | Reserved     |             | De         | lay        |            |  |

| 0100 | Link_active             | Contender               |      | Jitter       |             |            | Pwr_class  |            |  |

| 0101 | Watchdog                | ISBR                    | Loop | Pwr_fail     | Timeout     | Port_event | Enab_accel | Enab_multi |  |

| 0110 |                         |                         |      | Rese         | erved       |            |            |            |  |

| 0111 |                         | Page_select             |      | Reserved     | Port_select |            |            |            |  |

| 1000 |                         |                         |      | Register0 (p | age_select) |            |            |            |  |

| 1001 |                         |                         |      | Register1 (p | age_select) |            |            |            |  |

| 1010 |                         |                         |      | Register2 (p | age_select) |            |            |            |  |

| 1011 |                         |                         |      | Register3 (p | age_select) |            |            |            |  |

| 1100 |                         | Register4 (page_select) |      |              |             |            |            |            |  |

| 1101 | Register5 (page_select) |                         |      |              |             |            |            |            |  |

| 1110 |                         | Register6 (page_select) |      |              |             |            |            |            |  |

| 1111 |                         |                         |      | Register7 (p | age_select) |            |            |            |  |

Table 2-1. Bit Field Description (1/3)

| Field                         | Size | R/W | Reset value         | Description                                                        |  |

|-------------------------------|------|-----|---------------------|--------------------------------------------------------------------|--|

| Physical_ID                   | 6    | R   | 000000              | Physical_ID value selected from Self_ID period.                    |  |

| R                             | 1    | R   | 0                   | If this bit is 1, the node is root.                                |  |

|                               |      |     |                     | 1: Root                                                            |  |

|                               |      |     |                     | 0: Not root                                                        |  |

| PS                            | 1    | R   |                     | Cable power status.                                                |  |

|                               |      |     |                     | 1: Cable power on                                                  |  |

|                               |      |     |                     | 0: Cable power off                                                 |  |

| RHB                           | 1    | R/W | 0                   | Root Hold -off bit. If 1, becomes root at the bus reset.           |  |

| IBR 1 R/W 0 Initiate bus rese |      | 0   | Initiate bus reset. |                                                                    |  |

|                               |      |     |                     | Setting to 1 begins a long bus reset.                              |  |

|                               |      |     |                     | Long bus reset signal duration: 166 $\mu$ sec.                     |  |

|                               |      |     |                     | Returns to 0 at the beginning of bus reset.                        |  |

| Gap_count                     | 6    | R/W | 111111              | Gap count value.                                                   |  |

|                               |      |     |                     | It is updated by the changes of transmitting and receiving the PHY |  |

|                               |      |     |                     | configuration packet Tx/Rx.                                        |  |

|                               |      |     |                     | The value is maintained after first bus reset.                     |  |

|                               |      |     |                     | After the second bus reset it returns to reset value.              |  |

| Extended                      | 3    | R   | 111                 | Shows the extended register map.                                   |  |

Data Sheet S14920EJ3V0DS

Table 2-1. Bit Field Description (2/3)

| Field       | Size              | R/W | Reset value | Description                                                                    |

|-------------|-------------------|-----|-------------|--------------------------------------------------------------------------------|

| Total_ports | 4                 | R   | 0010        | Supported port number.                                                         |

|             |                   |     |             | 0010: 2 ports                                                                  |

| Max_speed   | Max_speed 3 R See |     | See         | Indicate the maximum speed that this node supports.                            |

|             |                   |     | Description | Set variable by SPD pin(61 pin).                                               |

|             |                   |     |             | When SPD = "0" then 001: 98.304 and 196.608 Mbps.                              |

|             |                   |     |             | When SPD = "1" then 010: 98.304, 196.608 and 393.216 Mbps.                     |

| Delay       | 4                 | R   | 0000        | Indicate worst case repeating delay time. 144 + (Delay x 20) = 144 nsec        |

| Link_active | 1                 | R/W | 1           | Link active.                                                                   |

|             |                   |     |             | 1: Enable                                                                      |

|             |                   |     |             | 0: Disable                                                                     |

|             |                   |     |             | The logical AND status of this bit and LPS pin.                                |

|             |                   |     |             | State will be referred to "L bit" of Self-ID Packet#0.                         |

| Contender   | 1                 | R/W | See         | Contender.                                                                     |

|             |                   |     | Description | "1" indicate this node support bus manager function. This bit will be referred |

|             |                   |     |             | to "C bit" of Self-ID Packet#0.                                                |

|             |                   |     |             | The reset data is depending on CMC pin setting.                                |

|             |                   |     |             | CMC pin condition                                                              |

|             |                   |     |             | 1: Pull up (Contender)                                                         |

|             |                   |     |             | 0: Pull down (Non Contender)                                                   |

| Jitter      | 3                 | R   | 010         | The difference of repeating time (MaxMin.). (2+1) x 20=60 nsec                 |

| Pwr_class   | 3                 | R/W | See         | Power class.                                                                   |

|             |                   |     | Description | Please refer to IEEE1394a-2000 [4.3.4.1].                                      |

|             |                   |     |             | This bit will be referred to Pwr field of Self-ID Packet#0.                    |

|             |                   |     |             | The reset data will be determined by PC0-PC2 Pin status.                       |

| Watchdog    | 1                 | R/W | 0           | Watchdog Enable.                                                               |

|             |                   |     |             | This bit serves two purposes.                                                  |

|             |                   |     |             | When set to 1, if any one port does resume, the Port_event bit becomes 1.      |

|             |                   |     |             | This function has no effect when SUS/RES(19pin) = "0".                         |

|             |                   |     |             | To determine whether or not an interrupt condition shall be indicated to the   |

|             |                   |     |             | Link. On condition of LPS = 0 and Watchdog = 0, LKON as interrupt of Loop,     |

|             |                   |     |             | Pwr_fail, Timeout is not output. This function has effect both when            |

|             |                   |     |             | SUS/RES(19pin) = "1" or "0".                                                   |

| ISBR        | 1                 | R/W | 0           | Initiate short (arbitrated) bus reset.                                         |

|             |                   |     |             | Setting to 1 acquires the bus and begins short bus reset.                      |

|             |                   |     |             | Short bus reset signal output : 1.3 μsec                                       |

|             |                   |     |             | Returns to 0 at the beginning of the bus reset.                                |

| Loop        | 1                 | R/W | 0           | Loop detection output.                                                         |

|             |                   |     |             | 1: Detection                                                                   |

|             |                   |     |             | Writing 1 to this bit clears it to 0.                                          |

|             |                   |     |             | Writing 0 has no effect.                                                       |

| Pwr_fail 1  |                   | R/W | 1           | Power cable disconnect detect.                                                 |

|             |                   |     |             | It becomes 1 when there is a change from 1 to 0 in the CPS bit.                |

|             |                   |     |             | Writing 1 to this bit clears it to 0.                                          |

|             |                   |     |             | Writing 0 has no effect.                                                       |

Table 2-1. Bit Field Description (3/3)

| Field       | Size | R/W | Reset value | Description                                                                  |

|-------------|------|-----|-------------|------------------------------------------------------------------------------|

| Timeout     | 1    | R/W | 0           | Arbitration state machine time-out.                                          |

|             |      |     |             | Writing 1 to this bit clears it to 0.                                        |

|             |      |     |             | Writing 0 has no effect.                                                     |

| Port_event  | 1    | R/W | 0           | Set to 1 when the Int_enable bit in the register map of each port is 1 and   |

|             |      |     |             | there is a change in the ports connected, Bias, Disabled and Fault bits.     |

|             |      |     |             | Set to 1 when the Watchdog bit is 1 and any one port does resume.            |

|             |      |     |             | Writing 1 to this bit clears it to 0.                                        |

|             |      |     |             | Writing 0 has no effect.                                                     |

|             |      |     |             | This bit is not settable when SUS/RES(19pin) = "0".                          |

| Enab_accel  | 1    | R/W | 0           | Enables arbitration acceleration.                                            |

|             |      |     |             | Ack-acceleration and Fly-by arbitration are enabled.                         |

|             |      |     |             | 1: Enabled                                                                   |

|             |      |     |             | 0: Disabled                                                                  |

|             |      |     |             | If this bit changes while the bus request is pending, the operation is not   |

|             |      |     |             | guaranteed.                                                                  |

| Enab_multi  | 1    | R/W | 0           | Enable multi-speed packet concatenation.                                     |

|             |      |     |             | Setting this bit to 1 follows multi-speed transmission.                      |

|             |      |     |             | When this bit is set to 0,the packet will be transmitted with the same speed |

|             |      |     |             | as the first packet.                                                         |

| Page_select | 3    | R/W | 000         | Select page address between 1000 to 1111.                                    |

|             |      |     |             | 000: Port Status Page                                                        |

|             |      |     |             | 001: Vendor ID Page                                                          |

|             |      |     |             | 111: Vendor Dependent Page                                                   |

|             |      |     |             | Others: Unused                                                               |

| Port_select | 4    | R/W | 0000        | Port Selection.                                                              |

|             |      |     |             | Selecting 000 (Port Status Page) with the Page_select selects the port.      |

|             |      |     |             | Selecting 111 (Vendor Dependent Page) with the Page_select have to select    |

|             |      |     |             | the Port 1.                                                                  |

|             |      |     |             | 0000: Port 0                                                                 |

|             |      |     |             | 0001: Port 1                                                                 |

|             |      |     |             | Others: Unused                                                               |

| Reserved    | -    | R   | 000         | Reserved. Read as 0.                                                         |

# 2.2 Port Status Page (Page 000)

Figure 2-2. Port Status Page

|      | 0                | 1        | 2     | 3          | 4     | 5         | 6    | 7        |

|------|------------------|----------|-------|------------|-------|-----------|------|----------|

| 1000 | AStat            |          | BStat |            | Child | Connected | Bias | Disabled |

| 1001 | Negotiated_speed |          |       | Int_enable | Fault | Reserved  |      |          |

| 1010 | Reserved         |          |       |            |       |           |      |          |

| 1011 | Reserved         |          |       |            |       |           |      |          |

| 1100 |                  | Reserved |       |            |       |           |      |          |

| 1101 |                  | Reserved |       |            |       |           |      |          |

| 1110 | Reserved         |          |       |            |       |           |      |          |

| 1111 | Reserved         |          |       |            |       |           |      |          |

Table 2-2. Bit Field Description

| Field       | Size | R/W | Reset value | Description                                                                      |

|-------------|------|-----|-------------|----------------------------------------------------------------------------------|

| AStat       | 2    | R   | XX          | A port status value.                                                             |

|             |      |     |             | 00: invalid, 10: "0"                                                             |

|             |      |     |             | 01: "1", 11: "Z"                                                                 |

| BStat       | 2    | R   | XX          | B port status value.                                                             |

|             |      |     |             | 00: invalid, 10: "0"                                                             |

|             |      |     |             | 01: "1", 11: "Z"                                                                 |

| Child       | 1    | R   |             | Child node status value.                                                         |

|             |      |     |             | 1: Connected to child node                                                       |

|             |      |     |             | 0: Connected to parent node                                                      |

| Connected   | 1    | R   | 0           | Connection status value.                                                         |

|             |      |     |             | 1: Connected                                                                     |

|             |      |     |             | 0: Disconnected                                                                  |

| Bias        | 1    | R   |             | Bias voltage status value.                                                       |

|             |      |     |             | 1: Bias voltage                                                                  |

|             |      |     |             | 0: No bias voltage                                                               |

| Disabled    | 1    | R/W | See         | The reset value is set to 0: Enabled.                                            |

|             |      |     | Description |                                                                                  |

| Negotiated_ | 3    | R   |             | Shows the maximum data transfer rate of the node connected to this port.         |

| speed       |      |     |             | 000: 100 Mbps                                                                    |

|             |      |     |             | 001: 200 Mbps                                                                    |

|             |      |     |             | 010: 400 Mbps                                                                    |

| Int_enable  | 1    | R/W | 0           | When set to 1, the Port_event is set to 1 if any of this port's Connected, Bias, |

|             |      |     |             | Disabled or Fault bits change state.                                             |

|             |      |     |             | This bit has no effect when SUS/RES(19pin) = "0".                                |

| Fault       | 1    | R/W | 0           | Set to 1 if an error occurs during Suspend/Resume.                               |

|             |      |     |             | Writing 1 to this bit clears it to 0.                                            |

|             |      |     |             | Writing 0 has no effect.                                                         |

|             |      |     |             | This bit has no effect when SUS/RES(19pin) = "0"                                 |

| Reserved    | -    | R   | 000         | Reserved. Read as 0.                                                             |

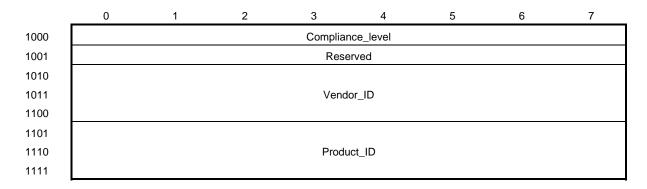

# 2.3 Vendor ID Page (Page 001)

Figure 2-3. Vendor ID Page

Table 2-3. Bit Field Description

| Field            | Size | R/W | Reset value | Description                          |

|------------------|------|-----|-------------|--------------------------------------|

| Compliance_level | 8    | R   | 0000001     | According to IEEE1394a-2000.         |

| Vendor_ID        | 24   | R   | 00004CH     | Company ID Code value, NEC IEEE OUI. |

| Product_ID       | 24   | R   |             | Product code.                        |

| Reserved         | ı    | R   | 000         | Reserved. Read as 0.                 |

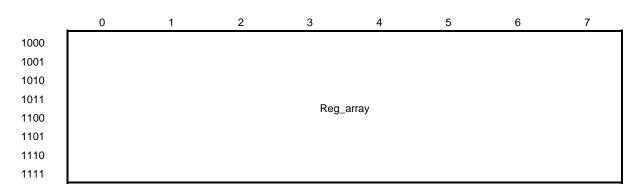

# 2.4 Vendor Dependent Page (Page 111 : Port\_select 0001)

Figure 2-4. Vendor Dependent Page

Table 2-4. Bit Field Description

| Field     | Size | R/W | Reset value | Description                          |

|-----------|------|-----|-------------|--------------------------------------|

| Reg_array | 64   | R/W | 0           | This register array is possible R/W. |

Data Sheet S14920EJ3V0DS

#### 3. INTERNAL FUNCTION

#### 3.1 Link Interface

#### 3.1.1 Connection Method

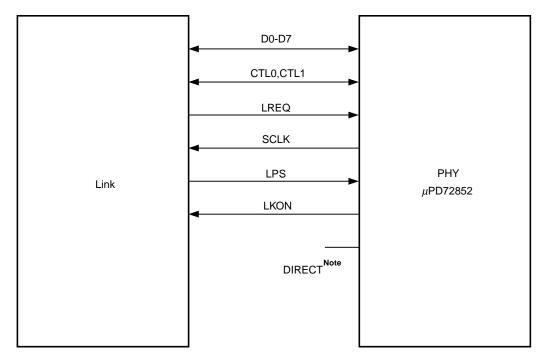

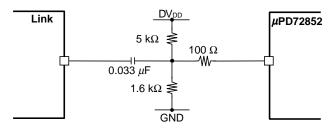

Figure 3-1. PHY/Link Connection Method

Note Clamping to VDD provides direct connection to Link.

Clamping to GND connects through isolation barrier to Link.

The isolation barrier connection circuit is described in 3.1.7 Isolation Barrier.

#### 3.1.2 LPS (Link Power Status)

LPS is a function to monitor the On/Off status of the Link power supply. After 1.2  $\mu$ sec or more, LPS is Low, the PHY/Link is reset and D and CTL are output Low (when the isolation barrier is Hi-Z). After 2.5  $\mu$ sec or more, LPS is Low, moreover, the PHY stops the supply of SCLK and SCLK outputs Low (when the isolation barrier is Hi-Z).

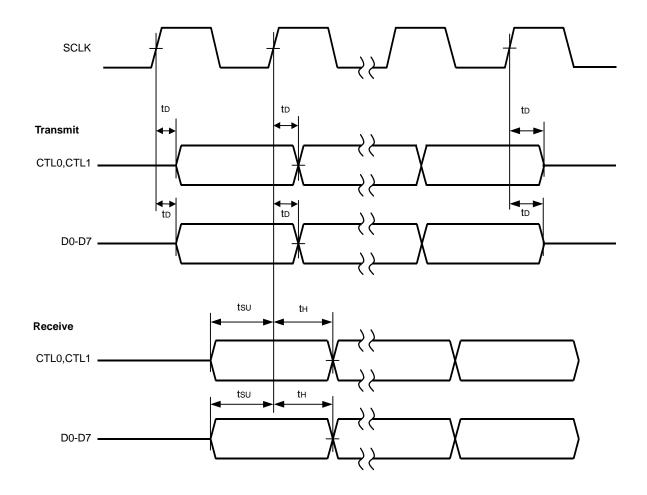

#### 3.1.3 LREQ, CTL0, CTL1 and D0-D7 Pins

LREQ : Indicates that a request is received from Link.

CTL0, CTL1: Bi-directional pin which controls the functions between the PHY/Link interface.

D0-D7 : Bi-directional pin which controls the data Transfer/Receive status signal, and the speed code

Transfer/Receive status signal.

#### 3.1.4 SCLK

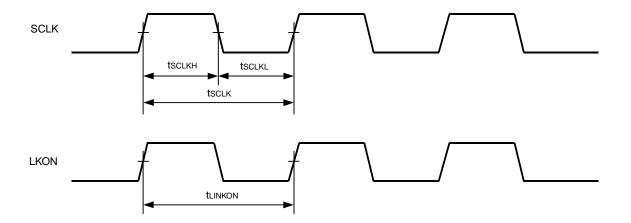

49.152 MHz clock supplied by PHY for the PHY/Link interface synchronization.

#### 3.1.5 LKON

When the Link power is off, it outputs a clock of 6.144 MHz. LKON outputs under the following conditions: LPS is Low and the internal PHY register of the Link\_active bit is 0.

- Link-on packet is received.

- Any bit of Loop, Pwr\_fail, Timeout or Port\_event is the PHY internal register becomes 1, and moreover either LPS or Link\_active bit is 0.

When LPS is asserted, LKON returns to Low.

#### **3.1.6 DIRECT**

Set DIRECT to Low for using the isolation barrier.

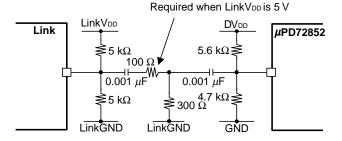

#### 3.1.7 Isolation Barrier

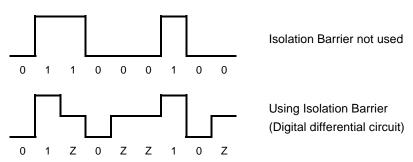

The IEEE1394 cable holds signals for Data/Strobe in addition to power and ground.

When the ground potential is different between connecting devices, the DC and AC current flows through the ground line in the cable and there is a possibility of malfunction due to ground difference between the two PHY.

The  $\mu$ PD72852 uses the isolation barrier to couple the AC between the PHY/Link interface to overcome the ground difference problem. Connecting the DIRECT pin to Low enables the digital differential circuit of the  $\mu$ PD72852. The differential circuit propagates only the change in the signal; the interface will be driven only during transitions High  $\rightarrow$  Low or Low  $\rightarrow$  High. The interface will assume the high impedance state when there is no signal change. The  $\mu$ PD72852 uses Schmitt trigger input buffers for D, CTL, LREQ and LPS pins to prevent noise when the bus assumes a high impedance state.

The digital differential circuit and the Schmitt trigger input buffers are needed on the Link layer controller LSI to implement the isolation barrier.

Figure 3-2. Waveforms of the Isolation Barrier

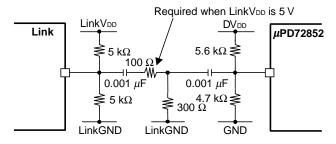

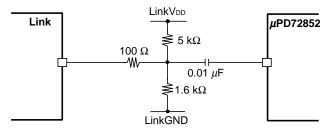

## **★** Figure 3-3. Isolation Barrier Circuits

## (a) CTL0, CTL1, D0-Dn Isolation Barrier Circuit

#### (b) Link-on Isolation Barrier Circuit

#### (c) LPS Isolation Barrier Circuit

## (d) LREQ Isolation Barrier Circuit

## (e) SCLK Isolation Barrier Circuit

The Operating range of the power supply voltage is between 3.0 V and 3.45 V. Please refer to **IEEE1394a-2000 [5A.8.4]**.

## 3.2 Cable Interface

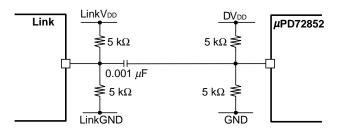

# 3.2.1 Connections

Figure 3-4. Cable Interface

#### 3.2.2 Cable Interface Circuit

Each port is configured with two twisted-pairs of TpA and TpB.

TpA and TpB are used to monitor the state of the Transmit/Receive line, control signals, data and cables.

During transmission to the IEEE1394 bus, the Data/Strobe signal received from the Link layer controller is encoded, converted from parallel to serial and transmitted.

While receiving from the IEEE1394 bus, the Data/Strobe signal from TpA, TpB is converted from serial to parallel after synchronization by SCLK, then transmitted to the Link layer controller in 2/4/8 bits according to the data rate of 100/200/400 Mbps.

The bus arbitration for TpA and TpB and the state of the line are monitored by the built-in comparator. The state of the IEEE1394 bus is transmitted to the state machine in the LSI.

#### 3.2.3 Unused Ports

TpAp, TpAn: Not connected

TpBp, TpBn: GND

TpBias : Not connected

#### 3.2.4 CPS

Connect an external resistor of 390 k $\Omega$  between the CPS pin and the power cable, and an external resistor of 100 k $\Omega$  between the CPS pin and GND to monitor the power of the power cable.

If the cable power falls under 7.5 V there is an indication to the Link layer controller that the power has failed.

## 3.3 Suspend/Resume

#### 3.3.1 Suspend/Resume On Mode (SUS/RES = "H")

There are two ways of transition from the active status to the suspended status.

One is when the receipt of a remote command packet that sets the initiate suspend command. After that, the PHY transmits a remote confirmation packet with the ok bit set, subsequently signals TX\_SUSPEND to the connected peer PHY with the port which specified by the port field in the remote command packet, and then the PHY port transitions to the suspended state.

The other is when the receipt of a RX\_SUSPEND or RX\_DISABLE\_NOTIFY signal. When the port observes RX\_SUSPEND, it transmits TX\_SUSPEND to the active ports.

The TX\_SUSPEND transmitted propagates until it reaches a leaf node. The PHY port transitions to the suspended state. The propagation of the suspended domain may be blocked by a PHY compliant with IEEE1394a-2000, a disabled or a suspended port.

Any one of a number of reasons may cause a suspended port to attempt to resume normal operations:

- Bias is detected and there is no fault condition;

- A resume packet is received or transmitted by the PHY;

- A remote command packet that sets the resume port command is received; or

- Either port of a node without active ports detects bias.

#### 3.3.2 Suspend/Resume Off Mode (SUS/RES = "L")

- Remote command packet is ignored.

- Resume packet is ignored.

- Disabled, Int\_enable and resume\_int bits in PHY register are ignored.

- · Responses to Remote access packet.

- Detects the connection of the port in TpBias.

- Output the 1.85 V voltage of the port in TpBias.

## 3.4 PLL and Crystal Oscillation Circuit

## 3.4.1 Crystal Oscillation Circuit

To supply the clock of 24.576 MHz ± 100 ppm, use an external capacitor of 10 pF and a crystal of 50 ppm.

#### 3.4.2 PLL

The crystal oscillator multiplies the 24.576 MHz frequency by 16 (393.216 MHz).

#### 3.5 CMC

CMC shows the bus manager function which corresponds to the c bit of the Self\_ID packet and the Contender bit in the PHY register when the input is High.

The value of CMC can be changed with software through the Link layer; this pin sets the initial value during Poweron Reset. Use a pull-up or pull-down resistor of 10 k $\Omega$ , based on the device's specification.

#### 3.6 PC0-PC2

The PC0-PC2 pin corresponds to the power field of the Self\_ID packet and Pwr\_class in the PHY register. Refer to Section 4.3.4.1 of the IEEE1394a-2000 specification for information regarding the Pwr\_class. The value of Pwr can be changed with software through the Link layer controller; this pin sets the initial value during Power-on Reset. Use a pull-up or pull-down resistor of 10  $k\Omega$  based on the application.

#### 3.7 RESETB

Connect an external capacitor of 0.1  $\mu$ F between the RESETB pin and GND. If the voltage drops below 0 V, a reset pulse is generated. All of the circuits are initialized, including the contents of the PHY register.

## 3.8 RI1

Connect an external resistor of 9.1 k $\Omega$  between the RI1 pin and GND to limit the LSI's current.

## 4. PHY/LINK INTERFACE

# 4.1 Initialization of Link Power Status (LPS) and PHY/Link Interface

The LPS pin monitors the On/Off status of the Link power state. This pin is used during the PHY/Link interface Enable/Disable (initialization).

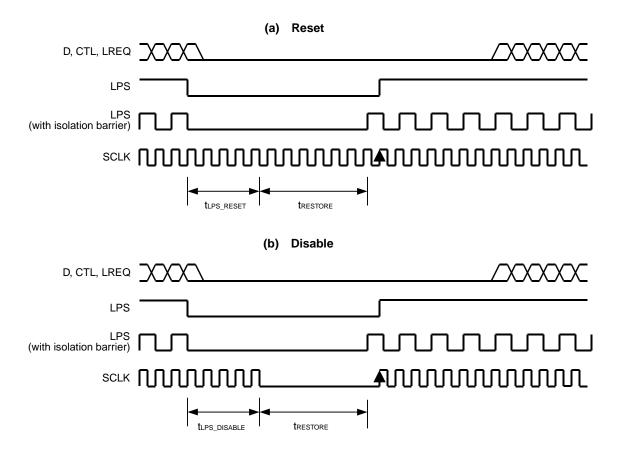

#### Reset

When the LPS input pin is Low for TLPS\_RESET:

- CTL0, CTL1 and D0-D7 output Low (When the isolation barrier is Hi-Z).

- SCLK continuously supplies the clock signal to the Link.

#### Disable

When the LPS input pin is Low for TLPS\_DISABLE:

- CTL0, CTL1, D0-D7 continue to output Low as TLPS\_RESET has already occurred (When the isolation barrier is Hi-Z).

- SCLK to Link stops and it outputs Low (When the isolation barrier is Hi-Z).

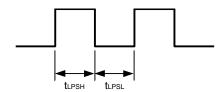

Table 4-1. LPS Timing Parameters

| Parameter                                             | Symbol       | MIN. | MAX. | Unit |

|-------------------------------------------------------|--------------|------|------|------|

| LPS = Low propagation delay (with isolation barrier)  | tlpsl        | 0.09 | 1.00 | μs   |

| LPS = High propagation delay (with isolation barrier) | tlpsh        | 0.09 | 1.00 | μs   |

| Reset active                                          | tlps_reset   | 1.2  | 2.75 | μs   |

| Disable active                                        | tlps_disable | 25   | 30   | μs   |

| Setup time when using isolation barrier               | trestore     | 15   | 20   | μs   |

Figure 4-1. LPS Waveform when Connected to Isolation Barrier

Figure 4-2. PHY/Link Interface Reset and Disable

#### 4.2 Link-on Indication

When the power supply of Link is off (LPS is Low and the internal PHY register Link\_active bit is 0), the pin LKON outputs a clock of 6.144 MHz according to the following conditions:

- Link-on packet is received.

- When any bit of the  $\mu$ PD72852 PHY register's loop, Pwr\_fail, Timeout or Port\_event becomes 1, and either LPS or the Link\_active bit is 0.

| Parameter                                                   | MIN. | MAX. | Unit |

|-------------------------------------------------------------|------|------|------|

| Frequency                                                   | 4    | 8    | MHz  |

| Duty Cycle                                                  | 40   | 60   | %    |

| Propagation delay before the Link becomes active (LPS is    |      | 500  | ns   |

| asserted and the Link_active bit in the PHY register is 1). |      |      |      |

Table 4-2. Link-on Timing

- If LPS or the Link\_active bit is 0, the Link is considered inactive.

When the Link is inactive and any of Loop, Pwr\_fail, Timeout, Port\_event becomes 1, then Link-on is asserted

- High.

- When the Link is active (both LPS and Link\_active become 1) and Loop, Pwr\_fail, Timeout and Port\_event become 1, Status transfer is sent on the PHY/Link interface.

- The  $\mu$ PD72852 activates the PHY/Link interface when LPS is 1, regardless of the value of the Link active bit.

# 4.3 PHY/Link Interface Operation (CTL0, CTL1, LREQ, D0-D7)

The PHY/Link Interface consists of the following operations:

- Status transfer to the Link layer controller by CTL

- Transmit packet

- Receive packet

- Request from the Link layer controller by LREQ

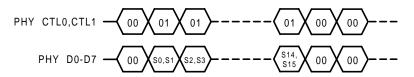

#### 4.3.1 CTL0, CTL1

CTL0, CTL1 controls the PHY/Link interface as shown in the Table 4-3.

Table 4-3. CTL Controls PHY

| CTL0,CTL1 | Туре    | Content                                     |

|-----------|---------|---------------------------------------------|

| 00        | Idle    | PHY is in idle function                     |

| 01        | Status  | PHY transmitting status information to Link |

| 10        | Receive | PHY receiving data from the Link            |

| 11        | Grant   | PHY allows Link to transmit data            |

This is the operation by which, after Grant, the Link obtains the right to control the interface.

Table 4-4. CTL Controls Link

| CTL0,CTL1 | Туре     | Content                                                                     |

|-----------|----------|-----------------------------------------------------------------------------|

| 00        | Idle     | Link completes the packet transmission and releases the PHY/Link interface. |

| 01        | Hold     | 1) Link transmits Hold until the data is ready for transmission.            |

|           |          | 2) Link transmits the interface connect packet.                             |

| 10        | Transmit | Link transmits the data to PHY.                                             |

| 11        | -        | Not used.                                                                   |

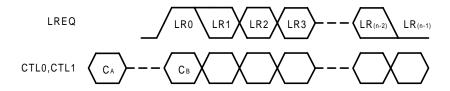

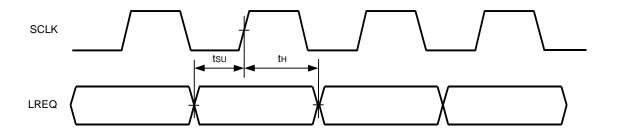

## 4.3.2 LREQ

Access to the PHY register and the bus is controlled from the Link layer controller through the LREQ pin of PHY.

Figure 4-3. LREQ and CTL Timing

$C_A$ : CTL before generation of LREQ  $C_B$ : CTL during LREQ execution

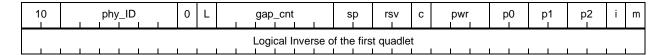

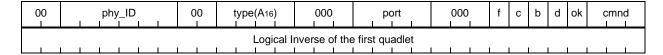

# (1) LREQ format

# • Bus Request

Table 4-5. Bus Request Format

| Bit | Туре    | Content                                   |

|-----|---------|-------------------------------------------|

| 0   | start   | Signal that starts a request : 1          |

| 1-3 | request | Bus request type:                         |

|     |         | 000: ImmReq acknowledge packet transmit   |

|     |         | 001: IsoReq isochronous packet transmit   |

|     |         | 010: PriReq cycle start packet transmit   |

|     |         | 011: FairReq asynchronous packet transmit |

| 4-6 | speed   | Transmit speed:                           |

|     |         | 000: 100 Mbps                             |

|     |         | 010: 200 Mbps                             |

|     |         | 100: 400 Mbps                             |

|     |         | other: reserved                           |

| 7   | stop    | End request signal : 0 (optional)         |

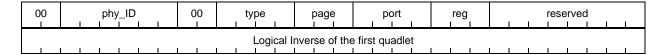

# • PHY Register Read Request

Table 4-6. Read Request Register Format

| Bit | Туре           | Content                          |

|-----|----------------|----------------------------------|

| 0   | start          | Signal that starts a request : 1 |

| 1-3 | request        | Read Request.                    |

|     |                | 100 : ReadReq                    |

| 4-7 | access address | PHY register address.            |

| 8   | stop           | End request signal : 0           |

# • PHY Register Write Request

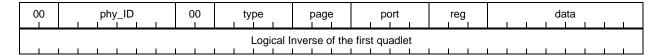

Table 4-7. Write Request Register Format

| Bit  | Туре           | Content                          |

|------|----------------|----------------------------------|

| 0    | start          | Signal that starts a request : 1 |

| 1-3  | request        | Write Request.                   |

|      |                | 101 : WriteReq                   |

| 4-7  | access address | PHY register address.            |

| 8-15 | write data     | Write data.                      |

| 16   | stop           | End request signal : 0           |

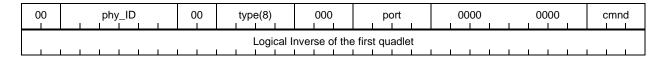

#### Acceleration Controller

Table 4-8. Acceleration Controller Request Format

| Bit | Туре           | Content                              |

|-----|----------------|--------------------------------------|

| 0   | start          | Signal that starts a request : 1     |

| 1-3 | request        | 110 : Acc Ctrl accelerate controller |

| 4   | access address | 0: Accelerate disable                |

|     |                | 1: Accelerate enable                 |

| 5   | stop           | End request signal : 0               |

Table 4-9. Request Type List

| Bit | Туре    | Content                                                                      |

|-----|---------|------------------------------------------------------------------------------|

| 000 | ImmReq  | Used to acknowledge packet transmit.                                         |

|     |         | When Idle is detected, PHY immediately controls the bus.                     |

| 001 | IsoReq  | Used to transmit isochronous packet.                                         |

|     |         | PHY does arbitration after isochronous gap is detected and acquires the bus. |

| 010 | PriReq  | Used for Cycle master request.                                               |

| 011 | FairReq | Fair request.                                                                |

| 100 | RdReg   | PHY register read request.                                                   |

| 101 | WrReg   | PHY register write request.                                                  |

| 110 | AccCtrl | Disable/enable of arbitration acceleration.                                  |

| 111 | -       | Unused.                                                                      |

For the Link to execute Priority request and Fair, start the request using LREQ when CTL0, CTL1 becomes idle, after one clock. When request is acknowledged, the  $\mu$ PD72852 outputs Grant to CTL0, CTL1.

The Link of cycle master uses PriReq to transmit the cycle start packet. IsoReq transmits the isochronous packet.

IsoReq becomes effective only as follows:

- The transmission of the cycle start packet is performed on the same isochronous period as Receive. (The period until the subaction gap is detected.)

- During isochronous packet Transmit or Receive.

The  $\mu$ PD72852 cancels IsoReq with the subaction gap detection or bus reset. To meet the timing, do not issue the IsoReq to PHY when CRC operation is performed.

The Link cancel method is described later.

After the packet is received, Link issues ImmReq as the acknowledge packet transmission. The purpose is to prevent another node from detecting subaction gap as ACK\_RESPONSE\_TIME. The  $\mu$ PD72852 acquires the bus after packet receive and returns Grant to CTL0, CTL1. When CRC fails, before Link detects Grant, assert 3 Idle cycles to CTL0, CTL1.

When the bus reset is generated, the unprocessed requests are canceled.

The  $\mu$ PD72852 updates the data of the Write request register and the contents of the Read register are changed. The contents of the register of the specified address are output to the Link as a status transfer in the Read request register, When the status transmission is interrupted by transmitting/receiving packets, the status transmission will re-start from the first bit after completing the transmit/receive of the packets.

The bus request (ImmReq, IsoReq, PriReg, FairReq) is completed (in case of ImmReq, IsoReq, when the subaction gap is detected) when the packet is transmitted or canceled by canceling the bus request.

#### (2) LREQ rules

The Link request and the status of the serial bus are asynchronous; the bus request can be canceled by the status of the serial bus.

The following rules apply to a request by LREQ:

- Link cannot issue a bus request (ImmReq, IsoReq, PriReq, FairReq) if Grant is given to an LREQ request or until the Link's request is canceled. The request can be canceled by the  $\mu$ PD72852 if it detects subaction gap at ImmReq, IsoReq.

- Do not issue a RdReg or WrReg request when the status transmission is not completed by the Read request register.

- All of the bus requests (ImmReq, IsoReq, PriReq, FairReq) are canceled by a bus reset.

In addition, there is a limitation in the request of LREQ according to the state of CTL as shown in Table 4-10.

Table 4-10. Rules for Other Requests

| Request        | State of CTL in C <sub>A</sub> to which LREQ is allowed | LREQ issues permission when Link | Note                                                          |

|----------------|---------------------------------------------------------|----------------------------------|---------------------------------------------------------------|

|                | when PHY drives CTL                                     | drives CTL                       |                                                               |

| Fair, Priority | Idle, Status                                            | wrong                            | Fair, Priority request cannot be issued until the             |

|                |                                                         |                                  | unprocessed bus request is completed.                         |

| Immediate      | Receive, Idle                                           | wrong                            | Link issues the request after completing the decoding of      |

|                |                                                         |                                  | Destination_ID, when the acknowledge packet is ready.         |

|                |                                                         |                                  | After the packet is received, it is necessary to transmit the |

|                |                                                         |                                  | first bit of the request within four cycles.                  |

| Isochronous    | any                                                     | correct                          | If the isochronous packet transmission is prepared for the    |

|                |                                                         |                                  | isochronous period, it is issued.                             |

|                |                                                         |                                  | Do not issue the request to transmit the isochronous          |

|                |                                                         |                                  | packet appending to the currently transmitted isochronous     |

|                |                                                         |                                  | packet (Using Hold).                                          |

| Register Read  | any                                                     | correct                          | Do not issue this request if the unprocessed Read request     |

| Register Write |                                                         |                                  | has not been completed.                                       |

| AccCtrl        | any                                                     | correct                          | To set acceleration bit 0:                                    |

|                |                                                         |                                  | When the isochronous period starts, if the Enab_accel bit     |

|                |                                                         |                                  | is one, Cycle slave should adjust accelerate bit to 0.        |

|                |                                                         |                                  |                                                               |

|                |                                                         |                                  | To set acceleration bit 1:                                    |

|                |                                                         |                                  | Do not set the cycle master.                                  |

|                |                                                         |                                  | It is issued when the isochronous period ends.                |

Table 4-11. PHY Operation Before LREQ Request to the CTL Function Changes

| Request         | State of CTL in CB after       | Operation of the PHY                                                        |

|-----------------|--------------------------------|-----------------------------------------------------------------------------|

|                 | LREQ was issued                |                                                                             |

| Fair, Priority  | Receive                        | Hold the request if the acceleration of arbitration packet transmitted with |

|                 |                                | enable is 8 bits (ACK).                                                     |

|                 |                                | Except for 8 bits, the requests are ignored.                                |

|                 |                                | Ignore the request when the acceleration of arbitration is disabled.        |

|                 | Grant                          | Arbitration Won.                                                            |

|                 | Idle, Status                   | Excluding when the bus reset is generated, Hold the requests.               |

| Immediate       | Grant                          |                                                                             |

|                 | Receive                        | The packet is being transmitted to Link. Request Hold.                      |

|                 | Idle, Status                   | Excluding when the bus reset is generated, hold the request.                |

| Isochronous     | Transmit Idle (driven by Link) | Request Hold.                                                               |

|                 | Grant                          | Arbitration Won.                                                            |

|                 | Receive                        | Request Hold.                                                               |

|                 | Status                         | Request is ignored when sub-action gap is detected.                         |

|                 | Idle                           |                                                                             |

| Register Read   | Any (driven by Link)           |                                                                             |

|                 | Grant                          | Request Hold.                                                               |

|                 | Receive                        | Request Hold.                                                               |

|                 | Status                         | Hold the request until the corresponding register value is returned.        |

|                 | Idle                           |                                                                             |

| Register Write, | Any                            | Request is completed.                                                       |

| Acceleration    |                                |                                                                             |

| control         |                                |                                                                             |

# 4.3.3 SCLK Timing

Table 4-12. SCLK Timing

| Timing Constant      | Comment                                              | MIN. | MAX. | Unit       |

|----------------------|------------------------------------------------------|------|------|------------|

| BUS_TO_LINK_DELAY    | Period from receiving RX_DATA_PREFIX until           | 2    | 9    | SCLK cycle |

|                      | Receive to CTL is output.                            |      |      |            |

| DATA_PREFIX_TO_GRANT | Period when the Grant is output to CTL after         |      | 25   | SCLK cycle |

|                      | TX_DATA_PREFIX is output to a port.                  |      |      |            |

| LINK_TO_BUS_DELAY    | Period when TX_DATA_END is output to all ports       | 2    | 5    | SCLK cycle |

|                      | after transmitting the packet by Link after idle was |      |      |            |

|                      | asserted to CTL.                                     |      |      |            |

| MAX_HOLD             | Maximum period when Hold can be asserted by Link     |      | 47   | SCLK cycle |

|                      | to confirm Grant.                                    |      |      |            |

#### 4.4 Acceleration Control

Enable of ack-acceleration and fly-by on the same isochronous period may create a problem. The isochronous cycle may extend unintentionally when transmitting the asynchronous packet by a node using ack-acceleration and fly-by.

To avoid this problem, Link should control Disable/Enable of these enhancements (ack-Acceleration, fly-by), by Acceleration Control requests. Cycle master cannot issue the Acceleration Control request.

The enhancements should not be used from the generation of the local cycle synchronization event to the confirmation of cycle start. In this period, all Links except for Cycle Master use Acceleration Control as follows:

- Do not issue Fair nor Priority request to Link after generating local cycle synchronization, if the Acceleration Control request's Accelerate bit is not set to 0.

- Link must not use Hold when transmitting continuous primary asynchronous packet after the Acknowledge packet, except after ack\_pending to complete the split transaction.

- Ending the Link during the isochronous period issues the acceleration control request to set the Accelerate bit to 1, enabling these enhancements.

The  $\mu$ PD72852 does not require setting the Acceleration Control during isochronous transmit to enable the isochronous request fly-by acceleration.

It is not necessary to issue Acceleration Control request when the cycle master is absent from the serial bus. These enhancements are enabled if the Enab\_accel bit in the PHY register is set. The  $\mu$ PD72852 supports Variable Acceleration controlled by the Acceleration Control during power-on reset.

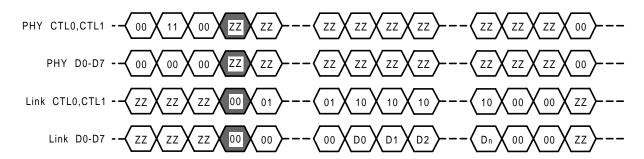

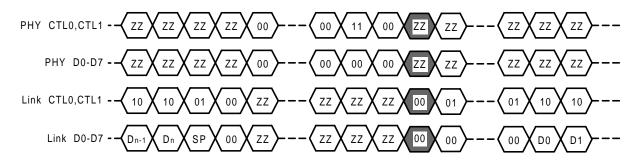

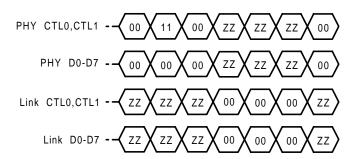

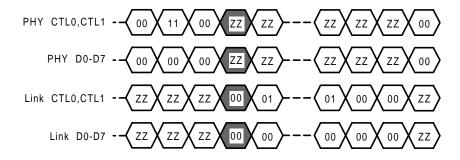

### 4.5 Transmit Status

Pin D0, D1 of the  $\mu$ PD72852 transmits status information to the Link. Status is asserted to CTL while transmitting Status. The status transmission is interrupted if the serial bus receives a packet which contains states other than status to CTL. Between two status transmissions, assert Idle to CTL for at least one SCLK cycle.

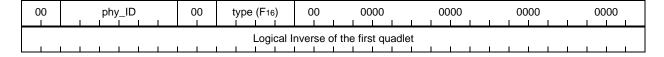

The  $\mu$ PD72852 transmits status in 16 bits as follows:

- In response to the register request

- After deciding the new Physical\_ID for the Self\_ID period resetting the bus (after a Self\_ID packet is transmitted)

The event indication is the only 4-bit transmission of the  $\mu$ PD72852.

Figure 4-4. Status Timing

Table 4-13. Status Data Format

| Bit(s) | Name            | Description                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |