#### 查询IDT72132L35P供应商

与多邦 专业PCB打样工厂 24小时加急出货

CMOS SERIAL-TO-PARALLEL FIFO 2048 x 9

4096 x 9

IDT72132 IDT72142

Integrated Device Technology, Inc.

## FEATURES:

- 35ns parallel-port access time, 45ns cycle time

- 50MHz serial port shift rate

- Expandable in depth and width with no external components

- Programmable word lengths including 8, 9, 16-18, and 32-36 bit using Flexshift<sup>™</sup> serial input without using any additional components

- Multiple status flags: Full, Almost-Full (1/8 from full), Half-Full, Almost Empty (1/8 from empty), and Empty

- Asynchronous and simultaneous read and write operations

- Dual-Port zero fall-through architecture

- · Retransmit capability in single device mode

- Produced with high-performance, low-power CMOS technology

- Available in the 28-pin plastic DIP

- Industrial temperature range (-40°C to +85°C) is available, tested to military electrical specifications

## **DESCRIPTION:**

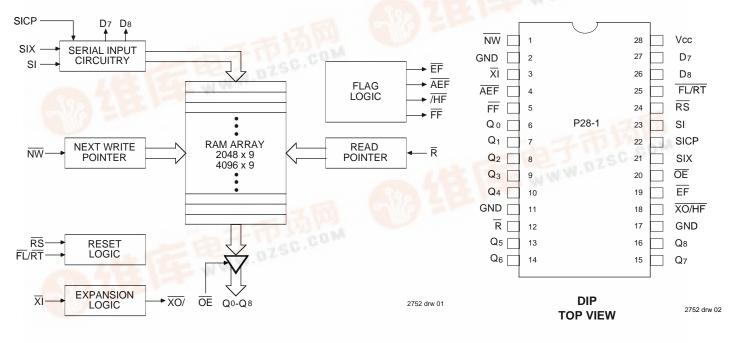

The IDT72132/72142 are high-speed, low-power serial-toparallel FIFOs. These FIFOs are ideally suited to serial communications applications, tape/disk controllers, and local area networks (LANs). The IDT72132/72142 can be configured with the IDTs parallel-to-serial FIFOs (IDT72131/72141) for bidirectional serial data buffering.

The FIFO has a serial input port and a 9-bit parallel output port. Wider and deeper serial-to-parallel data buffers can be built using multiple IDT72132/72142 chips. IDTs unique Flexshift serial expansion logic (SIX,  $\overline{NW}$ ) makes width expansion possible with no additional components. These FIFOs will expand to a variety of word widths including 8, 9, 16, and 32 bits. The IDT72132/142 can also be directly connected for depth expansion.

Five flags are provided to monitor the FIFO. The full and empty flags prevent any FIFO data overflow or underflow conditions. The Almost-Full (7/8), Half-Full, and Almost Empty (1/8) flags signal memory utilization within the FIFO.

The IDT72132/72142 is fabricated using IDTs high-speed submicron CMOS technology.

# FUNCTIONAL BLOCK DIAGRAM

# PIN CONFIGURATION

The DT togo is a registered trademark of Integrated Device Technology, Inc.

COMMERCIAL TEMPERATURE RANGES

# **PIN DESCRIPTIONS**

| Symbol | Name                              | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|-----------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SI     | Serial Input                      | Ι   | Serial data is shifted in least significant bit first. In the serial cascade mode, the Serial Input (SI) pins are tied together and SIX plus D7, D8 determine which device stores the data.                                                                                                                                                                                                                                                                                                      |

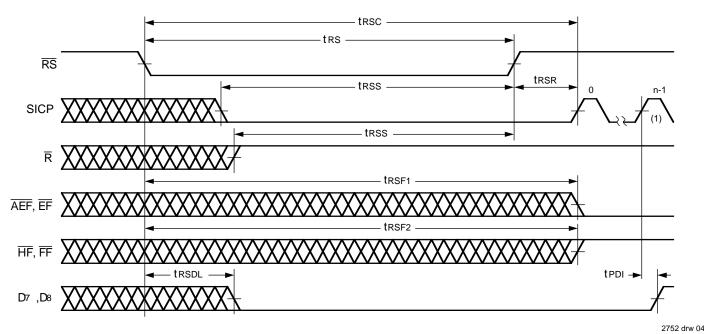

| RS     | Reset                             | Ι   | When $\overline{\text{RS}}$ is set LOW, internal READ and WRITE pointers are set to the first location of the RAM array. $\overline{\text{HF}}$ and $\overline{\text{FF}}$ go HIGH, and $\overline{\text{AEF}}$ , and $\overline{\text{EF}}$ go LOW. A reset is required before an initial WRITE after power-up. $\overline{\text{R}}$ must be HIGH during an $\overline{\text{RS}}$ cycle.                                                                                                      |

| NW     | Next Write                        | I   | To program the Serial In word width , connect $\overline{\text{NW}}$ with one of the Data Set pins (D7, D8).                                                                                                                                                                                                                                                                                                                                                                                     |

| SICP   | Serial Input Clock                | Ι   | Serial data is read into the serial input register on the rising edge of SICP. In both Depth and Serial Word Width Expansion modes, all of the SICP pins are tied together.                                                                                                                                                                                                                                                                                                                      |

| R      | Read                              | Ι   | When READ is LOW, data can be read from the RAM array sequentially, independent of SICP. In order for READ to be active, $\overline{\text{EF}}$ must be HIGH. When the FIFO is empty ( $\overline{\text{EF}}$ -LOW), the internal READ operation is blocked and Q0-Q8 are in a high impedance condition.                                                                                                                                                                                         |

| FL/RT  | First Load/<br>Retransmit         | I   | This is a dual-purpose input. In the single device configuration ( $\overline{XI}$ grounded), activating retransmit ( $\overline{FL/RT}$ -LOW) will set the internal READ pointer to the first location. There is no effect on the WRITE pointer. $\overline{R}$ must be HIGH and SICP must be LOW before setting $\overline{FL/RT}$ LOW. Retransmit is not possible in depth expansion. In the depth expansion configuration, $\overline{FL/RT}$ grounded indicates the first activated device. |

| XI     | Expansion In                      | Ι   | In the single device configuration, $\overline{XI}$ is grounded. In depth expansion or daisy chain expansion, $\overline{XI}$ is connected to $\overline{XO}$ (expansion out) of the previous device.                                                                                                                                                                                                                                                                                            |

| SIX    | Serial Input<br>Expansion         | Ι   | In the Expansion mode, the SIX pin of the least significant device is tied HIGH. The SIX pin of all other devices is connected to the D7 or D8 pin of the previous device. For single device operation, SIX is tied HIGH.                                                                                                                                                                                                                                                                        |

| ŌĒ     | Output Enable                     | Ι   | When $\overline{OE}$ is set LOW, the parallel output buffers receive data from the RAM array. When $\overline{OE}$ is set HIGH, parallel three state buffers inhibit data flow.                                                                                                                                                                                                                                                                                                                  |

| Q0–Q8  | Output Data                       | 0   | Data outputs for 9-bit wide data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FF     | Full Flag                         | 0   | When FF goes LOW, the device is full and data must not be clocked by SICP. When FF is HIGH, the device is not full. See the diagram on page 7 for more details.                                                                                                                                                                                                                                                                                                                                  |

| EF     | Empty Flag                        | 0   | When $\overline{\text{EF}}$ goes LOW, the device is empty and further READ operations are inhibited. When $\overline{\text{EF}}$ is HIGH, the device is not empty.                                                                                                                                                                                                                                                                                                                               |

| AEF    | Almost-Empty/<br>Almost-Full Flag | 0   | When $\overline{\text{AEF}}$ is LOW, the device is empty to 1/8 full or 7/8 to completely full. When $\overline{\text{AEF}}$ is HIGH, the device is greater than 1/8 full, but less than 7/8 full.                                                                                                                                                                                                                                                                                               |

| XO/HF  | Expansion Out/<br>Half-Full Flag  | 0   | This is a dual-purpose output. In the single device configuration ( $\overline{XI}$ grounded), the device is more than half full when $\overline{HF}$ is LOW. In the depth expansion configuration ( $\overline{XO}$ connected to $\overline{XI}$ of the next device), a pulse is sent from $\overline{XO}$ to $\overline{XI}$ when the last location in the RAM array is filled.                                                                                                                |

| D7, D8 | Data Set                          | 0   | The appropriate Data Set pin (D7, D8) is connected to $\overline{NW}$ to program the Serial In data word width. For example: D7 - $\overline{NW}$ programs a 8-bit word width, D8 - $\overline{NW}$ programs a 9-bit word width, etc.                                                                                                                                                                                                                                                            |

| Vcc    | Power Supply                      |     | Single Power Supply of 5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GND    | Ground                            |     | Three grounds at 0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# **STATUS FLAGS**

| Number of W | /ords in FIFO |           |            |           |             |

|-------------|---------------|-----------|------------|-----------|-------------|

| IDT72132    | IDT72142      | <u>FF</u> | <u>AEF</u> | <u>HF</u> | <u>EF</u>   |

| 0           | 0             | Н         | L          | Н         | L           |

| 1-255       | 1-511         | Н         | L          | Н         | Н           |

| 256-1024    | 512-2048      | Н         | Н          | Н         | Н           |

| 1025-1792   | 2049-3584     | Н         | Н          | L         | Н           |

| 1793-2047   | 3585-4095     | Н         | L          | L         | Н           |

| 2048        | 4096          | L         | L          | L         | Н           |

|             | •             |           |            |           | 2752 tbl 02 |

2752 tbl 01

| Symbol | Rating                                     | Commercial   | Unit |

|--------|--------------------------------------------|--------------|------|

| Vterm  | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0 | V    |

| TA     | Operating<br>Temperature                   | 0 to +70     | °C   |

| TBIAS  | Temperature<br>Under Bias                  | -55 to +125  | °C   |

| Тѕтс   | Storage<br>Temperature                     | -55 to +125  | °C   |

| Ιουτ   | DC Output<br>Current                       | 50           | mA   |

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

NOTE:

2752 tbl 03

Stresses greater than those listed under ABSOLUTE MAXIMUM 1. RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# CAPACITANCE (TA = +25°C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit        |

|--------|--------------------------|------------|------|-------------|

| CIN    | Input Capacitance        | VIN = 0V   | 10   | pF          |

| Соит   | Output Capacitance       | Vout = 0V  | 12   | pF          |

| NOTE:  |                          |            | 2    | 2752 tbl 05 |

NOTE:

1. This parameter is sampled and not 100% tested.

# DC ELECTRICAL CHARACTERISTICS

(Commercial: Vcc =  $5.0V \pm 10\%$ , TA = 0°C to +70°C)

|                          |                                                                                                                     |      | IDT72132/IDT72142<br>Commercial |      |      |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------|------|---------------------------------|------|------|--|

| Symbol                   | Parameter                                                                                                           | Min. | Тур.                            | Max. | Unit |  |

| IIL <sup>(1)</sup>       | Input Leakage Current<br>(Any Input)                                                                                | -1   | —                               | 1    | μΑ   |  |

| IOL <sup>(2)</sup>       | Output Leakage Current                                                                                              | -10  | _                               | 10   | μΑ   |  |

| Vон                      | Output Logic "1" Voltage,<br>Io∪⊤ = -2mA                                                                            | 2.4  | —                               | -    | V    |  |

| Vol                      | Output Logic "0" Voltage,<br>Io∪⊤ = 8mA                                                                             | —    | —                               | 0.4  | V    |  |

| ICC1 <sup>(3)</sup>      | Power Supply Current                                                                                                |      | 90                              | 140  | mA   |  |

| ICC2 <sup>(3)</sup>      | Average Standby Current<br>( $\overline{R} = \overline{RS} = \overline{FL}/\overline{RT} = V_{H}$ )<br>(SICP = VIL) | _    | 8                               | 12   | mA   |  |

| ICC3(L) <sup>(3,4)</sup> | Power Down Current                                                                                                  | _    |                                 | 2    | mA   |  |

#### NOTES:

1. Measurements with 0.4  $\leq$  VIN  $\leq$  VCC.

2752 tbl 06

**COMMERCIAL TEMPERATURE RANGES**

2752 tbl 04

# **RECOMMENDED DC OPERATING CONDITIONS**

| Symbol             | Parameter                        | Min. | Тур. | Max. | Unit |  |  |  |  |

|--------------------|----------------------------------|------|------|------|------|--|--|--|--|

| Vcc                | Commercial Supply<br>Voltage     | 4.5  | 5.0  | 5.5  | V    |  |  |  |  |

| GND                | Supply Voltage                   | 0    | 0    | 0    | V    |  |  |  |  |

| Viн                | Input High Voltage<br>Commercial | 2.0  | _    |      | V    |  |  |  |  |

| VIL <sup>(1)</sup> | Input Low Voltage                | _    | —    | 0.8  | V    |  |  |  |  |

#### NOTE:

1. 1.5V undershoots are allowed for 10ns once per cycle.

R ≤ VIL, 0.4 ≤ VOUT ≤ VCC.

Icc measurements are made with outputs open.

## **AC ELECTRICAL CHARACTERISTICS**

(Commercial: Vcc =  $5.0V \pm 10\%$ , TA =  $0^{\circ}C$  to + $70^{\circ}C$ )

|          |                                                      | Commercial<br>IDT72132L35 IDT72132L50 |          |        |      |           |

|----------|------------------------------------------------------|---------------------------------------|----------|--------|------|-----------|

|          |                                                      | IDT72                                 |          |        |      |           |

| <b>.</b> |                                                      |                                       | 142L35   | IDT721 |      | ·         |

| Symbol   | Parameter                                            | Min.                                  | Max.     | Min.   | Max. | Unit      |

| ts       | Parallel Shift Frequency                             | —                                     | 22.2     | —      | 15   | MHz       |

| tSICP    | Serial-InShift Frequency                             | —                                     | 50       | —      | 40   | MHz       |

|          | EL OUTPUT TIMINGS                                    | 1                                     | 1        | 1      |      | . <u></u> |

| tA       | Access Time                                          | —                                     | 35       | —      | 50   | ns        |

| trr      | Read Recovery Time                                   | 10                                    |          | 15     |      | ns        |

| tRPW     | Read Pulse Width                                     | 35                                    | —        | 50     | —    | ns        |

| tRC      | Read Cycle Time                                      | 45                                    | —        | 65     | —    | ns        |

| trlz     | Read Pulse LOW to Data Bus at Low-Z <sup>(1)</sup>   | 5                                     | _        | 10     |      | ns        |

| trhz     | Read Pulse HIGH to Data Bus at High-Z <sup>(1)</sup> | —                                     | 20       | —      | 30   | ns        |

| tDV      | Data Valid from Read Pulse HIGH                      | 5                                     | —        | 5      | _    | ns        |

| toehz    | Output Enable to High-Z (Disable) <sup>(1)</sup>     | —                                     | 15       | —      | 15   | ns        |

| toelz    | Output Enable to Low-Z (Enable) <sup>(1)</sup>       | 5                                     | _        | 5      | _    | ns        |

| taoe     | Output Enable to Data Valid (Q0-8)                   | —                                     | 20       | —      | 22   | ns        |

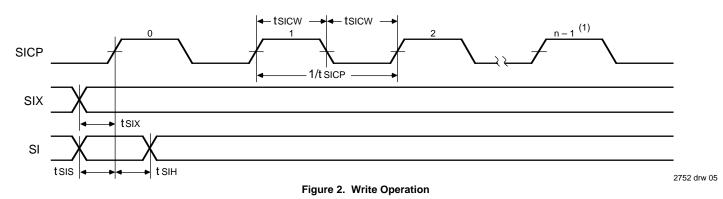

| SERIAL   | INPUT TIMINGS                                        |                                       |          | ·      |      |           |

| tsis     | Serial Data in Set-Up Time to SICP Rising Edge       | 12                                    | —        | 15     | —    | ns        |

| tsih     | Serial Data in Hold Time to SICP Rising Edge         | 0                                     | —        | 0      | —    | ns        |

| tsıx     | SIX Set-Up Time to SICP Rising Edge                  | 5                                     | —        | 5      | —    | ns        |

| tsicw    | Serial-In Clock Width HIGH/LOW                       | 8                                     | -        | 10     | —    | ns        |

| FLAG TI  | MINGS                                                |                                       |          | 1      |      | 1         |

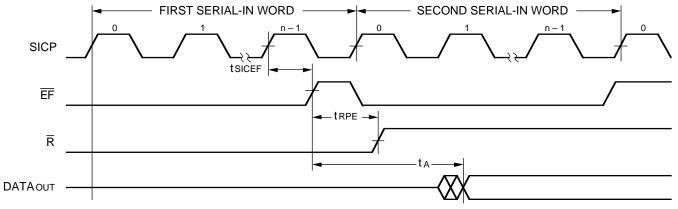

| tSICEF   | SICP Rising Edge (Last Bit - First Word) to EF HIGH  | —                                     | 45       | —      | 65   | ns        |

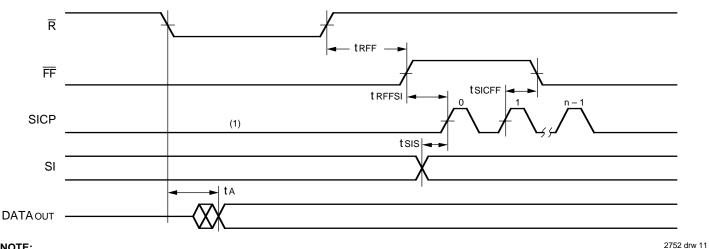

| tSICFF   | SICP Rising Edge (Bit 1 - Last Word) to FF LOW       | _                                     | 30       | _      | 40   | ns        |

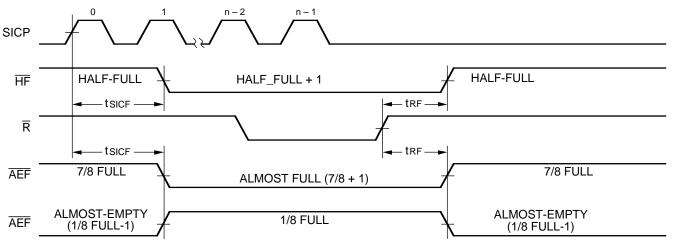

| tSICF    | SICP Rising Edge to HF, AEF                          | _                                     | 45       | _      | 65   | ns        |

| tRFFSI   | Recovery Time SICP After FF Goes HIGH                | 15                                    | _        | 15     | _    | ns        |

| tREF     | Read LOW to EF LOW                                   | _                                     | 30       | _      | 45   | ns        |

| tRFF     | Read HIGH to FF HIGH                                 | _                                     | 30       | _      | 45   | ns        |

| tRF      | Read HIGH to Transitioning HF and AEF                | _                                     | 45       | _      | 65   | ns        |

| tRPE     | Read Pulse Width After EF HIGH                       | 35                                    | _        | 50     |      | ns        |

| RESET 1  |                                                      |                                       |          |        |      |           |

| tRSC     | Reset Cycle Time                                     | 45                                    | _        | 65     | _    | ns        |

| tRS      | Reset Pulse Width                                    | 35                                    |          | 50     | _    | ns        |

| tRSS     | Reset Set-up Time                                    | 35                                    | _        | 50     | _    | ns        |

| tRSR     | Reset Recovery Time                                  | 10                                    |          | 15     |      | ns        |

| tRSF1    | Reset to EF and AEF LOW                              |                                       | 45       |        | 65   | ns        |

| tRSF2    | Reset to HF and FF HIGH                              |                                       | 45       |        | 65   | ns        |

| tRSDL    | Reset to D LOW                                       | 20                                    |          | 35     |      | ns        |

| tPOI     | SICP Rising Edge to D                                | 5                                     | 17       | 5      | 20   | ns        |

|          | ISMIT TIMINGS                                        | 5                                     | 17       | 5      | 20   | 115       |

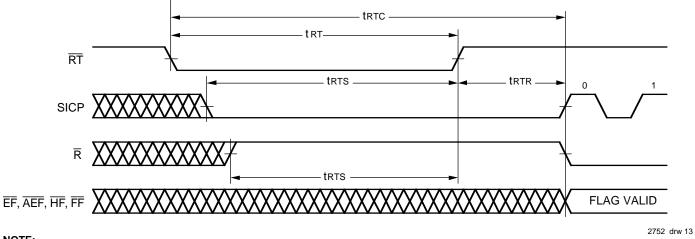

| TRTC     | Retransmit Cycle Time                                | 45                                    |          | 65     |      | 20        |

| tRT      | Retransmit Pulse Width                               | 45<br>35                              |          | 50     |      | ns        |

|          | Retransmit Set-up Time                               | 35                                    |          | 50     |      | ns        |

|          |                                                      | 10                                    | <u> </u> | 15     |      | ns        |

|          |                                                      | 10                                    | —        | 15     |      | ns        |

| -        |                                                      |                                       | 40       | 1      | 50   |           |

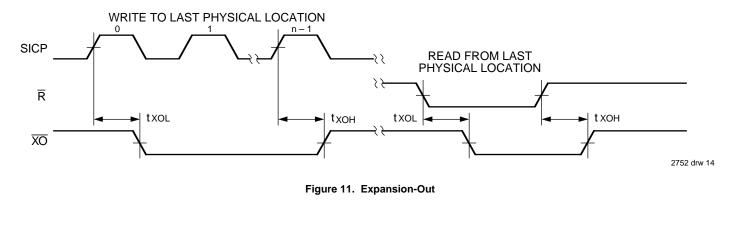

| txol     | Read/Write to XO LOW                                 | —                                     | 40       | —      | 50   | ns        |

| tхон     | Read/Write to XO HIGH                                |                                       | 40       |        | 50   | ns        |

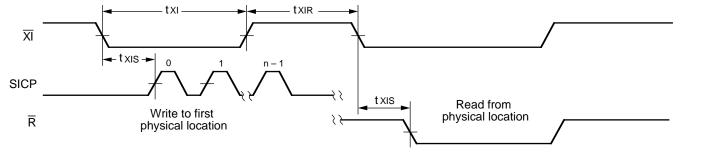

| txı      | XI Pulse Width                                       | 35                                    |          | 50     |      | ns        |

| txir     | XI Recovery Time                                     | 10                                    | —        | 10     | —    | ns        |

| txis     | XI Set-up Time                                       | 16                                    | —        | 15     | —    | ns        |

NOTE:

1. Guaranteed by design minimum times, not tested

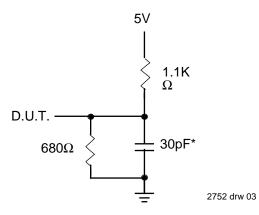

## AC TEST CONDITIONS

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise/Fall Times         | 5ns          |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| Output Load                   | See Figure A |

|                               |              |

2752 tbl 08

or equivalent circuit

Figure A. Output Load \*Includies jig and scope capacitances

# FUNCTIONAL DESCRIPTION

## **Serial Data Input**

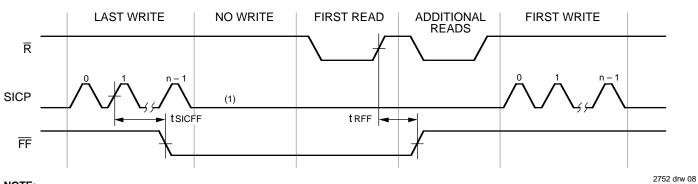

The serial data is input on the SI pin. The data is clocked in on the rising edge of SICP providing the Full Flag (FF) is not asserted. If the Full Flag is asserted then the next parallel data word is inhibited from moving into the RAM array. NOTE: SICP should not be clocked once the last bit of the last word has been shifted in, as indicated by NW HIGH and FF LOW. If it is, then the input data will be lost.

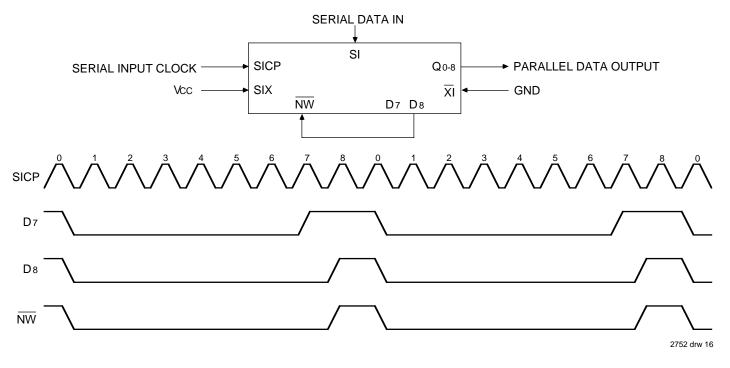

The serial word is shifted in Least Significant Bit first. Thus, when the FIFO is read, the Least Significant Bit will come out on Q0 and the second bit is on Q1 and so on. The serial word width must be programmed by connecting the appropriate Data Set line (D7, D8) to the  $\overline{NW}$  input. The data set lines are taps off a digital delay line. Selecting one of these taps programs the width of the serial word to be written in.

#### **Parallel Data Output**

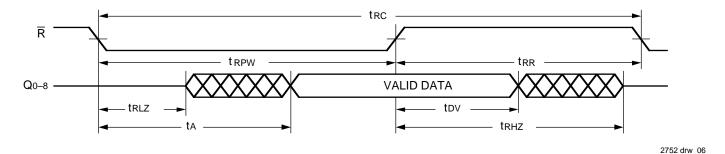

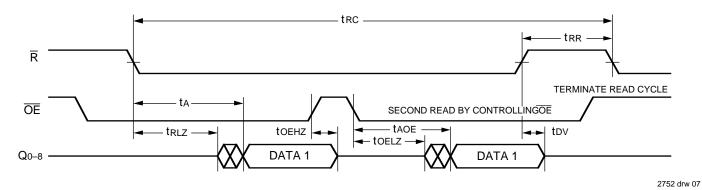

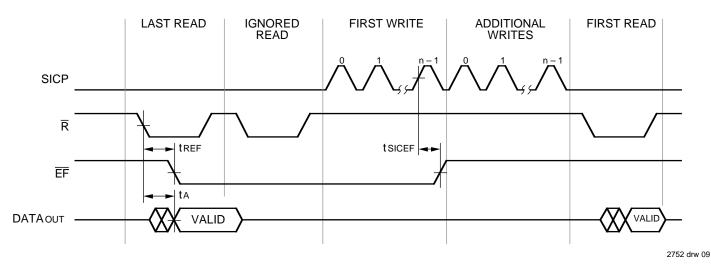

A read cycle is initiated on the falling edge of Read (R) provided the Empty Flag is not set. The output data is accessed on a first-in/first-out basis, independent of the ongoing write operations. The data is available tA after the falling edge of  $\overline{R}$  and the output bus Q goes into high impedance after  $\overline{R}$  goes HIGH.

Alternately, the user can access the FIFO by keeping  $\overline{R}$  LOW and enabling data on the bus by asserting Output Enable ( $\overline{OE}$ ). When  $\overline{R}$  is LOW, the  $\overline{OE}$  signal enables data on the output bus. When  $\overline{R}$  is LOW and  $\overline{OE}$  is HIGH, the output bus is three-stated. When  $\overline{R}$  is HIGH, the output bus is disabled irrespective of  $\overline{OE}$ .

NOTE: 1. Input bits are numbered 0 to n-1. D7 and D8 correspond to n=8 and n=9 respectively

## COMMERCIAL TEMPERATURE RANGES

#### NOTE:

1. Input bits are numbered 0 to n-1.

Figure 3. Read Operation

Figure 4. Output Enable Timings

COMMERCIAL TEMPERATURE RANGES

#### NOTE:

1. After FF goes LOW and the last bit of the final word has been clocked in, SICP should not be clocked until FF goes HIGH.

Figure 5. Full Flag from Last Write to First Read

Figure 6. Empty Flag from Last Read to First Write

Figure 7. Empty Boundry Condition Timing

**COMMERCIAL TEMPERATURE RANGES**

## NOTE:

1. After FF goes LOW and the last bit of the final word has been clocked in, SICP should not be clocked until FF goes HIGH.

Figure 8. Full Boundry Condition Timing

2752 drw 12

Figure 9. Half Full, Almost Full and Almost Empty Timings

# NOTE:

1. EF, AEF, HF and FF may change status during Retransmit, but flags will be valid at tRTC.

2752 drw 15

Figure 12. Expansion-In

# **OPERATING CONFIGURATIONS**

## **Single Device Configuration**

In the standalone case, the SIX line is tied HIGH and not used. On the first LOW-to-HIGH of the SICP clock, both of the

Data Set lines (D7, D8) go LOW and a new serial word is started. The Data Set lines then go HIGH on the equivalent SICP clock pulse. This continues until the D line connected to  $\overline{NW}$  goes HIGH completing the serial word. The cycle is then repeated with the next LOW-to-HIGH transition of SICP.

Figure 13. Nine-Bit Word Single Device Configuration

# TRUTH TABLES TABLE 1: RESET AND RETRANSMIT SINGLE DEVICE CONFIGURATION/WIDTH EXPANSION MODE

|            | Inputs |       | Interna | Outputs                  |                          |         |    |    |

|------------|--------|-------|---------|--------------------------|--------------------------|---------|----|----|

| Mode       | RS     | FL/RT | XI      | Read Pointer             | Write Pointer            | AEF, EF | FF | ĦF |

| Reset      | 0      | Х     | 0       | Location Zero            | Location Zero            | 0       | 1  | 1  |

| Retransmit | 1      | 0     | 0       | Location Zero            | Unchanged                | Х       | Х  | Х  |

| Read/Write | 1      | 1     | 0       | Increment <sup>(1)</sup> | Increment <sup>(1)</sup> | Х       | Х  | Х  |

#### NOTE:

1. Pointer will increment if appropriate flag is HIGH.

2752 tbl 09

## COMMERCIAL TEMPERATURE RANGES

#### **COMMERCIAL TEMPERATURE RANGES**

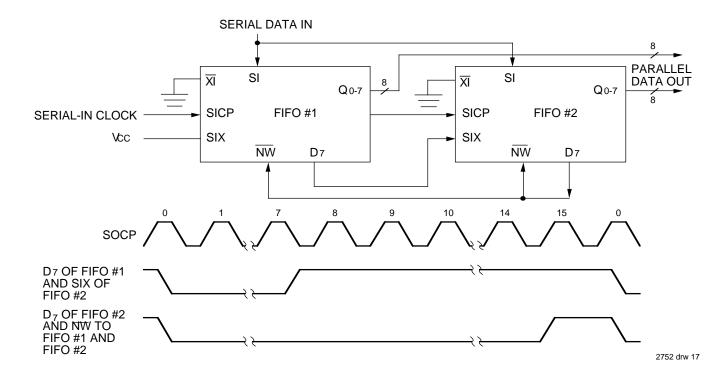

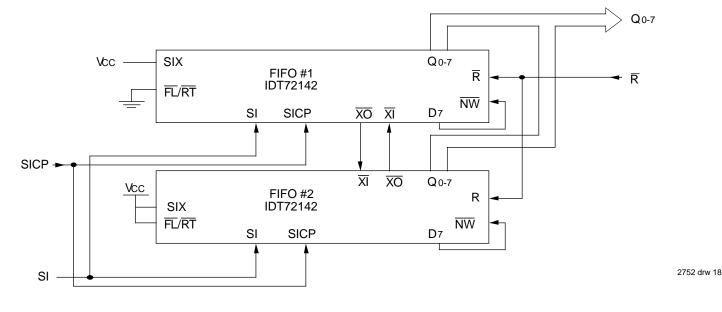

## Width Expansion Configuration

In the cascaded case, word widths of more than 9 bits can be achieved by using more than one device. By tying the SIX line of the least significant device HIGH and the SIX of the subsequent devices to the appropriate Data Set lines of the previous devices, a cascaded serial word is achieved.

On the first LOW-to-HIGH clock edge of SICP, both the Data Set lines go LOW. Just as in the standalone case, on each corresponding clock cycle, the equivalent Data Set line goes HIGH in order of least to most significant.

Figure 14. Serial-In to Parallel-Out Data of 16 Bits

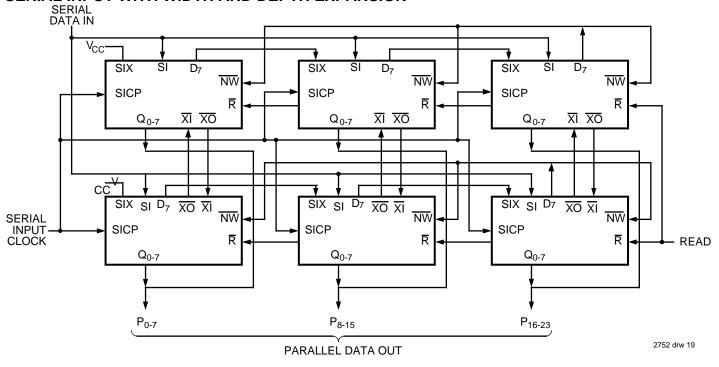

## Depth Expansion (Daisy Chain) Mode

The IDT72132/42 can be easily adapted to applications where the requirements are for greater than 2048/4096 words. Figure 15 demonstrates Depth Expansion using three IDT72132/42. Any depth can be attained by adding additional IDT72132/42 operates in the Depth Expansion configuration when the following conditions are met:

The first device must be designated by grounding the First Load (FL) control input.

## COMMERCIAL TEMPERATURE RANGES

- 2. All other devices must have  $\overline{FL}$  in the high state.

- 3. The Expansion Out  $(\overline{XO})$  pin and Expansion In  $(\overline{XI})$  pin of each device must be tied together.

- External logic is needed to generate a composite Full Flag (FF) and Empty Flag (EF). This requires the OR-ing of all EFs and OR-ing of all FFs (i.e., all must be set to generate the correct composite (FF) or (EF).

- 5. The Retransmit ( $\overline{RT}$ ) function and Half-Full Flag ( $\overline{HF}$ ) are not available in the Depth Expansion mode.

Figure 15. An 8K x 8 Serial-In Parallel-Out FIFO

# TABLE 2: RESET AND FIRST LOAD TRUTH TABLE —DEPTH EXPANSION/COMPOUND EXPANSION MODE

|                            |    | Inputs |     | Internal Status |               | 0  | utputs |

|----------------------------|----|--------|-----|-----------------|---------------|----|--------|

| Mode                       | RS | FL/RT  | XĪ  | Read Pointer    | Write Pointer | ĒF | FF     |

| Reset-First<br>Device      | 0  | 0      | (1) | Location Zero   | Location Zero | 0  | 1      |

| Reset all<br>Other Devices | 0  | 1      | (1) | Location Zero   | Location Zero | 0  | 1      |

| Read/Write                 | 1  | Х      | (1) | Х               | Х             | Х  | Х      |

#### NOTES:

1.  $\overline{XI}$  is connected to  $\overline{XO}$  of the previous device.

2.  $\overline{\text{RS}}$  = Reset Input,  $\overline{\text{FL}}/\overline{\text{RT}}$  = First Load/Retransmit,  $\overline{\text{EF}}$  = Empty Flag Ouput,  $\overline{\text{FF}}$  = Full Flag Output,  $\overline{\text{XI}}$  = Expansion Input.

2752 tbl 10

# SERIAL INPUT WITH WIDTH AND DEPTH EXPANSION

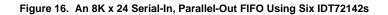

# **ORDERING INFORMATION**