急出伤

# HI-508L/HI-509L

Single 8/Differential 4 Channel CMOS Analog Multiplexers With Latches And Overvoltage Protection

#### DESCRIPTION **FEATURES** These monolithic CMOS multiplexers feature on-board address latches, plus · Analog Overvoltage protection overvoltage protection for the analog inputs and the output as well. Each model includes digital inputs for channel selection and an Enable input for de- Resettable Latches (RS) vice selection under program control. In addition, Write (WR) and Reset (RS) inputs allow the program to store or clear the channel address TTL/DTL and CMOS Compatible The overvoltage performance of these multiplexers is particularly useful in re- Failsafe for conditions of Overvoltage & Loss of Power dundant systems, where the inputs and output must present a high impedance when power is off. This is achieved by a switch cell with three MOSFET's in series, rather than the conventional transmission gate design. No SCR Latch-up Each channel can withstand overvoltage to +25VDC with respect to ground · Break-before-make switching with power ON or OFF. An OFF channel remains OFF in the presence of overvoltage. If the channel is ON, output voltage is clamped below the supply rail, Microprocessor Bus compatible which protects the load circuit. The HI-508L offers 8 single-ended channels, and the HI-509L is a 4 channel dif- Very low leakage - ID(off) ≤ 4nA (typ) over full temp range ferential version. The recommended supply voltages are 15V, though operation at reduced levels or with a single supply may also be implemented. The Access time - t<sub>A</sub> = 500nS (typ) package is a 18 pin ceramic or plastic DIP. Minimum write pulse width (WR) = 300 nS Each product is specified for the commercial temperature range (0°C to 75°C, -5 suffix) and the military range (-55°C to + 125°C, -2 suffix). Military high reli- OFF isolation = -100dB, typ @ 10kHz ability burned-in product is available as a "-8" suffix. FUNCTIONAL DIAGRAM **PINOUT** HI-508L HI-508L **ENABLE** -VSUPPLY IN 2 IN 4 HI-509L HI-509L WR ENABLE GND + VSHPPLY VSUPPLY IN 2A **IN 3B**

IN 4B OUT B

## **SPECIFICATIONS**

### **ABSOLUTE MAXIMUM RATINGS** (Note 1)

Supply Voltage Between Pins 4 and 14 (15) Digital Input Overvoltage, VA, VEN, VRS, VWR;

V supply (+) V supply ( – ) Analog Overvoltage Input to Ground

Total Power Dissipation\* (Package)

44V Operating Temperature

> HI-508L/509L-2 HI-508L/509L-5

- 55°C to 125°C 0°C to 75°C

-65°C to +150°C Storage Temperature

1200mW \*Derate-8mW/°C above  $T_A = +75$ °C

+ 4V

- 4V

±25VDC

## ELECTRICAL CHARACTERISTICS (Unless otherwise specified)

+ V supply = 15V, - V supply = -15V, VAH (Logic High) = 2.0V, VAL (Logic Low) = 0.8V

|                                                                        | HI-508L/509L-2<br>- 55°C to + 125°C |      |           |      | HI-508L/509L-5<br>0°C to +75°C |      |      |                                                  |

|------------------------------------------------------------------------|-------------------------------------|------|-----------|------|--------------------------------|------|------|--------------------------------------------------|

| PARAMETER                                                              | TEMP                                | MIN  | TYP       | MAX  | MIN                            | TYP  | MAX  | UNIT                                             |

| ANALOG CHANNEL CHARACTERISTICS                                         |                                     |      |           |      |                                |      |      |                                                  |

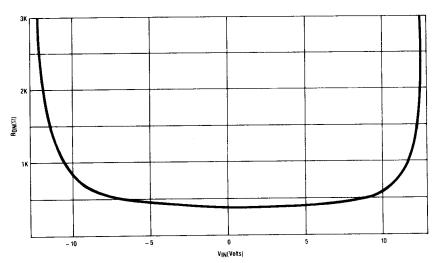

| Vs Analog Signal Range                                                 | Full                                |      | ± 10      |      |                                | ± 10 |      | l v                                              |

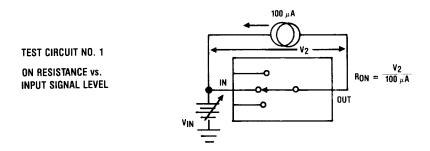

| RON, ON Resistance (Note 2)                                            | + 25°C                              |      |           | 1.2  |                                |      | 1.5  | ΚΩ                                               |

| (1111)                                                                 | Full                                |      |           | 1.8  |                                |      | 1.8  | ΚΩ                                               |

| ΔR <sub>ON</sub> , Change In R <sub>ON</sub> (Note 3) between channels | +25°C                               |      | 5         |      |                                | 5    |      | %                                                |

| IS(off), OFF input leakage current                                     | +25°C                               |      |           | 10   |                                |      | 10   | nA                                               |

| 3(0)                                                                   | Full                                |      | 5         | 50   |                                | 5    | 50   | nA                                               |

| D(off). OFF output leakage current                                     | + 25°C                              |      |           | 10   |                                |      | 10   | nA                                               |

| HI-508L                                                                | Full                                |      | 4         | 100  |                                | 4    | 100  | nA                                               |

| HI-509L                                                                | Full                                |      | 2         | 50   |                                | 2    | 50   | nΑ                                               |

| D(On), ON Channel leakage current                                      | +25°C                               |      | _         | 10   |                                | -    | 10   | nA                                               |

| HI-508L                                                                | Full                                |      | 5         | 100  | 1                              | 5    | 100  | nA                                               |

| HI-509L                                                                | Full                                |      | 2         | 50   |                                | 2    | 50   | nA                                               |

| FAULT CHARACTERISTICS                                                  |                                     |      |           |      |                                |      |      | <del>                                     </del> |

| S(Off), with Power OFF                                                 | Full                                |      | 10        | 1000 |                                | 10   | 5000 |                                                  |

|                                                                        | Full                                |      | 10        | 750  |                                |      |      | nA                                               |

| S(Off), overvoltage (Note 4)                                           | +25°C                               |      | 10        | 100  | 1                              | 10   | 2500 | nA                                               |

| D(Off), with input over-                                               | 1 1                                 |      |           | 750  |                                | 5    | 0500 | nA                                               |

| voltage applied (Note 4)                                               | Full                                |      | 10        | 750  |                                | 10   | 2500 | nA                                               |

| DIGITAL INPUT CHARACTERISTICS                                          |                                     |      |           |      |                                |      |      |                                                  |

| V <sub>AL</sub> , Input Low Threshold                                  | Full                                |      | 1.4       | 0.8  |                                | 1.4  | 0.8  | ٧                                                |

| V <sub>AH</sub> , Input High Threshold                                 | Full                                | 2.0  | 1.4       |      | 2.0                            | 1.4  |      | V                                                |

| IAH, Input High Current (Note 5)                                       | Full                                |      | 10        | 40   |                                | 10   | 40   | μΑ                                               |

| AL, Input Low Current (Note 5)                                         | Full                                |      | 40        | 200  |                                | 40   | 200  | μΑ                                               |

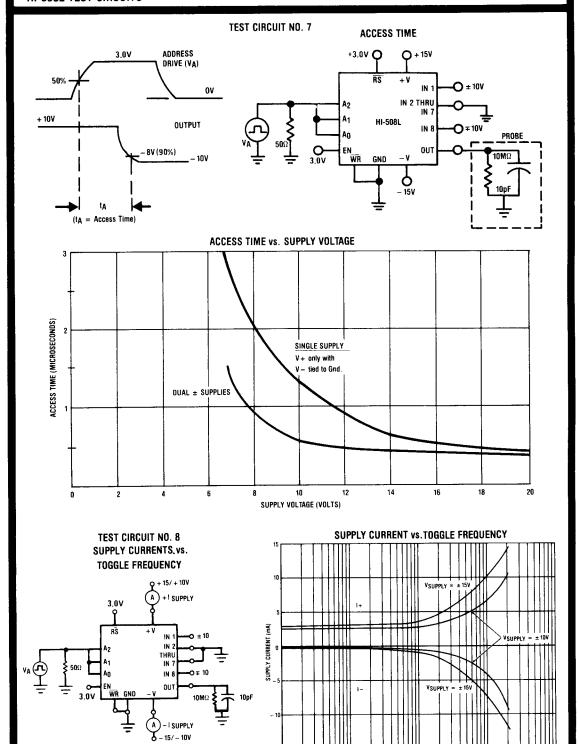

| DYNAMIC SWITCHING CHARACTERISTICS                                      | (Note 6)                            |      |           |      |                                |      |      |                                                  |

| ta, Access Time                                                        | 1 +25°C                             |      | 0.5       | 1.0  |                                | 0.5  | 1.0  | μS                                               |

| OPEN, Break-Before-Make                                                | +25°C                               | .025 | 0.1       | -    | .025                           | 0.1  |      | μS                                               |

| ON, (EN), Enable Delay (ON)                                            | +25°C                               |      | 0.5       | 1.0  |                                | 0.5  | 1.0  | μS                                               |

| tore (EN), Enable                                                      | +25°C                               |      | 0.5       | 1.0  |                                | 0.5  | 1.0  | μS                                               |

| Delay (OFF)                                                            | '25 0                               |      | 0.0       | 1.0  |                                | 0.5  | 1.0  | μο                                               |

| Settling Time (±0.1%)                                                  | +25°C                               |      | 1.0       |      |                                | 1.0  |      | c                                                |

| (±0.01%)                                                               | +25°C                               |      | 1.75      |      |                                | 1.75 |      | μS<br>μS                                         |

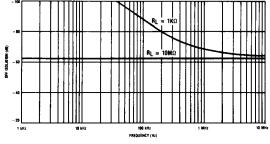

| OFF Isolation (Note 7)                                                 | +25°C                               | 50   | 68        |      | 50                             | 68   |      | μS<br>dB                                         |

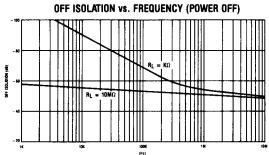

| OFF Isolation POWER OFF (Note 8)                                       | +25°C                               | 30   | <b>56</b> |      | JU                             | 56   |      | dB<br>dB                                         |

|                                                                        | +25°C                               |      | 100<br>5  |      |                                | 1    |      |                                                  |

| CS(Off), Channel Input Cap.                                            | +23-0                               |      | J         |      |                                | 5    |      | pF                                               |

| CD(Off), Channel Output Cap.<br>HI-508L                                | 12500                               |      | 0.5       |      |                                |      |      |                                                  |

|                                                                        | +25°C                               |      | 25        |      |                                | 25   |      | pF                                               |

| HI-509L                                                                | +25°C                               |      | 12        |      |                                | 12   |      | pF                                               |

| CA, Digital Input Capacitance                                          | +25°C                               |      | 5         |      |                                | 5    |      | pF                                               |

| CDS(Off), Input to Output capacitance                                  | +25°C                               |      | 0.1       |      |                                | 0.1  |      | pF                                               |

| POWER REQUIREMENTS                                                     |                                     |      |           |      |                                |      |      |                                                  |

| PD, Power Dissipation (Note 9)                                         | Full                                |      | 60        | 100  |                                | 60   | 100  | mW                                               |

| +, Current Pin 14 (Note 9)                                             | Full                                |      | 3.7       | 6.0  |                                | 3.7  | 6.0  | mA                                               |

| - , Current Pin 4 (Note 9)                                             | Full                                |      | 0.3       | 0.6  |                                | 0.3  | 0.6  | mA                                               |

NOTES 1 Absolute maximum ratings are limiting values, applied individually, beyond which the serviceability of the entering the part of fractional object on the control and part of fractional object on sarry more active or on times and the part of the part o

RON(Avg.)

<sup>5.</sup> IAH and IAL tested at 2.4V and 0.4 V respectively

<sup>6</sup> For measurements in this section, input logic levels are 3.0V (High) and 0V (Low).

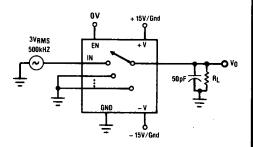

7. VCN = 0.8V. N = 18C), C, = 15pF, VS = 7Vms, 1 = 500kt;

Off isolation = 20 log [YD]

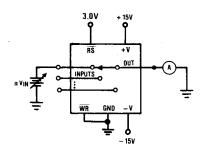

<sup>8.</sup> V + , V = 0V, R<sub>L</sub> = 1K(2 C<sub>L</sub> = 50pF, V<sub>S</sub> = 3Yrms, I = 500 kHz. 9. See Test Circuit #8 for high toggle trequency applications.

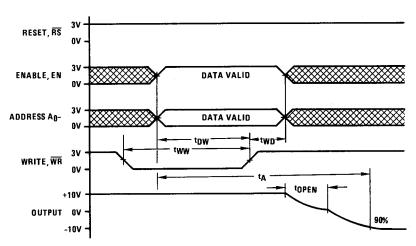

#### MINIMUM TIMING REQUIREMENTS

| PARAMETER                                              | MIN LIMITS<br>FULL TEMP RANGE | UNITS |  |

|--------------------------------------------------------|-------------------------------|-------|--|

| tww. Write Pulse Width                                 | 300                           | nS    |  |

| tow. A. EN Data Valid To WRITE<br>(Stabilization Time) | 225                           | nS    |  |

| twD, A, EN Data Valid After Write<br>(hold Time)       | 100                           | nS    |  |

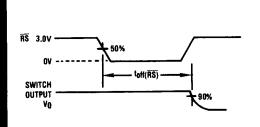

| tps. RESET pulse width                                 | 400                           | nS    |  |

| toff (RS) Reset Delay                                  | 1000                          | nS    |  |

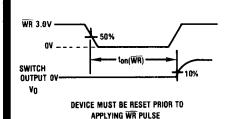

| ton (WR) Write Turn-on Time                            | 1000                          | nS    |  |

#### **TIMING REQUIREMENTS**

- 1. +VSUPPLY = +15V; -VSUPPLY = -15V.

- 2. Logic Levels: VAL = 0V; VAH = +3.0V.

- 3. Time intervals are measured between 50% levels unless otherwise noted.

- 4. Minimum values for  $t\overline{RS}$ , tDW, tWW and tWD are guaranteed separately but not simultaneously.

Figure 1

## SCHEMATIC DIAGRAM

#### TRUTH TABLES

508L

| A2 | A1 | A0 | EN | WR           | RS | OUTPUT - ON CHANNEL    |

|----|----|----|----|--------------|----|------------------------|

| Χ  | Х  | х  | L  | L            | Н  | None                   |

| Χ  | Х  | Х  | X  | _ <b>J</b> _ | н  | Previous ON Channel.   |

| Χ  | Х  | Х  | X  | X            | L  | None (latches cleared) |

| L  | L  | L  | н  | Ł            | Н  | Channel 1              |

| L  | L  | H  | Н  | L            | Н  | Channel 2              |

| L  | Н  | L  | н  | L            | н  | Channel 3              |

| L  | Н  | Н  | H  | L            | Н  | Channel 4              |

| Н  | Ł  | L  | Н  | L            | Н  | Channel 5              |

| Н  | L  | н  | н  | L            | н  | Channel 6              |

| Н  | Н  | L  | Н  | L            | н  | Channel 7              |

| Н  | н  | Н  | Н  | L            | Н  | Channel 8              |

509L

| A1 | A0 | EN | WR       | RS | OUTPUT - ON CHANNEL PAIR |

|----|----|----|----------|----|--------------------------|

| Х  | Х  | L  | L        | Н  | None                     |

| X  | X  | Х  | <b>_</b> | Н  | Previous ON Channel.     |

| Χ  | Х  | x  | X        | L  | None (latches cleared)   |

| L  | L  | н  | L        | Н  | Channel 1A and 1B        |

| L  | Н  | н  | L        | н  | Channel 2A and 2B        |

| Н  | L  | Н  | L        | н  | Channel 3A and 3B        |

| H  | Н  | Н  | L        | Н  | Channel 4A and 4B        |

|    |    |    |          |    |                          |

### **DESCRIPTION AND APPLICATION**

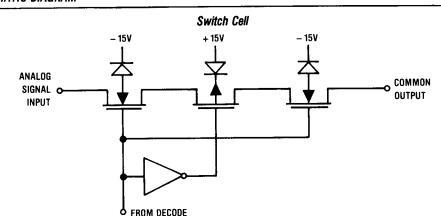

The switch cell of HI-508L/509L has a different structure than earlier Harris designs (HI-508. HI508A). The new switch (Figure 2) consists of an N-channel, P-channel and N-channel MOSFET in series, as opposed to the transmission gate configuration with an N and P-channel device in parallel. The series N-P-N switch offers higher Off isolation with power off, and better fault performance. Channel overvoltage protection is inherent since one of the three MOSFETs turn off in the presence of overvoltage. This turn-off process begins well below the supply rail so the V $_{\rm IN}$  range is less than the power supply range. Electrical performance is guaranteed to  $\pm$  10V for each channel, and the usable range extends above  $\pm$  11

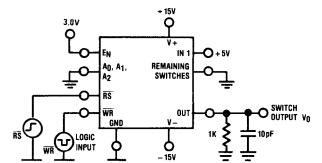

The address inputs  $A_0$ ,  $A_1$ ,  $A_2$ , and ENABLE are latched into an internal buffer when  $\overline{WR}$  goes high. Each latch output is level shifted into the decode section, which activates the appropriate channel. The device may be reset (all channels OFF) by taking  $\overline{RS}$  low. Usually,  $\overline{RS}$  is tied to the system RESET line, to assure that all channels are  $\overline{OFF}$  following a turn-on of power. The reset function overrides all others, just as  $\overline{WR}$  overrides the address inputs ( $A_0$ - $A_2$  and EN are ignored when  $\overline{WR}$  is high). With  $\overline{WR}$  low and  $\overline{RS}$  high, the switches respond immediately to a change in channel address; i.e., the latches are "transparent". Refer to Figure 1. For additional Applications information please see AN 545.

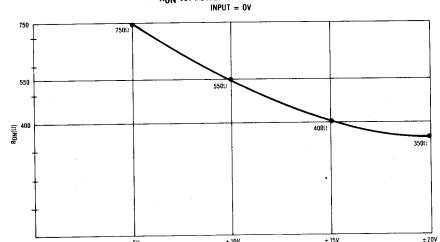

RON vs. POWER SUPPLY VOLTAGES

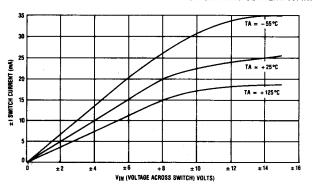

## TEST CIRCUIT NO. 9 ON CHANNEL CURRENT vs. INPUT VOLTAGE

OFF ISOLATION vs. FREQUENCY POWER ON

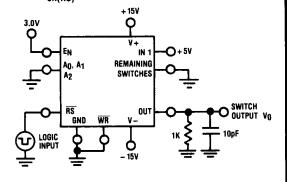

# TEST CIRCUIT 11 WRITE TURN-ON TIME ton(WR)

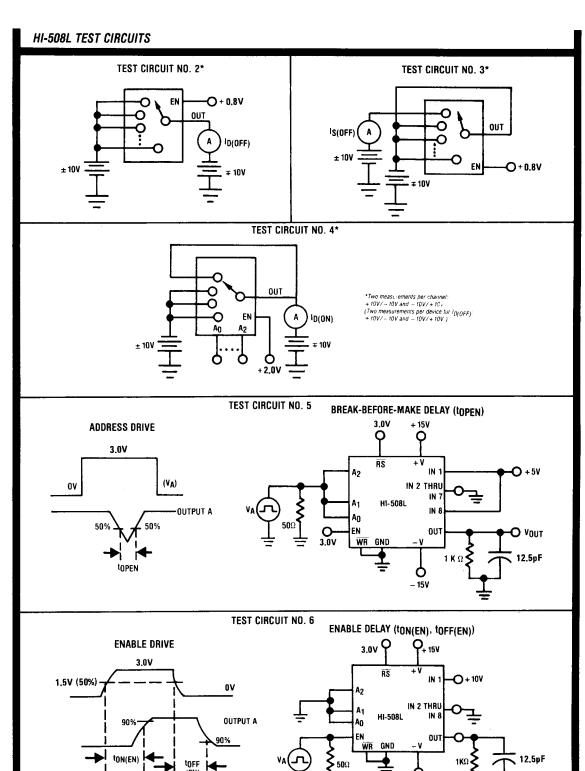

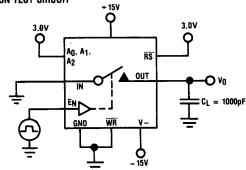

### **HI-508L TEST CIRCUITS**

### **TEST CIRCUIT 12** RESET TURN-OFF TIME toff(RS)

#### **TEST CIRCUIT 13**

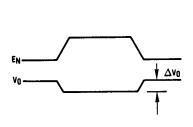

#### **CHARGE INJECTION TEST CIRCUIT**

$\Delta v_0$  is the measured voltage error DUE TO CHARGE INJECTION. THE ERROR VOLTAGE IN COULOMBS IS  $\dot{Q} = C_L X \triangle V_0$ .

## DIE CHARACTERISTICS

**Transistor Count**

397

Die Size

124x114mils.

Thermal Impedance

$\theta$ JA

80°C/W

$\theta$ JC

22ºC/W

Tie Substrate to:

-V<sub>Supply</sub>

**Process**

CMOS-DI