#### 查询LC78632RE供应商

**LC78632RE**

**Compact Disk Player DSP**

## Preliminary

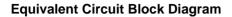

### **Overview**

The LC78632RE is a compact disc D/A signal-processing LSI for Video-CD players that provides a variable clock error correction (VCEC) mode. The LC78632RE demodulates the EFM signal from the optical pickup and performs de-interleaving, error detection, error correction, digital filtering, and other processing. The LC78632RE includes an on-chip 1-bit D/A converter, and executes commands sent from a control microprocessor.

WWW.DZSC.CO

### **Features**

- VCEC support

- Built-in PLL circuit for EFM detection (supports 4× playback)

- 18KB RAM on chip

- Error detection and correction (corrects two errors in C1 and four errors in C2)

- Frame jitter margin: ±8 frames

- · Frame synchronization signal detection, protection, and insertion

- Dual interpolation adopted in the interpolation circuit.

- · EFM data demodulation

- Subcode demodulation

- · Zero-cross muting adopted

- Servo command interface

- 2fs digital filter

- Digital de-emphasis

- Built-in independent left- and right-channel digital attenuators (239 attenuation steps)

- Supports the bilingual function

- Left/right swap function

- Built-in 1-bit D/A converter (third-order  $\Delta \Sigma$  noise shaper, PWM output)

- Built-in digital output circuit

- CLV servo

PDF

- Arbitrary track jumping (of up to 255 tracks)

- Variable sled voltage (four levels)

- Six extended I/O ports and 2 extended output ports

- Built-in oscillator circuit using an external 16.9344 MHz or 33.8688 MHz (for 4× playback) element

- Supply voltage: 4.5 to 5.5 V

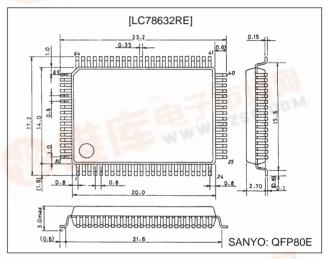

# Package Dimensions

unit: mm

#### 3174-QFP80E

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

#### LC78632RE

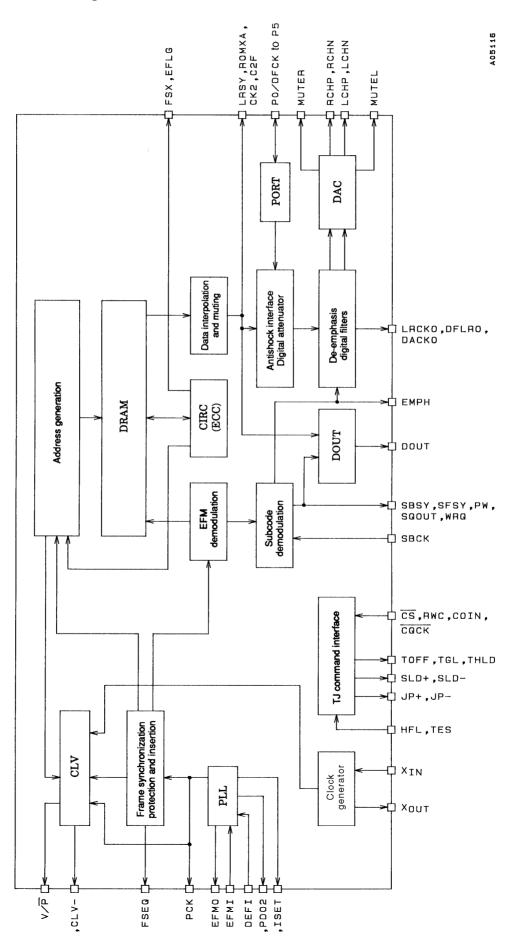

#### **Pin Assignment**

#### Absolute Maximum Ratings at Ta = $25^{\circ}$ C, V<sub>SS</sub> = 0 V

| Parameter                   | Symbol              | Conditions | Ratings                       | Unit |

|-----------------------------|---------------------|------------|-------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max |            | -0.3 to +7.0                  | V    |

| Input voltage               | V <sub>IN</sub>     |            | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage              | V <sub>OUT</sub>    |            | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Allowable power dissipation | Pd max              |            | 470                           | mW   |

| Operating temperature       | Topr                |            | -30 to +75                    | °C   |

| Storage temperature         | Tstg                |            | -40 to +125                   | °C   |

## Allowable Operating Ranges at Ta = 25°C, $V_{SS}$ = 0 V

| Parameter                | Symbol            | Conditions                                                                                                                                                                                                                          | min                 | typ | max                 | Unit |

|--------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|---------------------|------|

| Supply voltage           | V <sub>DD</sub>   | $V_{DD}$ , $AV_{DD}$ , $XV_{DD}$ , $LV_{DD}$ , $RV_{DD}$                                                                                                                                                                            | 4.5                 | 5.0 | 5.5                 | V    |

| Input high-level voltage | V <sub>IH</sub> 1 | $V_{IH1} \begin{array}{c} {\sf TEST1 \ to \ TEST5, \ TAI, \ HFL, \ TES, \ P0/DFCK, \ P1/DFIN, \\ P2, \ P3/DFLR, \ P4, \ P5, \ SBCK, \ RWC, \ COIN, \ \overline{CQCK}, \\ \hline RES, \ \overline{CS}, \ X_{IN}, \ DEFI \end{array}$ |                     |     | V <sub>DD</sub>     | V    |

|                          | V <sub>IH</sub> 2 | EFMI                                                                                                                                                                                                                                | 0.6 V <sub>DD</sub> |     | V <sub>DD</sub>     | V    |

| Input low-level voltage  | V <sub>IL</sub> 1 | TEST1 to TEST5, TAI, HFL, TES, P0/DFCK, P1/DFIN, P2, P3/DFLR, P4, P5, SBCK, RWC, COIN, $\overrightarrow{CQCK}$ , RES, $\overrightarrow{CS}$ , X <sub>IN</sub> , DEFI                                                                | 0                   |     | 0.3 V <sub>DD</sub> | V    |

|                          | V <sub>IL</sub> 2 | EFMI                                                                                                                                                                                                                                | 0                   |     | 0.4 V <sub>DD</sub> | V    |

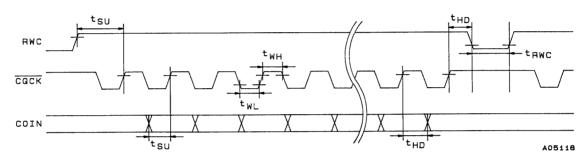

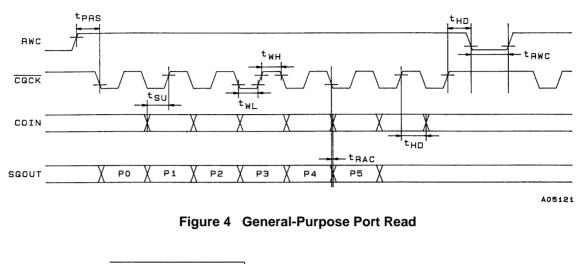

| Data setup time          | t <sub>SU</sub>   | COIN, RWC: Figures 1 and 4                                                                                                                                                                                                          | 400                 |     |                     | ns   |

|                          | t <sub>PRS</sub>  | RWC: Figure 4                                                                                                                                                                                                                       | 100                 |     |                     | ns   |

| Data hold time           | t <sub>HD</sub>   | COIN, RWC: Figures 1 and 4                                                                                                                                                                                                          | 400                 |     |                     | ns   |

#### Continued from preceding page.

| Parameter                    | Symbol           | Conditions                                  | min  | typ  | max  | Unit |

|------------------------------|------------------|---------------------------------------------|------|------|------|------|

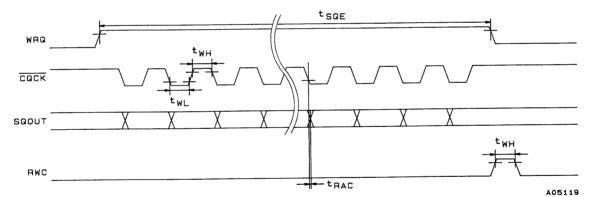

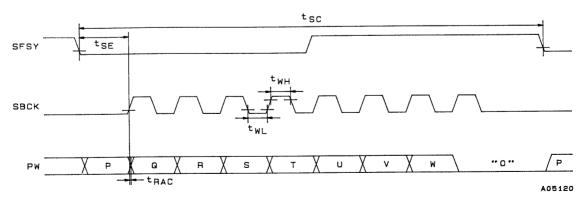

| High-level clock pulse width | t <sub>WH</sub>  | SBCK, CQCK: Figures 1, 2, 3, and 4          | 400  |      |      | ns   |

| Low-level clock pulse width  | t <sub>WL</sub>  | SBCK, CQCK: Figures 1, 2, 3, and 4          | 400  |      |      | ns   |

| Data read access time        | t <sub>RAC</sub> | SQOUT, PW: Figures 2, 3, and 4              | 0    |      | 400  | ns   |

| Command transfer time        | t <sub>RWC</sub> | RWC: Figures 1 and 4                        | 1000 |      |      | ns   |

| Subcode Q read enable time   | t <sub>SQE</sub> | WRQ: Figure 2, with no RWC signal           |      | 11.2 |      | ms   |

| Subcode read cycle           | t <sub>SC</sub>  | SFSY: Figure 3                              |      | 136  |      | μs   |

| Subcode read enable          | t <sub>SE</sub>  | SFSY: Figure 3                              | 400  |      |      | ns   |

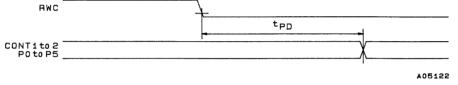

| Port output delay time       | t <sub>PD</sub>  | CONT1, CONT2, P0 to P5: Figure 5            |      |      | 1200 | ns   |

| Input loval                  | V <sub>EI</sub>  | EFMI                                        | 1.0  |      |      | Vp-p |

| Input level                  | V <sub>XI</sub>  | X <sub>IN</sub> : Capacitance coupled input | 1.0  |      |      | Vp-p |

Note: Due to the structure of this IC, the identical voltage must be applied to all power-supply pins.

# Electrical Characteristics at Ta = 25°C, $V_{DD}$ = 5 V, $V_{SS}$ = 0 V

| Parameter                  | Symbol             | Conditions                                                                                                                                                                            | min  | typ  | max  | Unit |

|----------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Current drain              | I <sub>DD</sub>    | Normal-speed playback                                                                                                                                                                 |      | 30   |      | mA   |

| Input high-level current   | I <sub>IH</sub> 1  | EFMI, HFL, TES, SBCK, RWC, COIN, $\overrightarrow{CQCK}$ , $\overrightarrow{RES}$ , DEFI: V <sub>IN</sub> = 5 V                                                                       |      |      | 5    | μΑ   |

|                            | I <sub>IH</sub> 2  | TAI, TEST1 to TEST5, $\overline{CS}$ : V <sub>IN</sub> = 5 V                                                                                                                          | 25   |      | 75   | μA   |

| Input low-level current    | I <sub>IL</sub>    | TAI, EFMI, HFL, TES, SBCK, RWC, COIN, $\overline{CQCK}$ , $\overline{RES}$ , TEST1 to TEST5, $\overline{CS}$ , DEFI: $V_{IN} = 0 V$                                                   | -5   |      |      | μΑ   |

|                            | V <sub>OH</sub> 1  | EFMO, CLV <sup>+</sup> , CLV <sup>-</sup> , V/ $\overline{P}$ , PCK, FSEQ, TOFF, TGL, THLD, JP <sup>+</sup> , JP <sup>-</sup> , EMPH, EFLG, FSX I <sub>OH</sub> = -1 mA               | 4    |      |      | v    |

| Output high-level voltage  | V <sub>OH</sub> 2  | MUTEL, MUTER, LRCKO, DFLRO, DACKO, P0/DFCK,<br>P1/DFIN, P2, P3/DFLR, P4, P5, LRSY, CK2, ROMXA,<br>C2F, SBSY, PW, SFSY, WRQ, SQOUT, 16M, 4.2M,<br>CONT1, CONT2: $I_{OH} = -0.5$ mA     | 4    |      |      | v    |

|                            | V <sub>OH</sub> 3  | VPDO: I <sub>OH</sub> = -1 mA                                                                                                                                                         | 4.5  |      |      | V    |

|                            | V <sub>OH</sub> 4  | DOUT: I <sub>OH</sub> = -12 mA                                                                                                                                                        | 4.5  |      |      | V    |

|                            | V <sub>OH</sub> 5  | LCHP, RCHP, LCHN, RCHN: I <sub>OH</sub> = -1 mA                                                                                                                                       | 3.0  |      | 4.5  | V    |

| Output low-level voltage   | V <sub>OL</sub> 1  | EFMO, CLV <sup>+</sup> , CLV <sup>-</sup> , V/ $\overline{P}$ , PCK, FSEQ, TOFF, TGL, THLD, JP <sup>+</sup> , JP <sup>-</sup> , EMPH, EFLG, FSX I <sub>OL</sub> = 1 mA                |      |      | 1    | v    |

|                            | V <sub>OL</sub> 2  | MUTEL, MUTER, LRCKO, DFLRO, DACKO, P0/DFCK,<br>P1/DFIN, P2, P3/DFLR, P4, P5, LRSY, CK2, ROMXA,<br>C2F, SBSY, PW, SFSY, WRQ, SQOUT, 16M, 4.2M,<br>CONT1, CONT2: I <sub>OL</sub> = 2 mA |      |      | 0.4  | V    |

|                            | V <sub>OL</sub> 3  | VPDO: I <sub>OL</sub> = 1 mA                                                                                                                                                          |      |      | 0.5  | V    |

|                            | V <sub>OL</sub> 4  | DOUT: I <sub>OL</sub> = 12 mA                                                                                                                                                         |      |      | 0.5  | V    |

|                            | V <sub>OL</sub> 5  | LCHP, RCHP, LCHN, RCHN: I <sub>OL</sub> = 1 mA                                                                                                                                        | 0.5  |      | 2.0  | V    |

|                            | I <sub>OFF</sub> 1 | PDO1, PDO2, VPDO, P0/DFCK, P1/DFIN,<br>P2, P3/DFLR, P4, P5: V <sub>OUT</sub> = 5 V                                                                                                    |      |      | 5    | μΑ   |

| Output off leakage current | I <sub>OFF</sub> 2 | PDO1, PDO2, VPDO, P0/DFCK, P1/DFIN,<br>P2, P3/DFLR, P4, P5: V <sub>OUT</sub> = 0 V                                                                                                    | -5   |      |      | μΑ   |

| Charge pump output current | IPDOH              | PDO1, PDO2: R <sub>ISET</sub> = 68 kΩ                                                                                                                                                 | -96  | -80  | -64  | μA   |

|                            | IPDOL              | PDO1, PDO2: R <sub>ISET</sub> = 68 kΩ                                                                                                                                                 | 64   | 80   | 96   | μA   |

|                            | V <sub>SLD</sub> 1 |                                                                                                                                                                                       | 1.0  | 1.25 | 1.5  | V    |

| Sled output voltage        | V <sub>SLD</sub> 2 |                                                                                                                                                                                       | 2.25 | 2.5  | 2.75 | V    |

| olog odiput voltage        | V <sub>SLD</sub> 3 |                                                                                                                                                                                       | 3.5  | 3.75 | 4.0  | V    |

|                            | V <sub>SLD</sub> 4 |                                                                                                                                                                                       | 4.75 |      |      | V    |

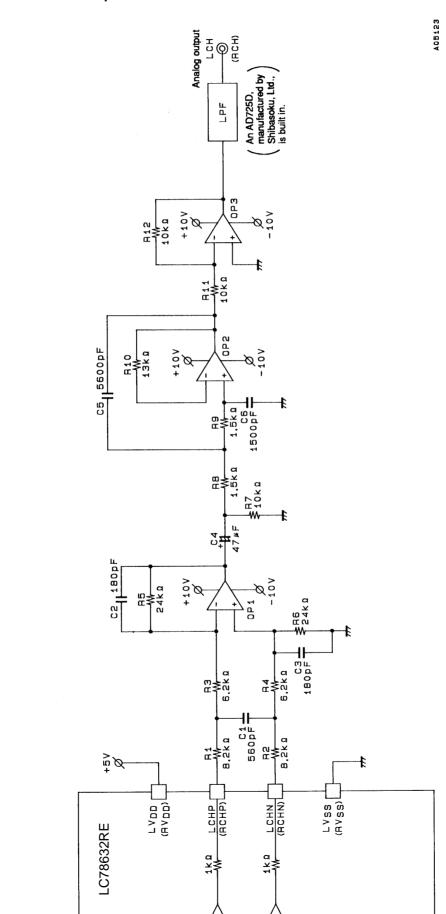

# D/A Converter Analog Characteristics at $Ta=25^{\circ}C,\,V_{DD}=5$ V, $V_{SS}=0$ V

| Parameter                 | Symbol  | Conditions                                                                                                  | min | typ   | max | Unit |

|---------------------------|---------|-------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Total harmonic distortion | THD + N | LCHP, LCHN, RCHP, RCHN; 1 kHz: 0 dB input,<br>using a 20-kHz low-pass filter (AD725D built in)              |     | 0.006 |     | %    |

| Dynamic range             | DR      | LCHP, LCHN, RCHP, RCHN; 1 kHz: -60 dB input, using the 20-kHz low-pass filter (A filter (AD725D built in))  |     | 90    |     | dB   |

| Signal-to-noise ratio     | S/N     | LCHP, LCHN, RCHP, RCHN; 1 kHz: 0 dB input, using<br>the 20-kHz low-pass filter (A filter (AD725D built in)) | 98  | 100   |     | dB   |

| Crosstalk CT              |         | LCHP, LCHN, RCHP, RCHN; 1 kHz: 0 dB input,<br>using a 20-kHz low-pass filter (AD725D built in)              | 96  | 98    |     | dB   |

Note: Measured in normal-speed playback mode in a Sanyo 1-bit D/A converter block reference circuit, with the digital attenuator set to EE (hexadecimal).

Figure 1 Command Input

Figure 2 Subcode Q Output

Figure 3 Subcode Output

Figure 5 General-Purpose Port Output

One-Bit D/A Converter Output Block Reference Circuit

#### LC78632RE

#### **Pin Functions**

| Pin No.  | Symbol           | I/O |                                                                                                                                                                                     | Function                                                                                                                      |  |  |  |

|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1        | VPDO             | 0   | Test output                                                                                                                                                                         |                                                                                                                               |  |  |  |

| 2        | PDO2             | 0   | Double-speed and quad-speed mode playback PLL charge pump output. Must be left open if unused.                                                                                      |                                                                                                                               |  |  |  |

| 3        | PDO1             | 0   | Normal-speed mode pla                                                                                                                                                               | nyback PLL charge pump output                                                                                                 |  |  |  |

| 4        | AV <sub>SS</sub> |     |                                                                                                                                                                                     | Must be connected to 0 V.                                                                                                     |  |  |  |

| 5        | FR               |     |                                                                                                                                                                                     | range setting resistor connection                                                                                             |  |  |  |

| 6        | AV <sub>DD</sub> |     | Analog system power su                                                                                                                                                              | ly ly                                                                                                                         |  |  |  |

| 7        | ISET             |     |                                                                                                                                                                                     | t current setting resistor connection                                                                                         |  |  |  |

| 8        | TAI              | 1   |                                                                                                                                                                                     | resistor is built in. Must be connected to 0 V.                                                                               |  |  |  |

| 9        | EFMO             | 0   |                                                                                                                                                                                     | FM signal output                                                                                                              |  |  |  |

| 10       | V <sub>SS</sub>  | -   |                                                                                                                                                                                     | Aust be connected to 0 V.                                                                                                     |  |  |  |

| 11       | EFMI             | 1   | EFM signal input                                                                                                                                                                    |                                                                                                                               |  |  |  |

| 12       | TEST1            | 1   |                                                                                                                                                                                     | resistor is built in. Must be connected to 0 V.                                                                               |  |  |  |

| 13       | CLV+             | 0   |                                                                                                                                                                                     |                                                                                                                               |  |  |  |

| 13       | CLV-             | 0   | deceleration.                                                                                                                                                                       | tput. CLV+ outputs a high level for acceleration, and CLV- outputs a high level for                                           |  |  |  |

| 14       |                  | 0   |                                                                                                                                                                                     | trol automatic switching monitor output. A high-level output indicates rough servo, and a                                     |  |  |  |

| 15       | V/P              | 0   | low-level output indicate                                                                                                                                                           |                                                                                                                               |  |  |  |

| 16       | TEST2            | I   | Test input. A pull-down                                                                                                                                                             | resistor is built in. Must be connected to 0 V.                                                                               |  |  |  |

| 17       | TEST3            | I   | Test input. A pull-down                                                                                                                                                             | resistor is built in. Must be connected to 0 V.                                                                               |  |  |  |

| 18       | P4               | I/O | I/O port                                                                                                                                                                            |                                                                                                                               |  |  |  |

| 19       | HFL              | I   | Track detection signal ir                                                                                                                                                           | nput. This is a Schmitt input.                                                                                                |  |  |  |

| 20       | TES              | I   | Tracking error signal inp                                                                                                                                                           | out. This is a Schmitt input.                                                                                                 |  |  |  |

| 21       | РСК              | 0   | EFM data playback bit c<br>playback.                                                                                                                                                | lock monitor. Outputs 4.3218 MHz when the phase is locked in normal-speed mode                                                |  |  |  |

| 22       | FSEQ             | 0   | Synchronization signal detection output. Outputs a high level when the synchronization signal detected from the EFM signal matches the internally generated synchronization signal. |                                                                                                                               |  |  |  |

| 23       | TOFF             | 0   | Tracking off output                                                                                                                                                                 |                                                                                                                               |  |  |  |

| 24       | TGL              | 0   | • ·                                                                                                                                                                                 | Tracking gain switching output. Increase the gain when this pin outputs a low level.                                          |  |  |  |

| 25       | THLD             | 0   |                                                                                                                                                                                     | racking gain switching output. Increase the gain when this pin outputs a low level.                                           |  |  |  |

| 26       | TEST4            | 1   | - · ·                                                                                                                                                                               | est input. A pull-down resistor is built in. Must be connected to 0 V.                                                        |  |  |  |

| 27       |                  |     |                                                                                                                                                                                     | igital system power supply                                                                                                    |  |  |  |

|          | V <sub>DD</sub>  | -   |                                                                                                                                                                                     | ack jump output. JP+ outputs a high level both for acceleration during outward direction jumps and for                        |  |  |  |

| 28<br>29 | JP+              | 0   | deceleration during inwa                                                                                                                                                            | eceleration during inward direction jumps. JP <sup>-</sup> outputs a high level both for acceleration during inward direction |  |  |  |

| 30       | SLD+             | 0   | Jumps and for deceleration                                                                                                                                                          | nps and for deceleration during outward direction jumps.                                                                      |  |  |  |

|          | SLD <sup>-</sup> | 0   | Sled output. This pin car                                                                                                                                                           | ed output. This pin can be set to 1 of 4 levels by commands sent from the system control microprocessor.                      |  |  |  |

| 31       | EMPH             | -   | De emphasie meniter A                                                                                                                                                               | high lavel indicates that a disk requising de emphasis is heing played                                                        |  |  |  |

| 32       |                  | 0   | •                                                                                                                                                                                   | high level indicates that a disk requiring de-emphasis is being played.                                                       |  |  |  |

| 33       | P5               | 1/0 | I/O port                                                                                                                                                                            |                                                                                                                               |  |  |  |

| 34       | LRCKO            | 0   |                                                                                                                                                                                     | LR clock output                                                                                                               |  |  |  |

| 35       | DFLRO            | 0   | Digital filter outputs                                                                                                                                                              | LR data output. The digital filter can be turned off with the DFOFF command.                                                  |  |  |  |

| 36       | DACKO            | 0   |                                                                                                                                                                                     | Bit clock output                                                                                                              |  |  |  |

| 37       | CONT1            | 0   | Output port                                                                                                                                                                         |                                                                                                                               |  |  |  |

| 38       | P0/DFCK          | I/O | I/O port. DF bit clock inp                                                                                                                                                          |                                                                                                                               |  |  |  |

| 39       | P1/DFIN          | I/O | I/O port. DF data input in                                                                                                                                                          |                                                                                                                               |  |  |  |

| 40       | P2               | I/O | I/O port. Used as the de<br>on when this pin is high.                                                                                                                               | -emphasis filter on/off switching pin in antishock mode. The de-emphasis filter is turned                                     |  |  |  |

| 41       | P3/DFLR          | I/O | I/O port output or digital                                                                                                                                                          | filter LR clock input (when anti-shock mode)                                                                                  |  |  |  |

| 42       | LRSY             | 0   |                                                                                                                                                                                     | LR clock output                                                                                                               |  |  |  |

| 43       | CK2              | 0   |                                                                                                                                                                                     | Bit clock output. The polarity can be inverted with the CK2CON command.                                                       |  |  |  |

| 44       | ROMXA            | 0   | ROMXA pins                                                                                                                                                                          | Interpolated data output. Data that has not been interpolated can be output by issuing the ROMXA command.                     |  |  |  |

| 45       | C2F              | 0   | 1                                                                                                                                                                                   | C2 flag output                                                                                                                |  |  |  |

| 46       | MUTEL            | 0   |                                                                                                                                                                                     | Left channel mute output                                                                                                      |  |  |  |

| 40       | LV <sub>DD</sub> | Ĕ   |                                                                                                                                                                                     | Left channel power supply                                                                                                     |  |  |  |

| 47       |                  | 0   |                                                                                                                                                                                     | Left channel P output                                                                                                         |  |  |  |

| 48       | LCHP             | 0   | One-bit D/A                                                                                                                                                                         |                                                                                                                               |  |  |  |

| 49<br>50 |                  |     | converter pins Left channel N output                                                                                                                                                |                                                                                                                               |  |  |  |

|          | LV <sub>SS</sub> |     | Left channel ground. Must be connected to 0V.                                                                                                                                       |                                                                                                                               |  |  |  |

Note: Of the general-purpose I/O ports, any unused input ports must be connected to 0 V, or set to be output ports.

#### Continued from preceding page.

| Pin No. | Symbol           | I/O | Function                                                           |                                                                                                           |  |  |  |

|---------|------------------|-----|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| 51      | XV <sub>SS</sub> |     | Crystal oscillator ground. Must be connected to 0 V.               |                                                                                                           |  |  |  |

| 52      | Х <sub>ОИТ</sub> | 0   |                                                                    |                                                                                                           |  |  |  |

| 53      | X <sub>IN</sub>  | I   | 16.9344 MHZ Crysta                                                 | 16.9344 MHz crystal oscillator connections. Use a 33.8688 MHz crystal oscillator for quad-speed playback. |  |  |  |

| 54      | XV <sub>DD</sub> |     | Crystal oscillator po                                              | Crystal oscillator power supply                                                                           |  |  |  |

| 55      | RV <sub>SS</sub> |     |                                                                    | Right channel ground. Must be connected to 0 V.                                                           |  |  |  |

| 56      | RCHN             | 0   | ]                                                                  | Right channel N output                                                                                    |  |  |  |

| 57      | RCHP             | 0   | One-bit D/A<br>converter pins                                      | Right channel P output                                                                                    |  |  |  |

| 58      | RV <sub>DD</sub> |     |                                                                    | Right channel power supply                                                                                |  |  |  |

| 59      | MUTER            | 0   | ]                                                                  | Right channel mute output                                                                                 |  |  |  |

| 60      | SBSY             | 0   | Subcode block syne                                                 | chronization signal output                                                                                |  |  |  |

| 61      | EFLG             | 0   | C1 and C2 error co                                                 | rrection state monitor                                                                                    |  |  |  |

| 62      | PW               | 0   | Subcode P, Q, R, S                                                 | Subcode P, Q, R, S, T, U, V, and W output                                                                 |  |  |  |

| 63      | SFSY             | 0   | Subcode frame syn                                                  | Subcode frame synchronization signal output. Falls when the subcode output goes to the standby state.     |  |  |  |

| 64      | SBCK             | I   | Subcode readout cl                                                 | Subcode readout clock input. This is a Schmitt input. This pin must be connected to 0 V if unused.        |  |  |  |

| 65      | DOUT             | 0   | Digital output                                                     | Digital output                                                                                            |  |  |  |

| 66      | FSX              | 0   | Outputs a 7.35 kHz                                                 | Outputs a 7.35 kHz synchronization signal generated by dividing the crystal oscillator frequency.         |  |  |  |

| 67      | WRQ              | 0   | Subcode Q output s                                                 | Subcode Q output standby output                                                                           |  |  |  |

| 68      | RWC              | I   | Read/write control i                                               | Read/write control input                                                                                  |  |  |  |

| 69      | SQOUT            | 0   | Subcode Q output                                                   | Subcode Q output                                                                                          |  |  |  |

| 70      | COIN             | I   | Input for commands                                                 | s from the control microprocessor                                                                         |  |  |  |

| 71      | CQCK             | I   | Command input ac                                                   | quisition clock. Also used as the SQOUT subcode readout clock input. This is a Schmitt input              |  |  |  |

| 72      | RES              | I   | Chip reset input. Th                                               | is pin must be set low temporarily when power is first applied.                                           |  |  |  |

| 73      | TESTF            | 0   | Test output                                                        |                                                                                                           |  |  |  |

| 74      | CONT2            | 0   | Output port                                                        |                                                                                                           |  |  |  |

| 75      | 16M              | 0   | 16.9344 MHz outpu                                                  | 16.9344 MHz output                                                                                        |  |  |  |

| 76      | 4.2M             | 0   | 4.2336 MHz output                                                  |                                                                                                           |  |  |  |

| 77      | TEST5            | I   | Test input. A pull-de                                              | own resistor is built in. Must be connected to 0 V.                                                       |  |  |  |

| 78      | CS               | I   | Chip select input. A                                               | pull-down resistor is built in. When control is not used, this pin must be connected to 0 V.              |  |  |  |

| 79      | DEFI             | I   | Defect detection signal input. Must be connected to 0 V if unused. |                                                                                                           |  |  |  |

| 80      | VCOC             | 1   | Test input. Must be connected to 0 V.                              |                                                                                                           |  |  |  |

Note: Of the general-purpose I/O ports, any unused input ports must be connected to 0 V, or set to be output ports.

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provide information as of December, 1997. Specifications and information herein are subject to change without notice.