# TC74VHC123,221AF/AFN/AFT

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC74VHC123AF, TC74VHC123AFN, TC74VHC123AFT TC74VHC221AF, TC74VHC221AFN, TC74VHC221AFT

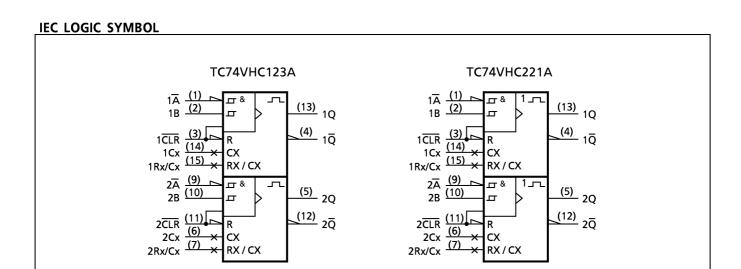

**DUAL MONOSTABLE MULTIVIBRATOR** TC74VHC123AF / AFN / AFT RETRIGGERBLE TC74VHC221AF / AFN / AFT NON - RETRIGGERBLE

TC74VHC123A / 221A are high speed MONOSTABLE MULTIVIBRATOR fabricated with silicon gate C2MOS technology.

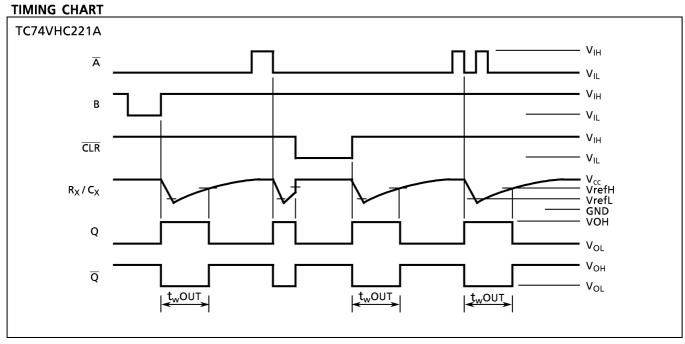

There are two trigger inputs,  $\overline{A}$  input (Negative edge), and B input (Positive edge). These inputs are valid for a slow rise/fall time signal (tr = tf = 1 s) as they are schmitt trigger inputs. This device may also be triggered by using CLR input (Positive edge).

After triggering, the output stays in a MONOSTABLE state for a time period determined by the external resistor and capacitor (Rx, Cx). A low level at the CLR input breaks this state.

Limits for Cx and Rx are:

External capacitor, Cx ...... No limit

External resistor, Rx ...... $V_{CC} = 2.0 \text{ V}$  more than  $5 \text{ k}\Omega$  $V_{CC} \ge 3.0 \text{ V}$  more than  $1 \text{ k}\Omega$

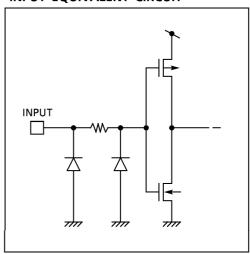

An input protection circuit ensures that 0 to 5.5 V can be applied to the input pins without regard to the supply voltage. This device can be used to interface 5 V to 3 V systems and two supply systems such as battery back up. This circuit prevents device destruction due to mismatched supply and input voltages.

#### FEATURES:

f.dzsc.com

- High Speed······ $t_{pd}$  = 8.1 ns (typ.) at  $V_{CC}$  = 5 V

- Low Power Dissipation

Standby State  $\mu$ A (Max.) at Ta = 25°C Active State  $\sim$  600  $\mu$ A (Max.) at Ta = 25°C

- High Noise Immunity VNIH = VNIL = 28% VCC (Min.)

- Power Down Protection is equipped with all inputs.

- Balanced Propagation Delays ·····  $t_{pLH} \simeq t_{pHL}$

- Wide Operating Voltage Range...  $V_{CC}$  (opr) = 2  $V \sim 5.5$  V

- Pin and Function Compatible with 74HC123A/221A

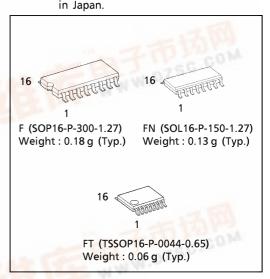

(Note) : The JEDEC SOP (FN) is not available

#### **PIN ASSIGNMENT** $1\overline{A}$ 16 V<sub>CC</sub> 1 15 1Rx/Cx 1B 2 1CLR 3 1Cx 1Q 4 13 1Q 12 2Q 2Q 5 2Cx 6 2CLR 2Rx/Cx 7 10 2B 9 GND 8 $2\overline{A}$ (TOP VIEW)

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

### TRUTH TABLE

| INPUTS |   |     | OUT | PUTS | FUNCTION      |  |  |

|--------|---|-----|-----|------|---------------|--|--|

| Ā      | В | CLR | Q   | Q    | FUNCTION      |  |  |

| ¬_     | Н | Н   | Л   | П    | OUTPUT ENABLE |  |  |

| Х      | L | Н   | L   | Н    | INHIBIT       |  |  |

| Н      | Х | Н   | L   | Н    | INHIBIT       |  |  |

| L      |   | Н   | Л   | П    | OUTPUT ENABLE |  |  |

| L      | Н |     | Л   | П    | OUTPUT ENABLE |  |  |

| Х      | Х | L   | L   | Н    | RESET         |  |  |

X : Don't Care

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

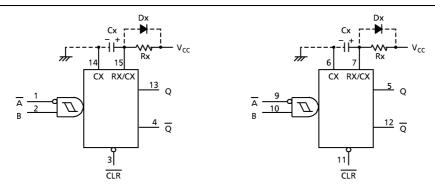

#### **BLOCK DIAGRAM**

Notes: (1) Cx, Rx, Dx are external Capacitor, Resistor, and Diode, respectively.

## (2) External clamping diode, Dx;

The external capacitor is charged to  $V_{CC}$  level in the wait state, i.e. when no trigger is applied.

If the supply voltage is turned off, Cx is discharges mainly through the internal (parasitic) diode. If Cx is sufficiently large and  $V_{\rm CC}$  drops rapidly, there will be some possibility of damaging the IC through in rush current or latch-up. If the capacitance of the supply voltage filter is large enough and  $V_{\rm CC}$  drops slowly, the in rush current is automatically limited and damage to the IC is avoided.

The maximum value of forward current through the parasitic diode is  $\pm 20$  mA.

In the case of a large Cx, the limit of fall time of the supply voltage is determined as follows:

$$t_f \ge (V_{CC} - 0.7) \cdot Cx / 20 \text{ mA}$$

(tf is the time between the supply voltage turn off and the supply voltage reaching 0.4  $V_{\text{CC}}.)$

In the even a system does not satisfy the above condition, an external clamping diode (Dx) is needed to protect the IC from rush current.

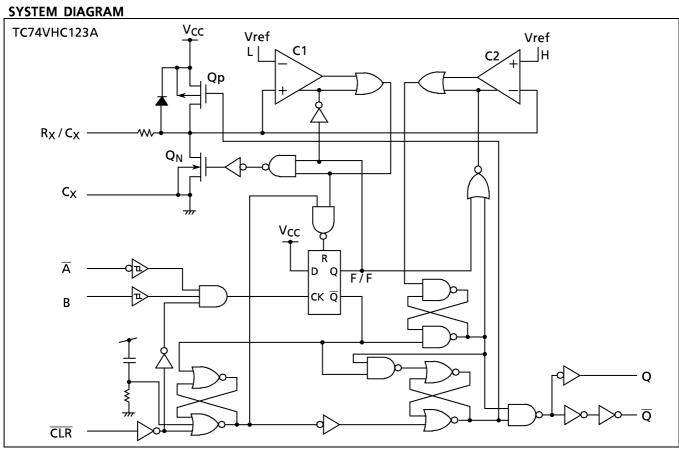

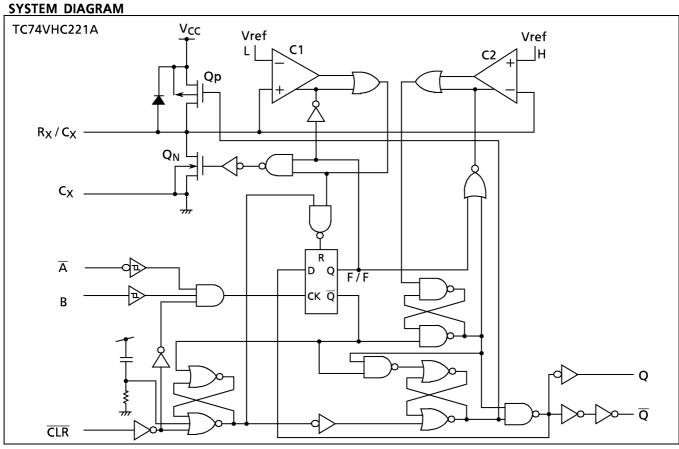

#### **FUNCTIONAL DESCRIPTION**

#### (1)Stand-by State

The external capacitor (Cx) is fully charged to  $V_{CC}$  in the stand-by state. That means, before triggering, the  $Q_P$  and  $Q_N$  transistors which are connected to the Rx/Cx node are in the off state. Two comparators that relate to the timing of the output pulse, and two reference voltage supplies turn off. The total supply current is only leakage current.

### (2)Trigger operation

Trigger operation is effective in any of the following three cases. First, the condition where the  $\overline{A}$  input is low, and the B input has a rising signal; second, where the B input is high, and the  $\overline{A}$  input has a falling signal; and third, where the  $\overline{A}$  input is low and the B input is high, and the  $\overline{CLR}$  input has a rising signal.

After a trigger becomes effective, comparators C1 and C2 start operating, and  $Q_N$  is turned on. The external capacitor discharges through  $Q_N$ . The voltage level at the Rx/Cx node drops. If the Rx/Cx voltage level falls to the internal reference voltage Vref L, the output of C1 becomes low. The flip-flop is then reset and  $Q_N$  turns off. At that moment C1 stops but C2 continues operating.

After  $Q_N$  turns off, the voltage at the Rx/Cx node starts rising at a rate determined by the time constant of external capacitor Cx and resistor Rx.

Upon triggering, output Q becomes high, following some delay time of the internal F/F and gates. It stays high even if the voltage of Rx/Cx changes from falling to rising. When Rx/Cx reaches the internal reference voltage VrefH, the output of C2 becomes low, the output Q goes low and C2 stops its operation. That means, after triggering, when the voltage level of the Rx/Cx node reaches VrefH, the IC returns to its MONOSTABLE state.

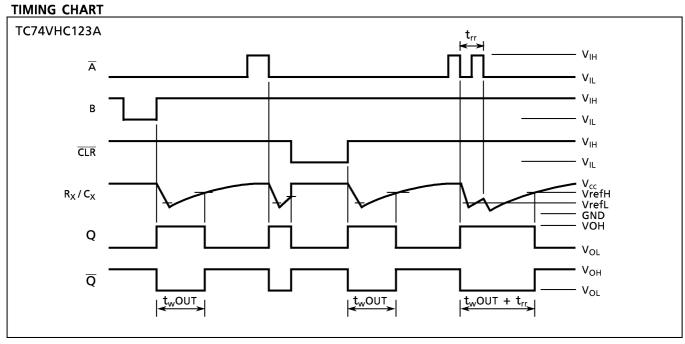

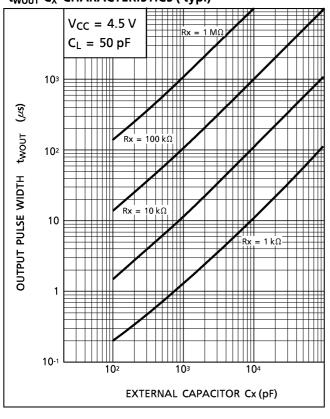

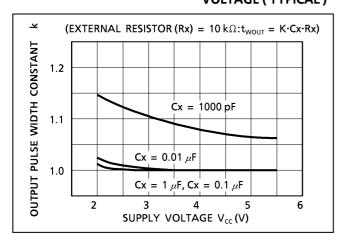

With large values of Cx and Rx, and ignoring the discharge time of the capacitor and internal delays of the IC, the width of the output pulse, tw (OUT), is as follows:

tw(OUT) = 1.0 Cx Rx

# (3)Retrigger operation (TC74VHC123A)

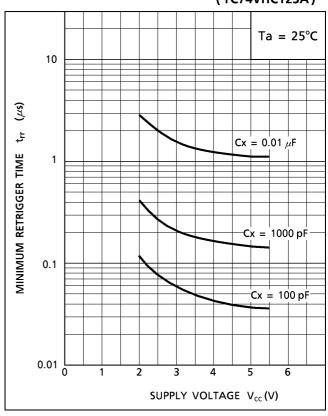

When a new trigger is applied to either input  $\overline{A}$  or B while in the MONOSTABLE state, it is effective only if the IC is charging Cx. The voltage level of the Rx/Cx node then falls to Vref L level again. Therefore the Q output stays high if the next trigger comes in before the time period set by Cx and Rx.

If the new trigger is very close to previous trigger, such as an occurrence during the discharge cycle, it will have no effect.

The minimum time for a trigger to be effective 2nd trigger, trr (Min.), depends on V<sub>CC</sub> and Cx.

#### (4)Reset operation

In normal operation, the  $\overline{CLR}$  input is held high. If  $\overline{CLR}$  is low, a trigger has no effect because the Q output is held low and the trigger control F/F is reset. Also,  $Q_P$  turns on and Cx is charged rapidly to  $V_{CC}$ .

This means if  $\overline{CLR}$  is set low, the IC goes into a wait state.

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                          | SYMBOL           | VALUE                    | UNIT |

|------------------------------------|------------------|--------------------------|------|

| Supply Voltage Range               | $V_{CC}$         | -0.5~7.0                 | V    |

| DC Input Voltage                   | VIN              | <b>−</b> 0.5~7.0         | V    |

| DC Output Voltage                  | V <sub>OUT</sub> | $-0.5 \sim V_{CC} + 0.5$ | V    |

| Input Diode Current                | I <sub>LK</sub>  | <b>-20</b>               | mA   |

| Output Diode Current               | I <sub>OK</sub>  | ± 20                     | mA   |

| DC Output Current                  | I <sub>OUT</sub> | ± 25                     | mA   |

| DC V <sub>CC</sub> /Ground Current | I <sub>cc</sub>  | ± 50                     | mA   |

| Power Dissipation                  | P <sub>D</sub>   | 180                      | mW   |

| Storage Temperature                | T <sub>stg</sub> | <b>−65~150</b>           | °C   |

# **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                | SYMBOL           | VALUE                                                                           | UNIT   |

|--------------------------|------------------|---------------------------------------------------------------------------------|--------|

| Supply Voltage           | $V_{cc}$         | 2.0~5.5                                                                         | V      |

| Input Voltage            | VIN              | 0~5.5                                                                           | V      |

| Output Voltage           | V <sub>OUT</sub> | 0~V <sub>cc</sub>                                                               | V      |

| Operating Temperature    | T <sub>opr</sub> | <b>−40~85</b>                                                                   | °C     |

| Input Rise and Fall Time | dt/dv            | $0\sim100 \ (V_{CC} = 3.3 \pm 0.3 \ V)$<br>$0\sim20 \ (V_{CC} = 5 \pm 0.5 \ V)$ | ns / V |

| External Capacitor       | Cx               | No Limitation *                                                                 | F      |

| External Resistor        | Rx               | ≥ 5 K*(VCC = 2.0 V)<br>≥ 1 K*(VCC ≥ 3.0 V)                                      | Ω      |

<sup>\*</sup> The maximum allowable values of Cx and Rx are a function of leakage of capacitor Cx, the leakage of TC74VHC123A/221A, and leakage due to board layout and surface resistance.

Susceptibility to externally induced noise signals may occur for Rx  $> 1 \mathrm{M} \Omega$ .

# DC ELECTRICAL CHARACTERISTICS

| PARAMETER                           | CYMPOL          | TEST CONDITION                                       |                                                   | V <sub>cc</sub>   | Т                     | a = 25°           | C                     | Ta = -                | 40∼85°C               | UNIT       |

|-------------------------------------|-----------------|------------------------------------------------------|---------------------------------------------------|-------------------|-----------------------|-------------------|-----------------------|-----------------------|-----------------------|------------|

| PARAIVIETER                         | SYMBOL          |                                                      |                                                   | (V)               | MIN.                  | TYP.              | MAX.                  | MIN.                  | MAX.                  | OWIT       |

| High - Level                        | .,              |                                                      |                                                   | 2.0<br>3.0~       | 1.50                  | _                 | _                     | 1.50                  | _                     | ,,         |

| Input Voltage                       | V <sub>IH</sub> |                                                      |                                                   |                   | V <sub>cc</sub> × 0.7 | _                 | -                     | V <sub>cc</sub> × 0.7 | _                     |            |

| Low - Level                         |                 |                                                      |                                                   | 2.0               | -                     | _                 | 0.50                  | _                     | 0.50                  |            |

| Input Voltage                       | V <sub>IL</sub> |                                                      |                                                   | 3.0~<br>5.5       | _                     | _                 | V <sub>cc</sub> × 0.3 | _                     | V <sub>cc</sub> × 0.3 | V          |

|                                     |                 | .,                                                   | FO. A                                             | 2.0               | 1.9                   | 2.0               | _                     | 1.9                   | _                     |            |

| High - Level<br>Output Voltage      | V <sub>OH</sub> | $V_{IN} = V_{IH} \text{ or } V_{IL}$                 | $I_{OH} = -50 \mu A$                              | 3.0<br>4.5        | 2.9<br>4.4            | 3.0<br>4.5        | _                     | 2.9<br>4.4            | _                     | v          |

| output voltage                      |                 |                                                      | $I_{OH} = -4 \text{ mA}$ $I_{OH} = -8 \text{ mA}$ | 3.0<br>4.5        | 2.58<br>3.94          |                   | _                     | 2.48<br>3.80          | _                     |            |

|                                     | V <sub>OL</sub> | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OL</sub> = 50 μA                           | 2.0               | -                     | 0.0               | 0.1                   | _                     | 0.1                   |            |

| Low - Level<br>Output Voltage       |                 |                                                      |                                                   | 3.0<br>4.5        | _                     | 0.0<br>0.0        | 0.1                   | _                     | 0.1<br>0.1            | v          |

| Output voitage                      |                 |                                                      | I <sub>OL</sub> = 4 mA<br>I <sub>OL</sub> = 8 mA  | 3.0<br>4.5        | _<br>_                | _<br>_            | 0.36<br>0.36          | _<br>_                | 0.44<br>0.44          |            |

| Input Leakage Current               | I <sub>IN</sub> | $V_{1N} = 5.5 V \text{ or}$                          | GND                                               | 0~5.5             | ı                     | ı                 | ±0.1                  | _                     | ± 1.0                 |            |

| Rx/Cx Terminal<br>Off-State Current | I <sub>IN</sub> | $V_{IN} = V_{CC}$ or GND                             |                                                   | 5.5               | 1                     | 1                 | ± 0.25                | _                     | ± 2.5                 | μ <b>A</b> |

| Quiescent Supply Current            | I <sub>cc</sub> | $V_{IN} = V_{CC}$ or $C$                             | 5.5                                               | -                 | -                     | 4.0               | _                     | 40.0                  |                       |            |

| Active - State * Supply Current     | I <sub>CC</sub> | $V_{IN} = V_{CC}$ or GND<br>Rx/Cx = 0.5 $V_{CC}$     |                                                   | 3.0<br>4.5<br>5.5 |                       | 160<br>380<br>560 | 250<br>500<br>750     | _<br>_<br>_           | 280<br>650<br>975     | μΑ         |

<sup>\*:</sup>Per circiut

TIMING REQUIREMENTS (Input  $t_r = t_f = 6 \text{ ns}$ )

| PARAMETER                    | SYMBOL                                 | TEST CONDITION                     |                        | Ta = 25°C |            | Ta = −40~85°C | UNIT |  |

|------------------------------|----------------------------------------|------------------------------------|------------------------|-----------|------------|---------------|------|--|

| TAKAMETER                    | 31 MBOL                                | TEST CONDITION                     | V <sub>cc</sub> (V)    | TYP.      | LIMIT      | LIMIT         | OWIT |  |

| Minimum Pulse Width          | t <sub>W(L)</sub><br>t <sub>W(H)</sub> |                                    | 3.3 ± 0.3<br>5.0 ± 0.5 |           | 5.0<br>5.0 | 5.0<br>5.0    |      |  |

| Minimum Clear Width<br>(CLR) | t <sub>W(L)</sub>                      |                                    | 3.3 ± 0.3<br>5.0 ± 0.5 |           | 5.0<br>5.0 | 5.0<br>5.0    | ns   |  |

| **<br>Minimum Retrigger Time | t <sub>rr</sub>                        | $Rx = 1 k\Omega$ $Cx = 100 pF$     | 3.3 ± 0.3<br>5.0 ± 0.5 |           |            | _<br>_        |      |  |

| William Retrigger Time       | <b>V</b> rr                            | $Rx = 1 k\Omega$ $Cx = 0.01 \mu F$ | 3.3 ± 0.3<br>5.0 ± 0.5 |           | -          | _             | μs   |  |

\*\*: for TC74VHC123A only

# AC ELECTRICAL CHARACTERISTICS (Input $t_r = t_f = 3 \text{ ns}$ )

| PARAMETER                                                         | SYM-                                 | TEST CONDITION                               |                        |         | Ta = 25°C |      |      | $Ta = -40 \sim 85^{\circ}C$ |      | UNIT     |

|-------------------------------------------------------------------|--------------------------------------|----------------------------------------------|------------------------|---------|-----------|------|------|-----------------------------|------|----------|

| PARAIVIETER                                                       | BOL                                  |                                              | V <sub>CC</sub> (V)    | CL (pF) | MIN.      | TYP. | MAX. | MIN.                        | MAX. | OINIT    |

|                                                                   |                                      |                                              | 3.3 ± 0.3              | 15      | -         | 13.4 | 20.6 | 1.0                         | 24.0 |          |

| Propagation Delay Time                                            | t <sub>pLH</sub>                     |                                              |                        | 50      | I         | 15.9 | 24.1 | 1.0                         | 27.5 |          |

| $(A,B-Q,\overline{Q})$                                            | t <sub>pHL</sub>                     |                                              | 5.0 ± 0.5              | 15      | 1         | 8.1  | 12.0 | 1.0                         | 14.0 |          |

|                                                                   |                                      |                                              | 3.0 ± 0.5              | 50      | ı         | 9.6  | 14.0 | 1.0                         | 16.0 |          |

|                                                                   |                                      |                                              | 3.3 ± 0.3              | 15      | -         | 14.5 | 22.4 | 1.0                         | 26.0 |          |

| Propagation Delay Time                                            | t <sub>pLH</sub>                     |                                              | 3.3 ± 0.3              | 50      | _         | 17.0 | 25.9 | 1.0                         | 29.5 |          |

| $(\overline{CLR} \text{ trigger} - Q, \overline{Q})$              | t <sub>pHL</sub>                     |                                              | 5.0 ± 0.5              | 15      |           | 8.7  | 12.9 | 1.0                         | 15.0 | ns       |

|                                                                   |                                      |                                              | 3.0 ± 0.3              | 50      | _         | 10.2 | 14.9 | 1.0                         | 17.0 | ''3      |

|                                                                   |                                      |                                              | 3.3 ± 0.3<br>5.0 ± 0.5 | 15      |           | 10.3 | 15.8 | 1.0                         | 18.5 |          |

| Propagation Delay Time                                            | t <sub>pLH</sub><br>t <sub>pHL</sub> |                                              |                        | 50      |           | 12.8 | 19.3 | 1.0                         | 22.0 |          |

| $(\overline{CLR} - Q, \overline{Q})$                              |                                      |                                              |                        | 15      |           | 6.3  | 9.4  | 1.0                         | 11.0 |          |

|                                                                   |                                      |                                              | 3.0 ± 0.5              | 50      | _         | 7.8  | 11.4 | 1.0                         | 13.0 |          |

|                                                                   |                                      |                                              | 3.3 ± 0.3<br>5.0 ± 0.5 | 50      | 1         | 160  | 240  | _                           | 300  | μs<br>ms |

|                                                                   |                                      | $\mathbf{R}\mathbf{x} = 2  \mathbf{k}\Omega$ |                        | 50      | ı         | 133  | 200  | _                           | 240  |          |

| Output Pulse Width                                                | t <sub>wOUT</sub>                    | $Cx = 0.01 \mu F$                            | 3.3 ± 0.3              | 50      | 90        | 100  | 110  | 90                          | 110  |          |

|                                                                   | -wooi                                | $Rx = 10 k\Omega$                            | 5.0 ± 0.5              | 50      | 90        | 100  | 110  | 90                          | 110  |          |

|                                                                   |                                      | $Cx = 0.1 \ \mu F$                           |                        | 50      | 0.9       | 1.0  | 1.1  | 0.9                         | 1.1  |          |

|                                                                   |                                      | $Rx = 10 k\Omega$                            | 5.0 ± 0.5              |         | 0.9       | 1.0  | 1.1  | 0.9                         | 1.1  |          |

| Output Pulse Width Error<br>Between Circuits<br>(In same Package) | $	riangle \mathbf{t}_{wOUT}$         |                                              |                        |         | -         | ± 1  | _    | _                           | _    | %        |

| Input Capacitance                                                 | C <sub>I N</sub>                     |                                              |                        |         |           | 4    | 10   | _                           | 10   | ne       |

| Power Dissipation<br>Capacitance                                  | C <sub>PD</sub>                      | (1)                                          | lote 1)                |         | 1         | 73   | _    | _                           | _    | рF       |

(Note 1) :  $C_{\text{PD}}$  is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.

Average operating current can be obtained by the equation:

$I_{CC}$  (opr) =  $C_{PD} \cdot V_{CC} \cdot f_{IN} + I_{CC}$  · Duty / 100 +  $I_{CC}$  / 2 (per circuit) ( $I_{CC}$  ': Active Supply Current) (Duty : %)

twout-Cx CHARACTERISTICS (typ.)

# $t_{rr}$ - $V_{CC}$ CHARACTERISTICS ( TYP.) ( TC74VHC123A )

# OUTPUT PULSE WIDTH CONSTANT K-SUPPLY VOLTAGE (TYPICAL)

# INPUT EQUIVALENT CIRCUIT

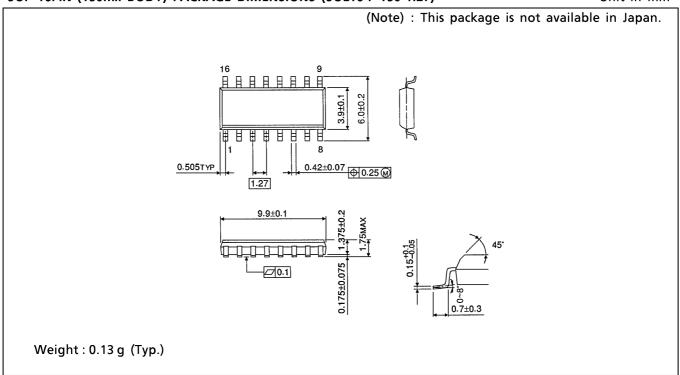

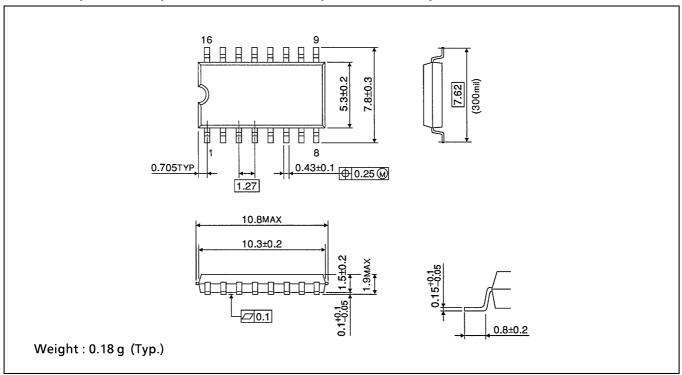

# SOP 16PIN (200mil BODY) PACKAGE DIMENSIONS (SOP16-P-300-1.27)

Unit in mm

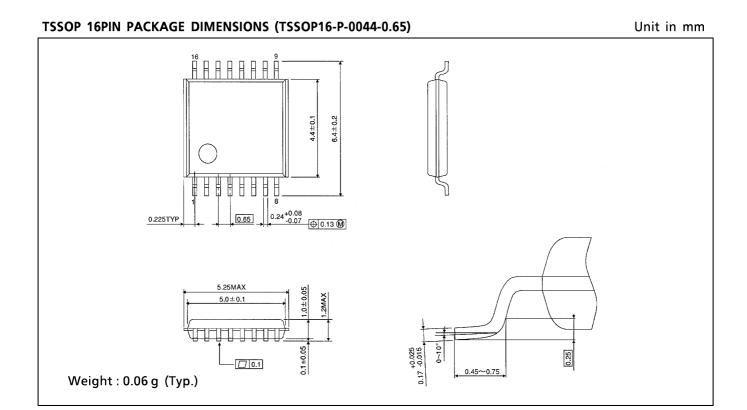

# SOP 16PIN (150mil BODY) PACKAGE DIMENSIONS (SOL16-P-150-1.27)

Unit in mm