###

## Two-Channel, Triple/Quad RGB Video Switches and Buffers

#### **General Description**

The MAX463–MAX470 series of two-channel, triple/quad buffered video switches and video buffers combines high-accuracy, unity-gain-stable amplifiers with high-performance video switches. Fast switching time and low differential gain and phase error make this series of switches and buffers ideal for all video applications. The devices are all specified for ±5V supply operation with inputs and outputs as high as ±2.5V when driving  $150\Omega$  loads ( $75\Omega$  back-terminated cable).

Input capacitance is typically only 5pF, and channel-tochannel crosstalk is better than 60dB, accomplished by surrounding all inputs with AC ground pins. The onboard amplifiers feature a 200V/µs slew rate (300V/µs for  $A_V = 2V/V$  amplifiers), and a bandwidth of 100MHz (90MHz for  $A_V = 2V/V$  buffers). Channel selection is controlled by a single TTL-compatible input pin or by a microprocessor interface, and channel switch time is

For design flexibility, devices are offered with bufferamplifier gains of 1V/V or 2V/V for 75 $\Omega$  back-terminated applications. Output amplifiers have a guaranteed output swing of  $\pm 2V$  into  $75\Omega$ .

Devices offered in this series are as follows:

| PART   | DESCRIPTION                | VOLTAGE GAIN<br>(V/V) |

|--------|----------------------------|-----------------------|

| MAX463 | Triple RGB Switch & Buffer | 11                    |

| MAX464 | Quad RGB Switch & Buffer   | 1.1                   |

| MAX465 | Triple RGB Switch & Buffer | 2                     |

| MAX466 | Quad RGB Switch & Buffer   | 2                     |

| MAX467 | Triple Video Buffer        | 1                     |

| MAX468 | Quad Video Buffer          | 1                     |

| MAX469 | Triple Video Buffer        | 2                     |

| MAX470 | Quad Video Buffer          | 2                     |

#### **Applications**

Broadcast-Quality Color-Signal Multiplexing

**RGB** Multiplexing

RGB Color Video Overlay Editors

RGB Color Video Security Systems

RGB Medical Imaging

Coaxial-Cable Line Drivers

Typical Operating Circuit appears at end of data sheet.

#### **Features**

- ♦ 100MHz Unity-Gain Bandwidth

- ♦ 90MHz Bandwidth with 2V/V Gain

- 0.01%/0.03° Differential Gain/Phase Error

- ♦ Drives 50Ω and 75Ω Back-Terminated Cable Directly

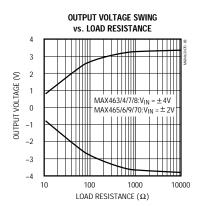

- ♦ Wide Output Swing:  $\pm 2V$  into  $75\Omega$  $\pm 2.5V$  into  $150\Omega$

- ♦ 300V/µs Slew Rate (2V/V gain)

- **♦ 20ns Channel Switching Time**

- **♦ Logic Disable Mode: High-Z Outputs Reduced Power Consumption**

- Outputs May Be Paralleled for Larger Networks

- ♦ 5pF Input Capacitance (channel on or off)

#### Ordering Information

| PART      | TEMP. RANGE    | PIN-PACKAGE           |

|-----------|----------------|-----------------------|

| MAX463CNG | 0°C to +70°C   | 24 Narrow Plastic DIP |

| MAX463CWG | 0°C to +70°C   | 24 Wide SO            |

| MAX463C/D | 0°C to +70°C   | Dice*                 |

| MAX463ENG | -40°C to +85°C | 24 Narrow Plastic DIP |

| MAX463EWG | -40°C to +85°C | 24 Wide SO            |

#### Ordering Information continued on last page.

Dice are specified at  $T_A = +25$ °C, DC parameters only.

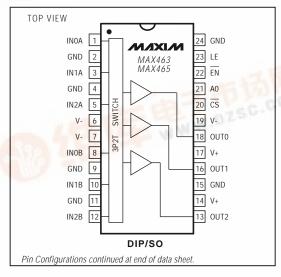

#### Pin Configurations

MIXIM

Maxim Integrated Products

Call toll free 1-800-998-8800 for free samples or literature.

#### **ABSOLUTE MAXIMUM RATINGS**

| Power-Supply Ranges                                      |

|----------------------------------------------------------|

| V+ to V                                                  |

| Analog Input Voltage(V 0.3V) to (V+ + 0.3V)              |

| Digital Input Voltage0.3V to (V+ + 0.3V)                 |

| Output Short-Circuit Duration (to GND)1 Minute           |

| Input Current into Any Pin, Power On or Off±50mA         |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )    |

| 16-Pin Plastic DIP (derate 22.22mW/°C above +70°C)1778mW |

| 16-Pin Wide SO (derate 20.00mW/°C above +70°C)1600mW     |

|                                                          |

| 24-Pin Narrow Plastic DIP                     |             |

|-----------------------------------------------|-------------|

| (derate 20.2mW/°C above +70°C)                | 1620mW      |

| 24-Pin Wide SO (derate 19.3mW/°C above +70°C) | 1590mW      |

| 28-Pin Narrow Plastic DIP                     |             |

| (derate 20.2mW/°C above +70°C)                | 1620mW      |

| 28-Pin Wide SO (derate 18.1mW/°C above +70°C) | 1440mW      |

| Operating Temperature Ranges                  |             |

| MAX4C                                         |             |

| MAX4E40                                       | °C to +85°C |

| Storage Temperature Range65°                  |             |

| Lead Temperature (soldering, 10sec)           | +300°C      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V+ = 5V, V- = -5V, -2V  $\leq$  VIN  $\leq$  +2V, RLOAD = 75 $\Omega$ , unless otherwise noted.)

| PARAMETER                            | SYMBOL          | CONI                                                               | DITIONS                         |       | tyP  |       | T <sub>A</sub> = T <sub>MIN</sub><br>MIN | to T <sub>MAX</sub> | UNITS |

|--------------------------------------|-----------------|--------------------------------------------------------------------|---------------------------------|-------|------|-------|------------------------------------------|---------------------|-------|

| Operating Supply Voltage             | Vs              |                                                                    |                                 | ±4.75 | ±5   | ±5.25 | ±4.75                                    | ±5.25               | V     |

| Input Voltage Range                  | VIN             |                                                                    |                                 | -2    |      | 2     | -2                                       | 2                   | V     |

| Offset Voltage                       | Vos             |                                                                    |                                 |       | ±3   | ±10   |                                          | ±15                 | mV    |

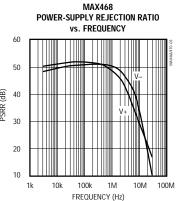

| Power-Supply Rejection Ratio         | PSRR            |                                                                    |                                 | 50    | 60   |       | 50                                       |                     | dB    |

| On Input Bias Current                | IBIAS           |                                                                    |                                 |       | ±1   | ±3    |                                          | ±5                  | μΑ    |

| On Input Resistance                  | RIN             |                                                                    |                                 | 300   | 700  |       | 150                                      |                     | kΩ    |

| Input Capacitance                    | C <sub>IN</sub> | Channel off or or                                                  | า                               |       | 5    |       |                                          |                     | pF    |

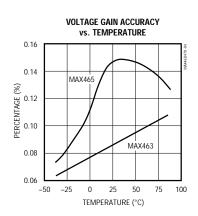

| Voltage Cein Agguragy                |                 | MAX463/MAX464<br>(Note 1)                                          | 4, MAX467/MAX468                |       | 0.2  | 0.5   |                                          | 1.0                 | %     |

| Voltage-Gain Accuracy                |                 | MAX465/MAX466, MAX469/MAX470,<br>$R_{LOAD} = 150\Omega$ , (Note 2) |                                 |       | 0.3  | 1.0   |                                          | 2.0                 | 70    |

| Output Valtage Curing                | VOLIT           | $R_{LOAD} = 150\Omega$                                             |                                 | ±2.5  | ±2.8 |       | ±2.5                                     |                     | V     |

| Output Voltage Swing                 | VOU1            | $R_{LOAD} = 75\Omega$                                              |                                 | ±2.0  | ±2.4 |       | -1.5/+2                                  |                     | ]     |

|                                      |                 | f <sub>IN</sub> = 10MHz                                            |                                 |       | 5    |       |                                          |                     |       |

| Output Impedance                     | Rout            | fin = DC                                                           | MAX463/MAX464,<br>MAX467/MAX468 |       | 0.05 |       |                                          |                     | Ω     |

|                                      |                 | III - DC                                                           | MAX465/MAX466,<br>MAX469/MAX470 |       | 0.1  |       |                                          |                     |       |

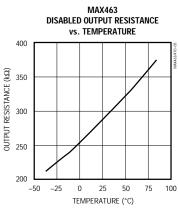

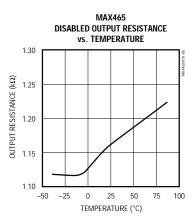

| Output Resistance,                   | ROUTD           | MAX463/MAX464                                                      | 4                               | 150   | 250  |       | 100                                      |                     | kΩ    |

| Disabled Mode                        | KOUID           | MAX465/MAX466                                                      | 6                               | 0.7   | 1    |       | 0.7                                      |                     | kΩ    |

| Output Capacitance,<br>Disabled Mode | Coutd           | MAX463-MAX46                                                       | 06                              |       | 10   |       |                                          |                     | pF    |

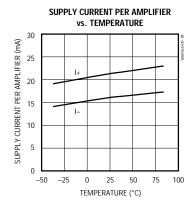

|                                      | I+              | MAX463/MAX465/MAX467/MAX469,<br>V <sub>IN</sub> = 0V               |                                 |       | 65   | 80    |                                          | 100                 |       |

| Positive Supply Current              |                 | MAX464/MAX466/MAX468/MAX470,<br>V <sub>IN</sub> = 0V               |                                 |       | 85   | 100   |                                          | 120                 | mA    |

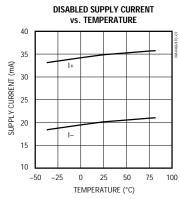

|                                      |                 | MAX463/MAX465                                                      | 5, disabled mode                |       | 35   | 45    |                                          | 50                  |       |

|                                      |                 | MAX464/MAX466                                                      | 6, disabled mode                |       | 40   | 50    |                                          | 55                  | 1     |

### **ELECTRICAL CHARACTERISTICS (continued)** (V+ = 5V, V- = -5V, -2V $\leq$ V<sub>IN</sub> $\leq$ +2V, R<sub>LOAD</sub> = 75 $\Omega$ , unless otherwise noted.)

| PARAMETER                                       | SYMBOL          | CONDITIONS                                              | T <sub>A</sub> = +25<br>MIN TYP | °C<br>MAX | T <sub>A</sub> = T <sub>MIN</sub> to | o T <sub>MAX</sub><br>MAX | UNITS             |  |

|-------------------------------------------------|-----------------|---------------------------------------------------------|---------------------------------|-----------|--------------------------------------|---------------------------|-------------------|--|

|                                                 |                 | MAX463/MAX465/MAX467/MAX469,<br>V <sub>IN</sub> = 0V    | 50                              | 65        |                                      | 75                        |                   |  |

| Negative Supply Current                         | l-              | MAX464/MAX466/MAX468/MAX470,<br>V <sub>IN</sub> = 0V    | 65                              | 80        |                                      | 95                        | mA                |  |

|                                                 |                 | MAX463/MAX465, disabled mode                            | 20                              | 30        |                                      | 35                        |                   |  |

|                                                 |                 | MAX464/MAX466, disabled mode                            | 25                              | 35        |                                      | 40                        |                   |  |

| Input Noise Density                             | en              | fin = 10kHz                                             | 20                              |           |                                      |                           | nV/√Hz            |  |

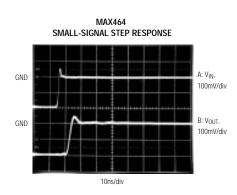

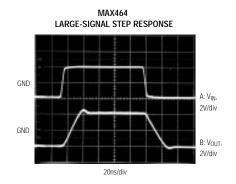

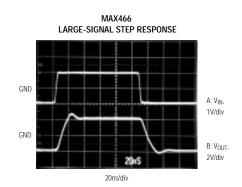

| Slew Rate                                       | SR              | MAX463/MAX464, MAX467/MAX468                            | 200                             |           |                                      |                           | V/µs              |  |

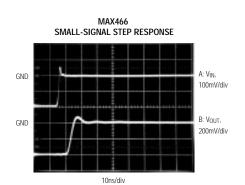

| Siew Rate                                       | JK              | MAX465/MAX466, MAX469/MAX470                            | 300                             |           |                                      |                           | V/μS              |  |

| -3dB Bandwidth                                  | BW              | MAX463/MAX464, MAX467/MAX468                            | 100                             |           |                                      |                           | MHz               |  |

| -30B Bandwidin                                  | BVV             | MAX465/MAX466, MAX469/MAX470                            | 90                              |           |                                      |                           | IVIHZ             |  |

| Differential Gain Error                         | DG              | MAX463/MAX464, MAX467/MAX468                            | 0.01                            |           |                                      |                           | %                 |  |

| (Note 3)                                        | DG              | MAX465/MAX466, MAX469/MAX470                            | 0.12                            |           |                                      |                           | 70                |  |

| Differential Phase Error                        | DP              | MAX463/MAX464, MAX467/MAX468                            | 0.03                            |           |                                      |                           | -1                |  |

| (Note 3)                                        | DP              | MAX465/MAX466, MAX469/MAX470                            | 0.14                            |           |                                      |                           | deg.              |  |

| Settling Time to 0.1%                           | ts              | V <sub>IN</sub> = 2V-to-0V step                         | 50                              |           |                                      |                           | ns                |  |

| Adjacent Channel Crosstalk (Note 4)             | XTALK           | fin = 10MHz                                             | 60                              |           |                                      |                           | dB                |  |

| All-Hostile Crosstalk (Note 5)                  | XTALK           | f <sub>IN</sub> = 10MHz                                 | 50                              |           |                                      |                           | dB                |  |

| All-Hostile Off Isolation (Note 6)              | ISO             | f <sub>IN</sub> = 10MHz, MAX463–MAX466                  | 70                              |           |                                      |                           | dB                |  |

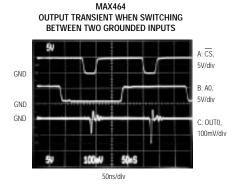

| Channel Switching<br>Propagation Delay (Note 7) | tpD             | MAX463-MAX466                                           | 15                              |           |                                      |                           | ns                |  |

| Channel Switching Time (Note 8)                 | tsw             | MAX463-MAX466                                           | 20                              |           |                                      |                           | ns                |  |

| Switching Transient                             |                 | V <sub>INA</sub> = V <sub>INB</sub> = 0V, MAX463–MAX466 | 300                             |           |                                      |                           | mV <sub>P-P</sub> |  |

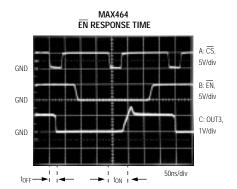

| Amplifier Switching Off-Time (Note 9)           | toff            | MAX463-MAX466                                           | 80                              |           |                                      |                           | ns                |  |

| Amplifier Switching On-Time (Note 10)           | ton             | MAX463-MAX466                                           | 100                             |           |                                      |                           | ns                |  |

| Logic Input High Threshold                      | V <sub>IH</sub> | EN, A0, CS, LE; MAX463-MAX466                           |                                 | 2         |                                      | 2                         | V                 |  |

| Logic Input Low Threshold                       | VIL             | EN, A0, CS, LE; MAX463-MAX466                           | 0.8                             |           | 0.8                                  |                           | V                 |  |

| Logic Input Current High                        | linhi           | EN, A0, CS, LE; MAX463-MAX466                           |                                 | 200       |                                      | 200                       | μΑ                |  |

| Logic Input Current Low                         | linlo           | EN, A0, CS, LE; MAX463-MAX466                           |                                 | 200       |                                      | 200                       | μΑ                |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V + = 5V, V - = -5V, -2V \le V_{IN} \le +2V, R_{LOAD} = 75\Omega$ , unless otherwise noted.)

| PARAMETER                    | SYMBOL          | CONDITIONS                    | MIN | A = +25<br>TYP | °C<br>MAX | T <sub>A</sub> = T <sub>MIN</sub> | to T <sub>MAX</sub> | UNITS |

|------------------------------|-----------------|-------------------------------|-----|----------------|-----------|-----------------------------------|---------------------|-------|

| Address Setup Time (Note 11) | t <sub>SU</sub> | EN, A0, CS, LE; MAX463-MAX466 | 30  |                |           | 30                                |                     | ns    |

| Address Hold Time (Note 11)  | t <sub>H</sub>  | EN, A0, CS, LE; MAX463-MAX466 |     |                | 0         |                                   | 0                   | ns    |

| CS Pulse Width Low (Note 11) | tcs             | EN, A0, CS, LE; MAX463-MAX466 | 15  |                |           | 15                                |                     | ns    |

Note 1: Voltage gain accuracy for the unity-gain devices is defined as [(V<sub>OUT</sub> - V<sub>IN</sub>) at V<sub>IN</sub> = 1V - (V<sub>OUT</sub> - V<sub>IN</sub>) at V<sub>IN</sub> = -1V]/2.

Note 2: Voltage gain accuracy for the gain-of-two devices is defined as [(VOUT/2 - VIN) at VIN = 1V - (VOUT/2 - VIN) at VIN = 1-1V]/2.

Note 3: Tested with a 3.58MHz sine wave of amplitude 40IRE superimposed on a linear ramp (0IRE to 100IRE),  $R_L = 150\Omega$  to ground.

Note 4: Tested with the selected input connected to ground through a 750 resistor, and a 4V<sub>P-P</sub> sine wave at 10MHz driving adjacent input.

Note 5: Tested in the same manner as described in Note 4, but with all other inputs driven.

**Note 6:** Tested with LE = 0V,  $\overline{\text{EN}}$  = V+, and all inputs driven with a 4Vp-p, 10MHz sine wave. **Note 7:** Measured from a channel switch command to measurable activity at the output.

Note 8: Measured from where the output begins to move to the point where it is well defined.

**Note 9:** Measured from a disable command to amplifier in a non-driving state.

Note 10: Measured from an enable command to the point where the output reaches 90% current out.

Note 11: Guaranteed by design.

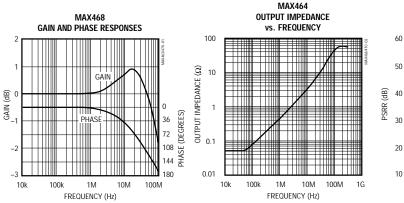

#### Typical Operating Characteristics

( $T_A = +25$ °C, unless otherwise noted.)

#### Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, unless otherwise noted.)$

\_Typical Operating Characteristics (continued)

( $T_A = +25$ °C, unless otherwise noted.)

#### \_Pin Descriptions

| PIN                    |                        | NAME | FUNCTION                                                                                                                                                                                                                                                                                                      |  |  |

|------------------------|------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX463/MAX465          | MAX464/MAX466          | NAME | FUNCTION                                                                                                                                                                                                                                                                                                      |  |  |

| 1                      | 28                     | INOA | Channel A, Analog Input 0                                                                                                                                                                                                                                                                                     |  |  |

| 2, 4, 9,<br>11, 15, 24 | 1, 3, 5,<br>11, 13, 19 | GND  | Analog Ground                                                                                                                                                                                                                                                                                                 |  |  |

| 3                      | 2                      | IN1A | Channel A, Analog Input 1                                                                                                                                                                                                                                                                                     |  |  |

| 5                      | 4                      | IN2A | Channel A, Analog Input 2                                                                                                                                                                                                                                                                                     |  |  |

| -                      | 6                      | IN3A | Channel A, Analog Input 3                                                                                                                                                                                                                                                                                     |  |  |

| 6, 7, 19               | 7, 9, 21, 23           | V-   | Negative Power-Supply Input. Connect to -5V. Thermal path.                                                                                                                                                                                                                                                    |  |  |

| 8                      | 8                      | INOB | Channel B, Analog Input 0                                                                                                                                                                                                                                                                                     |  |  |

| 10                     | 10                     | IN1B | Channel B, Analog Input 1                                                                                                                                                                                                                                                                                     |  |  |

| 12                     | 12                     | IN2B | Channel B, Analog Input 2                                                                                                                                                                                                                                                                                     |  |  |

| -                      | 14                     | IN3B | Channel B, Analog Input 3                                                                                                                                                                                                                                                                                     |  |  |

| -                      | 15                     | OUT3 | Buffered Analog Output 3                                                                                                                                                                                                                                                                                      |  |  |

| 13                     | 17                     | OUT2 | Buffered Analog Output 2                                                                                                                                                                                                                                                                                      |  |  |

| 14, 17                 | 16, 18                 | V+   | Positive Power-Supply Input. Connect to +5V.                                                                                                                                                                                                                                                                  |  |  |

| 16                     | 20                     | OUT1 | Buffered Analog Output 1                                                                                                                                                                                                                                                                                      |  |  |

| 18                     | 22                     | OUT0 | Buffered Analog Output 0                                                                                                                                                                                                                                                                                      |  |  |

| 20                     | 24                     | CS   | Chip-Select—latch control for the digital inputs. When $\overline{CS}$ is low, A0 and $\overline{EN}$ input registers are transparent. When $\overline{CS}$ goes high, the A0 input register latches. If LE is high, the $\overline{EN}$ input register also latches when $\overline{CS}$ goes high (see LE). |  |  |

| 21                     | 25                     | A0   | Channel-Select Input. When $\overline{\text{CS}}$ is low, driving A0 low selects channel A and driving A0 high selects channel B.                                                                                                                                                                             |  |  |

| 22                     | 26                     | ĒN   | Buffer-Enable Input. When $\overline{\text{CS}}$ is low or LE is low, driving $\overline{\text{EN}}$ low enables all output buffers and driving $\overline{\text{EN}}$ high disables all output buffers.                                                                                                      |  |  |

| 23                     | 27                     | LE   | Digital Latch-Enable Input. When LE is low, the EN register is transparent; when LE is high, the EN register is transparent only when CS is low. Hardwire to V+ or GND for best crosstalk performance.                                                                                                        |  |  |

| PI             | PIN           |      | FUNCTION                                                   |  |

|----------------|---------------|------|------------------------------------------------------------|--|

| MAX467/MAX469  | MAX468/MAX470 | NAME | FUNCTION                                                   |  |

| 1              | 1             | IN0  | Analog Input 0                                             |  |

| 2, 7, 8, 9, 15 | 2, 7, 15      | GND  | Analog Ground                                              |  |

| 3              | 3             | IN1  | Analog Input 1                                             |  |

| 4, 5, 12, 13   | 4, 5, 12, 13  | V-   | Negative Power-Supply Input. Connect to -5V. Thermal path. |  |

| 6              | 6             | IN2  | Analog Input 2                                             |  |

| -              | 8             | IN3  | Analog Input 3                                             |  |

| _              | 9             | OUT3 | Buffered Analog Output 3                                   |  |

| 10             | 10            | V+   | Positive Power-Supply Input. Connect to +5V.               |  |

| 11             | 11            | OUT2 | Buffered Analog Output 2                                   |  |

| 14             | 14            | OUT1 | Buffered Analog Output 1                                   |  |

| 16             | 16            | OUT0 | Buffered Analog Output 0                                   |  |

#### **Detailed Description**

The MAX463–MAX470 have a bipolar construction, which results in a typical channel input capacitance of only 5pF, whether the channel is on or off. This low input capacitance allows the amplifiers to realize full AC performance, even with source impedances as great as  $250\Omega$ . It also minimizes switching transients because the driving source sees the same load whether the channel is on or off. Low input capacitance is critical, because it forms a single-pole RC low-pass filter with the output impedance of the signal source, and this filter can limit the system's signal bandwidth if the RC product becomes too large.

The MAX465/MAX466/MAX469/MAX470's amplifiers are internally configured for a gain of two, resulting in an overall gain of one at the cable output when driving back-terminated coaxial cable (see the section *Driving Coaxial Cable*). The MAX463/MAX464/MAX467/MAX468 are internally configured for unity gain.

#### Power-Supply Bypassing and Board Layout

To realize the full AC performance of high-speed amplifiers, pay careful attention to power-supply bypassing and board layout, and use a large, low-impedance ground plane. With multi-layer boards, the ground plane should be located on the layer that is not dedicated to a specific signal trace.

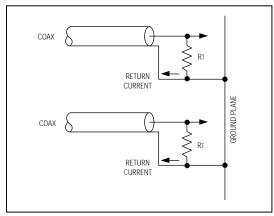

To prevent unwanted signal coupling, minimize the trace area at the circuit's critical high-impedance nodes, and surround the analog inputs with an AC ground trace (analog ground, bypassed DC power supply, etc). The analog input pins to the MAX463–MAX470 have been separated with AC ground pins (GND, V+, V-, or a hard-wired logic input) to minimize parasitic coupling, which can degrade crosstalk and/or stability of the amplifier. Keep signal paths as short as possible to minimize inductance, and ensure that all input channel traces are of equal length to maintain the phase relationship between the R, G, and B signals. Connect the coaxial-cable shield to the ground side of the  $75\Omega$  terminating resistor at the ground plane to further reduce crosstalk (see Figure 1).

Bypass all power-supply pins directly to the ground plane with  $0.1\mu F$  ceramic capacitors, placed as close to the supply pins as possible. For high-current loads, it may be necessary to include  $10\mu F$  tantalum or aluminum-electrolytic capacitors in parallel with the  $0.1\mu F$  ceramics. Keep capacitor lead lengths as short as possible to minimize series inductance; surface-mount (chip) capacitors are ideal.

Figure 1. Low-Crosstalk Layout. Return current from the termination resistor does not flow through the ground plane.

Connect all V- pins to a large power plane. The V- pins conduct heat away from the internal die, aiding thermal dissipation.

#### Differential Gain and Phase Errors

Differential gain and phase errors are critical specifications for an amplifier/buffer in color video applications, because these errors correspond directly to changes in the color of the displayed picture in composite video systems. The MAX467–MAX470 have low differential gain and phase errors, making them ideal in broadcast-quality composite color applications, as well as in RGB video systems where these errors are less significant.

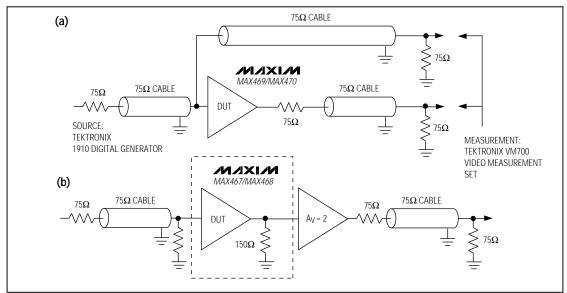

The MAX467–MAX470 differential gain and phase errors are measured with the Tektronix VM700 Video Measurement Set, with the input test signal provided by the Tektronix 1910 Digital Generator as shown in Figure 2.

Measuring the differential gain and phase of the MAX469/MAX470 (Figure 2a) is straightforward because the output amplifiers are configured for a gain of two, allowing connection to the VM700 through a back-terminated coaxial cable. Since the MAX467/MAX468 are unity-gain devices, driving a back-terminated coax would result in a gain of 1/2 at the VM700.

Figure 2b shows a test method to measure the differential gain and phase for the MAX467/MAX468. First, measure and store the video signal with the device under test (DUT) removed and replaced with a short circuit, and the  $150\Omega$  load resistor omitted. Then do another measurement with the DUT and load resistor in the circuit, and calculate the differential gain and phase errors by subtracting the results.

Figure 2. Differential Phase and Gain Error Test Circuits (a) for the MAX469/MAX470 Gain-of-Two Amplifiers, (b) for the MAX467/MAX468 Unity-Gain Amplifiers

#### **Driving Coaxial Cable**

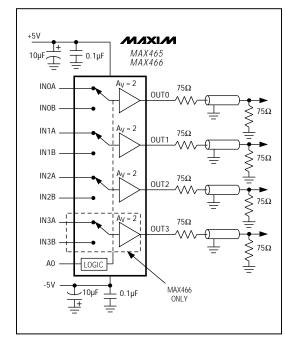

High-speed performance, excellent output current capability, and an internally fixed gain of two make the MAX465/MAX466/MAX469/MAX470 ideal for driving  $50\Omega$  or  $75\Omega$  back-terminated coaxial cables. The MAX465/MAX466/MAX469/MAX470 will drive a  $150\Omega$  load ( $75\Omega$  back-terminated cable) to  $\pm 2.5 V$ .

The Typical Operating Circuit shows the MAX465/MAX466 driving four back-terminated  $75\Omega$  video cables. The back-termination resistor (at each amplifier output) provides impedance matching at the driven end of the cable to eliminate signal reflections. It forms a voltage divider with the load impedance, which attenuates the signal at the cable output by one-half. The amplifier operates with an internal 2V/V closed-loop gain to provide unity gain at the cable's output.

#### **Driving Capacitive Loads**

Driving large capacitive loads increases the likelihood of oscillation in most amplifier circuits. This is especially true for circuits with high loop-gains, like voltage followers. The amplifier's output impedance and the capacitive load form an RC filter that adds a pole to the loop response. If the pole frequency is low enough, as when driving a large capacitive load, the circuit phase margin is degraded and oscillation may occur.

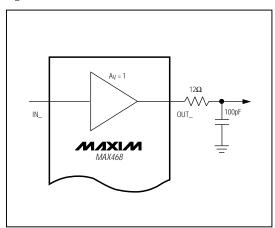

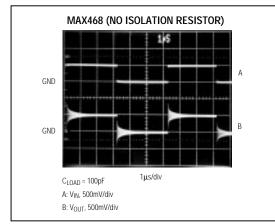

The MAX463–MAX470 phase margin and capacitive-load driving performance are optimized by internal compensation. When driving capacitive loads greater than 50pF, connect an isolation resistor between the amplifier output and the capacitive load, as shown in Figure 3.

Figure 3a. Using an Isolation Resistor with a Capacitive Load

# MAX463-MAX470

## Two-Channel, Triple/Quad RGB Video Switches and Buffers

Figure 3b. Step Response without an Isolation Resistor

# $\label{eq:GND} \text{GND} \\ \text{GND} \\ \\ \text{GND} \\ \\ \text{D} \\ \\ \text{D} \\ \text{D}$

Figure 3c. Step Response with an Isolation Resistor

#### Digital Interface

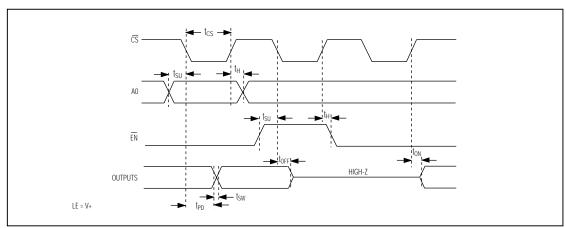

The MAX463–MAX466 multiplexer architecture provides an input transistor buffer, ensuring that no input channels are ever connected together. Select a channel by changing A0's state (A0 = 0 for channel A, and A0 = 1 for channel B) and pulsing  $\overline{\text{CS}}$  low (see Tables 1a, 1b). Figure 4 shows the logic timing diagram.

#### Output Disable (MAX463-MAX466)

When the enable input (EN) is driven to a TTL low state, it enables the MAX463–MAX466 amplifier outputs. When EN is driven high, it disables the amplifier outputs. The

disabled MAX463/MAX464 outputs exhibit a 250k $\Omega$  typical resistance. Because their internal feedback resistors are required to produce a gain of two, the MAX465/MAX466 exhibit a 1k $\Omega$  disabled output resistance.

LE determines whether  $\overline{\text{EN}}$  is latched by  $\overline{\text{CS}}$  or operates independently. When the latch-enable input (LE) is connected to V+,  $\overline{\text{CS}}$  becomes the latch control for the  $\overline{\text{EN}}$  input register. If  $\overline{\text{CS}}$  is low, both the  $\overline{\text{EN}}$  and A0 registers are transparent; once  $\overline{\text{CS}}$  returns high, both registers are latched.

Figure 4. Logic Timing Diagram

Table 1a. Amplifier and Channel Selection with LE = V+

| <u>cs</u> | ĒÑ | A0 | FUNCTION                                      |  |

|-----------|----|----|-----------------------------------------------|--|

| 0         | 0  | 0  | Enables amplifier outputs. Selects channel A. |  |

| 0         | 0  | 1  | Enables amplifier outputs. Selects channel B. |  |

| 0         | 1  | Х  | Disables amplifiers. Outputs high-Z.          |  |

| 1         | Х  | Х  | Latches all input registers. Changes nothing. |  |

Table 1b. Amplifier and Channel Selection with LE = GND

| cs | ĒÑ | A0 | FUNCTION                                                                                                                                                  |

|----|----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0  | Enables amplifier outputs. Selects channel A.                                                                                                             |

| 0  | 0  | 1  | Enables amplifier outputs.<br>Selects channel B.                                                                                                          |

| 0  | 1  | 0  | Disables amplifiers. Outputs high-Z.<br>A0 register = channel A                                                                                           |

| 0  | 1  | 1  | Disables amplifiers. Outputs high-Z.<br>A0 register = channel B                                                                                           |

| 1  | 0  | Х  | Enables amplifier outputs, latches A0 register, programs outputs to output A or B, according to the setting of A0 at $\overline{\text{CS}}$ 's last edge. |

| 1  | 1  | Х  | Disables amplifiers. Outputs high-Z.                                                                                                                      |

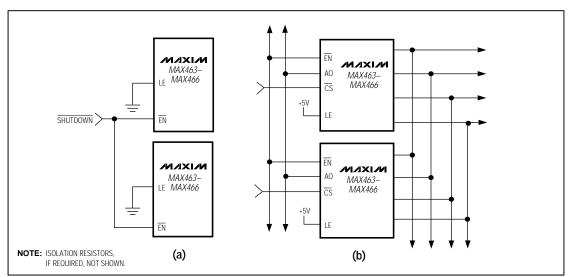

When LE is connected to ground, the  $\overline{\text{EN}}$  register is transparent and independent of  $\overline{\text{CS}}$  activity. This allows all MAX463–MAX466 devices to be simultaneously shut down, regardless of the  $\overline{\text{CS}}$  input state. Simply connect LE to ground and connect all  $\overline{\text{EN}}$  inputs together (Figure 5a). For the MAX464 and MAX466, LE must be hardwired to either V+ or ground (rather than driving LE with a gate) to prevent crosstalk from the digital inputs to INOA.

Another option for output disable is to connect LE to V+, parallel the outputs of several MAX463-MAX466s, and use  $\overline{\text{EN}}$  to individually disable all devices but the one in use (Figure 5b).

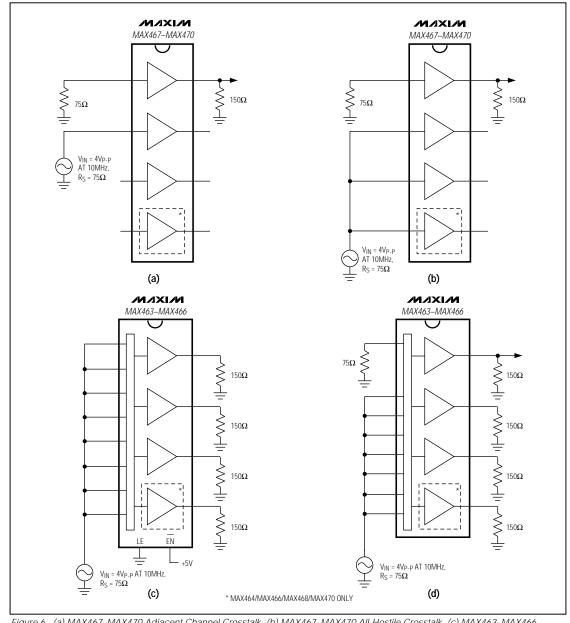

When the outputs are disabled, the off isolation from the analog inputs to the amplifier outputs is typically 70dB at 10MHz, all inputs driven with a 4Vp-p sine wave and a  $150\Omega$  load impedance. Figure 6 shows the test circuits used to measure isolation and crosstalk.

Figure 5. (a) Simultaneous Shutdown of all MAX463–MAX466, (b) Enable (EN) Register Latched by CS

Figure 6. (a) MAX467–MAX470 Adjacent Channel Crosstalk, (b) MAX467–MAX470 All-Hostile Crosstalk, (c) MAX463–MAX466 All-Hostile Off Isolation, (d) MAX463–MAX466 All-Hostile Crosstalk

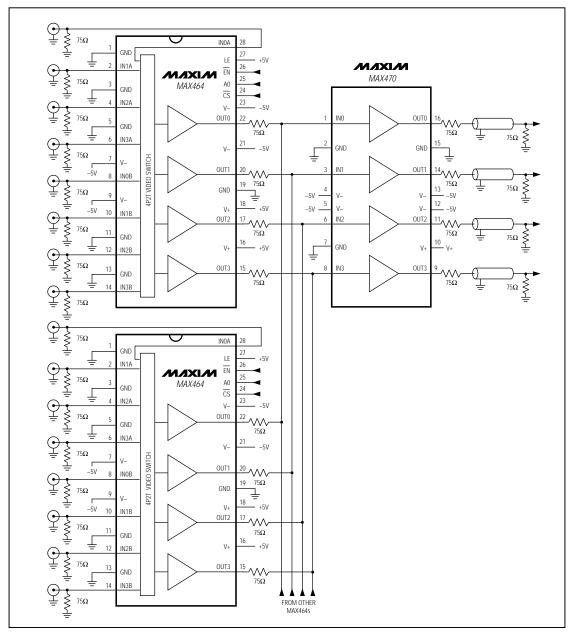

Figure 7. Higher-Order RGB + Sync Video Multiplexer

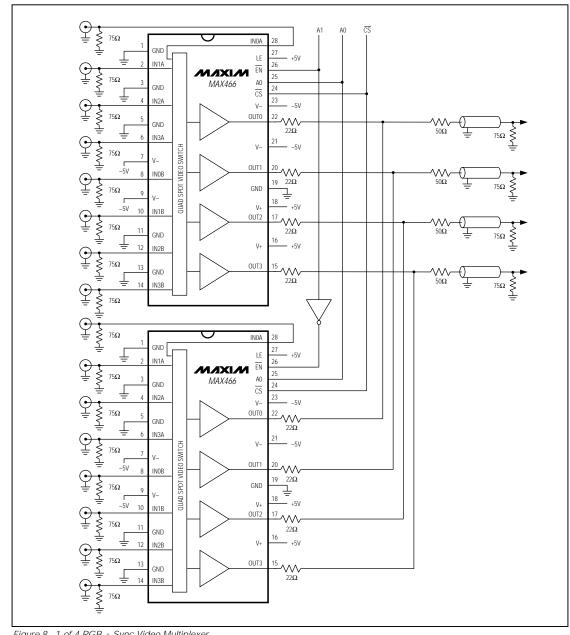

Figure 8. 1-of-4 RGB + Sync Video Multiplexer

#### \_Applications Information

#### Higher-Order RGB + Sync Video Multiplexing

Higher-order RGB video multiplexers can be realized by paralleling several MAX463/MAX464s. Connect LE to V+ and use  $\overline{\text{CS}}$  and  $\overline{\text{EN}}$  to disable all devices but the one in use. Since the disabled output resistance of the MAX463/MAX464 is 250k $\Omega$ , several devices may be paralleled to form larger RGB video multiplexer arrays without signal degradation. Connect series resistors at each amplifier's output to isolate the disabled output capacitance of each paralleled device, and use a MAX469 or MAX470 to drive the output coaxial cables (see Figure 7).

#### Paralleling MAX466s to Switch 1-of-4 RGB + Sync Signal Inputs

Figure 8 shows a 1-of-4 RGB + sync video mux/amp circuit. The  $1k\Omega$  disabled output resistance limits the number of paralleled MAX465/MAX466s to no more than two. The amplifier outputs are connected after a  $22\Omega$  isolation resistor and ahead of a  $50\Omega$  back-termination resistor, which isolates the active amplifier output from the capacitive load (5pF typ) presented by the inactive output of the second MAX466. Impedance mismatching is minimal, and the signal gain at the cable end is near 1. This minimizes ringing in the output signals. For multiplexing more than two devices, see the section *Higher Order RGB + Sync Video Multiplexing*, above.

#### Pin Configurations (continued)

#### \_Typical Operating Circuit

#### \_Ordering Information (continued)

| PART      | TEMP. RANGE    | PIN-PACKAGE           |

|-----------|----------------|-----------------------|

| MAX464CNI | 0°C to +70°C   | 28 Narrow Plastic DIP |

| MAX464CWI | 0°C to +70°C   | 28 Wide SO            |

| MAX464C/D | 0°C to +70°C   | Dice*                 |

| MAX464ENI | -40°C to +85°C | 28 Narrow Plastic DIP |

| MAX464EWI | -40°C to +85°C | 28 Wide SO            |

| MAX465CNG | 0°C to +70°C   | 24 Narrow Plastic DIP |

| MAX465CWG | 0°C to +70°C   | 24 Wide SO            |

| MAX465C/D | 0°C to +70°C   | Dice*                 |

| MAX465ENG | -40°C to +85°C | 24 Narrow Plastic DIP |

| MAX465EWG | -40°C to +85°C | 24 Wide SO            |

| MAX466CNI | 0°C to +70°C   | 28 Narrow Plastic DIP |

| MAX466CWI | 0°C to +70°C   | 28 Wide SO            |

| MAX466C/D | 0°C to +70°C   | Dice*                 |

| MAX466ENI | -40°C to +85°C | 28 Narrow Plastic DIP |

| MAX466EWI | -40°C to +85°C | 28 Wide SO            |

| MAX467CPE | 0°C to +70°C   | 16 Plastic DIP        |

| MAX467CWE | 0°C to +70°C   | 16 Wide SO            |

| MAX467C/D | 0°C to +70°C   | Dice*                 |

| MAX467EPE | -40°C to +85°C | 16 Plastic DIP        |

| MAX467EWE | -40°C to +85°C | 16 Wide SO            |

| MAX468CPE | 0°C to +70°C   | 16 Plastic DIP        |

| MAX468CWE | 0°C to +70°C   | 16 Wide SO            |

| MAX468C/D | 0°C to +70°C   | Dice*                 |

| MAX468EPE | -40°C to +85°C | 16 Plastic DIP        |

| MAX468EWE | -40°C to +85°C | 16 Wide SO            |

| MAX469CPE | 0°C to +70°C   | 16 Plastic DIP        |

| MAX469CWE | 0°C to +70°C   | 16 Wide SO            |

| MAX469C/D | 0°C to +70°C   | Dice*                 |

| MAX469EPE | -40°C to +85°C | 16 Plastic DIP        |

| MAX469EWE | -40°C to +85°C | 16 Wide SO            |

| MAX470CPE | 0°C to +70°C   | 16 Plastic DIP        |

| MAX470CWE | 0°C to +70°C   | 16 Wide SO            |

| MAX470C/D | 0°C to +70°C   | Dice*                 |

| MAX470EPE | -40°C to +85°C | 16 Plastic DIP        |

| MAX470EWE | -40°C to +85°C | 16 Wide SO            |

<sup>\*</sup> Dice are specified at T<sub>A</sub> = +25°C, DC parameters only.