Data sheet acquired from Harris Semiconductor SCHS258

January 1997

# NOT RECOMMENDED FOR NEW DESIGNS Use CMOS Technology

#### **Features**

- · Buffered Inputs

- Typical Propagation Delay: 6.4ns at V<sub>CC</sub> = 5V,

T<sub>A</sub> = 25°C, C<sub>L</sub> = 50pF

- Noninverting

- Family Features

- SCR Latchup Resistant BiCMOS Process and

#

**BiCMOS FCT Interface Logic,** Octal Register/Transceiver, Three-State

Circuit Design

- Speed of Bipolar FAST™/AS/S

- 64mA Output Sink Current

- Output Voltage Swing Limited to 3.7V at V<sub>CC</sub> = 5V

- Controlled Output Edge Rates

- Input/Output Isolation to V<sub>CC</sub>

- BiCMOS Technology with Low Quiescent Power

## **Ordering Information**

| PART NUMBER  | TEMP.<br>RANGE (°C) | PACKAGE    | PKG.<br>NO. |

|--------------|---------------------|------------|-------------|

| CD74FCT543EN | 0 to 70             | 24 Ld PDIP | E24.3       |

| CD74FCT543M  | 0 to 70             | 24 Ld SOIC | M24.3       |

| CD74FCT543SM | 0 to 70             | 24 Ld SSOP | M24.209     |

NOTE: When ordering the suffix M and SM packages, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

#### **Pinout**

CD74FCT543 (PDIP, SOIC, SSOP) TOP VIEW

| LEBA 1  | $egin{array}{cccccccccccccccccccccccccccccccccccc$ | 24 | vcc         |

|---------|----------------------------------------------------|----|-------------|

| OEBA 2  | ]                                                  | 23 | CEBA        |

| A0 3    |                                                    | 22 | B0          |

| A1 4    |                                                    | 21 | B1          |

| A2 5    | A FAN                                              | 20 | B2          |

| A3 6    | NA.                                                | 19 | B3          |

| A4 7    |                                                    | 18 | B4          |

| A5 8    | 1                                                  | 17 | B5          |

| A6 9    | ]                                                  | 16 | B6          |

| A7 10   | 1                                                  | 15 | B7          |

| CEAB 11 | 1                                                  | 14 | <b>LEAB</b> |

| GND 12  |                                                    | 13 | OEAB        |

|         |                                                    |    |             |

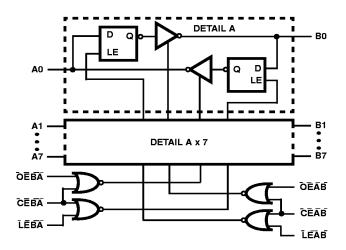

## Functional Diagram

TRUTH TABLE For A to B (Symmetric with B to A)

|      | INPUTS |      | LATCH STATUS | OUTPUT BUFFERS             |

|------|--------|------|--------------|----------------------------|

| CEAB | LEAB   | OEAB | A TO B       | B0 THRU B7                 |

| Н    | X      | X    | Storing      | High Z                     |

| Х    | Н      | -    | Storing      | -                          |

| Х    | -      | Н    | -            | High Z                     |

| L    | L      | L    | Transparent  | Current A Inputs           |

| L    | Н      | L    | Storing      | Previous A Inputs (Note 1) |

#### NOTE:

1. Before **LEAB** LOW to HIGH Transition

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

A to B data flow shown; B to A flow control is the same, except using  $\overline{\text{CEBA}}$ ,  $\overline{\text{LEBA}}$ , and  $\overline{\text{OEBA}}$ .

# IEC Logic Symbol

#

#

#### Thermal Information

|                                          | •                      |

|------------------------------------------|------------------------|

| Thermal Resistance (Typical, Note 2)     | θ <sub>JA</sub> (°C/W) |

| PDIP Package                             | 75                     |

| SOIC Package                             | 75                     |

| SSOP Package                             |                        |

| Maximum Junction Temperature             | 150°C                  |

| Maximum Storage Temperature Range65      | 5°C to 150°C           |

| Maximum Lead Temperature (Soldering 10s) |                        |

| (SOIC and SSOP-Lead Tips Only)           |                        |

#### **Operating Conditions**

| Operating Temperature Range (TA)      | 0°C to 70°C            |

|---------------------------------------|------------------------|

| Supply Voltage Range, V <sub>CC</sub> | 4.75V to 5.25V         |

| DC Input Voltage, V <sub>1</sub>      | 0 to V <sub>CC</sub>   |

| DC Output Voltage, VO                 | 0 to ≤ V <sub>CC</sub> |

| Input Rise and Fall Slew Rate, dt/dv  | 0 to 10ns/V            |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

2.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications Commercial Temperature Range 0°C to 70°C, V<sub>CC</sub> Max = 5.25V, V<sub>CC</sub> Min = 4.75V

|                                                                                      |                  |                                                 |                     |                     | AME | BIENT TEMI | PERATURE | E (T <sub>A</sub> ) |       |

|--------------------------------------------------------------------------------------|------------------|-------------------------------------------------|---------------------|---------------------|-----|------------|----------|---------------------|-------|

|                                                                                      |                  | TEST CO                                         | NDITIONS            |                     | 25  | o°C        | 0°C T    | O 70°C              | 1     |

| PARAMETER                                                                            | SYMBOL           | V <sub>I</sub> (V)                              | I <sub>O</sub> (mA) | V <sub>CC</sub> (V) | MIN | MAX        | MIN      | MAX                 | UNITS |

| High Level Input Voltage                                                             | V <sub>IH</sub>  |                                                 |                     | 4.75 to<br>5.25     | 2   | -          | 2        | -                   | ٧     |

| Low Level Input Voltage                                                              | V <sub>IL</sub>  |                                                 |                     | 4.75 to<br>5.25     | -   | 0.8        | -        | 0.8                 | ٧     |

| High Level Output Voltage                                                            | V <sub>OH</sub>  | $V_{ m IH}$ or $V_{ m IL}$                      | -15                 | Min                 | 2.4 | -          | 2.4      | -                   | ٧     |

| Low Level Output Voltage                                                             | $V_{OL}$         | $V_{IH}$ or $V_{IL}$                            | 64                  | Min                 | -   | 0.55       | -        | 0.55                | ٧     |

| High Level Input Current                                                             | lін              | V <sub>CC</sub>                                 |                     | Max                 | -   | 0.1        | -        | 1                   | μА    |

| Low Level Input Current                                                              | I <sub>IL</sub>  | GND                                             |                     | Max                 | -   | -0.1       | -        | -1                  | μΑ    |

| Three-State Leakage Current                                                          | lozh             | V <sub>CC</sub>                                 |                     | Max                 | -   | 0.5        | -        | 10                  | μА    |

|                                                                                      | lozL             | GND                                             |                     | Max                 | -   | -0.5       | -        | -10                 | μА    |

| Input Clamp Voltage                                                                  | V <sub>IK</sub>  | V <sub>CC</sub> or<br>GND                       | -18                 | Min                 | =   | -1.2       | -        | -1.2                | ٧     |

| Short Circuit Output Current (Note 3)                                                | los              | V <sub>O</sub> = 0<br>V <sub>CC</sub> or<br>GND |                     | Max                 | -60 | -          | -60      | -                   | mA    |

| Quiescent Supply Current,<br>MSI                                                     | lcc              | V <sub>CC</sub> or<br>GND                       | 0                   | Max                 | -   | 8          | -        | 80                  | μА    |

| Additional Quiescent Supply<br>Current per Input Pin<br>TTL Inputs High, 1 Unit Load | Δl <sub>CC</sub> | 3.4V<br>(Note 4)                                |                     | Max                 | -   | 1.6        | -        | 1.6                 | mA    |

#### NOTES:

- 3. Not more than one output should be shorted at one time. Test duration should not exceed 100ms.

- 4. Inputs that are not measured are at  $V_{CC}$  or GND.

- 5. FCT Input Loading: All inputs are 1 unit load. Unit load is ΔI<sub>CC</sub> limit specified in Electrical Specifications table, e.g., 1.6mA Max. at 70°C.

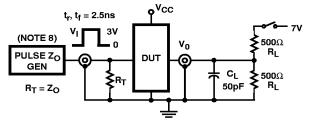

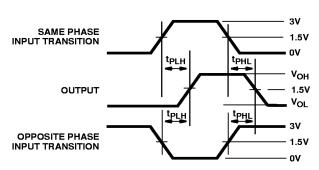

Switching Specifications Over Operating Range FCT Series  $t_r$ ,  $t_f$  = 2.5ns,  $C_L$  = 50pF,  $R_L$  (Figure 4)

|                                                                                                          |                                     |                     | 25°C | 0°C TO 70°C |     |      |       |

|----------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------|------|-------------|-----|------|-------|

| PARAMETER                                                                                                | SYMBOL                              | V <sub>CC</sub> (V) | TYP  | MIN         | TYP | MAX  | UNITS |

| Propagation Delays                                                                                       |                                     |                     |      |             |     |      |       |

| $An \leftrightarrow Bn$                                                                                  | t <sub>PLH</sub> , t <sub>PHL</sub> | 5                   | 6.4  | 2.5         | -   | 8.5  | ns    |

| LEBA to An or LEAB to Bn                                                                                 | t <sub>PLH</sub> , t <sub>PHL</sub> | 5                   | 9.4  | 2.5         | -   | 12.5 | ns    |

| CEBA or CEAB to An or Bn                                                                                 | t <sub>PLZ</sub> , t <sub>PHZ</sub> | 5                   | 6.8  | 2           | -   | 9    | ns    |

|                                                                                                          | t <sub>PZL</sub> , t <sub>PZH</sub> | 5                   | 9    | 2           | -   | 12   | ns    |

| Power Dissipation Capacitance                                                                            | C <sub>PD</sub><br>(Note 6)         | -                   | 49   | -           | 49  | -    | pF    |

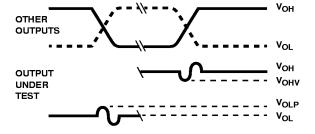

| Minimum (Valley) V <sub>OHV</sub> During Switching of<br>Other Outputs (Output Under Test Not Switching) | V <sub>OHV</sub>                    | 5                   | 0.5  | -           | -   | -    | V     |

| Maximum (Peak) V <sub>OLP</sub> During Switching of<br>Other Outputs (Output Under Test Not Switching)   | V <sub>OLP</sub>                    | 5                   | 1    | -           | -   | -    | ٧     |

| Input Capacitance                                                                                        | Cl                                  | -                   | -    | -           | -   | 10   | pF    |

| Input/Output Capacitance                                                                                 | C <sub>I/O</sub>                    | -                   | -    | -           | -   | 15   | pF    |

| 1077                                                                                                     | •                                   | •                   |      | •           | -   | -    | •     |

#### NOTE:

6.  $C_{PD}$ , measured per flip-flop, is used to determine the dynamic power consumption.  $P_D$  (per package) =  $V_{CC} I_{CC} + \Sigma (V_{CC}^2 f_I C_{PD} + V_O^2 f_O C_L + V_{CC} \Delta I_{CC} D)$  where:  $V_{CC}$  = supply voltage

$\Delta I_{CC}$  = supply voltage  $\Delta I_{CC}$  = flow through current x unit load  $C_L$  = output load capacitance D = duty cycle of input high

f<sub>O</sub> = output frequency f<sub>I</sub> = input frequency

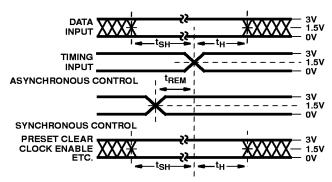

## **Prerequisite for Switching**

|                                 |                 |                     | 25°C | 0°C T | O 70°C |       |

|---------------------------------|-----------------|---------------------|------|-------|--------|-------|

| PARAMETER                       | SYMBOL          | V <sub>CC</sub> (V) | TYP  | MIN   | MAX    | UNITS |

| Data to Latch Enable Setup Time | t <sub>SU</sub> | 5<br>(Note 7)       | -    | 3     | -      | ns    |

| Data to Latch Enable Hold Time  | t <sub>H</sub>  | 5                   | -    | 2     | -      | ns    |

| Latch Enable Pulse Width        | t <sub>W</sub>  | 5                   | -    | 9     | -      | ns    |

#### NOTE:

7. 5V: Minimum is at 4.75V for 0°C to 70°C, Typical is at 5V.

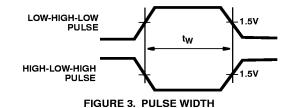

#### Test Circuits and Waveforms

#### NOTE:

8. Pulse Generator for All Pulses: Rate  $\leq$  1.0MHz;  $Z_{OUT} \leq$  50 $\Omega$ ;  $t_f, t_r \le 2.5 ns.$

FIGURE 1. TEST CIRCUIT

FIGURE 2. SETUP, HOLD, AND RELEASE TIMING

#### **SWITCH POSITION**

| TEST                                                                      | SWITCH |

|---------------------------------------------------------------------------|--------|

| t <sub>PLZ</sub> , t <sub>PZL</sub> , Open Drain                          | Closed |

| t <sub>PHZ</sub> , t <sub>PZH</sub> , t <sub>PLH</sub> , t <sub>PHL</sub> | Open   |

#### **DEFINITIONS:**

C<sub>L</sub> = Load capacitance, includes jig and probe capacitance.

$R_T$  = Termination resistance, should be equal to  $Z_{OLIT}$  of the Pulse Generator.

$V_{IN} = 0V \text{ to } 3V.$

Input:  $t_r = t_f = 2.5$ ns (10% to 90%), unless otherwise specified

DISABLE **ENABLE** 3V **CONTROL INPUT** 1.5V nν t<sub>PLZ</sub> tpzl 3.5V OUTPUT NORMALLY LOW SWITCH 0.3V V<sub>OL</sub> t<sub>PHZ</sub>|• <sup>t</sup>PZH V<sub>OH</sub> 0.3V OUTPUT NORMALLY HIGH SWITCH

OPEN

#### FIGURE 5. PROPAGATION DELAY

#### NOTES:

- 9. V<sub>OLP</sub> is measured with respect to a ground reference near the output under test. V<sub>OHV</sub> is measured with respect to V<sub>OH</sub>.

- 10. Input pulses have the following characteristics:  $P_{RR} \le 1MHz$ ,  $t_r = 2.5ns$ ,  $t_f = 2.5ns$ , skew 1ns.

- 11. R.F. fixture with 700MHz design rules required. IC should be soldered into test board and bypassed with 0.1µF capacitor. Scope and probes require 700MHz bandwidth.

#### FIGURE 6. SIMULTANEOUS SWITCHING TRANSIENT WAVEFORMS