For Immediate Assistance, Contact Your Local Salesperson 急出货

4127

# LOGARITHMIC AMPLIFIER

### **FEATURES**

- ACCEPTS INPUT VOLTAGES OR CURRENTS OF EITHER POLARITY

- WIDE INPUT DYNAMIC RANGE

6 Decades of Current

4 Decades of Voltage

- VERSATILE Log, Antilog, and Log Ratio Capability

### **DESCRIPTION**

Packaged in a ceramic double wide DIP, the 4127 is the first hybrid logarithmic amplifier that accepts signals of either polarity from current or voltage sources. A special purpose monolithic chip, developed specifically for logarithmic conversions, functions accurately for up to six decades of input

current and four decades of input voltage. In addition, a current inverter and a precise internal reference allow pin programming of the 4127 as a logarithmic, log ratio, or antilog amplifier.

To further increase its versatility and reduce your system cost, the 4127 has an uncommitted operational amplifier in its package that can be used as a buffer, inverter, filter, or gain element.

The 4127 is available with initial accuracies (log conformity) of 0.5% and 1.0%, and operates over an ambient temperature range of -10°C to +70°C.

With its versatility and high performance, the 4127 has many applications in signal compression, transducer linearization, and phototube buffering. Manufacturers of medical equipment, analytical instruments, and process control instrumentation will find the 4127 a low cost solution to many signal processing problems.

**1**731365 0028676 04T

### **SPECIFICATIONS**

#### **ELECTRICAL**

Typical Specifications at +25°C with rated supplies, unless otherwise noted.

|                                                            |                                                                   | s otherwise holed.            |

|------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------|

| MODEL                                                      | 4127KG                                                            | 4127JG                        |

| ACCURACY(1), % of FSR                                      |                                                                   |                               |

| Current Source Input: 1nA to 1mA                           | 0.5% max                                                          | 1% max                        |

| Voltage Input: 1mV to 10V                                  | 0.5% max                                                          | 1% max                        |

| INPUT                                                      |                                                                   | ·                             |

| Current Source Input, Pin 4                                | +1nA to +1mA                                                      |                               |

| Current Source Input, Pin 7                                | -1nA to -1mA                                                      |                               |

| Reference Current Input, Pin 2                             | +1µA to +1mA                                                      |                               |

| Absolute Maximum Inputs                                    | ±10mA or ±Supply Volts                                            |                               |

| OUTPUT                                                     |                                                                   | -                             |

| Voltage                                                    | ±10V                                                              |                               |

| Current                                                    | ±5mA                                                              |                               |

| Impedance                                                  | 1(                                                                | 0Ω                            |

| FREQUENCY RESPONSE                                         |                                                                   |                               |

| -3dB Small Signal at Current Input                         |                                                                   |                               |

| of 100μA                                                   | 90kHz                                                             |                               |

| of 10µA                                                    | 50kHz                                                             |                               |

| of 1µA<br>of 100nA                                         |                                                                   | Hz                            |

| of 100A                                                    | 250Hz<br>80Hz                                                     |                               |

| Step Response to within ±1% of                             | , BU                                                              | mz                            |

| Final Value (I <sub>R</sub> = 1µA, A = 5)                  | 10ms                                                              |                               |

| STABILITY                                                  |                                                                   |                               |

| Scale Factor Drift (ΔA/°C)                                 | +0.00                                                             | 0EA (9C                       |

| Reference Current Drift (ΔI <sub>p</sub> /°C)              | ±0.0005A/°C<br>±0.001 l <sub>n</sub> /°C for l <sub>n</sub> ≥ 1μA |                               |

| , , , , , , , , , , , , , , , , , , ,                      |                                                                   | 400 nA < i <sub>B</sub> < 1μΑ |

| Input Offset Current Drift (ΔI <sub>s</sub> /°C)           | 10pA at +25°C, Doubles Every 10°C                                 |                               |

| Input Offset Voltage Drift                                 | ±10µV/°C                                                          |                               |

| Accuracy vs Supply Variation                               |                                                                   |                               |

| Reference Current                                          |                                                                   | 011 <sub>R</sub> /V           |

| Input Offset Voltage                                       | ±300μV/V                                                          |                               |

| Input Noise - Current Input<br>Input Noise - Voltage Input | 1pA, rms, 10Hz to 10kHz                                           |                               |

|                                                            | 10μA, rms, 10Hz to 10kHz                                          |                               |

| UNCOMMITTED OP AMP CHARACTERISTICS                         |                                                                   |                               |

| Input Offset Voltage<br>Input Bias Current                 |                                                                   | mV                            |

| Input Impedance                                            | 40nA<br>1MΩ                                                       |                               |

| Large Signal Voltage Gain                                  | 85dB                                                              |                               |

| Output Current                                             |                                                                   | nA                            |

| TEMPERATURE RANGE                                          |                                                                   |                               |

| Specification                                              | 0°C to +60°C                                                      |                               |

| Operating                                                  | 0°C to +60°C<br>−10°C to +70°C                                    |                               |

| Storage                                                    |                                                                   | 0 +125°C                      |

| POWER SUPPLY REQUIREMENTS                                  |                                                                   |                               |

| Rated Supply Voltages                                      | ſ                                                                 | VDC                           |

| Supply Voltage Range                                       | ±15VDC<br>±14VDC to ±16VDC                                        |                               |

| Supply Current Drain                                       | TI44DC 10 EIBADC                                                  |                               |

| at Quiescent, max                                          | ±20mA                                                             |                               |

| at Full Load, max                                          |                                                                   | 5mA                           |

|                                                            |                                                                   | ·                             |

NOTE: (1) Log conformity at 25°C.

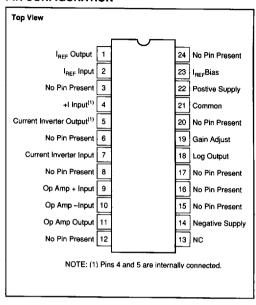

### PIN CONFIGURATION

### PACKAGE INFORMATION(1)

| MODEL  | PACKAGE | PACKAGE DRAWING<br>NUMBER |

|--------|---------|---------------------------|

| 4127KG | 24-Pin  | 075                       |

| 4127JG | 24-Pin  | 075                       |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

### For Immediate Assistance, Contact Your Local Salesperson

### TYPICAL PERFORMANCE CURVES

At +25°C with rated supplies, unless otherwise noted.

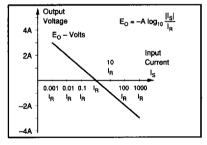

IISI AND OUTPUT LOG RELATIONSHIP OF VOLTAGE IN TERMS OF "A"

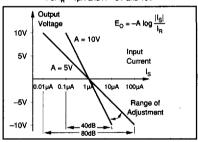

RELATIONSHIP OF  $\frac{|I_S|}{I_R}$  AND OUTPUT VOLTAGE For I<sub>R</sub> = 1µA and A = 5V and 10V

### **DISCUSSION OF SPECIFICATIONS**

#### **ACCURACY**

The deviation from the ideal output voltage defined as a percent of the full scale output voltage.

#### INPUT/OUTPUT RANGE

The log relationships of -A log

$$\frac{I_s}{I_R}$$

and -A log  $\frac{E_s}{I_RR}$  are

subject to the constraints specified. The 4127 can be operated with inputs lower than those given, but the accuracy will be degraded.

#### **FREQUENCY RESPONSE**

The small-signal frequency response varies considerably with signal level and scaling, so the frequency response is specified under several different operating conditions.

#### STABILITY

The use of a monolithic transistor quad and low-drift amps minimizes drift, but some drift remains in the scale-factor, reference current, and input offset. Input offset consists of a bias current plus the op amp input voltage offset divided by the signal source resistance. Also, there is some slight drift in conformity to the log function and in output amplifier offset, but this is generally negligible.

### THEORY OF OPERATION

The 4127 is a complete logarithmic amplifier that can be pin-programmed to accept input currents or voltages of either polarity. By making use of the internal current inverter, reference current generator, log ratio element, and uncommitted on amp, you can generate a variety of logarith-

mic functions, including the log ratio of two signals, the logarithm of an input signal, or the antilog of an input signal. The unique FET-input current-inverting element removes the polarity limitations present in most conventional log amplifiers.

Utilizing the inherent exponential characteristics of transistor functions, the 4127 calculates accurate log functions for input currents from 1nA to 1mA, or input voltages from 1mV to 10V. Carefully matched monolithic quad transistors and temperature sensitive gain elements are used to produce a log amplifier with excellent temperature characteristics.

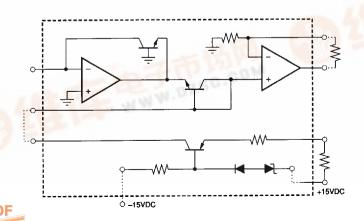

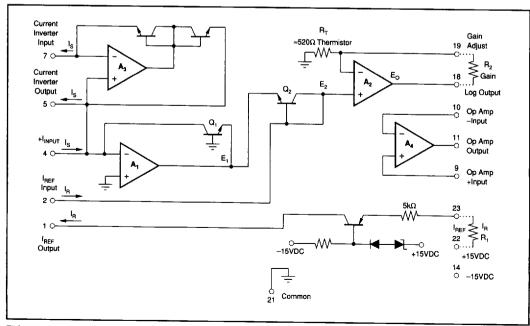

A functional diagram of the 4127 circuit is shown in Figure 1. In addition to the basic log amplifier, the 4127 contains a separate internal current source, a current inverter, and an uncommitted operational amplifier. The current inverter accurately converts negative input current to a positive current of equal magnitude.

The 4127 is capable of accurately logging input current over a 120dB range, but to use this full range, good shielding practice must be followed. A current source input is, by definition, a high impedance source and is therefore subject to electrostatic pickup.

The input op amps,  $A_1$  and  $A_3$ , have FET input stages for low noise and very-low input bias current. The op amp,  $A_1$ , will make the collector current of  $Q_1$  equal to the signal input current  $I_s$ , and the collector current of  $Q_2$  will be the reference input current  $I_R$ .

From the semiconductor junction characteristics, the base-to-emitter voltage will be:

$$V_{BE} \approx \frac{mKT}{q} \ell n \frac{I_C}{I_L}$$

where:  $I_c$  = Collector current  $I_L$  = Reverse saturation current q, m, K = Contstants T = Absolute temperature

So

$$E_1 = -\frac{mKT_1}{q} \ \ell n \ \frac{I_s}{I_{L1}}$$

and  $E_2 - E_1 = \frac{mKT_2}{q} \ \ell n \ \frac{I_R}{I_{L2}}$

If the transistors  $\mathbf{Q}_1$  and  $\mathbf{Q}_2$  are at the same temperature and have matched characteristics, then:

$$E_2 = \frac{mKT}{q} \left[ \ell n \frac{I_R}{I_L} - \ell n \frac{I_S}{I_L} \right]$$

$$E_2 = \frac{-mKT}{q} \ell n \frac{I_S}{I_R}$$

The output op amp,  $A_2$ , provides a voltage gain of approximately  $(R_T + R_2)/R_T$ , and the value of (mKT)/q is about 26mV at room temperature. Since resistor  $R_T$  varies with temperature to compensate for gain drift, the output voltage,  $E_0$ , expressed as a log will be:

FIGURE 1. Functinal Diagram.

### For Immediate Assistance, Contact Your Local Salesperson

$$E_{\rm O} = -A \log_{10} \frac{I_{\rm S}}{I_{\rm R}},$$

where A

$$\approx \frac{R_T + R_2}{R_T} (26 mV) \frac{1}{0.434}$$

,  $R_T \approx 520 \Omega$

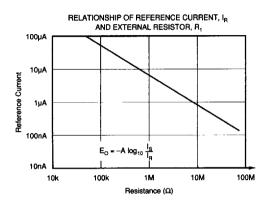

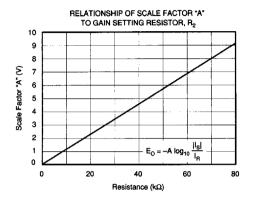

The external resistor  $R_1$  sets the reference current  $I_R$  and resistor  $R_2$  sets the scale-factor "A".  $R_1$  and  $R_2$  must be trimmed to the desired values, but the approximate relationships are shown in Typical Performance Curves.

The relationship between the input current,  $I_s$ , and the output voltage,  $E_o$ , in terms of the externally adjusted parameters,  $I_R$  and "A", is illustrated in Typical Performance Curves. This relationship is, of course, restricted to values of  $I_s$  between 1nA and 1mA and output voltages of less than  $\pm 10V$ .

# CHOOSING THE OPTIMUM SCALE FACTOR AND REFERENCE CURRENT

To minimize the effects of output offset and noise, it is usually best to use the full  $\pm 10$ V output range. Once an output range of  $\pm 10$ V has been chosen, then "A" and  $I_R$  can be determined from the Min/Max of the input current,  $I_S$ .

$$E_{\rm o} = - \; A \; \log \; \frac{I_{\rm s}}{I_{\rm R}}$$

, where  $I_{\rm MIN} < I_{\rm s} < I_{\rm MAX}$

The output range of  $\pm 10 V$  for an input range of  $I_{\rm MIN}$  to  $I_{\rm MAX}$  means that:

+10 = -A log

$$\frac{I_{\text{MIN}}}{I_{\text{R}}}$$

and -10 = - A log  $\frac{I_{\text{MAX}}}{I_{\text{R}}}$

Adding these two equations together

$$\log \frac{-I_{\text{MAX}} + I_{\text{MIN}}}{I_{\text{R}}^{\ 2}} \ = 0, \ \text{or} \ I_{\text{R}} = \sqrt{I_{\text{MAX}} \ I_{\text{MIN}}}$$

The value for A can be found from:

$$10 = A \log \frac{I_{\text{MAX}}}{\sqrt{I_{\text{MAX}} I_{\text{MIN}}}}$$

In terms of the input current range for  $I_s$ , the values for  $I_R$  and A that will provide a full  $\pm 10V$  output swing are:

$$I_{R} = \sqrt{I_{MAX}~I_{MIN}}~and~~A = \frac{10}{\log \frac{I_{MAX}}{I_{*}}}$$

#### **EXAMPLE**

Assume that  $I_{MIN}$  is +10nA and  $I_{MAX}$  is +100 $\mu$ A. This is an 80dB range.

$$I_R = \sqrt{I_{MAX} I_{MIN}} = \sqrt{(10^{-4}) (10^{-8})} = 10^{-6}, \text{ or } 1\mu\text{A}.$$

$$\frac{I_{\text{MAX}}}{I_{\text{P}}} = \frac{10^{-4}}{10^{-6}} = 100$$

$$\log \frac{I_{MAX}}{I_{b}} = 2; \text{ So, A} = 5$$

For an I<sub>B</sub> of 1µA and A of 5,

$$E_{o} = -5\log \frac{I_{s}}{1\mu A}$$

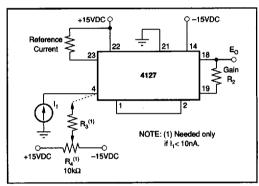

### **CONNECTION DIAGRAMS**

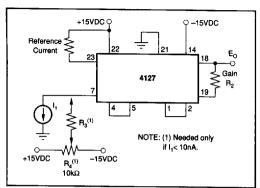

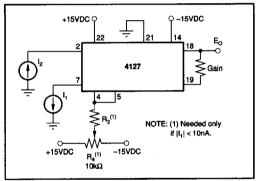

Transfer function is  $E_0 = -A \log \frac{I_1}{I_R}$  where  $I_1$  is a positive

input current and  $I_R$  is the resistor-programmed internal reference current (see Figure 2).

FIGURE 2. Transfer Function When I, is Positive.

#### **ADJUSTMENT PROCEDURE**

- Refer to Choosing the Optimum Scale Factor and Reference Current.

- 2. Apply  $|I_1| = I_R$ , adjust  $R_1$  such that  $E_0 = 0$ .

- 3. Apply  $II_1I = I_{MAX}$ , adjust  $R_2$  for the proper output voltage.

- 4. Repeat steps 2 and 3 if necessary.

- Ignore this step if |I<sub>1MIN</sub>| ≥ 10nA. Otherwise, apply |I<sub>1</sub>| = 1nA, make R<sub>3</sub> = 1kMΩ and adjust R<sub>4</sub> for the proper output voltage. For R<sub>3</sub>, a single resistor is recommended. A voltage divider network is difficult to use due to amplifier offset voltage.

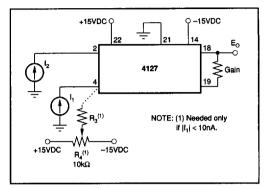

Transfer function is  $E_o = -A \log \frac{|I_1|}{I_R}$  where  $I_1$  is a negative

input current and  $I_{\rm R}$  is the resistor-programmed internal reference current (see Figure 3).

FIGURE 3. Transfer Function When I, is Negative.

### **ADJUSTMENT PROCEDURE**

- Refer to Choosing the Optimum Scale Factor and Reference Current.

- 2. Apply  $|I_1| = I_R$  adjust  $R_1$  such that  $E_0 = 0$ .

- 3. Apply  $|I_1| = I_{MAX}$ , adjust  $R_2$  for the proper output voltage

- 4. Repeat steps 2 and 3 if necessary.

- Ignore this step if |I<sub>IMIN</sub>| ≥ 10nA. Otherwise, apply |I<sub>i</sub>| = 1nA, make R<sub>3</sub> = 1kMΩ and adjust R<sub>4</sub> for the proper output voltage. For R<sub>3</sub>, a single resistor is recommended. A voltage divider network is difficult to use due to amplifier offset voltage.

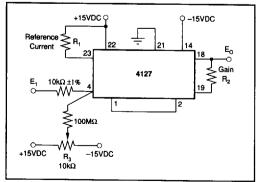

Transfer function is  $E_0 = -A \log \frac{E_1}{R_4 I_R}$ , where  $E_1$  is a positive input voltage and  $I_R$  is the resistor-programmed internal reference current (see Figure 4).

FIGURE 4. Transfer Function When E, is Positive.

### ADJUSTMENT PROCEDURE

- Refer to Choosing the Optimum Scale Factor and Reference Current.

- 2. Apply  $E_1 = I_R$  (10k $\Omega$ ), adjust  $R_1$  such that  $E_0 = 0$ .

- 4. Apply  $E_1 = E_{MIN}$ , adjust  $R_3$  for the proper output.

- 5. Repeat steps 2 through 4 if necessary.

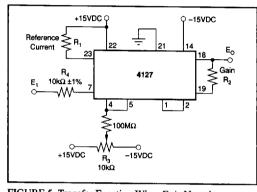

Transfer function is  $E_0 = -A \log \frac{|E_1|}{R_4 I_R}$ , where  $E_1$  is a negative input voltage and  $I_R$  is the resistor-programmed internal reference current (see Figure 5).

FIGURE 5. Transfer Function When E, is Negative.

#### ADJUSTMENT PROCEDURE

- Refer to Choosing the Optimum Scale Factor and Reference Current.

- 2. Apply  $|E_1| = I_R$  (10k $\Omega$ ), adjust  $R_1$  such that  $E_0 = 0$ .

- 3. Apply  $|E_1| = E_{MAX}$ , adjust  $R_2$  for the proper output voltage.

- 4. Apply  $|E_1| = E_{MIN}$ , adjust  $R_3$  for the proper output.

- 5. Repeat steps 2 through 4 if necessary.

Transfer function is  $E_0 = -A \log \frac{|I_1|}{|I_2|}$  with  $I_1$  and  $I_2$  negative;  $|I_1| \ge 1 nA$ ,  $|I_2| \ge 1 \mu A$  (see Figure 6).

FIGURE 6. Transfer Function When I, and I, are Negative.

### For Immediate Assistance, Contact Your Local Salesperson

#### **ADJUSTMENT PROCEDURE**

- Refer to Choosing the Optimum Scale Factor and Reference Current.

- 2. No further adjustment is necessary if  $I_{1 \text{ MIN}} \geq 10 \text{nA}$ , otherwise connect the  $R_3$  and  $R_4$  network, with  $R_4 = 10 \text{k}\Omega$  and  $R_3 = 10^9 \Omega$ . Adjust  $R_4$  for proper output voltage after adjusting gain errors. Since the voltage at pin 4 is in the range of  $\pm 5 \text{mV}$ , it is not practical to use a T-network to replace  $R_3$ .

Transfer function is  $E_0 = -A \log \frac{|I_1|}{I_2}$  with  $I_1$  negative,  $I_2$  positive;  $|I_1| \ge 1 nA$ ,  $I_2 \ge 1 \mu A$  (see Figure 7).

FIGURE 7. Transfer Function When  $I_1$  is Negative,  $I_2$  is Positive.

### **ADJUSTMENT PROCEDURE**

- Refer to Choosing the Optimum Scale Factor and Reference Current.

- No further adjustment is necessary if II<sub>1</sub>I<sub>MIN</sub> ≥ 10nA, otherwise connect the R<sub>3</sub> and R<sub>4</sub> network, with R<sub>4</sub> = 10kΩ and R<sub>3</sub> = 10°Ω. Adjust R<sub>4</sub> for proper output voltage after adjusting gain errors. Since the voltage at pin 4 is in the range of ±5mV, it is not practical to use a T-network to replace R<sub>3</sub>.

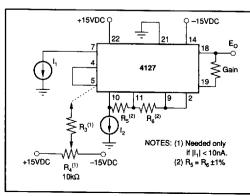

Transfer function is  $E_0 = -A \log \frac{I_1}{I_2}$  with  $I_1$  and  $I_2$  positive;  $I_1 \ge 1nA$ ,  $I_2 \ge 1\mu A$  (see Figure 8).

#### **ADJUSTMENT PROCEDURE**

- Refer to Choosing the Optimum Scale Factor and Reference Current.

- No further adjustment is necessary if I<sub>1 MIN</sub> ≥ 10nA, otherwise connect the R<sub>3</sub> and R<sub>4</sub> network, with R<sub>4</sub> = 10kΩ and R<sub>3</sub> = 10°Ω. Adjust R<sub>4</sub> for proper output voltage after adjusting gain errors. Since the voltage at pin 4 is in the

range of  $\pm 5$ mV, it is not practical to use a T-network to replace  $R_3$ .

FIGURE 8. Transfer Function When I, and I, is Positive.

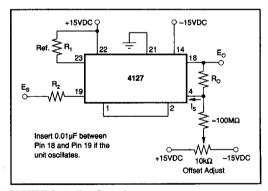

### **ANTILOG OPERATION**

The 4127 can also perform the antilog function. The output is connected through a resistor,  $R_0$ , into the current input, pin 4. The input signal is connected through a gain resistor to pin 19 as shown in Figure 9.

FIGURE 9. Antilog Operation.

These connections form an implicit loop for computing the antilog function. From the block diagram of Figure 1, the voltage at the inverting input of the output amplifier  $A_2$  must equal  $E_2$ , so

$$E_2 \approx \frac{R_T}{R_T + R_2} E_S, R_T \approx 520\Omega$$

Since the output is connected through  $R_0$  to pin 4, the current  $I_s$  will equal  $E_0/R_0$  and  $E_2$  will be

$$E_2 = -\frac{mKT}{q} \ell n \frac{E_0}{R_0 I_R}$$

Combining expressions for E2 gives the relationship:

$$\begin{split} \frac{R_{_T}}{R_{_T}+R_{_2}} E_s &= -\frac{mKT}{q} \ \ell n \ \frac{E_o}{R_o I_R} \\ &- \frac{E_s}{A} \ = \log \frac{E_o}{R_o I_R} \end{split}$$

where:

$$A \approx \frac{R_T + R_2}{R_T} (26mV) \frac{1}{0.434}$$

$$E_0 = R_0 I_R Antilog - \frac{E_S}{A}$$

Setting  $R_o$  and  $I_R$  will set the scale factor. For example, an  $R_o$  of  $1M\Omega$  and  $I_R$  of  $1\mu A$  will give a scale factor of unity

and

$$E_0 = Antilog - \frac{E_S}{A}$$