# 500ns MAX. 12-BIT A/D CONVERTER

4193/5

The 4193/4195 A/D converters are intended for applications requiring extremely fast, precise analog-to-digital conversion. The conversion speed is 500ns maximum. Proven monolithic circuits and recent advanced designs are combined to produce a device with improved performance but low cost. These devices are manufactured using thick and thin film hybrid technology.

The 4193 has an input range of 0 to 5V, while the 4195 input range is ±2.5V. Factory laser trims adjust all parameters so that most applications will require no additional adjustment. An optional gain adjust is provided for the user's convenience.

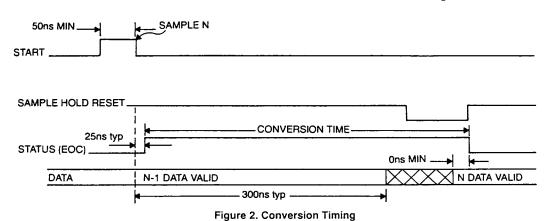

Signals are provided to interface the 4193 between the user's digital circuits and a track/hold (T/H). Conversions are initiated by a single pulse 50ns wide minimum. Data is valid 20ns before STATUS goes low. Data remains valid for at least 300ns after the next START pulse.

Timing signal (SAMPLE HOLD RESET) allows the user to increase overall sample rate with a T/H. After 380ns (typical), this signal changes state, signaling the converter is done using the analog input. This allows the T/H to begin acquiring the next sample while the 4193 is completing its internal digital encoding.

Power consumption is low typically, I.8W. Only three supplies are required: ±15V and +5V.

The 4193/4195 A/D converters are specified for 0°C to +70°C operation. The -83 versions are fully specified for operation over the -55° TO +125° temperature range and meet the high reliability requirements of MIL-STD-883, Class B. These devices can be ordered screened to Class S. Teledyne Philbrick is qualified to MIL-STD-1772.

# **FEATURES**

- ☐ 12-Bit Resolution

- ☐ 500ns.. Max. Conversion Time

- ☐ Low Power, 1.8W Max.

- □ Tri-State Output Buffers

- ☐ -55°C to +125°C Operation

# **APPLICATIONS**

- ☐ Medical Instrumentation

- ☐ High Speed Data Acquisition

# **ABSOLUTE MAXIMUM RATINGS**

Operating Temperature Range: 4193/5 4193/5-83

Storage Temperature

+15VC Supply (+V<sub>CC</sub>, Pin 9) -15V Supply (-V<sub>CC</sub>, Pin 3)

+5V Supply (+V<sub>dd</sub>, Pins 15, 22, 39)

Digital Inputs Analog Input: 4193

4195

0°C to +70°C

-55°C to +125°C

-65°C to +150°C

-0.5V to +18V

+0.5 to -18V

10.5 10 - 10 4

-0.3 to +7V -0.3V to + $V_{dd}$ +0.3V

-1V to +6V

-3.5V to +3.5V

# SPECIFICATIONS (T<sub>A</sub> = +25°C, Supply Voltages $\pm 15$ V and +5V unless otherwise indicated). (1)

| PARAMETER                                                                                                                                                    | MIN.                                               | TYP.                            | MAX                             | UNITS                         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------|---------------------------------|-------------------------------|--|

| Analog Inputs Input Voltage Range: 4193 4195 Input Impedance                                                                                                 |                                                    | 0 to 5<br>-2.5 to +2.5<br>1K/30 | _<br>_<br>_                     | Volts<br>Volts<br>kΩ/pF       |  |

| Digital Inputs Logic Levels: Logic "1" Logic "0" Loading: Start Convert Input IIH Data Enable Input IIL                                                      | +2.25<br>0<br>—<br>—                               | <br><br>40<br>-200              | +0.8                            | Volts<br>Volts<br>μΑ<br>μΑ    |  |

| Transfer Characteristics (3) Integral Linearity Error: Initial (+25°C) Over Temperature Differential Linearity Error 12-Bit No Missing Codes                 | _<br>_<br>_                                        | ±¼<br>±½<br>±½<br>Guaranteed Ov | ±1<br>±1<br>—<br>er Temperature | LSB<br>LSB<br>—               |  |

| Full Scale Absolute Accuracy Error (4) Initial (+25°C) Over Temperature Unipolar Offset Error (4193) (5)                                                     | =                                                  | ±0.05<br>±0.1%                  | ±0.15<br>±0.3                   | %FSR<br>%FSR                  |  |

| Initial (+25°C) Over Temperature Drift                                                                                                                       | _<br>_<br>_                                        | ±0.05<br>±0.1<br>±10            | ±0.1<br>±0.15<br>—              | %FSR<br>%FSR<br>PPM of FSR/°C |  |

| Bipolar Zero Error (4195) (6) Initial (+25°C) Over Temperature Drift Coin Error (7)                                                                          |                                                    | ±0.05<br>±0.1<br>±10            | ±0.1<br>±0.2<br>—               | %FSR<br>%FSR<br>PPM of FSR/°C |  |

| Gain Error (7): Initial (+25°C) Over Temperature Drift                                                                                                       | _<br>_<br>_                                        | ±0.05<br>±0.1<br>±20            | ±0.1<br>±0.3<br>—               | %<br>%<br>PPM/°C              |  |

| Digital Outputs Output Coding (8): 4193 4195 Output Drive Conshills (8)                                                                                      | Straight Binary Offset Binary 5   —   LS TTL Loads |                                 |                                 |                               |  |

| Output Drive Capability (2)                                                                                                                                  |                                                    | _                               | <del></del>                     | LS TTL Loads                  |  |

| Dynamic Characteristics Conversion Time (9) Start Convert Pulse Width (10) Delay Falling Edge of Start to Status "1" Delay Falling Edge of Start to Previous | <br>50<br>                                         | 450<br>—<br>25                  | .500<br>—                       | nsec<br>nsec<br>nsec          |  |

| Output Data Invalid Delay Falling Edge of Status to Output Data Valid                                                                                        | 200<br>—                                           | 300<br>—                        | 0                               | nsec<br>nsec                  |  |

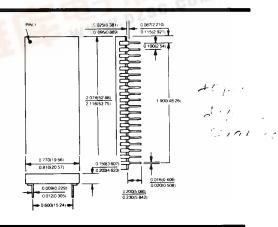

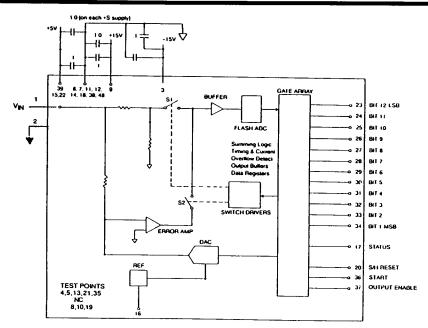

Figure 1. 4193 Pin Connections and Block Diagram

# Circuit Description -

The 4193 circuit uses a two stage subranging technique. First the input is approximated to seven bits. Then the seven bit word is applied to an accurate 12 bit DAC. The output of the DAC and the input are subtracted and amplified to create an error signal which is then digitized to seven bits. Combining the first and second seven bit word results in a 12 bit accurate result. See Figure 1, Pin Connections and Block Diagram.

The circuit uses a <u>flash converter</u>, a 7 bit DAC with >12 bit accuracy, and a digital gate array. Analog switches are used to multiplex the input of the flash converter between the analog input and the error signal, thus saving the cost and power of a second ash converter.

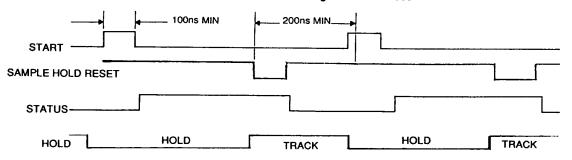

The timing of the ADC is initiated by a single START pulse 50ns wide minimum. See Figure 2, Conversion Timing. STATUS goes high on the

falling edge of START. The conversion is complete when STATUS goes low. SAMPLE HOLD RESET signals the 4193 is done using the analog input on its falling edge. Using this signal to control the timing of a track and hold amplifier improves the conversion rate. While the ADC is completing the conversion, the T/H may begin acquiring the next sample. See the 4193-4860 application for an example.

The analog input signal is encoded to seven bits just after the falling edge of the START pulse. The data is saved in the gate array and transmitted to the DAC.

The output of the DAC is subtracted from the analog input and the difference is amplified. Meanwhile S1 opens and S2 closes. The error signal goes to the Flash ADC.

After the DAC and Error Amp settle, the error signal is encoded to seven bits. The data is sent to the gate array. S2 opens and S1 closes. SAMPLE HOLD RESET goes low signaling that the ADC is done using the analog input.

The data from the second encode is added to the data from the first encode. The result is a twelve bit word precisely scaled to the analog input.

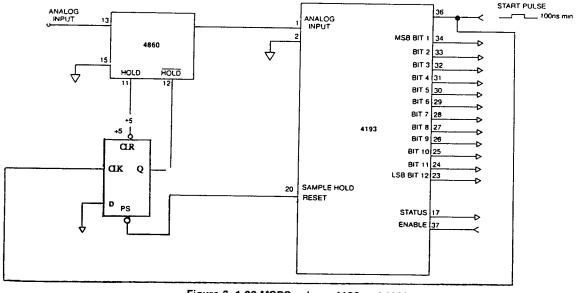

# Using a 4860 with 4193 -

This example shows the interconnections and timing requirements for a 4860 used with the 4193 ADC. See Figure 3, 1.33 MSPS using a 4193 and 4860.

The 4860 is driven from the 4193 through a D type flip-flop. Prior to the start pulse 200ns must be allowed for the 4860 to acquire the input signal. A l00ns (minimum) start pulse occurs which is applied to the 4193 and D flip-flop. Hold goes low after the rising edge of the start pulse. About 100ns later, the start pulse goes low. Then the first conversion of

the two step conversion occurs. Since the conversion begins right after start goes low, time must be allowed for the 4860 and the 4193 to sett' into hold. The 4193 is done with the analog inpuabout 375ns after the conversions begins (negative edge of start). Hold goes high putting the 4860 into track. This allows aquisition time and conversion time to overlap, increasing the system update rate. The combined 4860 and 4193 conversion time can be as low as 750ns with full scale dynamic inputs.

| INPUT VOLTAGE (VOLTS)    |         | OUTPUT CODING    |              |

|--------------------------|---------|------------------|--------------|

| SCALE                    | 4193    | 4195             | DATA         |

| F.S.                     | 5.0000  | 2.5000           | 11111111111  |

| F.S 1 LSB                | 4.9988  | 2.4988           |              |

| 4 F.S. + ½ LSB<br>4 F.S. |         | 1.2506<br>1.2500 | 11000000000  |

| ½ F.S. + ½ LSB           | 2.5006  | 0.0006           | 10000000000  |

| ½ F.S.                   | 2.5000  | 0.0000           |              |

| ½ F.S ½ LSB              | 2.4994  | -0.0006          | 011111111111 |

| ¼ F.S.                   | 1.2500  | -1.2500          |              |

| 4 F.S ½ LSB              | +0.0012 | -1.2506          | 001111111111 |

| 1 LSB                    |         | -2.4988          | 000000000000 |

| 0                        | 0.0000  | -2.5000          | 00000000000  |

Table A. Input Voltage and Output Coding

Figure 3. 1.33 MSPS using a 4193 and 4860

Figure 4. 4193/4860 Timing

Teledyne Philbrick makes no representation that use of its modules in the circuits described herein, or use of other technical information contained herein will not infringe on existing or future patent rights nor do the descriptions contained herein imply the granting of licenses to make, use or sell equipment constructed in accordance therewith. Device specifications as contained on this data sheet are current as of the publication date shown. Teledynce Philbrick maintains the right to make changes in the circuitry and/or specifications contained on this data sheet at any time, without notice and assumes no responsibility for the use of any circuits described herein.

Printed in U.S.A. 2/88 ZK Rev #1

# TELEDYNE PHILBRICK

# **ERRATA SHEET**

# 4193/95 500NS MAX. 12-BIT A/D CONVERTER

REV #1 2/88 2K (CODE ON DATA SHEET)

# **PIN DESIGNATIONS:**

# To read:

PIN 6 ANALOG GROUND

PIN 7 ANALOG GROUND

PIN 11 DIGITAL GROUND

PIN 12 ANALOG GROUND

PIN 19 TEST POINT (N/C)

PIN 40 DIGITAL GROUND

# **FEATURES:**

To Read: Low Power, 1.72 W - TYPICAL --- not 1.8W Max.

TELEDYNE PHILBRICK 40 Allied Drive, Dedham, MA 02026 Tel: (617) 329-1600 Tix: 212711 Fax: 617-326-6313

| PARAMETER                                                                                                   | MIN.                                                    | TYP.                                                                    | MAX                                                                 | UNITS                                                |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------|

| Reference Output Internal Reference: Voltage Accuracy Drift External Current                                | _<br>_<br>_                                             | +5.000<br>±2<br>±10<br>5                                                | _<br>_<br>_<br>_                                                    | Volts<br>%<br>PPM/°C<br>μA                           |

| Power Supply Requirements  Power Supply Range: +15V Supply                                                  | +14.55<br>-14.55<br>+4.75<br>—<br>—<br>—<br>—<br>—<br>— | +15<br>-15<br>+5<br>±0.02<br>±0.02<br>±0.002<br>20<br>38<br>170<br>1.72 | +15.45<br>-15.45<br>+5.25<br>—<br>—<br>—<br>26<br>48<br>210<br>2.16 | Volts Volts Volts Volts %FSR/%Vs %FSR/%Vs mA mA mA W |

| Thermal Characteristics Thermal Impedance: Case to Ambient, CA Junction to Case, JC Junction to Ambient, JA |                                                         | 17.2<br>7.8<br>25                                                       | _<br>_<br>_                                                         | °C/W<br>°C/W<br>°C/W                                 |

#### NOTES

- (1) Unless otherwise indicated, listed specifications apply for all 4193 and 4195 models. Drift specifications apply over each device's specified temperature range.

- One LS TTL load is defined as sinking 20µA with a logic "1" applied and sourcing 0.4mA with a logic "0" applied.

FSR = Full Scale Range. For both the 4193 and 4195, FSR = 5 volts. For a 12-bit converter, 1 LSB = 0.024% FSR

- (4) Full Scale Accuracy Error is defined as the difference between the actual and the ideal input voltage at which the 1111 1111 1110 to 1111 1111 1111 digital-output transition occurs. It includes offset, gain, linearity and noise errors and encompasses the drifts of those errors when specified over temperature.

- (5) Unipolar offset error is defined for the 4193 as the difference between the actual and ideal input voltage at which the 0000 0000 0000 to 0000 0000 0001 transition occurs.

(6) Bipolar zero error is defined as the difference between the actual and the ideal input voltage at which the 0111 1111 1111 to 1000 0000 0000 transition occurs for the

- 8) See Output Coding table for details.

- (9) Conversion time is defined as the width of the converter's Status output pulse. See Timing Diagram.

- (10) Actual conversion process is initiated on the falling edge of the Start Convert Signal. See Timing Diagram.

# Applying the 4193 -

The 4193 is designed for digitizing fast changing input signals. Combined with a track/hold (T/H), such as the 4860, it will sample dynamic signals at better than 1.3 MSPS (Mega Samples per Second). This assures digitized data with low harmonic distortion and good signal to noise ratio.

# Grounding and Bypassing.

Careful layout is a must for all high speed circuits and the 4193 is no exception. A ground plane is highly recommended. It will improve the ADC's performance and also the associated drive circuitry, amplifier or track and hold. The  $\pm 15$ V supplies should be bypassed with 1.0 $\mu$ f tantalum capacitors in parallel with .1 $\mu$ f ceramic capacitors. The +5V supply should be bypassed with a 1.0 $\mu$ f tantalum capacitor in parallel with a .1 $\mu$ f ceramic on each +5V pin (15, 22, 39). All grounds should be connected together to the ground plane. All three power supplies are used as analog supplies. In addition, the +5V supply is a digital supply.

### Input Drive Requirements

The 4193 is easy to drive. The input resistance is nominally  $1.0 K\Omega$ . Unlike successive approximation converters very little noise is generated at the analog input. However, best performance is assured by using a wide bandwidth low output impedance driver.

#### **Output Coding** .

The 4193 has straight binary and the 4195 has offset binary coding. See Table A, Output Coding, for details.

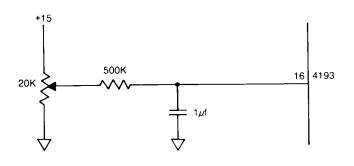

#### Gain Adjust -

Pin 16 has a two way function. The internal reference may be used by leaving this terminal open or adding a small  $(.1\mu f)$  capacitor to ground. An external reference may be used also. Connect a +5.000V reference to this pin. Gain may also be adjusted  $\pm .5\%$  using the circuit below.