FUJITSU SEMICONDUCTOR DATA SHEET

### DS07-13701-7E

邦,专业PCB打样工厂,24小时加急出货

# 16-bit Proprietary Microcontroller

**CMOS**

# F<sup>2</sup>MC-16LX MB90570 Series

# MB90573/574/574C/F574/F574A/V570/V570A

### DESCRIPTION

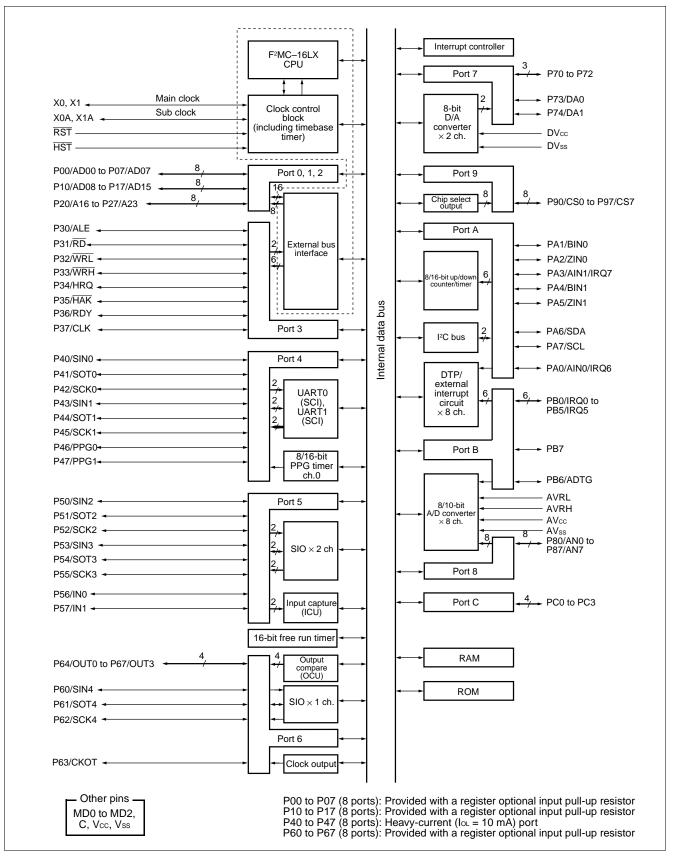

The MB90570 series is a general-purpose 16-bit microcontroller developed and designed by Fujitsu for process control applications in consumer products that require high-speed real time processing. It contains an I<sup>2</sup>C<sup>\*2</sup> bus interface that allows inter-equipment communication to be implemented readily. This product is well adapted to car audio equipment, VTR systems, and other equipment and systems.

The instruction set of F<sup>2</sup>MC-16LX CPU core inherits AT architecture of F<sup>2</sup>MC<sup>\*1</sup> family with additional instruction sets for high-level languages, extended addressing mode, enhanced multiplication/division instructions, and enhanced bit manipulation instructions. The microcontroller has a 32-bit accumulator for processing long word data.

The MB90570 series has peripheral resources of an 8/10-bit A/D converter, an 8-bit D/A converter, UART (SCI), an extended I/O serial interface, an 8/16-bit up/down counter/timer, an 8/16-bit PPG timer, I/O timer (a 16-bit free run timer, an input capture (ICU), an output compare (OCU)).

- \*1: F<sup>2</sup>MC stands for FUJITSU Flexible Microcontroller.

- \*2: Purchase of Fujitsu I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

### ■ FEATURES

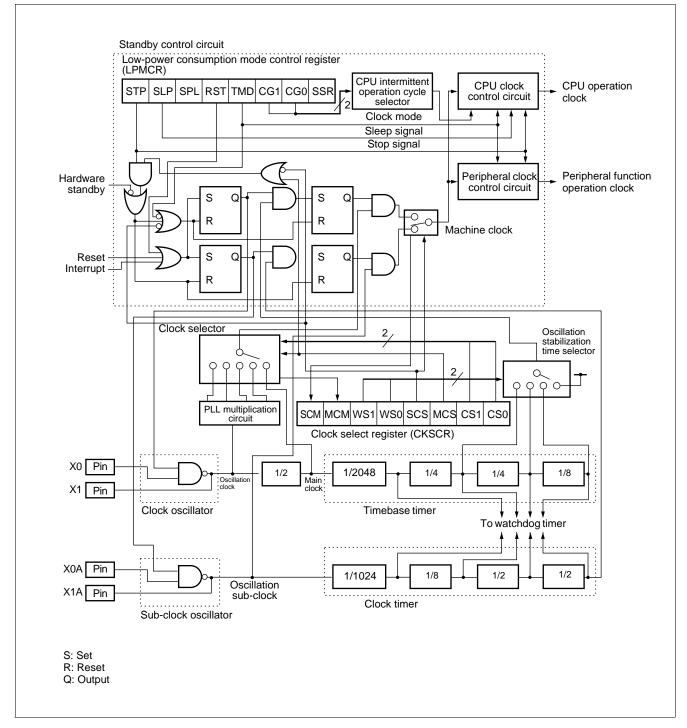

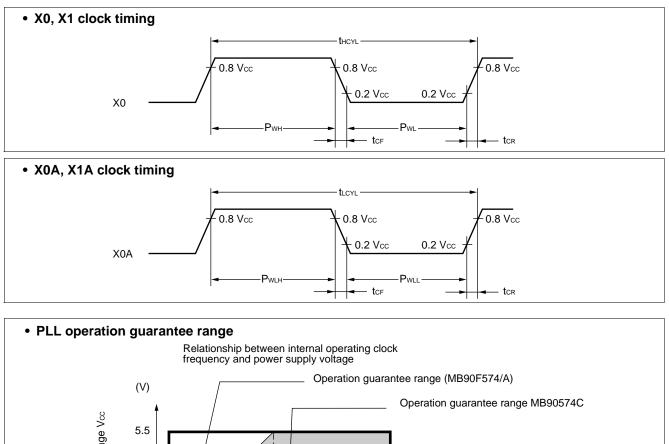

Clock

Embedded PLL clock multiplication circuit

Operating clock (PLL clock) can be selected from 1/2 to 4× oscillation (at oscillation of 4 MHz, 4 MHz to 16 MHz).

Minimum instruction execution time: 62.5 ns (at oscillation of 4 MHz, 4× PLL clock, operation at Vcc of 5.0 V)

Maximum memory space

16 Mbytes

- Instruction set optimized for controller applications

Rich data types (bit, byte, word, long word)

Rich addressing mode (23 types)

Enhanced signed multiplication/division instruction and RETI instruction functions

Enhanced precision calculation realized by the 32-bit accumulator

- Instruction set designed for high level language (C) and multi-task operations Adoption of system stack pointer Enhanced pointer indirect instructions Barrel shift instructions

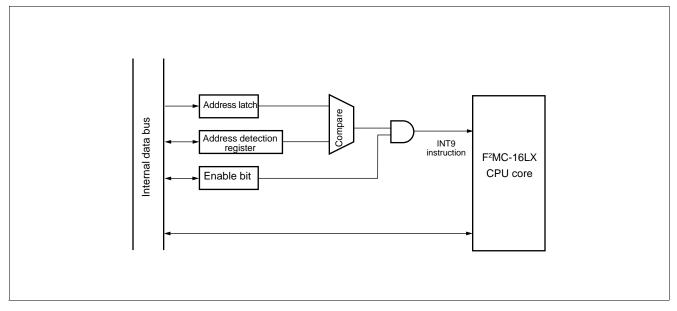

- Program patch function (for two address pointers)

- Enhanced execution speed 4-byte instruction queue

- Enhanced interrupt function 8 levels, 34 factors

- Automatic data transmission function independent of CPU operation Extended intelligent I/O service function (EI<sup>2</sup>OS): Up to 16 channels

- Embedded ROM size and types Mask ROM: 128 kbytes/256 kbytes Flash ROM: 256 kbytes Embedded RAM size: 6 kbytes/10 kbytes (mask ROM) 10 kbytes (flash memory)

- 10 kbytes (evaluation device)

- Low-power consumption (standby) mode

Sleep mode (mode in which CPU operating clock is stopped)

Stop mode (mode in which oscillation is stopped)

CPU intermittent operation mode

Hardware standby mode

- Process

- CMOS technology

- I/O port

General-purpose I/O ports (CMOS): 63 ports General-purpose I/O ports (with pull-up resistors): 24 ports General-purpose I/O ports (open-drain): 10 ports Total: 97 ports

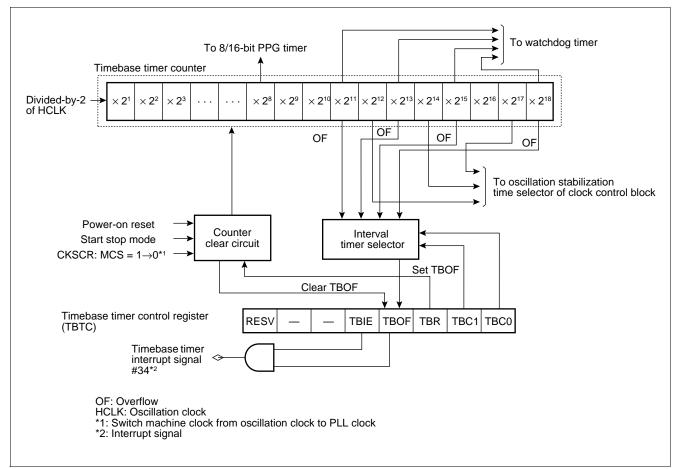

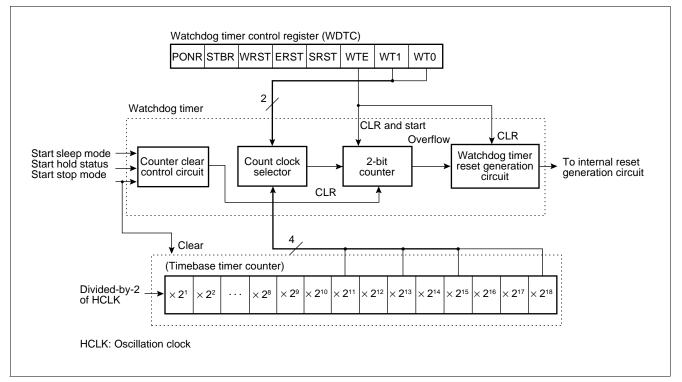

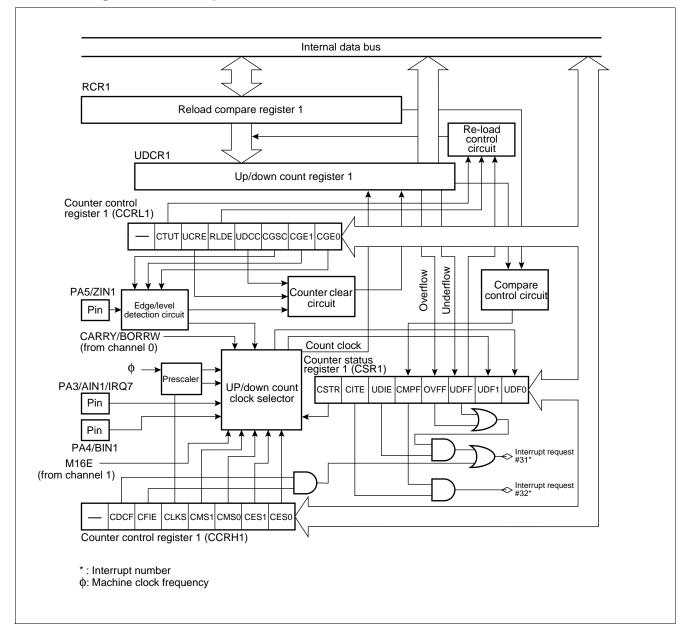

| <ul> <li>(Continued)</li> <li>Timer</li> <li>Timebase timer/watchdog timer: 1 channel</li> <li>8/16-bit PPG timer: 8-bit × 2 channels or 16-bit × 1 channel</li> <li>8/16-bit up/down counter/timer: 1 channel (8-bit × 2 channels)</li> </ul> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

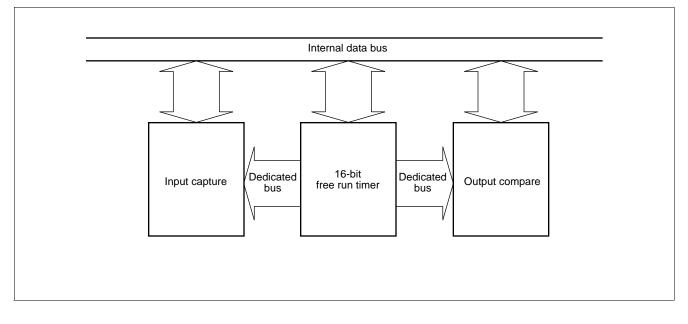

| <ul> <li>16-bit I/O timer</li> </ul>                                                                                                                                                                                                           |

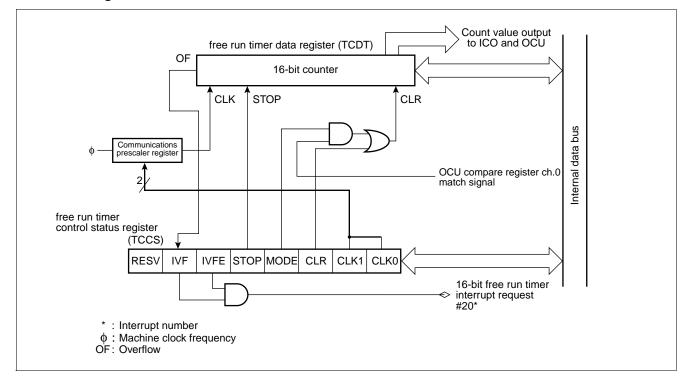

| 16-bit free run timer: 1 channel                                                                                                                                                                                                               |

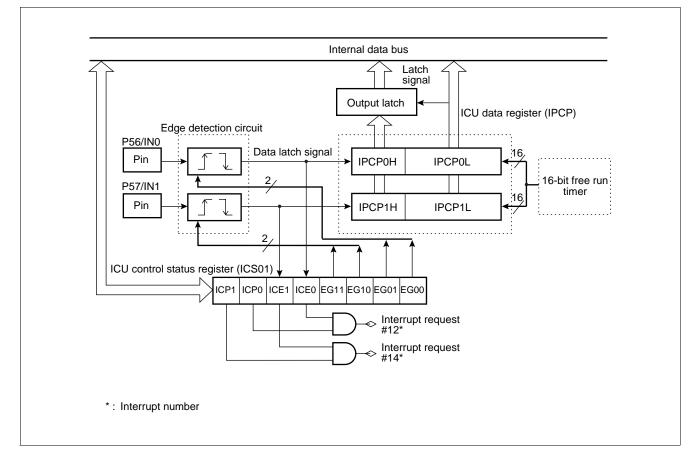

| Input capture (ICU): Generates an interrupt request by latching a 16-bit free run timer counter value upon detection of an edge input to the pin.                                                                                              |

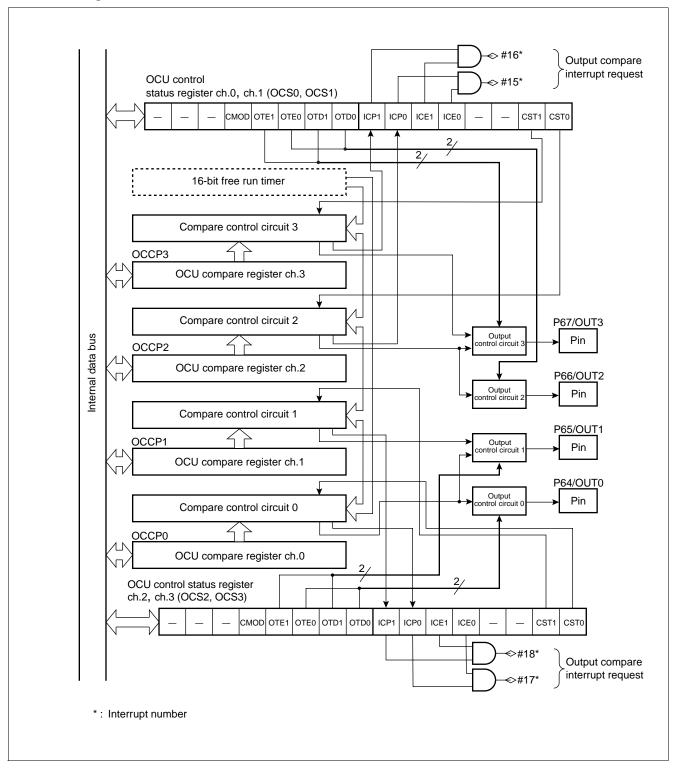

| Output compare (OCU): Generates an interrupt request and reverse the output level upon detection of a match between the 16-bit free run timer counter value and the compare setting value.                                                     |

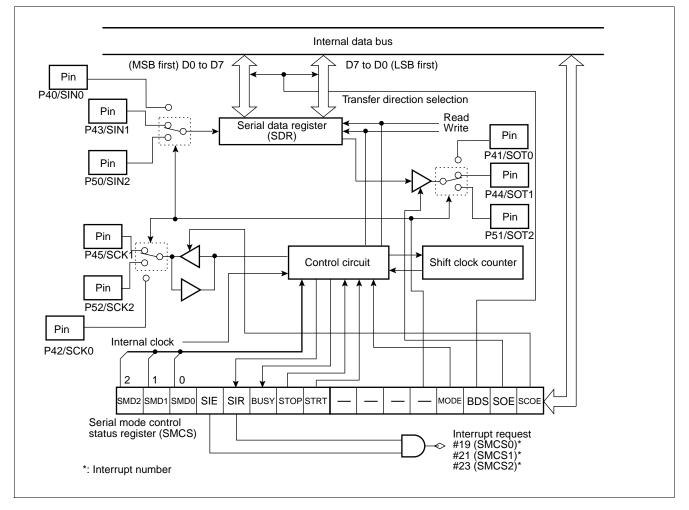

| Extended I/O serial interface: 3 channels                                                                                                                                                                                                      |

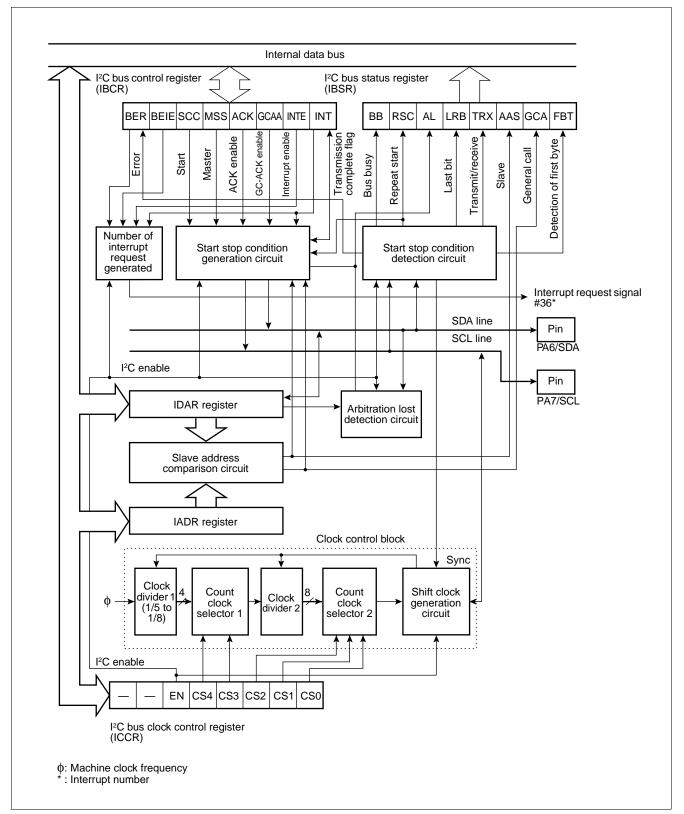

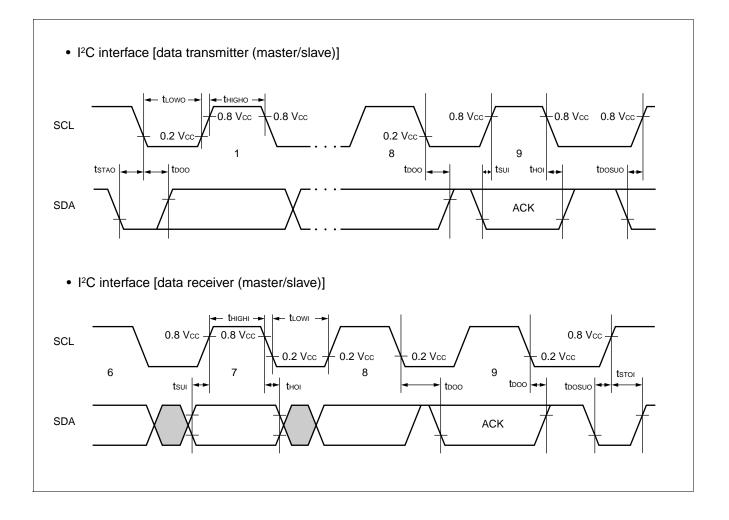

| <ul> <li>I<sup>2</sup>C interface (1 channel)</li> </ul>                                                                                                                                                                                       |

| Serial I/O port for supporting Inter IC BUS                                                                                                                                                                                                    |

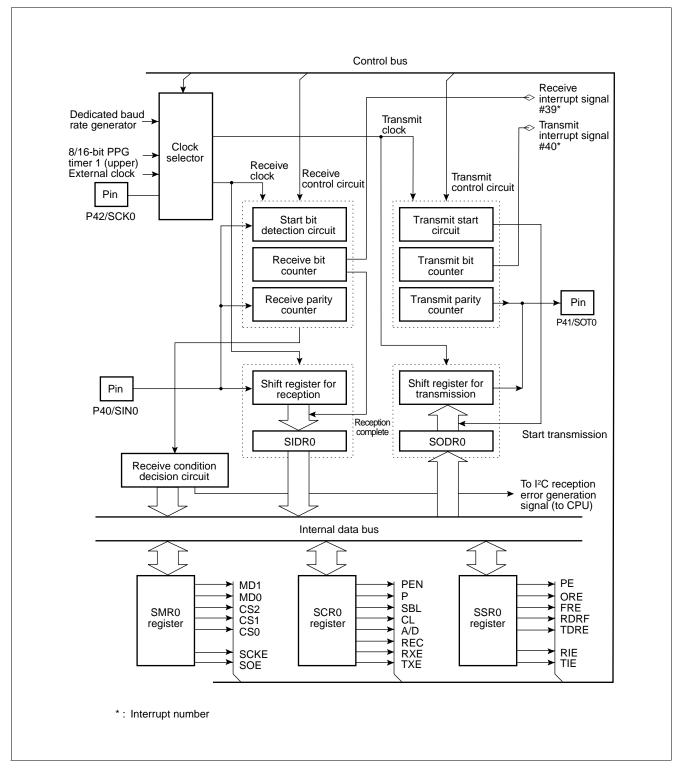

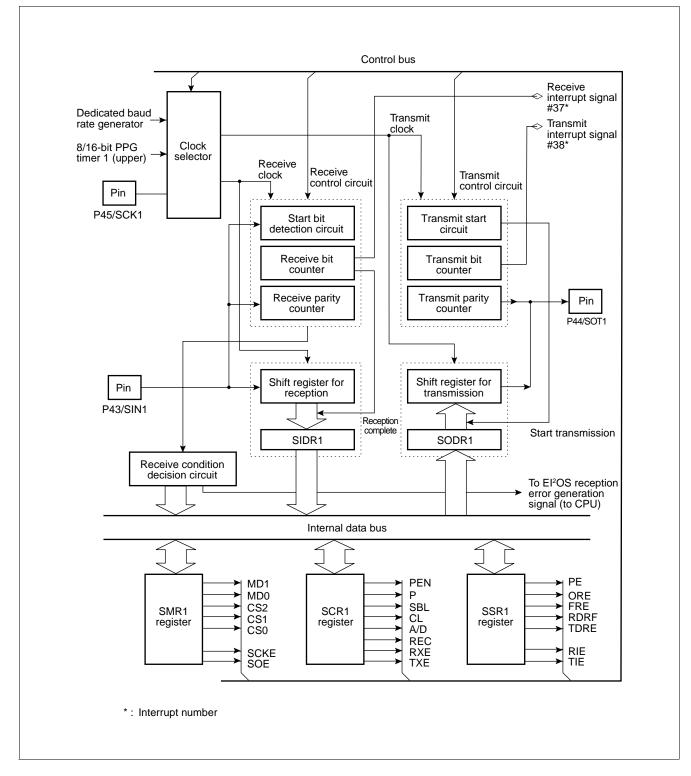

| • UARTO (SCI), UART1 (SCI)                                                                                                                                                                                                                     |

| With full-duplex double buffer                                                                                                                                                                                                                 |

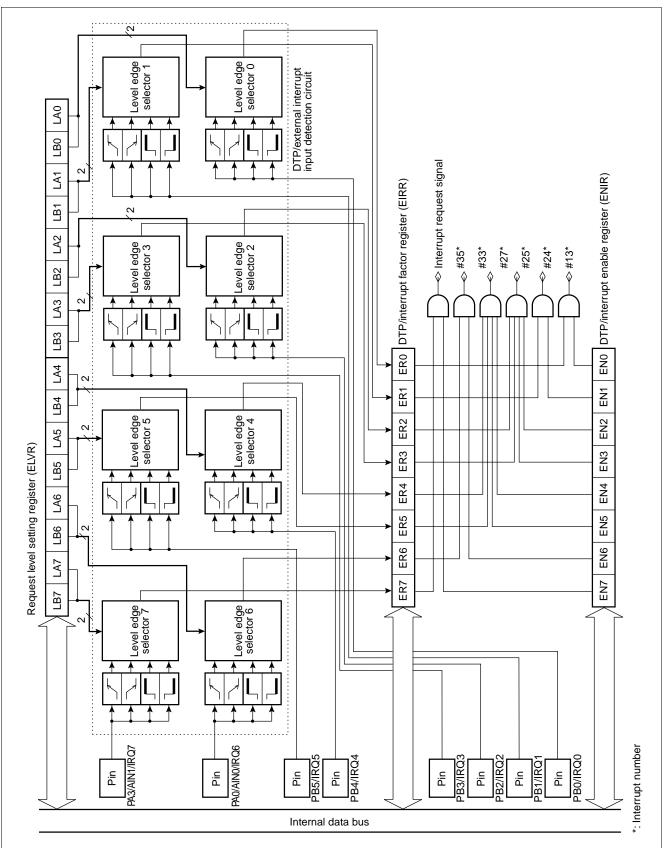

| <ul><li>Clock asynchronized or clock synchronized transmission can be selectively used.</li><li>DTP/external interrupt circuit (8 channels)</li></ul>                                                                                          |

| A module for starting extended intelligent I/O service (EI <sup>2</sup> OS) and generating an external interrupt triggered by an external input.                                                                                               |

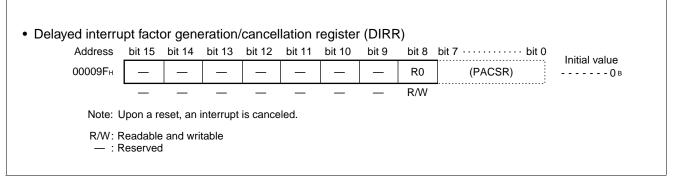

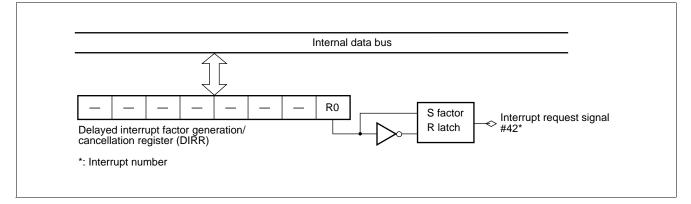

| Delayed interrupt generation module                                                                                                                                                                                                            |

| Generates an interrupt request for switching tasks.                                                                                                                                                                                            |

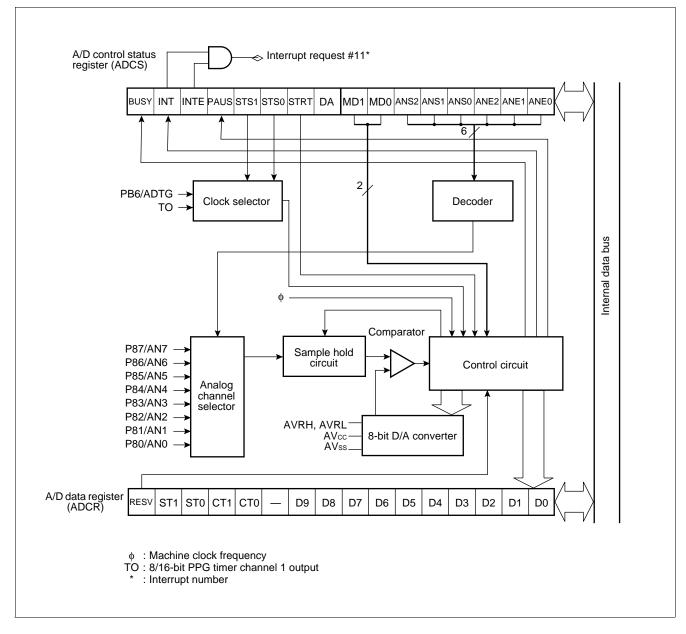

| <ul> <li>8/10-bit A/D converter (8 channels)</li> </ul>                                                                                                                                                                                        |

| 8/10-bit resolution                                                                                                                                                                                                                            |

| Starting by an external trigger input.                                                                                                                                                                                                         |

| Conversion time: 26.3 µs                                                                                                                                                                                                                       |

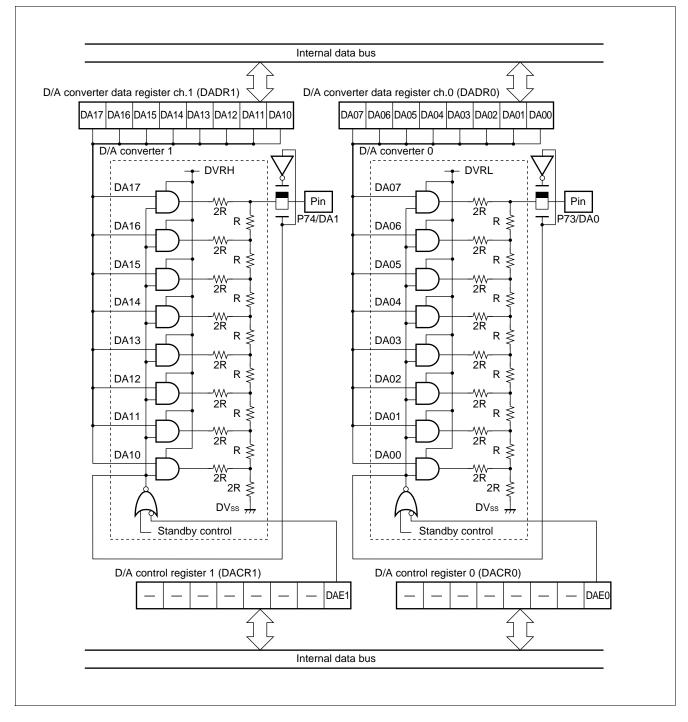

| <ul> <li>8-bit D/A converter (based on the R-2R system)</li> </ul>                                                                                                                                                                             |

| 8-bit resolution: 2 channels (independent)                                                                                                                                                                                                     |

| Setup time: 12.5 μs                                                                                                                                                                                                                            |

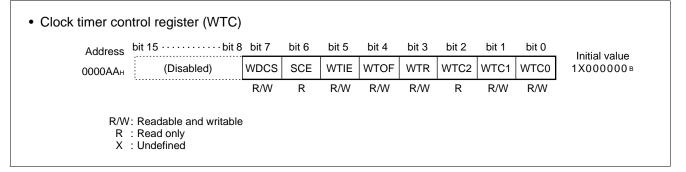

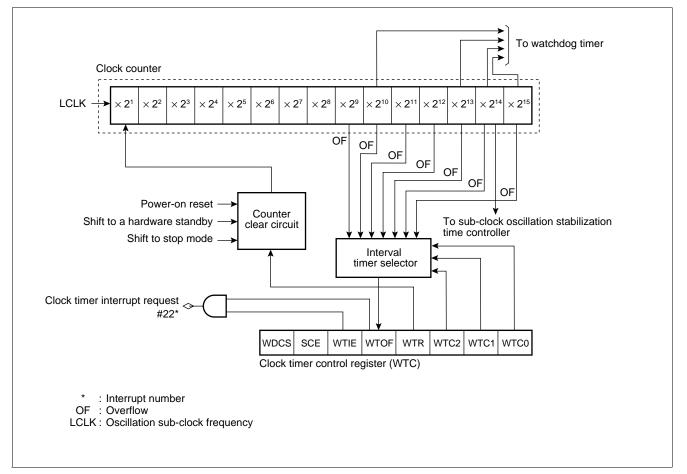

- Clock timer: 1 channel

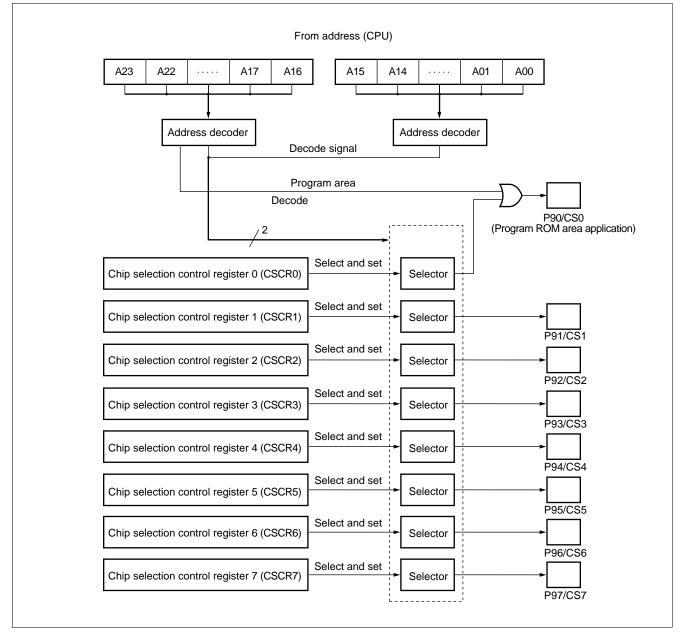

- Chip select output (8 channels) An active level can be set.

- Clock output function

### ■ PRODUCT LINEUP

|                         | Part number                | MB90573                                                                                                                                                                                                                                                                                                                                                                        | MB90574/C                                     | MB90F574/A                                                                           | MB90V570/A         |  |  |  |  |

|-------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------|--------------------|--|--|--|--|

| ltem                    |                            |                                                                                                                                                                                                                                                                                                                                                                                |                                               |                                                                                      |                    |  |  |  |  |

| Classification          |                            | Mask ROM                                                                                                                                                                                                                                                                                                                                                                       | A products                                    | Flash ROM products                                                                   | Evaluation product |  |  |  |  |

| ROM size                |                            | 128 kbytes                                                                                                                                                                                                                                                                                                                                                                     | 256                                           | kbytes                                                                               | None               |  |  |  |  |

| RAM size                |                            | 6 kbytes                                                                                                                                                                                                                                                                                                                                                                       |                                               | 10 kbytes                                                                            |                    |  |  |  |  |

| CPU function            | s                          | The number of instructions: 340<br>Instruction bit length: 8 bits, 16 bits<br>Instruction length: 1 byte to 7 bytes<br>Data bit length: 1 bit, 8 bits, 16 bits<br>Minimum execution time: 62.5 ns (at machine clock of 16 MHz)<br>Interrupt processing time: 1.5 µs (at machine clock of 16 MHz, minimum value)                                                                |                                               |                                                                                      |                    |  |  |  |  |

| Ports                   |                            | Gen                                                                                                                                                                                                                                                                                                                                                                            | eral-purpose I/O port<br>al-purpose I/O ports | orts (CMOS output): 6<br>s (with pull-up resistor<br>(N-ch open-drain outp<br>al: 97 | ): 24              |  |  |  |  |

| UART0 (SCI),            | , UART1 (SCI)              | Clock synchronized transmission (62.5 kbps to 1 Mbps)<br>Clock asynchronized transmission (1202 bps to 9615 bps)<br>Transmission can be performed by bi-directional serial transmission or by<br>master/slave connection.                                                                                                                                                      |                                               |                                                                                      |                    |  |  |  |  |

| 8/10-bit A/D c          | converter                  | Resolution: 8/10-bit<br>Number of inputs: 8<br>One-shot conversion mode (converts selected channel only once)<br>Scan conversion mode (converts two or more successive channels and can<br>program up to 8 channels.)<br>Continuous conversion mode (converts selected channel continuously)<br>Stop conversion mode (converts selected channel and stop operation repeatedly) |                                               |                                                                                      |                    |  |  |  |  |

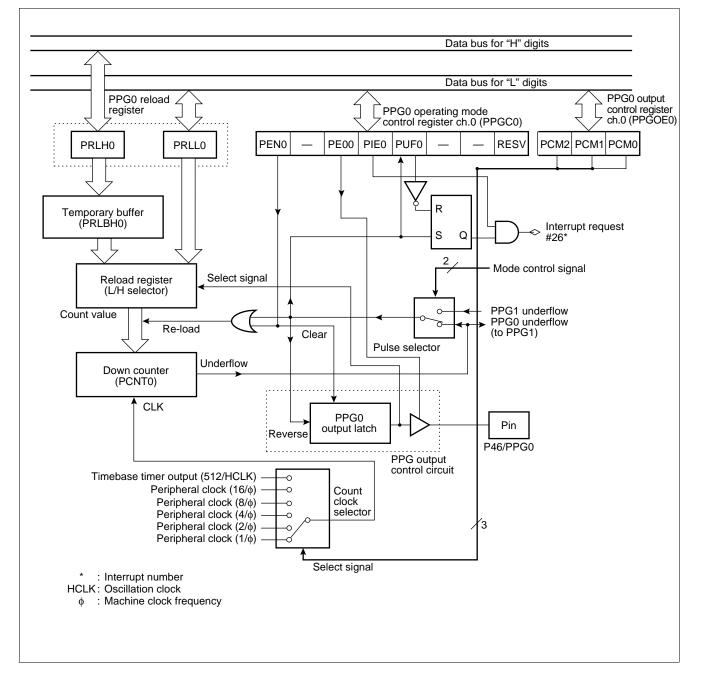

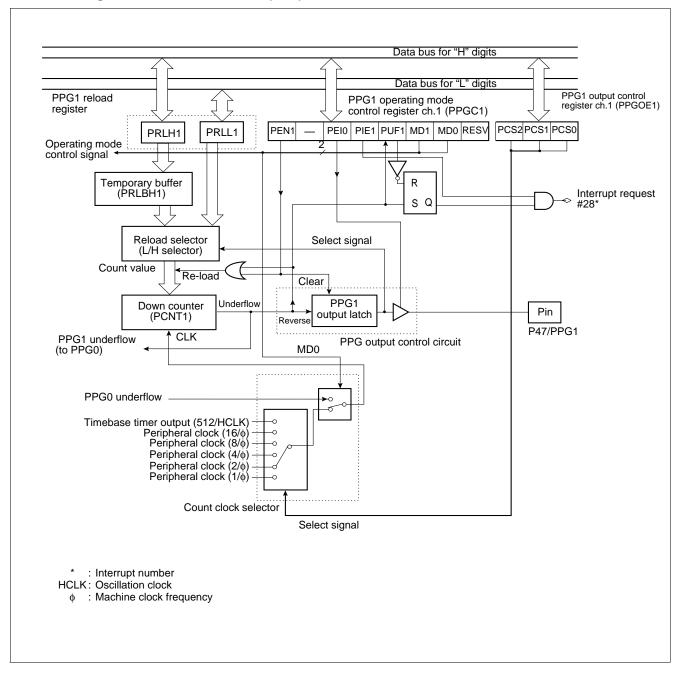

| 8/16-bit PPG            | timer                      | Number of channels: 1 (or 8-bit $\times$ 2 channels)<br>PPG operation of 8-bit or 16-bit<br>A pulse wave of given intervals and given duty ratios can be output.<br>Pulse interval: 62.5 ns to 1 $\mu$ s (at oscillation of 4 MHz, machine clock of 16 MHz)                                                                                                                    |                                               |                                                                                      |                    |  |  |  |  |

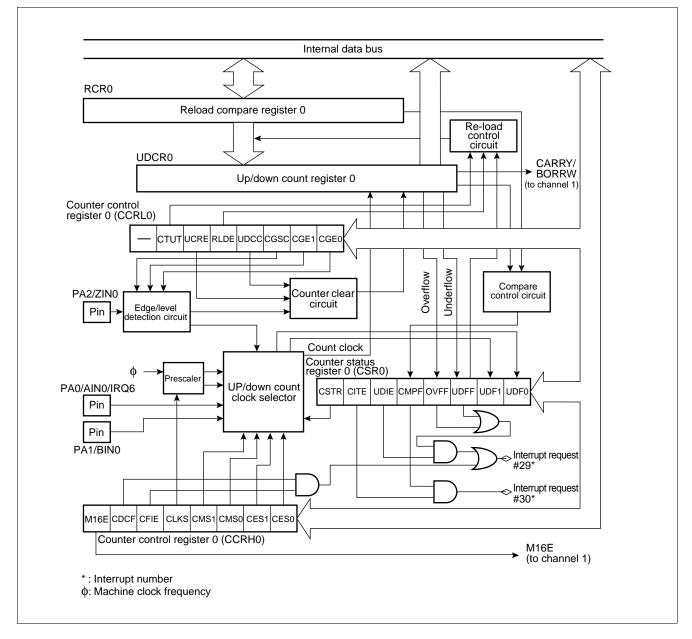

| 8/16-bit up/do<br>timer | own counter/               | Number of channels: 1 (or 8-bit × 2 channels)<br>Event input: 6 channels<br>8-bit up/down counter/timer used: 2 channels<br>8-bit re-load/compare function supported: 1 channel                                                                                                                                                                                                |                                               |                                                                                      |                    |  |  |  |  |

|                         | 16-bit<br>free run timer   | Number of channel: 1<br>Overflow interrupts                                                                                                                                                                                                                                                                                                                                    |                                               |                                                                                      |                    |  |  |  |  |

| 16-bit<br>I/O timer     | Output<br>compare<br>(OCU) | Pin i                                                                                                                                                                                                                                                                                                                                                                          | ister                                         |                                                                                      |                    |  |  |  |  |

|                         | Input capture<br>(ICU)     | Rewriting a reg                                                                                                                                                                                                                                                                                                                                                                |                                               | channels: 2<br>n input (rising, falling,                                             | or both edges)     |  |  |  |  |

#### (Continued)

| Part number<br>Item                     | MB90573                                                                                                                                                                                                     | MB90574/C | MB90F574/A | MB90V570/A |  |  |  |  |  |  |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|------------|--|--|--|--|--|--|--|

| DTP/external interrupt circuit          | Number of inputs: 8<br>Started by a rising edge, a falling edge, an "H" level input, or an "L" level inpu<br>External interrupt circuit or extended intelligent I/O service (EI <sup>2</sup> OS) can be use |           |            |            |  |  |  |  |  |  |  |

| Delayed interrupt generation module     | An interrupt generation module for switching tasks used in real time operating systems.                                                                                                                     |           |            |            |  |  |  |  |  |  |  |

| Extended I/O serial interface           | Clock synchronized transmission (3125 bps to 1 Mbps)<br>LSB first/MSB first                                                                                                                                 |           |            |            |  |  |  |  |  |  |  |

| I <sup>2</sup> C interface              | Serial I/O port for supporting Inter IC BUS                                                                                                                                                                 |           |            |            |  |  |  |  |  |  |  |

| Timebase timer                          | 18-bit counter<br>Interrupt interval: 1.024 ms, 4.096 ms, 16.384 ms, 131.072 ms<br>(at oscillation of 4 MHz)                                                                                                |           |            |            |  |  |  |  |  |  |  |

| 8-bit D/A converter                     | 8-bit resolution<br>Number of channels: 2 channels<br>Based on the R-2R system                                                                                                                              |           |            |            |  |  |  |  |  |  |  |

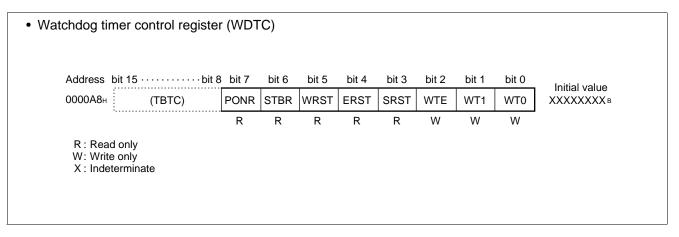

| Watchdog timer                          | Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms<br>(at oscillation of 4 MHz, minimum value)                                                                                               |           |            |            |  |  |  |  |  |  |  |

| Low-power consumption<br>(standby) mode | Sleep/stop/CPU intermittent operation/clock timer/hardware standby                                                                                                                                          |           |            |            |  |  |  |  |  |  |  |

| Process                                 |                                                                                                                                                                                                             | CM        | IOS        |            |  |  |  |  |  |  |  |

| Power supply voltage for operation*     | 4.5 V to 5.5 V                                                                                                                                                                                              |           |            |            |  |  |  |  |  |  |  |

\* : Varies with conditions such as the operating frequency. (See section "■ Electrical Characteristics.") Assurance for the MB90V570/A is given only for operation with a tool at a power voltage of 4.5 V to 5.5 V, an operating temperature of 0 to +25°C, and an operating frequency of 1 MHz to 16 MHz.

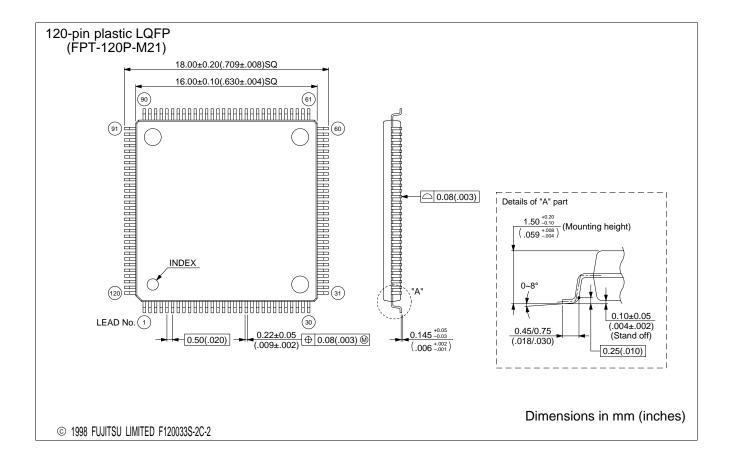

#### ■ PACKAGE AND CORRESPONDING PRODUCTS

| Package      | MB90573 | MB90574 | MB90F574/A | MB90574C |

|--------------|---------|---------|------------|----------|

| FPT-120P-M05 | 0       | 0       | 0          | ×        |

| FPT-120P-M13 | 0       | 0       | 0          | 0        |

| FPT-120P-M21 | ×       | ×       | 0          | 0        |

$\odot$  : Available  $\times:$  Not available

Note: For more information about each package, see section "■ Package Dimensions."

#### DIFFERENCES AMONG PRODUCTS

#### **Memory Size**

In evaluation with an evaluation product, note the difference between the evaluation product and the product actually used. The following items must be taken into consideration.

- The MB90V570/A does not have an internal ROM, however, operations equivalent to chips with an internal ROM can be evaluated by using a dedicated development tool, enabling selection of ROM size by settings of the development tool.

- In the MB90V570/A, images from FF4000H to FFFFFFH are mapped to bank 00, and FE0000H to FF3FFFH to mapped to bank FE and FF only. (This setting can be changed by configuring the development tool.)

- In the MB90F574/574/573/F574A/574C, images from FF4000 $_{\rm H}$  to FFFFFH are mapped to bank 00, and FF0000 $_{\rm H}$  to FF3FFFH to bank FF only.

- The products designated with /A or /C are different from those without /A or /C in that they are DTP/externallyinterrupted types which return from standby mode at the ch.0 to ch.1 edge request.

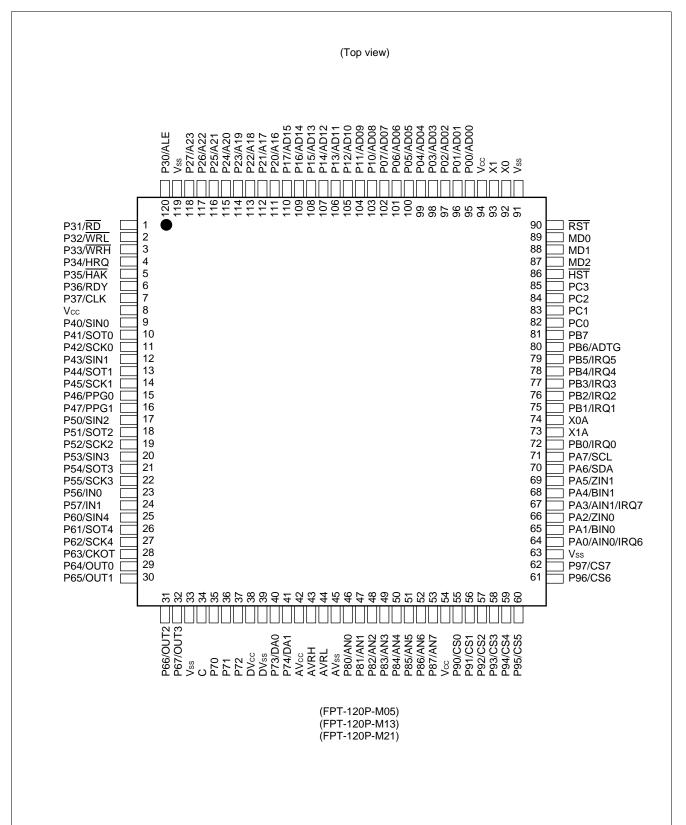

#### PIN ASSIGNMENT

### ■ PIN DESCRIPTION

| Pin no.                   |              |              |                                                                                                                                                                                                    |

|---------------------------|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP-120 *1<br>QFP-120 *2 | Pin name     | Circuit type | Function                                                                                                                                                                                           |

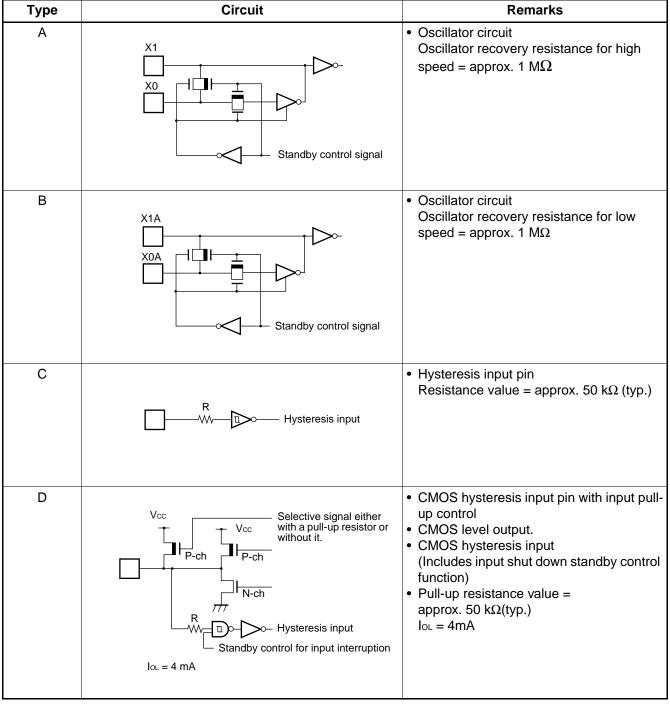

| 92,93                     | X0,X1        | А            | High speed oscillator input pins                                                                                                                                                                   |

| 74,73                     | X0A,X1A      | В            | Low speed oscillator input pins                                                                                                                                                                    |

| 89 to 87                  | MD0 to MD2   | С            | These are input pins used to designate the operating mode. They should be connected directly to Vcc or Vss.                                                                                        |

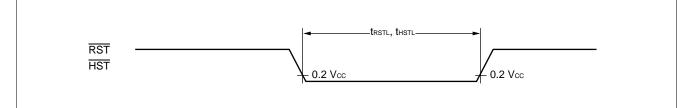

| 90                        | RST          | С            | Reset input pin                                                                                                                                                                                    |

| 86                        | HST          | С            | Hardware standby input pin                                                                                                                                                                         |

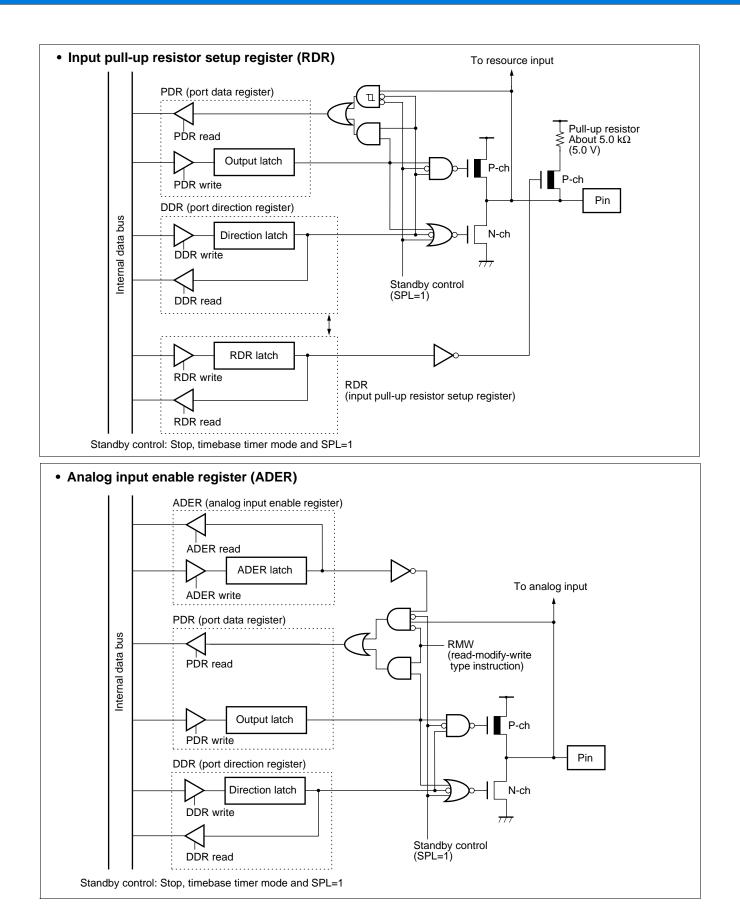

| 95 to 102                 | P00 to P07   | D            | In single chip mode, these are general purpose I/O pins. When set for input, they can be set by the pull-up resistance setting register (RDR0). When set for output, this setting will be invalid. |

|                           | AD00 to AD07 |              | In external bus mode, these pins function as address low output/data low I/O pins.                                                                                                                 |

| 103 to 110                | P10 to P17   | D            | In single chip mode, these are general purpose I/O pins. When set for input, they can be set by the pull-up resistance setting register (RDR1). When set for output, the setting will be invalid.  |

|                           | AD08 to AD15 |              | In external bus mode, these pins function as address middle output/data high I/O pins.                                                                                                             |

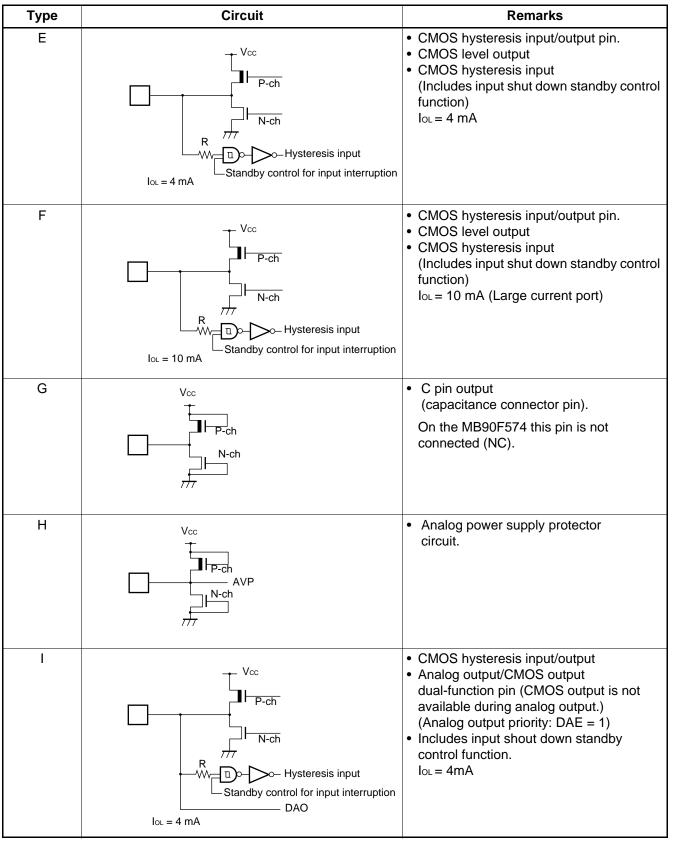

| 111 to 118                | P20 to P27   | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                            |

|                           | A16 to A23   |              | In external bus mode, these pins function as address high output pins.                                                                                                                             |

| 120                       | P30          | Е            | In single chip mode this is a general-purpose I/O port.                                                                                                                                            |

|                           | ALE          |              | In external bus mode, this pin functions as the address latch enable signal output pin.                                                                                                            |

| 1                         | P31          | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                            |

|                           | RD           |              | In external bus mode, this pin functions as the read strobe signal output pin.                                                                                                                     |

| 2                         | P32          | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                            |

|                           | WRL          |              | In external bus mode, this pin functions as the data bus lower 8-bit write strobe signal output pin.                                                                                               |

| 3                         | P33          | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                            |

|                           | WRH          |              | In external bus mode, this pin functions as the data bus upper 8-bit write strobe signal output pin.                                                                                               |

| 4                         | P34          | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                            |

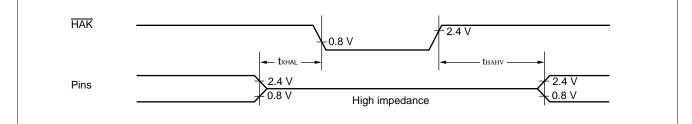

|                           | HRQ          |              | In external bus mode, this pin functions as the hold request signal input pin.                                                                                                                     |

| 5                         | P35          | Е            | In single chip mode this is a general-purpose I/O port.                                                                                                                                            |

|                           | HAK          |              | In external bus mode, this pin functions as the hold acknowledge signal output pin.                                                                                                                |

| 6                         | P36          | Е            | In single chip mode this is a general-purpose I/O port.                                                                                                                                            |

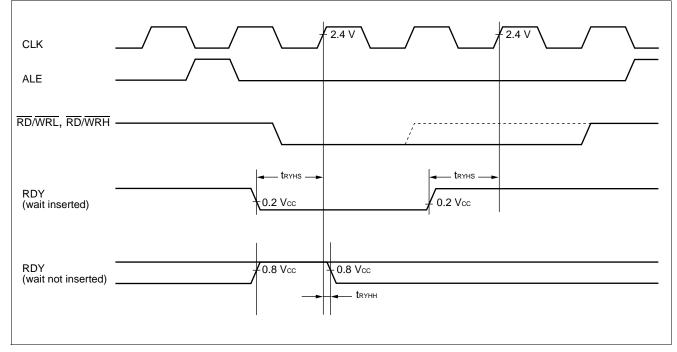

|                           | RDY          |              | In external bus mode, this pin functions as the ready signal input pin.                                                                                                                            |

| Pin no.                   |           |              |                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|---------------------------|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| LQFP-120 *1<br>QFP-120 *2 | Pin name  | Circuit type | Function                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 7                         | P37       | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                                                                                                                                |  |  |  |  |  |

|                           | CLK       |              | In external bus mode, this pin functions as the clock (CLK) signal output pin.                                                                                                                                                                                                                         |  |  |  |  |  |

| 9                         | P40       | F            | In single chip mode this is a general-purpose I/O port. It can be set to open drain by the ODR4 register.                                                                                                                                                                                              |  |  |  |  |  |

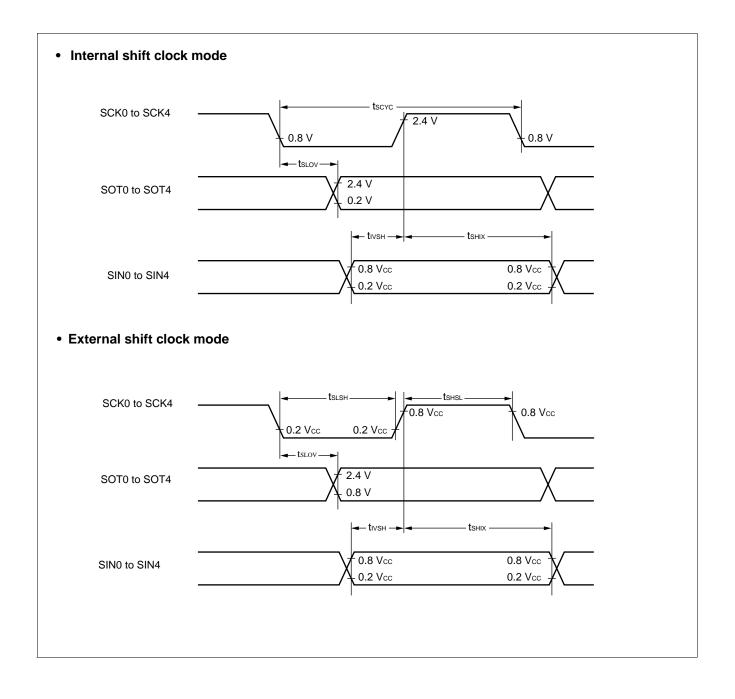

|                           | SINO      | -            | This is also the UART ch.0 serial data input pin. While UART ch.0 is in input operation, this input signal is in continuous use, and therefore the output function should only be used when needed. If shared by output from other functions, this pin should be output disabled during SIN operation. |  |  |  |  |  |

| 10                        | P41       | F            | In single chip mode this is a general-purpose I/O port. It can be set to oper drain by the ODR4 register.                                                                                                                                                                                              |  |  |  |  |  |

|                           | SOT0      |              | This is also the UART ch.0 serial data output pin. This function is valid when UART ch.0 is enabled for data output.                                                                                                                                                                                   |  |  |  |  |  |

| 11                        | P42       | F            | In single chip mode this is a general-purpose I/O port. It can be set to oper drain by the ODR4 register.                                                                                                                                                                                              |  |  |  |  |  |

|                           | SCK0      |              | This is also the UART ch.0 serial clock I/O pin. This function is valid wher UART ch.0 is enabled for clock output.                                                                                                                                                                                    |  |  |  |  |  |

| 12                        | P43       | F            | In single chip mode this is a general-purpose I/O port. It can be set to open-drain by the ODR4 register.                                                                                                                                                                                              |  |  |  |  |  |

|                           | SIN1      |              | This is also the UART ch.1 serial data input pin. While UART ch.1 is in input operation, this input signal is in continuous use, and therefore the output function should only be used when needed. If shared by output from other functions, this pin should be output disabled during SIN operation. |  |  |  |  |  |

| 13                        | P44       | F            | In single chip mode this is a general-purpose I/O port. It can be set to opendrain by the ODR4 register.                                                                                                                                                                                               |  |  |  |  |  |

|                           | SOT1      |              | This is also the UART ch.1 serial data output pin. This function is valid when UART ch.1 is enabled for data output.                                                                                                                                                                                   |  |  |  |  |  |

| 14                        | P45       | F            | In single chip mode this is a general-purpose I/O port. It can be set to open drain by the ODR4 register.                                                                                                                                                                                              |  |  |  |  |  |

|                           | SCK1      |              | This is also the UART ch.1 serial clock I/O pin. This function is valid wher UART ch.1 is enabled for clock output.                                                                                                                                                                                    |  |  |  |  |  |

| 15,16                     | P46,P47   | F            | In single chip mode this is a general-purpose I/O port. It can be set to open drain by the ODR4 register.                                                                                                                                                                                              |  |  |  |  |  |

|                           | PPG0,PPG1 |              | These are also the PPG0, 1 output pins. This function is valid when PPG0 1 output is enabled.                                                                                                                                                                                                          |  |  |  |  |  |

| 17                        | P50       | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                                                                                                                                |  |  |  |  |  |

|                           | SIN2      |              | This is also the I/O serial ch.0 data input pin. During serial data input, this input signal is in continuous use, and therefore the output function should only be used when needed.                                                                                                                  |  |  |  |  |  |

\*1: FPT-120P-M05

\*2: FPT-120P-M13,FPT-120P-M21

| Pin no.                   |          |              |                                                                                                                                                                                                                |     |     |   |                                                         |  |

|---------------------------|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---|---------------------------------------------------------|--|

| LQFP-120 *1<br>QFP-120 *2 | Pin name | Circuit type | Function                                                                                                                                                                                                       |     |     |   |                                                         |  |

| 18                        | P51      | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                                        |     |     |   |                                                         |  |

|                           | SOT2     |              | This is also the I/O serial ch.0 data output pin. This function is valid when serial ch.0 is enabled for serial data output.                                                                                   |     |     |   |                                                         |  |

| 19                        | P52      | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                                        |     |     |   |                                                         |  |

|                           | SCK2     | -            | This is also the I/O serial ch.0 clock I/O pin. This function is valid when serial ch.0 is enabled for serial data output.                                                                                     |     |     |   |                                                         |  |

| 20                        | P53      | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                                        |     |     |   |                                                         |  |

|                           | SIN3     | _            | This is also the I/O serial ch.1 data input pin. During serial data input, this input signal is in continuous use, and therefore the output function should only be used when needed.                          |     |     |   |                                                         |  |

| 21                        | P54      | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                                        |     |     |   |                                                         |  |

|                           | SOT3     | _            | This is also the I/O serial ch.1 data output pin. This function is valid when serial ch.1 is enabled for serial data output.                                                                                   |     |     |   |                                                         |  |

| 22                        | 22 P55   |              | P55                                                                                                                                                                                                            | P55 | P55 | E | In single chip mode this is a general-purpose I/O port. |  |

|                           | SCK3     |              | This is also the I/O serial ch.1 clock I/O pin. This function is valid when serial ch.1 is enabled for serial data output.                                                                                     |     |     |   |                                                         |  |

| 23,24                     | P56,P57  | E            | In single chip mode this is a general-purpose I/O port.                                                                                                                                                        |     |     |   |                                                         |  |

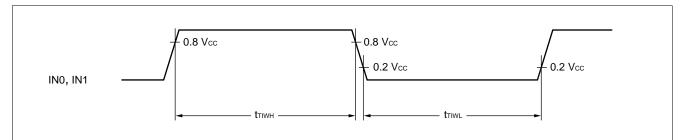

| INO,IN1                   |          | _            | These are also the input capture ch.0/1 trigger input pins. During input capture signal input on ch.0/1 this function is in continuous use, and therefore the output function should only be used when needed. |     |     |   |                                                         |  |

| 25                        | P60      | F            | In single chip mode this is a general-purpose I/O port. When set for input it can be set by the pull-up resistance register (RDR6). When set for output this setting will be invalid.                          |     |     |   |                                                         |  |

|                           | SIN4     | -            | This is also the I/O serial ch.2 data input pin. During serial data input this function is in continuous use, and therefore the output function should only be used when needed.                               |     |     |   |                                                         |  |

| 26                        | P61      | F            | In single chip mode this is a general-purpose I/O port. When set for input it can be set by the pull-up resistance register (RDR6). When set for output this setting will be invalid.                          |     |     |   |                                                         |  |

|                           | SOT4     | -            | This is also the I/O serial ch.2 data output pin. This function is valid when serial ch.2 is enabled for serial data output.                                                                                   |     |     |   |                                                         |  |

| 27                        | P62      | F            | In single chip mode this is a general-purpose I/O port. When set for input it can be set by the pull-up resistance register (RDR6). When set for output this setting will be invalid.                          |     |     |   |                                                         |  |

|                           | SCK4     |              | This is also the I/O serial ch.2 serial clock I/O pin. This function is valid when serial ch.2 is enabled for serial data output.                                                                              |     |     |   |                                                         |  |

| 28                        | P63      | F            | In single chip mode this is a general-purpose I/O port. When set for input it can be set by the pull-up resistance register (RDR6). When set for output this setting will be invalid.                          |     |     |   |                                                         |  |

|                           | СКОТ     |              | This is also the clock monitor output pin. This function is valid when clock monitor output is enabled.                                                                                                        |     |     |   |                                                         |  |

\*1: FPT-120P-M05

\*2: FPT-120P-M13,FPT-120P-M21

| Pin no.                   |                 |              |                                                                                                                                                                                                           |  |  |  |  |  |

|---------------------------|-----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| LQFP-120 *1<br>QFP-120 *2 | Pin name        | Circuit type | Function                                                                                                                                                                                                  |  |  |  |  |  |

| 29 to 32                  | P64 to P67      | F            | In single chip mode these are general-purpose I/O ports. When set for input they can be set by the pull-up resistance register (RDR6). When set for output this setting will be invalid.                  |  |  |  |  |  |

|                           | OUT0 to<br>OUT3 |              | These are also the output compare ch.0 to ch.3 event output pins. This function is valid when the respective channel(s) are enabled for output.                                                           |  |  |  |  |  |

| 35 to 37                  | P70 to P72      | E            | These are general purpose I/O ports.                                                                                                                                                                      |  |  |  |  |  |

| 40,41                     | P73,P74         | I            | These are general purpose I/O ports.                                                                                                                                                                      |  |  |  |  |  |

|                           | DA0,DA1         | -            | These are also the D/A converter ch.0,1 analog signal output pins.                                                                                                                                        |  |  |  |  |  |

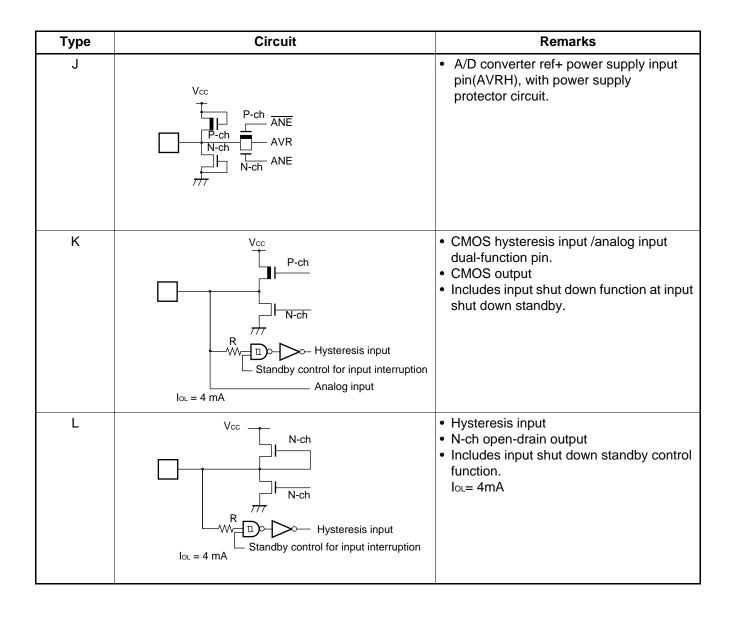

| 46 to 53                  | P80 to P87      | К            | These are general purpose I/O ports.                                                                                                                                                                      |  |  |  |  |  |

|                           | AN0 to AN7      |              | These are also A/D converter analog input pins. This function is valid when analog input is enabled.                                                                                                      |  |  |  |  |  |

| 55 to 62                  | P90 to P97      | E            | These are general purpose I/O ports.                                                                                                                                                                      |  |  |  |  |  |

|                           | CS0 to CS7      |              | These are also chip select signal output pins. This function is valid when chip select signal output is enabled.                                                                                          |  |  |  |  |  |

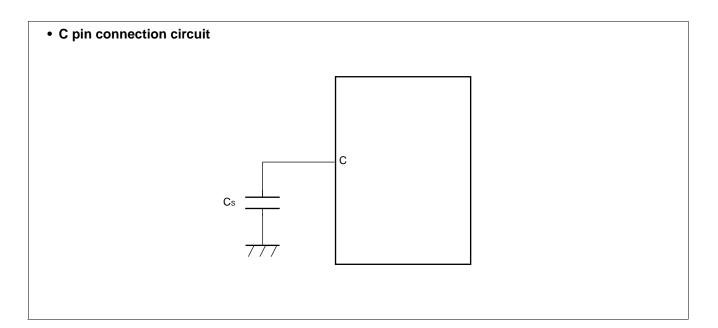

| 34                        | С               | G            | This is the power supply stabilization capacitor pin. It should be connected externally to an 0.1 $\mu$ F ceramic capacitor. Note that this is not required on the FLASH model (MB90F574/A) and MB90574C. |  |  |  |  |  |

| 64                        | PA0             | E            | This is a general purpose I/O port.                                                                                                                                                                       |  |  |  |  |  |

|                           | AINO            |              | This pin is also used as count clock A input for 8/16-bit up-down counter ch.0.                                                                                                                           |  |  |  |  |  |

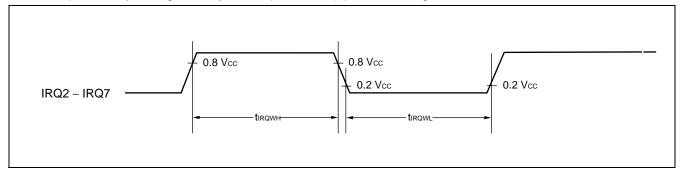

|                           | IRQ6            | -            | This pin can also be used as interrupt request input ch. 6.                                                                                                                                               |  |  |  |  |  |

| 65                        | PA1             | E            | This is a general purpose I/O port.                                                                                                                                                                       |  |  |  |  |  |

|                           | BIN0            |              | This pin is also used as count clock B input for 8/16-bit up-down counter ch.0.                                                                                                                           |  |  |  |  |  |

| 66                        | PA2             | E            | This is a general purpose I/O port.                                                                                                                                                                       |  |  |  |  |  |

|                           | ZINO            |              | This pin is also used as count clock Z input for 8/16-bit up-down counter ch.0.                                                                                                                           |  |  |  |  |  |

| 67                        | PA3             | E            | This is a general purpose I/O port.                                                                                                                                                                       |  |  |  |  |  |

|                           | AIN1            |              | This pin is also used as count clock A input for 8/16-bit up-down counter ch.1.                                                                                                                           |  |  |  |  |  |

|                           | IRQ7            | -            | This pin can also be used as interrupt request input ch.7.                                                                                                                                                |  |  |  |  |  |

| 68                        | PA4             | E            | This is a general purpose I/O port.                                                                                                                                                                       |  |  |  |  |  |

|                           | BIN1            | 1            | This pin is also used as count clock B input for 8/16-bit up-down counter ch.1.                                                                                                                           |  |  |  |  |  |

| 69                        | PA5             | E            | This is a general purpose I/O port.                                                                                                                                                                       |  |  |  |  |  |

|                           | ZIN1            |              | This pin is also used as count clock Z input for 8/16-bit up-down counter ch.1.                                                                                                                           |  |  |  |  |  |

\*1: FPT-120P-M05

\*2: FPT-120P-M13,FPT-120P-M21

(Continued)

| Pin no.                   |                       |                 |                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|---------------------------|-----------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LQFP-120 *1<br>QFP-120 *2 | Pin name              | Circuit type    | Function                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 70                        | PA6                   | L               | This is a general purpose I/O port.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                           | SDA                   |                 | This pin is also used as the data I/O pin for the I <sup>2</sup> C interface. This function is valid when the I <sup>2</sup> C interface is enabled for operation. While the I <sup>2</sup> C interface is operating, this port should be set to the input level (DDRA: bit6 = 0).                                                           |  |  |  |  |

| 71                        | PA7                   | L               | This is a general purpose I/O port.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                           | SCL                   |                 | This pin is also used as the clock I/O pin for the $I^2C$ interface. This function is valid when the $I^2C$ interface is enabled for operation. While the $I^2C$ interface is operating, this port should be set to the input level (DDRA: bit7 = 0).                                                                                        |  |  |  |  |

| 72,<br>75 to 79           | PB0,<br>PB1 to PB5    | E               | These are general-purpose I/O ports.                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                           | IRQ0,<br>IRQ1 to IRQ5 |                 | These pins are also the external interrupt input pins. IRQ0, 1 are<br>enabled for both rising and falling edge detection, and therefore cannot<br>be used for recovery from STOP status for MB90V570, MB90F574,<br>MB90573 and MB90574. However, IRQ0, 1 can be used for recovery<br>from STOP status for MB90V570A, MB90F574A and MB90574C. |  |  |  |  |

| 80                        | PB6                   | E               | This is a general purpose I/O port.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                           | ADTG                  |                 | This is also the A/D converter external trigger input pin. While the A/D converter is in input operation, this input signal is in continuous use, and therefore the output function should only be used when needed.                                                                                                                         |  |  |  |  |

| 81                        | PB7                   | E               | This is a general purpose I/O port.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 82 to 85                  | PC0 to PC3            | E               | These are general purpose I/O ports.                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 8,54,94                   | Vcc                   | Power<br>supply | These are power supply (5V) input pins.                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 33,63,<br>91,119          | Vss                   | Power<br>supply | These are power supply (0V) input pins.                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 42                        | AVcc                  | Н               | This is the analog macro (D/A, A/D etc.) Vcc power supply input pin.                                                                                                                                                                                                                                                                         |  |  |  |  |

| 43                        | AVRH                  | J               | This is the A/D converter Vref+ input pin. The input voltage should not exceed Vcc.                                                                                                                                                                                                                                                          |  |  |  |  |

| 44                        | AVRL                  | Н               | This is the A/D converter Vref-input pin. The input voltage should not less than Vss.                                                                                                                                                                                                                                                        |  |  |  |  |

| 45                        | AVss                  | Н               | This is the analog macro (D/A, A/D etc.) Vss power supply input pin.                                                                                                                                                                                                                                                                         |  |  |  |  |

| 38                        | DVcc                  | Н               | This is the D/A converter Vref input pin. The input voltage should not exceed Vcc.                                                                                                                                                                                                                                                           |  |  |  |  |

| 39                        | DVss                  | Н               | This is the D/A converter GND power supply pin. It should be set to Vss equivalent potential.                                                                                                                                                                                                                                                |  |  |  |  |

\*1: FPT-120P-M05

\*2: FPT-120P-M13,FPT-120P-M21

#### ■ I/O CIRCUIT TYPE

#### HANDLING DEVICES

#### 1. Preventing Latchup

CMOS ICs may cause latchup in the following situations:

- When a voltage higher than Vcc or lower than Vss is applied to input or output pins.

- When a voltage exceeding the rating is applied between Vcc and Vss.

- When AVcc power is supplied prior to the Vcc voltage.

In turning on/turning off the analog power supply, make sure the analog power voltage (AVcc, AVRH, DVcc) and analog input voltages not exceed the digital voltage (Vcc).

#### 2. Treatment of unused pins

Leaving unused input pins open may result in misbehavior or latch up and possible permanent damage of the device. Therefor they must be tied to Vcc or Ground through resistors. In this case those resistors should be more than 2 k<Symbol>W.

Unused bidirectional pins should be set to the output state and can be left open, or the input state with the above described connection.

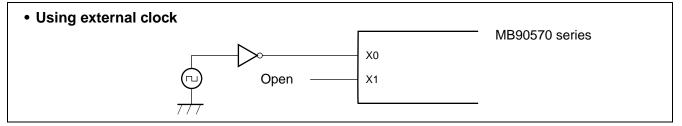

#### 3. Notes on Using External Clock

In using the external clock, drive X0 pin only and leave X1 pin unconnected.

#### 4. Unused Sub Clock Mode

If sub clock modes are not used, the oscillator should be connected to the X01A pin and X1A pin

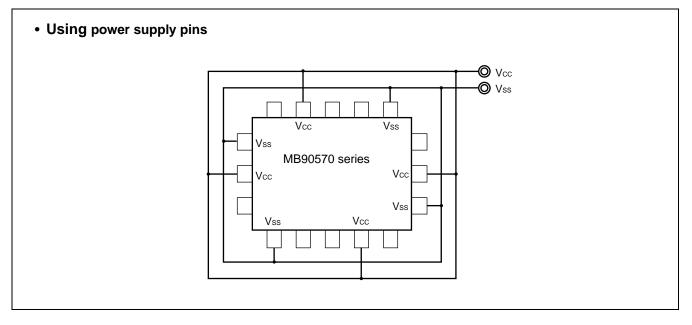

#### 5. Power Supply Pins (Vcc/Vss)

In products with multiple  $V_{cc}$  or  $V_{ss}$  pins, the pins of a same potential are internally connected in the device to avoid abnormal operations including latch-up. However, connect the pins external power and ground lines to lower the electro-magnetic emission level, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total current rating.

Make sure to connect Vcc and Vss pins via lowest impedance to power lines.

It is recommended to provide a bypass capacitor of around 0.1  $\mu$ F between V<sub>cc</sub> and V<sub>ss</sub> pin near the device.

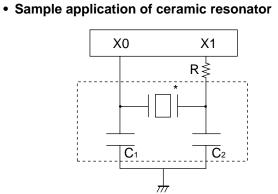

#### 6. Crystal Oscillator Circuit

Noises around X0 or X1 pins may be possible causes of abnormal operations. Make sure to provide bypass capacitors via shortest distance from X0, X1 pins, crystal oscillator (or ceramic resonator) and ground lines, and make sure, to the utmost effort, that lines of oscillation circuit do not cross the lines of other circuits.

It is highly recommended to provide a printed circuit board art work surrounding X0 and X1 pins with an grand area for stabilizing the operation.

#### 7. Turning-on Sequence of Power Supply to A/D Converter and Analog Inputs

Make sure to turn on the A/D converter power supply, D/A converter power supply (AVcc, AVRH, AVRL, DVcc, DVss) and analog inputs (AN0 to AN7) after turning-on the digital power supply (Vcc).

Turn-off the digital power after turning off the A/D converter supply and analog inputs. In this case, make sure that the voltage does not exceed AVRH or  $AV_{CC}$  (turning on/off the analog and digital power supplies simultaneously is acceptable).

#### 8. Connection of Unused Pins of A/D Converter

Connect unused pins of A/D converter to AVcc = Vcc, AVss = AVRH = DVcc = Vss.

#### 9. N.C. Pins

The N.C. (internally connected) pins must be opened for use.

#### 10. Notes on Energization

To prevent the internal regulator circuit from malfunctioning, set the voltage rise time during energization at 50 or more  $\mu$ s (0.2 V to 2.7 V).

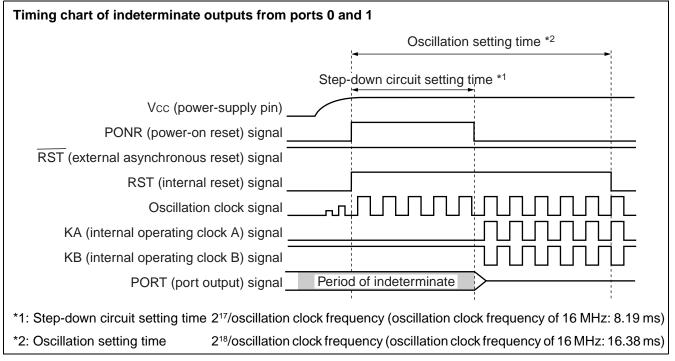

#### 11. Indeterminate outputs from ports 0 and 1

The outputs from ports 0 and 1 become indeterminate during oscillation setting time of step-down circuit (during a power-on reset) after the power is turned on. (MB90573, MB90574, MB90V570, MB90V570A)

The series without built-in step-down circuit have no oscillation setting time of step-down circuit, so outputs should not become indeterminate. (MB90F574,MB90F574A,MB90574C)

#### 12. Initialization

In the device, there are internal registers which are initialized only by a power-on reset. Turn on the power again to initialize these registers.

#### 13. Return from standby state

If the power-supply voltage goes below the standby RAM holding voltage in the standby state, the device may fail to return from the standby state. In this case, reset the device via the external reset pin to return to the normal state.

#### 14. Precautions for Use of 'DIV A, Ri,' and 'DIVW A, Ri' Instructions

The signed multiplication-division instructions 'DIV A, Ri,' and 'DIVW A, RWi' should be used when the corresponding bank registers (DTB, ADB, USB, SSB) are set to value '00h.' If the corresponding bank registers (DTB, ADB, USB, SSB) are set to a value other than '00h,' then the remainder obtained after the execution of the instruction will not be placed in the instruction operand register.

#### 15. Precautions for Use of REALOS

Extended intelligent I/O service (EI<sup>2</sup>OS) cannot be used, when REALOS is used.

#### BLOCK DIAGRAM

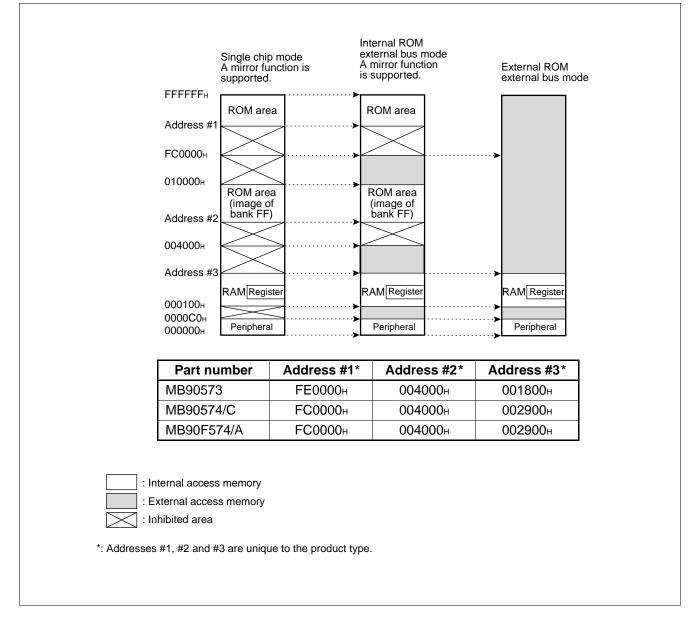

#### MEMORY MAP

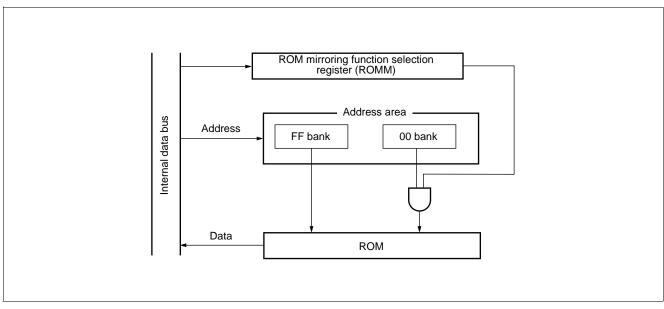

Note: The ROM data of bank FF is reflected in the upper address of bank 00, realizing effective use of the C compiler small model. The lower 16-bit of bank FF and the lower 16-bit of bank 00 is assigned to the same address, enabling reference of the table on the ROM without stating "far".

For example, if an attempt has been made to access 00C000H, the contents of the ROM at FFC000H are accessed actually. Since the ROM area of the FF bank exceeds 48 kbytes, the whole area cannot be reflected in the image for the 00 bank. The ROM data at FF4000H to FFFFFH looks, therefore, as if it were the image for 00400H to 00FFFFH. Thus, it is recommended that the ROM data table be stored in the area of FF4000H to FFFFFH.

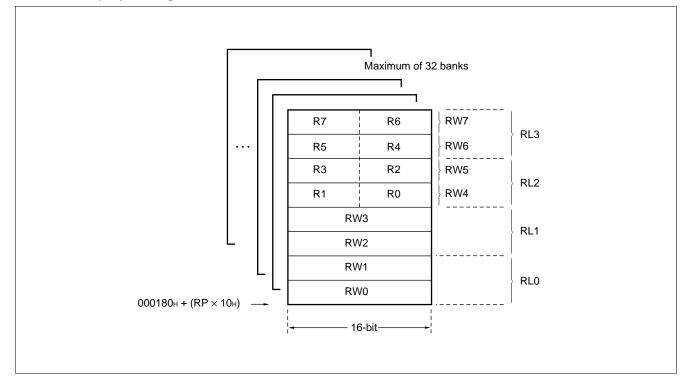

### ■ F<sup>2</sup>MC-16LX CPU PROGRAMMING MODEL

• Dedicated registers

| AH | AL      | : Accumulator (A)<br>Dual 16-bit register used for storing results of calculation etc. The two 16-bit<br>registers can be combined to be used as a 32-bit register. |

|----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | USP     | : User stack pointer (USP)<br>The 16-bit pointer indicating a user stack address.                                                                                   |

|    | SSP     | : System stack pointer (SSP)<br>The 16-bit pointer indicating the status of the system stack address.                                                               |

|    | PS      | : <b>Processor status (PS)</b><br>The 16-bit register indicating the system status.                                                                                 |

|    | PC      | : <b>Program counter (PC)</b><br>The 16-bit register indicating storing location of the current instruction code.                                                   |

|    | DPR     | : <b>Direct page register (DPR)</b><br>The 8-bit register indicating bit 8 through 15 of the operand address in the short direct addressing mode.                   |

|    | PCB     | : Program bank register (PCB)<br>The 8-bit register indicating the program space.                                                                                   |

|    | DTB     | <b>: Data bank register (DTB)</b><br>The 8-bit register indicating the data space.                                                                                  |

|    | USB     | : User stack bank register (USB)<br>The 8-bit register indicating the user stack space.                                                                             |

|    | SSB     | : System stack bank register (SSB)<br>The 8-bit register indicating the system stack space.                                                                         |

|    | ADB     | : Additional data bank register (ADB)<br>The 8-bit register indicating the additional data space.                                                                   |

| 32 | ¦16-Dit |                                                                                                                                                                     |

#### General-purpose registers

#### • Processor status (PS)

|                              |        | ILM    |        |        |        | RP     |       |       |       |       |       | CC    | R     |       |       |       |

|------------------------------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|                              | bit 15 | bit 14 | bit 13 | bit 12 | bit 11 | bit 10 | bit 9 | bit 8 | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |

| PS                           | ILM2   | ILM1   | ILM0   | B4     | B3     | B2     | B1    | B0    | _     | I     | s     | т     | Ν     | z     | V     | С     |

| Initial value                | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |       | 0     | 1     | Х     | Х     | Х     | Х     | Х     |

| —: Reserved<br>X : Undefined |        |        |        |        |        |        |       |       |       |       |       |       |       |       |       |       |

### ■ I/O MAP

| Address                  | Abbreviated<br>register<br>name | Register name                | Read/<br>write | Resource name                        | Initial value            |  |  |  |  |  |

|--------------------------|---------------------------------|------------------------------|----------------|--------------------------------------|--------------------------|--|--|--|--|--|

| 00000н                   | PDR0                            | Port 0 data register         | R/W            | Port 0                               | ХХХХХХХАв                |  |  |  |  |  |

| 000001н                  | PDR1                            | Port 1 data register         | R/W            | Port 1                               | ХХХХХХХХВ                |  |  |  |  |  |

| 00002н                   | PDR2                            | Port 2 data register         | R/W            | Port 2                               | ХХХХХХХАв                |  |  |  |  |  |

| 00003н                   | PDR3                            | Port 3 data register         | R/W            | Port 3                               | ХХХХХХХАв                |  |  |  |  |  |

| 000004н                  | PDR4                            | Port 4 data register         | R/W            | Port 4                               | ХХХХХХХАв                |  |  |  |  |  |

| 000005н                  | PDR5                            | Port 5 data register         | R/W            | Port 5                               | ХХХХХХХАв                |  |  |  |  |  |

| 00006н                   | PDR6                            | Port 6 data register         | R/W            | Port 6                               | ХХХХХХХАв                |  |  |  |  |  |

| 000007н                  | PDR7                            | Port 7 data register         | R/W            | Port 7                               | ХХХХХХХАв                |  |  |  |  |  |

| 00008н                   | PDR8                            | Port 8 data register         | R/W            | Port 8                               | ХХХХХХХАв                |  |  |  |  |  |

| 000009н                  | PDR9                            | Port 9 data register         | R/W            | Port 9                               | ХХХХХХХАв                |  |  |  |  |  |

| 00000Ан                  | PDRA                            | Port A data register         | R/W            | Port A                               | ХХХХХХХАв                |  |  |  |  |  |

| 00000Вн                  | PDRB                            | Port B data register         | R/W            | Port B                               | ХХХХХХХАв                |  |  |  |  |  |

| 00000Сн                  | PDRC                            | Port C data register         | R/W            | Port C                               | ХХХХХХХАв                |  |  |  |  |  |

| 00000Dн<br>to<br>00000Fн |                                 | (Disabled)                   |                |                                      |                          |  |  |  |  |  |

| 000010н                  | DDR0                            | Port 0 direction register    | R/W            | Port 0                               | 00000000в                |  |  |  |  |  |

| 000011н                  | DDR1                            | Port 1 direction register    | R/W            | Port 1                               | 00000000в                |  |  |  |  |  |

| 000012н                  | DDR2                            | Port 2 direction register    | R/W            | Port 2                               | 00000000в                |  |  |  |  |  |

| 000013н                  | DDR3                            | Port 3 direction register    | R/W            | Port 3                               | 00000000в                |  |  |  |  |  |

| 000014н                  | DDR4                            | Port 4 direction register    | R/W            | Port 4                               | 00000000в                |  |  |  |  |  |

| 000015н                  | DDR5                            | Port 5 direction register    | R/W            | Port 5                               | 00000000в                |  |  |  |  |  |

| 000016н                  | DDR6                            | Port 6 direction register    | R/W            | Port 6                               | 00000000в                |  |  |  |  |  |

| 000017н                  | DDR7                            | Port 7 direction register    | R/W            | Port 7                               | <b>— — — О О О О О</b> в |  |  |  |  |  |

| 000018н                  | DDR8                            | Port 8 direction register    | R/W            | Port 8                               | 00000000в                |  |  |  |  |  |

| 000019н                  | DDR9                            | Port 9 direction register    | R/W            | Port 9                               | 00000000в                |  |  |  |  |  |

| 00001Ан                  | DDRA                            | Port A direction register    | R/W            | Port A                               | 00000000в                |  |  |  |  |  |

| 00001Bн                  | DDRB                            | Port B direction register    | R/W            | Port B                               | 00000000в                |  |  |  |  |  |

| 00001CH                  | DDRC                            | Port C direction register    | R/W            | Port C                               | 00000000в                |  |  |  |  |  |

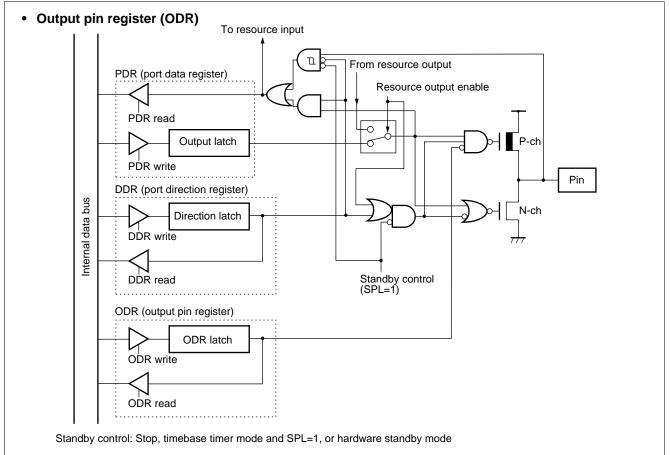

| 00001DH                  | ODR4                            | Port 4 output pin register   | R/W            | Port 4                               | 00000000в                |  |  |  |  |  |

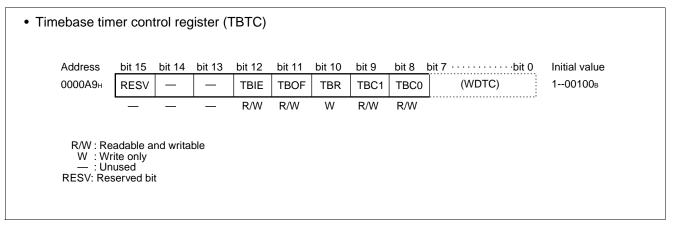

| 00001Ен                  | ADER                            | Analog input enable register | R/W            | Port 8,<br>8/10-bit<br>A/D converter | 11111118                 |  |  |  |  |  |

| 00001Fн                  |                                 | (Disa                        | bled)          |                                      |                          |  |  |  |  |  |

| 000020н                  | SMR0                            | Serial mode register 0       | R/W            | UART0                                | 00000000в                |  |  |  |  |  |