# UT28F256 Radiation-Hardened 32K x 8 PROM

**Data Sheet**

December 2002

#### **FEATURES**

- ☐ Programmable, read-only, asynchronous, radiationhardened, 32K x 8 memory

- Supported by industry standard programmer

- □ 45ns and 40ns maximum address access time (-55 °C to +125 °C)

- ☐ TTL compatible input and TTL/CMOS compatible output levels

- ☐ Three-state data bus

- ☐ Low operating and standby current

- Operating: 125mA maximum @25MHz

- Derating: 3mA/MHz

- Standby: 2mA maximum (post-rad)

- ☐ Radiation-hardened process and design; total dose irradiation testing to MIL-STD-883, Method 1019

- Total dose: 1E6 rad(Si)

- LET<sub>TH</sub>(0.25) ~ 100 MeV-cm<sup>2</sup>/mg

- SEL Immune  $\geq$ 128 MeV-cm<sup>2</sup>/mg

- Saturated Cross Section cm<sup>2</sup> per bit, 1.0E-11

- 1.2E-8 errors/device-day, Adams 90% geosynchronous heavy ion

- Memory cell LET threshold: >128 MeV-cm<sup>2</sup>/mg

- ☐ QML Q & V compliant part

- AC and DC testing at factory

- ☐ Packaging options:

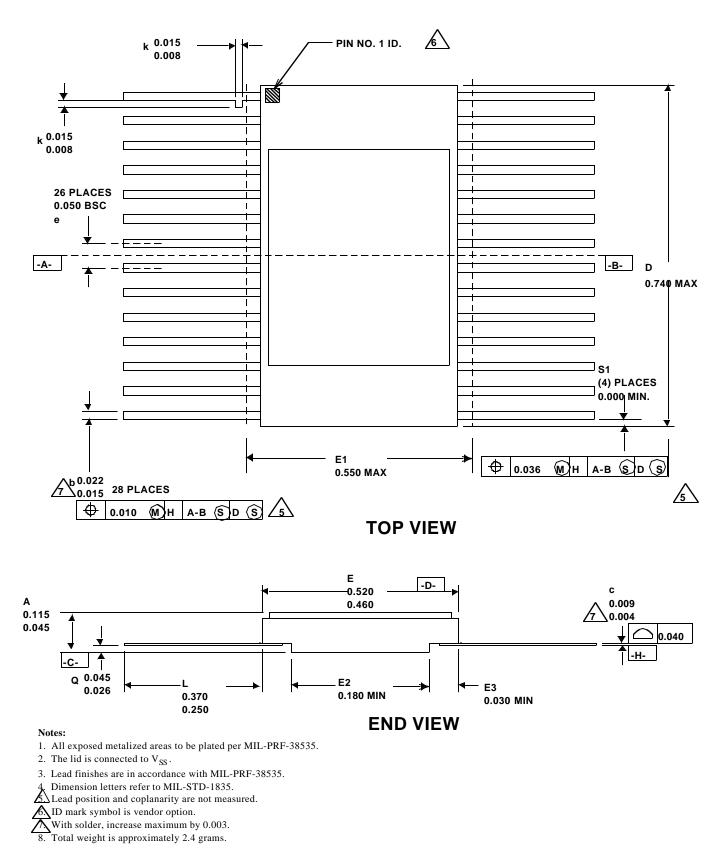

- 28-lead 50-mil center flatpack (0.490 x 0.74)

- 28-lead 100-mil center DIP (0.600 x 1.4) contact factory

- $\Box$  V<sub>DD</sub>: 5.0 volts <u>+</u> 10%

- ☐ Standard Microcircuit Drawing 5962-96891

#### PRODUCT DESCRIPTION

The UT28F256 amorphous silicon anti-fuse PROM is a high performance, asynchronous, radiation-hardened, 32K x 8 programmable memory device. The UT28F256 PROM features fully asychronous operation requiring no external clocks or timing strobes. An advanced radiation-hardened twin-well CMOS process technology is used to implement the UT28F256. The combination of radiation-hardness, fast access time, and low power consumption make the UT28F256 ideal for high speed systems designed for operation in radiation environments.

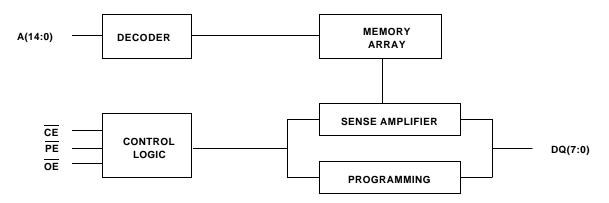

Figure 1. PROM Block Diagram

#### **DEVICE OPERATION**

The UT28F256 has three control inputs: Chip Enable (CE), Program Enable (PE), and Output Enable (OE); fifteen address inputs, A(14:0); and eight bidirectional data lines, DQ(7:0).CE is the device enable input that controls chip selection, active, and standby modes. AssertingCE causes I<sub>DD</sub> to rise to its active value and decodes the fifteen address inputs to select one of 32,768 words in the memory. PE controls program and read operations. During a read cycle, OE must be asserted to enable the outputs.

#### **PIN NAMES**

| A(14:0) | Address                |

|---------|------------------------|

| CE      | Chip Enable            |

| ŌĒ      | Output Enable          |

| PE      | Program Enable         |

| DQ(7:0) | Data Input/Data Output |

## PIN CONFIGURATION

|              |        |    | ] |           |

|--------------|--------|----|---|-----------|

| A14          | <br>1  | 28 |   | $V_{DD}$  |

| A12          | <br>2  | 27 |   | PE        |

| Α7           | <br>3  | 26 |   | A13       |

| A6           | <br>4  | 25 |   | <b>A8</b> |

| Α5           | <br>5  | 24 |   | A9        |

| A4           | <br>6  | 23 | _ | A11       |

| А3           | <br>7  | 22 |   | OE        |

| A2           | <br>8  | 21 |   | A10       |

| <b>A</b> 1   | <br>9  | 20 |   | CE        |

| A0           | <br>10 | 19 |   | DQ7       |

| DQ0          | <br>11 | 18 |   | DQ6       |

| DQ1          | <br>12 | 17 |   | DQ5       |

| DQ2          | <br>13 | 16 |   | DQ4       |

| $v_{\rm ss}$ | 14     | 15 |   | DQ3       |

**Table 1. Device Operation Truth Table** <sup>1</sup>

| OE | PE | CE | I/O MODE    | MODE              |

|----|----|----|-------------|-------------------|

| X  | 1  | 1  | Three-state | Standby           |

| 0  | 1  | 0  | Data Out    | Read              |

| 1  | 0  | 0  | Data In     | Program           |

| 1  | 1  | 0  | Three-state | Read <sup>2</sup> |

- **Notes:** 1. "X" is defined as a "don't care" condition.

- 2. Device active; outputs disabled.

# ABSOLUTE MAXIMUM RATINGS 1

(Referenced to  $V_{SS}$ )

| SYMBOL           | PARAMETER                                         | LIMITS                          | UNITS |

|------------------|---------------------------------------------------|---------------------------------|-------|

| V <sub>DD</sub>  | DC supply voltage                                 | -0.3 to 7.0                     | V     |

| V <sub>I/O</sub> | Voltage on any pin                                | -0.5 to (V <sub>DD</sub> + 0.5) | V     |

| T <sub>STG</sub> | Storage temperature                               | -65 to +150                     | °C    |

| $P_{\mathrm{D}}$ | Maximum power dissipation                         | 1.5                             | W     |

| T <sub>J</sub>   | Maximum junction temperature                      | +175                            | °C    |

| $\Theta_{ m JC}$ | Thermal resistance, junction-to-case <sup>2</sup> | 3.3                             | °C/W  |

| I <sub>I</sub>   | DC input current                                  | ±10                             | mA    |

- 1. Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Test per MIL-STD-883, Method 1012, infinite heat sink.

# RECOMMENDED OPERATING CONDITIONS

| SYMBOL            | PARAMETER               | LIMITS               | UNITS |

|-------------------|-------------------------|----------------------|-------|

| $V_{\mathrm{DD}}$ | Positive supply voltage | 4.5 to 5.5           | V     |

| $T_{\mathrm{C}}$  | Case temperature range  | -55 to +125          | °C    |

| V <sub>IN</sub>   | DC input voltage        | 0 to V <sub>DD</sub> | V     |

# DC ELECTRICAL CHARACTERISTICS (Pre/Post-Radiation)\*

$(V_{DD} = 5.0V \pm 10\%; -55^{\circ}C < T_{C} < +125^{\circ}C)$

| SYMBOL                             | PARAMETER                                                                      | CONDITION                                                                                                                                                                                  | MINIMUM              | MAXIMUM         | UNIT     |

|------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|----------|

| V <sub>IH</sub>                    | High-level input voltage                                                       | (TTL)                                                                                                                                                                                      | 2.4                  |                 | V        |

| V <sub>IL</sub>                    | Low-level input voltage                                                        | (TTL)                                                                                                                                                                                      |                      | 0.8             | V        |

| V <sub>OL1</sub>                   | Low-level output voltage                                                       | $I_{OL} = 4.0 \text{mA}, V_{DD} = 4.5 \text{V (TTL)}$                                                                                                                                      |                      | 0.4             | V        |

| V <sub>OL2</sub>                   | Low-level output voltage                                                       | $I_{OL} = 200 \mu\text{A},  V_{DD} = 4.5  V  (CMOS)$                                                                                                                                       |                      | $V_{SS} + 0.10$ | V        |

| V <sub>OH1</sub>                   | High-level output voltage                                                      | $I_{OH} = -200 \mu A, V_{DD} = 4.5 V (CMOS)$                                                                                                                                               | V <sub>DD</sub> -0.1 |                 | V        |

| V <sub>OH2</sub>                   | High-level output voltage                                                      | $I_{OH} = -2.0 \text{mA}, V_{DD} = 4.5 \text{V (TTL)}$                                                                                                                                     | 2.4                  |                 | V        |

| C <sub>IN</sub> <sup>1</sup>       | Input capacitance                                                              | $f = 1$ MHz, $V_{DD} = 5.0$ V<br>$V_{IN} = 0$ V                                                                                                                                            |                      | 15              | pF       |

| C <sub>IO</sub> 1, 4               | Bidirectional I/O capacitance                                                  | $f = 1$ MHz, $V_{DD} = 5.0$ V<br>$V_{OUT} = 0$ V                                                                                                                                           |                      | 15              | pF       |

| I <sub>IN</sub>                    | Input leakage current                                                          | $V_{IN} = 0V \text{ to } V_{DD}$                                                                                                                                                           | -5                   | 5               | μΑ       |

| I <sub>OZ</sub>                    | Three-state output leakage current                                             | $V_O = 0V \text{ to } V_{DD}$<br>$V_{DD} = 5.5V$<br>OE = 5.5V                                                                                                                              | -10                  | 10              | μА       |

| I <sub>OS</sub> <sup>2,3</sup>     | Short-circuit output current                                                   | $V_{DD} = 5.5V, V_{O} = V_{DD}$<br>$V_{DD} = 5.5V, V_{O} = 0V$                                                                                                                             | -90                  | 90              | mA<br>mA |

| I <sub>DD1</sub> (OP) <sup>5</sup> | Supply current operating<br>@25.0MHz (40ns product)<br>@22.2MHz (45ns product) | TTL inputs levels ( $I_{OUT} = 0$ ), $V_{IL} = 0.2V$<br>$V_{DD}$ , $\overline{PE} = 5.5V$                                                                                                  |                      | 125<br>117      | mA<br>mA |

| I <sub>DD2</sub> (SB)<br>post-rad  | Supply current standby                                                         | $\frac{\text{CMOS input levels V}_{\text{IL}} = \text{V}_{\text{SS}} + 0.25\text{V}}{\text{CE}} = \text{V}_{\text{DD}} - 0.25\text{ V}_{\text{IH}} = \text{V}_{\text{DD}} - 0.25\text{V}}$ |                      | 2               | mA       |

<sup>\*</sup> Post-radiation performance guaranteed at 25°C per MIL-STD-883 Method 1019 at 1E6 rad(Si).

1. Measured only for initial qualification, and after process or design changes that could affect input/output capacitance.

<sup>2.</sup> Supplied as a design limit but not guaranteed or tested.

<sup>3.</sup> Not more than one output may be shorted at a time for maximum duration of one second.4. Functional test.

<sup>5.</sup> Derates at 3.0mA/MHz.

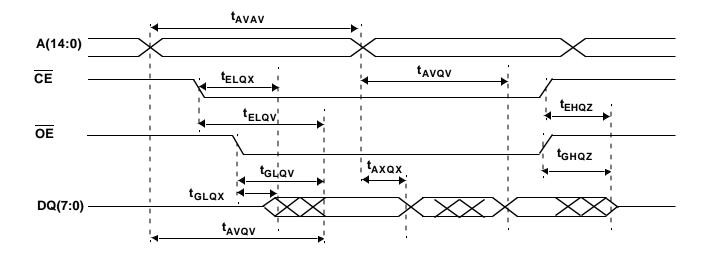

#### READ CYCLE

A combination of  $\overline{PE}$  greater than  $V_{IH}(min)$ , and  $\overline{CE}$  less than  $V_{IL}(max)$  defines a read cycle. Read access time is measured from the latter of device enable, output enable, or valid address to valid data output.

An address access read is initiated by a change in address inputs while the chip is enabled with  $\overline{OE}$  asserted and  $\overline{PE}$  deasserted. Valid data appears on data output, DQ(7:0), after the specified  $t_{AVQV}$  is satisfied. Outputs remain active throughout the entire cycle. As long as device enable and output enable are active, the address inputs may change at a rate equal to the minimum read cycle time.

The chip enable-controlled access is initiated by  $\overline{CE}$  going active while  $\overline{OE}$  remains asserted,  $\overline{PE}$  remains deasserted, and the addresses remain stable for the entire cycle. After the specified  $t_{ELQV}$  is satisfied, the eight-bit word addressed by A(14:0) appears at the data outputs DQ(7:0).

Output enable-controlled access is initiated by  $\overline{OE}$  going active while  $\overline{CE}$  is asserted,  $\overline{PE}$  is deasserted, and the addresses are stable. Read access time is  $t_{GLQV}$  unless  $t_{AVQV}$  or  $t_{ELQV}$  have not been satisfied.

## AC CHARACTERISTICS READ CYCLE (Post-Radiation)\*

$(V_{DD} = 5.0V \pm 10\%; -55^{\circ}C < T_{C} < +125^{\circ}C)$

| SYMBOL                         | IBOL PARAMETER 28F256-45              |     | 56-45 | 28F256-40 |     | UNIT |

|--------------------------------|---------------------------------------|-----|-------|-----------|-----|------|

|                                |                                       | MIN | MAX   | MIN       | MAX |      |

| $t_{AVAV}^{1}$                 | Read cycle time                       | 45  |       | 40        |     | ns   |

| $t_{AVQV}$                     | Read access time                      |     | 45    |           | 40  | ns   |

| t <sub>AXQX</sub> <sup>2</sup> | Output hold time                      | 0   |       | 0         |     | ns   |

| $t_{\rm GLQX}^2$               | OE-controlled output enable time      | 0   |       | 0         |     | ns   |

| $t_{GLQV}$                     | OE-controlled access time             |     | 15    |           | 15  | ns   |

| t <sub>GHQZ</sub>              | OE-controlled output three-state time |     | 15    |           | 15  | ns   |

| ${\rm t_{ELQX}}^2$             | CE-controlled output enable time      | 0   |       | 0         |     | ns   |

| t <sub>ELQV</sub>              | CE-controlled access time             |     | 45    |           | 40  | ns   |

| t <sub>EHQZ</sub>              | CE-controlled output three-state time |     | 15    |           | 15  | ns   |

- \* Post-radiation performance guaranteed at 25 °C per MIL-STD-883 Method 1019 at 1E6 rads(Si).

- 1. Functional test.

- 2. Three-state is defined as a 400mV change from steady-state output voltage.

Figure 2. PROM Read Cycle

## RADIATION HARDNESS

The UT28F256 PROM incorporates special design and layout features which allow operation in high-level radiation environments. UTMC has developed special low-temperature processing techniques designed to enhance the total-dose radiation hardness of both the gate oxide and the field oxide while

maintaining the circuit density and reliability. For transient radiation hardness and latchup immunity, UTMC builds all radiation-hardened products on epitaxial wafers using an advanced twin-tub CMOS process. In addition, UTMC pays special attention to power and ground distribution during the design phase, minimizing dose-rate upset caused by rail collapse.

## RADIATION HARDNESS DESIGN SPECIFICATIONS 1

| Total Dose                                                             | 1E6  | rad(Si)                 |

|------------------------------------------------------------------------|------|-------------------------|

| Latchup LET Threshold                                                  | >128 | MeV-cm <sup>2</sup> /mg |

| Memory Cell LET Threshold                                              | >128 | MeV-cm <sup>2</sup> /mg |

| Transient Upset LET Threshold                                          | 54   | MeV-cm <sup>2</sup> /mg |

| Transient Upset Device Cross Section @ LET=128 MeV-cm <sup>2</sup> /mg | 1E-6 | cm <sup>2</sup>         |

<sup>1.</sup> The PROM will not latchup during radiation exposure under recommended operating conditions.

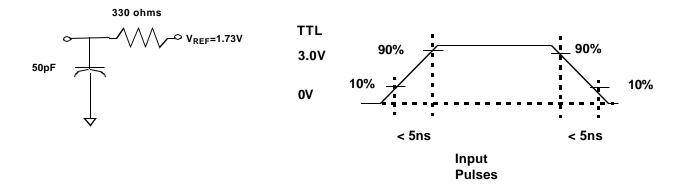

- 1. 50pF including scope probe and test socket.

- 2. Measurement of data output occurs at the low to high or high to low transition mid-point (TTL input = 1.5V).

Figure 3. AC Test Loads and Input Waveforms

Figure 5. 28-Lead 50-mil Center Flatpack (0.490 x 0.74)

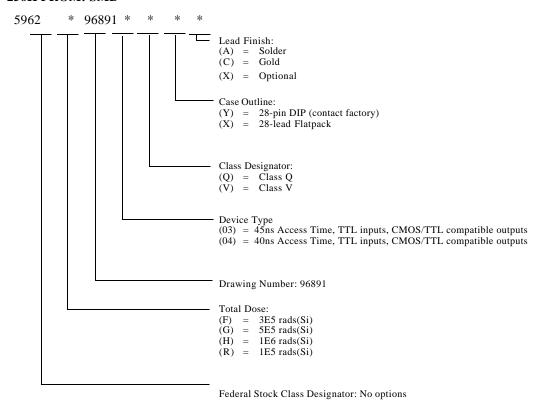

# **ORDERING INFORMATION**

## 256K PROM: SMD

- 1. Lead finish (A, C, or X) must be specified.

- 2. If an "X" is specified when ordering, part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

- 3. Total dose radiation must be specified when ordering. QML Q and QML V not available without radiation hardening.

- 4. Check factory for availability of 45ns part.

- 5. Lead finish: Factory programming either solder or gold. Field programming gold only.

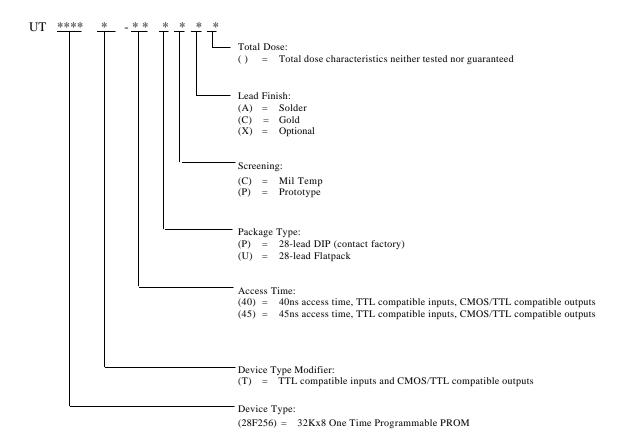

#### 256K PROM

- 1. Lead finish (A,C, or X) must be specified.

2. If an "X" is specified when ordering, then the part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

3. Military Temperature Range flow per UTMC Manufacturing Flows Document. Radiation characteristics are neither tested nor guaranteed and may not be specified.

- 4. Prototype flow per UTMC Manufacturing Flows Document. Devices have prototype assembly and are tested at 25°C only. Radiation characteristics are neither tested nor guaranteed and may not be specified.

- 5. Check factory for availability of 45ns part.

- 6. Lead finish: Factory programming either solder or gold. Field programming gold only.

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from:

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com