## intersil

# 捷多邦, 专业PCB打样工厂, 24小时加急出货 ACTS 161V/S

Radiation Hardened 4-Bit Synchronous Counter

January 1996

#### **Features**

- Devices QML Qualified in Accordance with MIL-PRF-38535

- Detailed Electrical and Screening Requirements are Contained in SMD# 5962-96716 and Intersil's QM Plan

- 1.25 Micron Radiation Hardened SOS CMOS

- Single Event Upset (SEU) Immunity: <1 x 10<sup>-10</sup> Errors/Bit/Day (Typ)

- Dose Rate Upset ......>10<sup>11</sup> RAD (Si)/s, 20ns Pulse

- Dose Rate Survivability.....>10<sup>12</sup> RAD (Si)/s, 20ns Pulse

- Latch-Up Free Under Any Conditions

- Significant Power Reduction Compared to ALSTTL Logic

- DC Operating Voltage Range . . . . . . . . . . . . 4.5V to 5.5V

- Input Logic Levels

- VIL = 0.8V Max

- VIH = VCC/2 Min

- Input Current ≤ 1μA at VOL, VOH

- Fast Propagation Delay . . . . . . . . . . . . . . . . . 25ns (Max), 16ns (Typ)

#### Description

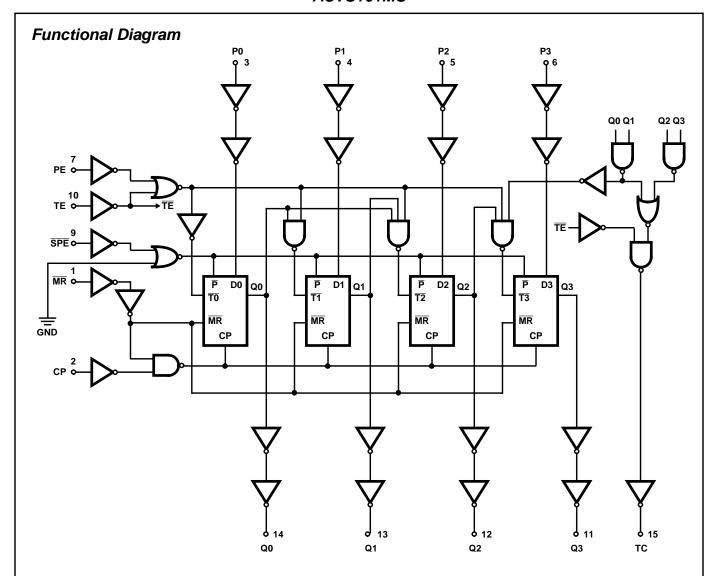

The Intersil ACTS161MS is a Radiation Hardened 4-Bit Binary Synchronous Counter, featuring asynchronous reset and load ahead carry logic. The  $\overline{\text{MR}}$  is an active low master reset.  $\overline{\text{SPE}}$  is an active low Synchronous Parallel Enable which disables counting and allows data at the preset inputs (P0 - P3) to load the counter.  $\overline{\text{CP}}$  is the positive edge clock.  $\overline{\text{TC}}$  is the terminal count or carry output. Both  $\overline{\text{TE}}$  and  $\overline{\text{PE}}$  must be high for counting to occur, but are irrelevant to loading.  $\overline{\text{TE}}$  low will keep  $\overline{\text{TC}}$  low.

The ACTS161MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of a radiation hardened, high-speed, CMOS/SOS Logic family.

The ACTS161MS is supplied in a 16 lead Ceramic Flatpack (K suffix) or a Ceramic Dual-In-Line Package (D suffix).

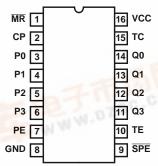

#### **Pinouts**

16 PIN CERAMIC DUAL-IN-LINE

MIL-STD-1835, DESIGNATOR CDIP2-T16,

LEAD FINISH C

TOP VIEW

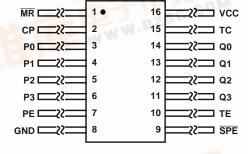

16 PIN CERAMIC FLATPACK

MIL-STD-1835, DESIGNATOR CDFP4-F16,

LEAD FINISH C

TOP VIEW

### O<mark>rdering Information</mark>

| PART NUMBER     | TEMPERATURE RANGE | SCREENING LEVEL       | PACKAGE                  |  |  |

|-----------------|-------------------|-----------------------|--------------------------|--|--|

| 5962F9671601VEC | -55°C to +125°C   | MIL-PRF-38535 Class V | 16 Lead SBDIP            |  |  |

| 5962F9671601VXC | -55°C to +125°C   | MIL-PRF-38535 Class V | 16 Lead Ceramic Flatpack |  |  |

| ACTS161D/Sample | 25°C              | Sample                | 16 Lead SBDIP            |  |  |

| ACTS161K/Sample | 25°C              | Sample                | 16 Lead Ceramic Flatpack |  |  |

| ACTS161HMSR     | 25°C              | Die                   | Die                      |  |  |

#### ACTS161MS

**TRUTH TABLE**

|                | INPUTS |    |            |            |            |                | OUTPUTS        |          |

|----------------|--------|----|------------|------------|------------|----------------|----------------|----------|

| OPERATING MODE | MR     | СР | PE         | TE         | SPE        | P <sub>N</sub> | Q <sub>N</sub> | тс       |

| Reset (Clear)  | L      | Х  | Х          | Х          | Х          | Х              | L              | L        |

| Parallel Load  | Н      |    | Х          | Х          | I          | I              | L              | L        |

|                | Н      |    | Х          | Х          | I          | h              | Н              | (Note 1) |

| Count          | Н      |    | h          | h          | h (Note 3) | Х              | count          | (Note 1) |

| Inhibit        | Н      | Х  | I (Note 2) | Х          | h (Note 3) | Х              | $q_N$          | (Note 1) |

|                | Н      | Х  | Х          | I (Note 2) | h (Note 3) | Х              | $q_N$          | L        |

H = High Steady State, L = Low Steady State, h = High voltage level one setup time prior to the Low-to-High clock transition, I = Low voltage level one setup time prior to the Low-to-High clock transition, X = Don't Care,q = Lower case letters indicate the state of the referenced output prior to the Low-to-High clock transition, \_\_\_\_ = Low-to-High Transition.

NOTES:

- 1. The TC output is High when TE is High and the counter is at Terminal Count (HHHH).

- 2. The High-to-Low transition of PE or TE should only occur while CP is High for conventional operation.

- 3. The Low-to-High transition of SPE should only occur while CP is High for conventional operation.

- ·· · F40000

#### ACTS161MS

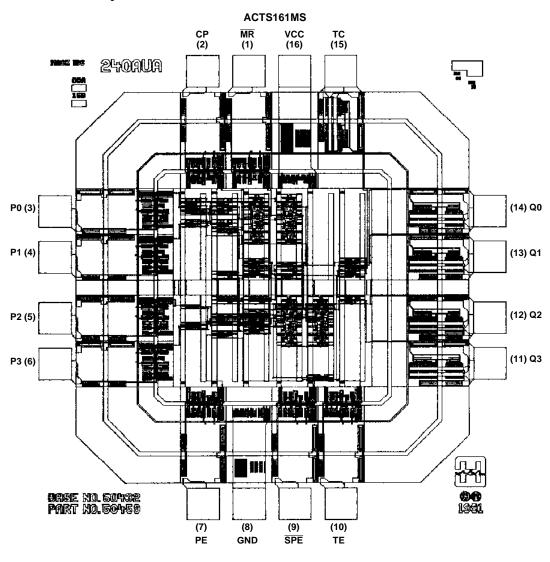

#### Die Characteristics

#### **DIE DIMENSIONS:**

88 mils x 88 mils 2240mm x 2240mm

#### **METALLIZATION:**

Type: AlSi

Metal 1 Thickness: 7.125kÅ ±1.125kÅ Metal 2 Thickness: 9kÅ ±1kÅ

#### **GLASSIVATION:**

Type: SiO<sub>2</sub>

Thickness: 8kÅ ±1kÅ

#### **WORST CASE CURRENT DENSITY:**

$< 2.0 \times 10^5 \text{A/cm}^2$

#### **BOND PAD SIZE:**

110μm x 110μm 4.3 mils x 4.3 mils

#### Metallization Mask Layout

- .. . E40000

#### ACTS161MS

1130 Brussels, Belgium

TEL: (32) 2.724.2111

FAX: (32) 2.724.22.05

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029

TEL: (321) 724-7000

FAX: (321) 724-7240