### 查询5962-8763308QA供应商

# 捷多邦,专业PCB打样工厂,24小时加急出货MS320C1x DIGITAL SIGNAL PROCESSORS

SPRS009C-JANUARY 1987-REVISED JULY 1991

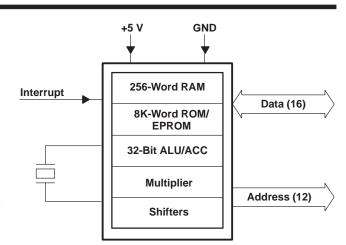

- Performance Up to 8.77 MIPs

- All TMS320C1x Devices are Object Code Compatible

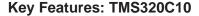

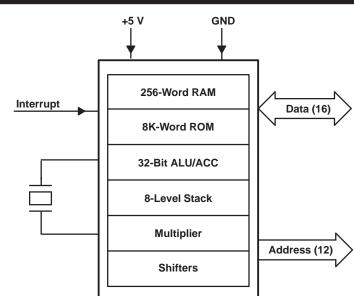

- 144/256-Word On-Chip Data RAM

- 1.5K/4K/8K-Word On-Chip Program ROM

- 4K-Word On-Chip Program EPROM (TMS320E14/P14/E15/P15/E17/P17)

- One-Time Programmable (OTP) Versions Available (TMS320P14/P15/P17)

- EPROM Code Protection for Copyright Security

- 4K / 64K-Word Total External Memory at **Full Speed**

- 32-Bit ALU/Accumulator

- 16 × 16-Bit Multiplier With a 32-Bit Product

- 0 to 16-Bit Barrel Shifter

- Eight Input/Output Channels 150.00M

- Dual-Channel Serial Port

- Simple Memory and I/O Interface

- 5-V and 3.3-V Versions Available (TMS320LC15/LC17)

#### introduction

- **Commercial and Military Versions Available**

- **Operating Free-Air Temperature** ... 0°C to 70°C

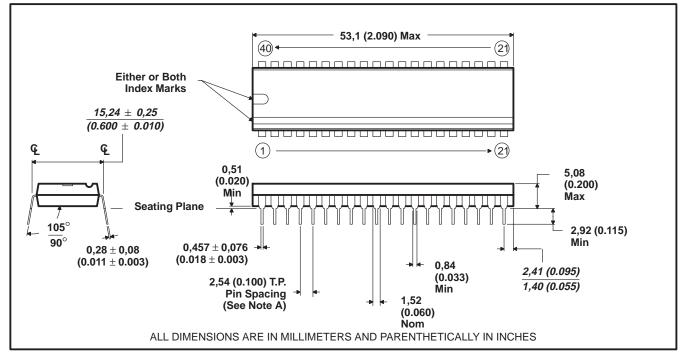

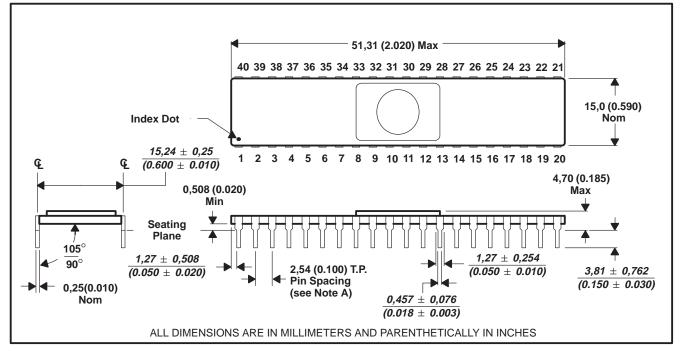

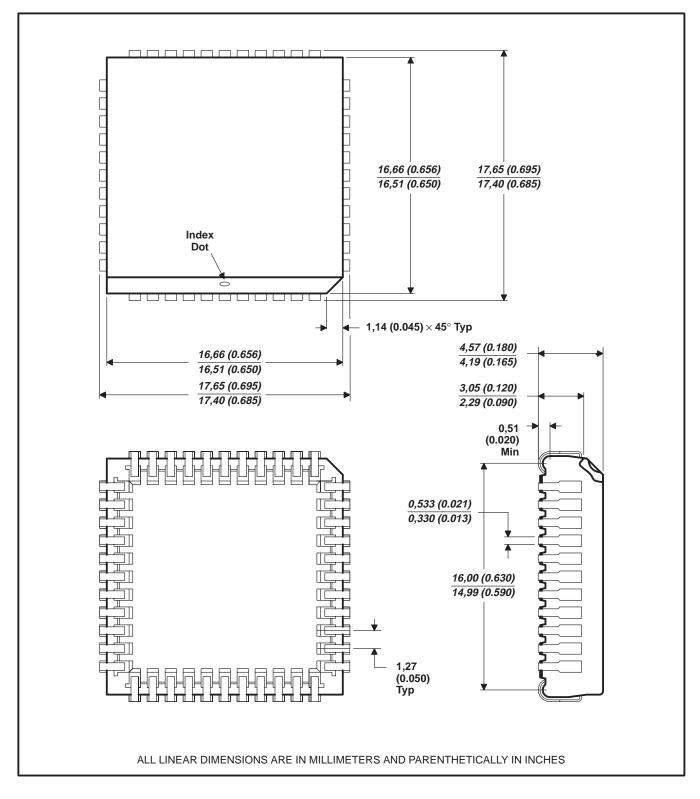

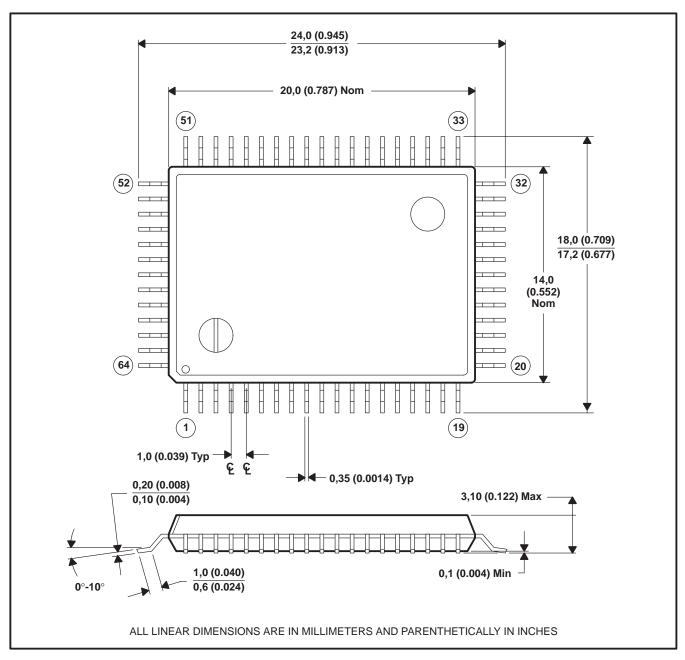

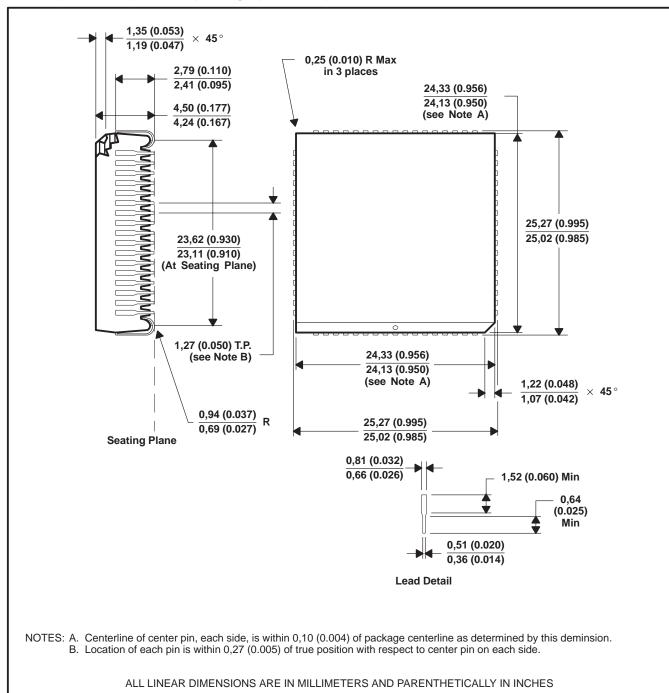

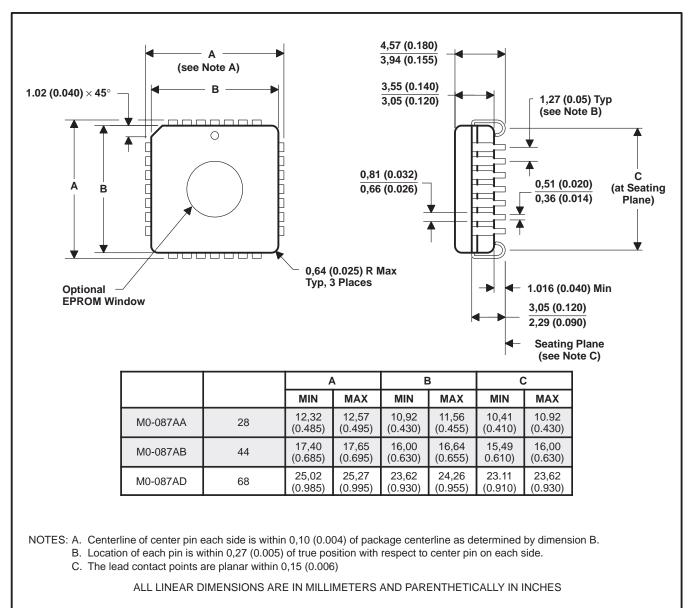

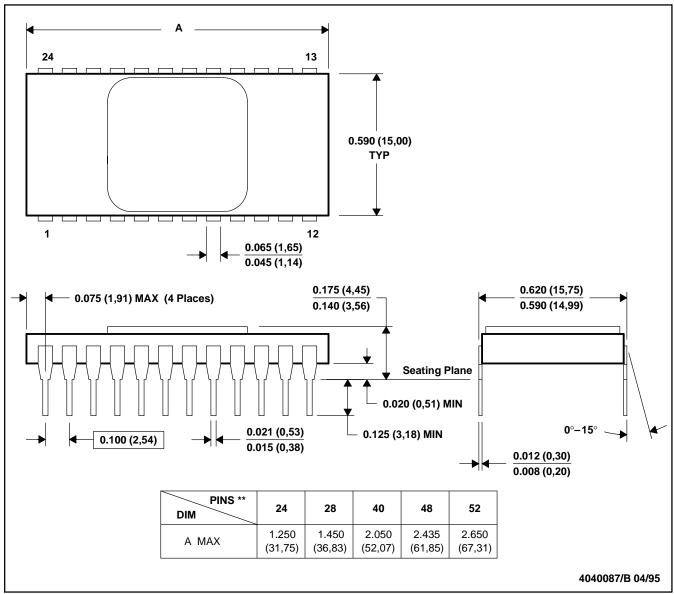

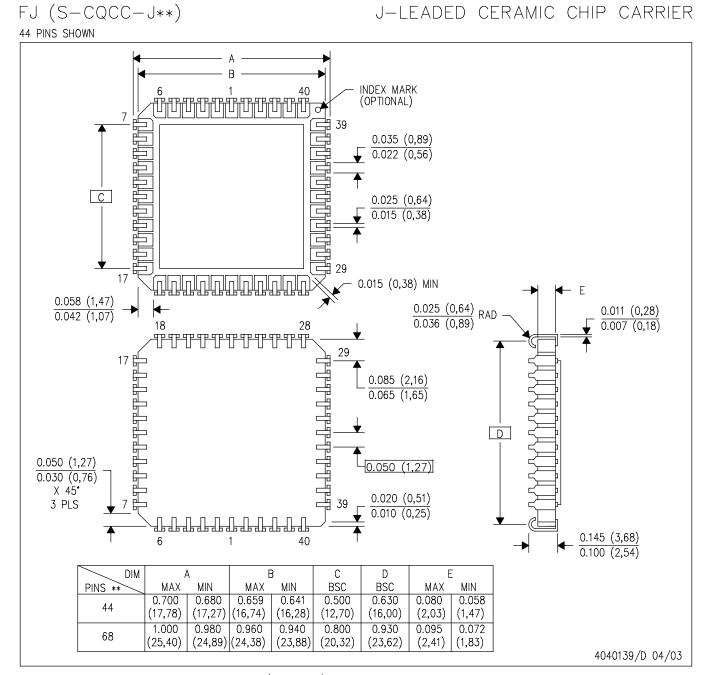

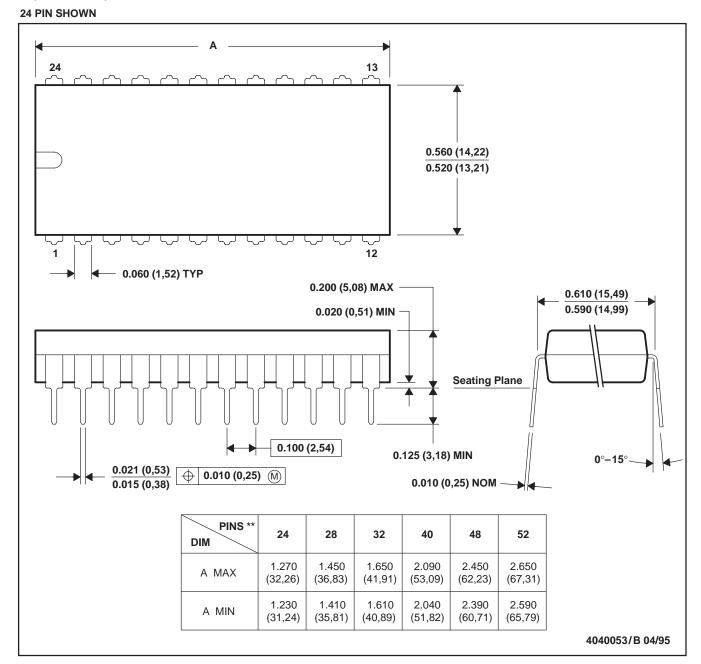

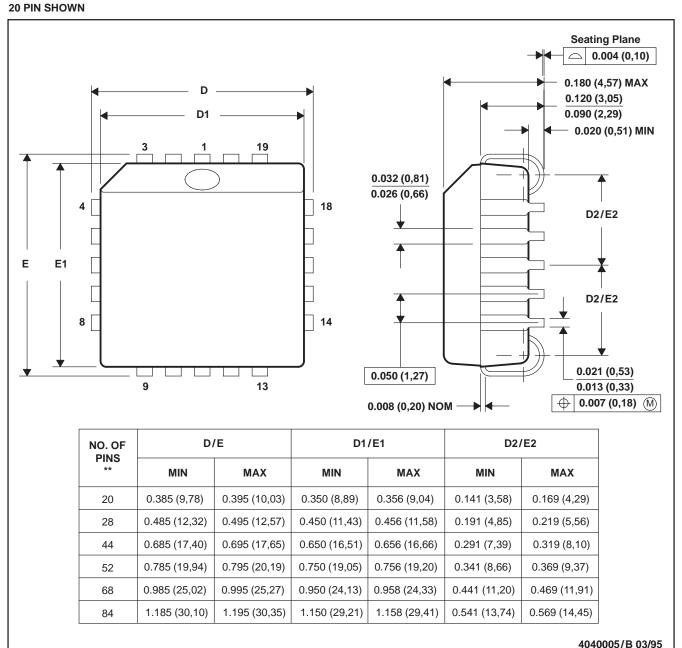

- Packaging: DIP, PLCC, Quad Flatpack, and **CER-QUAD**

- **CMOS** Technology:

| Device         | Cycle Time |

|----------------|------------|

| — TMS320C10    | 200-ns     |

| — TMS320C10-14 | 280-ns     |

| — TMS320C10-25 | 160-ns     |

| — TMS320C14    | 160-ns     |

| — TMS320E14    | 160-ns     |

| — TMS320P14    |            |

| — TMS320C15    | 200-ns     |

| - TMS320C15-25 | 160-ns     |

| — TMS320E15    | 200-ns     |

| - TMS320E15-25 | 160-ns     |

| — TMS320LC15   | 250-ns     |

| — TMS320P15    | 200-ns     |

| — TMS320C16    | 114-ns     |

| — TMS320C17    | 200-ns     |

| — TMS320E17    | 200-ns     |

| — TMS320LC17   | 278-ns     |

| — TMS320P17    | 200-ns     |

WWW.DZSC.COM

The TMS32010 digital signal processor (DSP), introduced in 1983, was the first DSP in the TMS320 family. From it has evolved this TMS320C1x generation of 16-bit DSPs. All 'C1x DSPs are object code compatible with the TMS32010 DSP. The 'C1x DSPs combine the flexibility of a high-speed controller with the numerical capability of an array processor, thereby offering an inexpensive alternative to multichip bit-slice processors. The highly paralleled architecture and efficient instruction set provide speed and flexibility to produce a CMOS microprocessor generation capable of executing up to 8.77 MIPS (million instructions per second) ('C16). These <sup>C1</sup>x devices utilize a modified Harvard architecture to optimize speed and flexibility, implementing functions in hardware that other processors implement through microcode or software.

The 'C1x generation's powerful instruction set, inherent flexibility, high-speed number-handling capabilities, reduced power consumption, and innovative architecture have made these cost-effective DSPs the ideal solution for many telecommunications, computer, commercial, industrial, and military applications.

This data sheet provides detailed design documentation for the 'C1x DSPs. It facilitates the selection of devices best suited for various user applications by providing specifications and special features for each 'C1x DSP.

This data sheet is arranged as follows: introduction, quick reference table of device parameters and packages, summary overview of each device, architecture overview, and the 'C1x device instruction set summary. These are followed by data sheets for each 'C1x device providing available package styles, terminal function tables, block diagrams, and electrical and timing parameters. An index is provided to facilitate data sheet usage.

# TMS320C1x DIGITAL SIGNAL PROCESSORS

SPRS009C-JANUARY 1987-REVISED JULY 1991

Table 1 provides an overview of 'C1x processors with comparisons of memory, I/O, cycle timing, military support, and package types. For specific availability, contact the nearest TI Field Sales Office.

| DEVICE                     |     | ME   | MORY  |       |        | I/O      | CYCLE |       | PACKAGE | (1)      |

|----------------------------|-----|------|-------|-------|--------|----------|-------|-------|---------|----------|

| DEVICE                     | RAM | ROM  | EPROM | PROG. | SERIAL | PARALLEL | (ns)  | DIP   | PLCC    | CER-QUAD |

| TMS320C10 (2)              | 144 | 1.5K | —     | 4K    | —      | 8×16     | 200   | 40    | 44      | -        |

| TMS320C10-14               | 144 | 1.5K | —     | 4K    | —      | 8×16     | 280   | 40    | 44      | -        |

| TMS320C10-25               | 144 | 1.5K | —     | 4K    | —      | 8×16     | 160   | 40    | 44      | -        |

| TMS320C14 (3)              | 256 | 4K   | -     | 4K    | 1      | 7×16 (4) | 160   | _     | 68      | - 1      |

| TMS320E14 (3)              | 256 | _    | 4K    | 4K    | 1      | 7×16 (4) | 160   | _     | —       | 68 CER   |

| TMS320P14 <sup>†</sup>     | 256 | _    | 4K    | 4K    | 1      | 7×16 (4) | 160   | _     | 68      | - 1      |

| TMS320C15 (3)              | 256 | 4K   | _     | 4K    | —      | 8×16     | 200   | 40    | 44      | - 1      |

| TMS320C15-25               | 256 | 4K   | _     | 4K    | —      | 8×16     | 160   | 40    | 44      | - 1      |

| TMS320E15 (3)              | 256 | _    | 4K    | 4K    | —      | 8×16     | 200   | 40    | _       | 44 CER   |

| TMS320E15-25               | 256 | _    | 4K    | 4K    | —      | 8×16     | 160   | 40    | _       | 44 CER   |

| TMS320LC15                 | 256 | 4K   | -     | 4K    | -      | 8×16     | 250   | 40    | 44      | —        |

| TMS320P15 <sup>†</sup>     | 256 | —    | 4K    | 4K    | -      | 8×16     | 200   | 40    | 44      | —        |

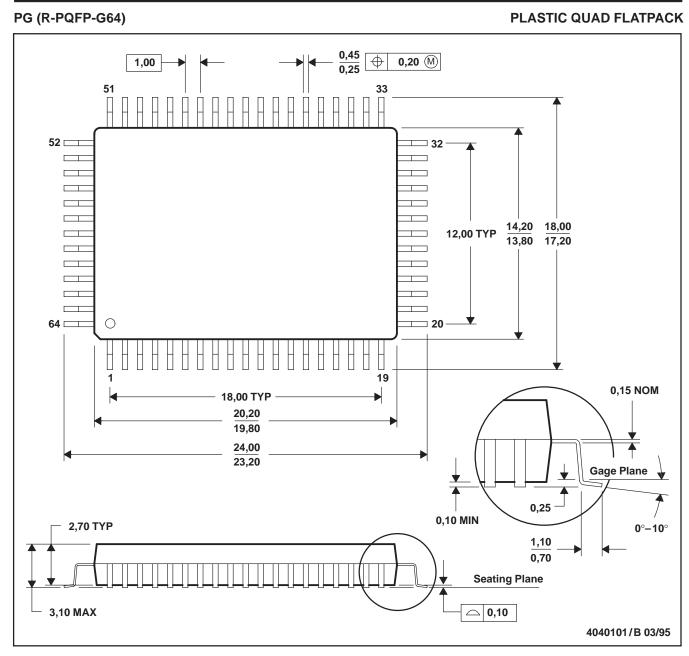

| TMS320C16                  | 256 | 8K   | —     | 64K   | —      | 8×16     | 114   | —     | —       | 64 QFP   |

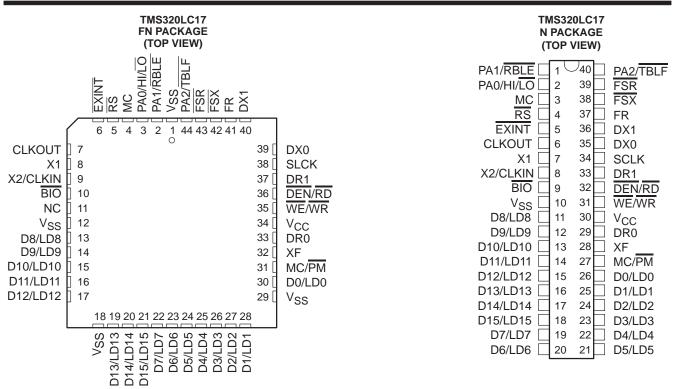

| TMS320C17                  | 256 | 4K   | _     | —     | 2      | 6×16 (5) | 200   | 40    | 44      | _        |

| TMS320E17 (5)              | 256 | —    | 4K    | —     | 2      | 6×16 (5) | 200   | 40    |         | 44 CER   |

| TMS320LC17 (5)             | 256 | 4K   | —     | —     | 2      | 6×16 (5) | 278   | 40 44 |         | _        |

| TMS320P17 (5) <sup>†</sup> | 256 |      | 4K    |       | 2      | 6×16 (5) | 200   | 40 44 |         |          |

## Table 1. TMS320C1x Device Overview

<sup>†</sup>One-time programmable (OTP) device is in a windowless plastic package and cannot be erased.

NOTES: 1. DIP = dual in-line package. PLCC = plastic-leaded chip carrier. CER = ceramic-leaded chip carrier. QFP = plastic quad flat pack. 2. Military version available.

3. Military versions planned; contact nearest TI Field Sales Office for availability.

4. On-chip 16-bit I/O, four capture inputs, and six compare outputs are available.

5. On-chip 16-bit coprocessor interface is optional by pin selection.

### description

#### TMS320C10

The 'C10 provides the core CPU used in all other 'C1x devices. Its microprocessor operates at 5 MIPS. It provides a parallel I/O of  $8 \times 16$  bits. Three versions with cycle times of 160, 200, and 280 ns are available as illustrated in Table 1. The 'C10 versions are offered in plastic 40-pin DIP or a 44-lead PLCC packages.

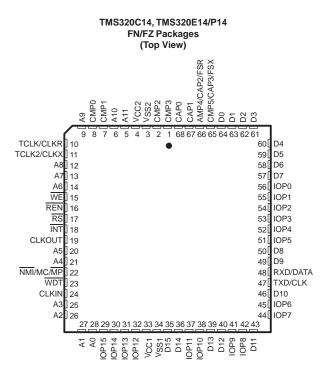

### TMS320C14/E14/P14

The 'C14/E14/P14 devices, using the 'C10 core CPU, offer expanded on-chip RAM, and ROM or EPROM ('E14/P14), 16 pins of bit selectable parallel I/O, an I/O mapped asynchronous serial port, four 16-bit timers, and external/internal interrupts. The 'C14 devices can provide for microcomputer/microprocessor operating modes. Three versions with cycle times of 160-ns are available as illustrated in Table 1. These devices are offered in 68-pin plastic PLCC or ceramic CER-QUAD packages.

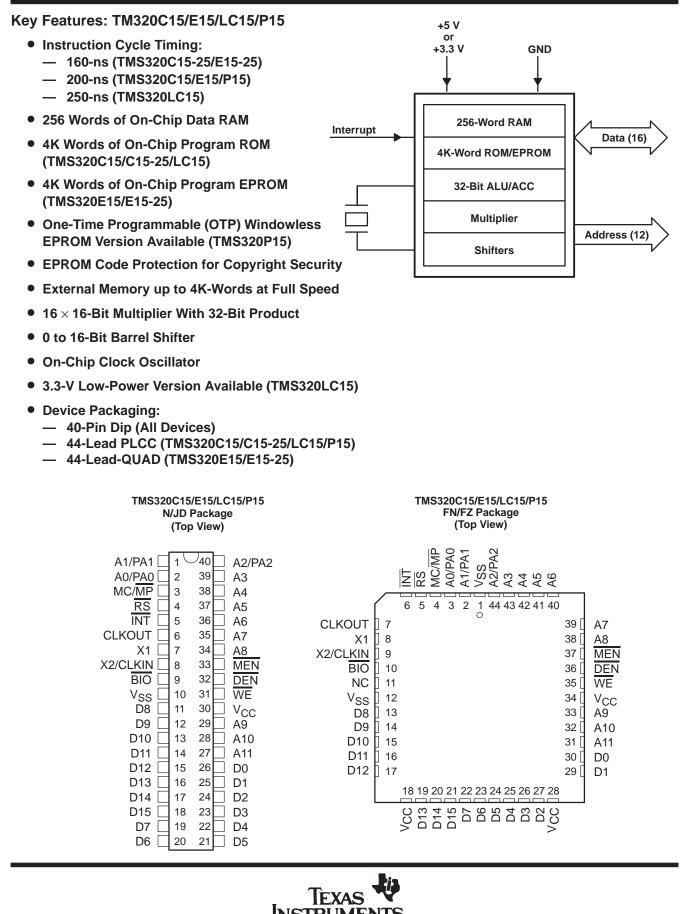

#### TMS320C15/E15/P15

The 'C15/E15/P15 devices are a version of the 'C10, offering expanded on-chip RAM, and ROM or EPROM ('E15/P15). The 'P15 is a one-time programmable (OTP), windowless EPROM version. These devices can operate in the microcomputer or microprocessor modes. Five versions are available with cycle times of 160 to 200 ns (see Table 1). These devices are offered in 40-pin DIP, 44-pin PLCC, or 44-pin ceramic packages.

#### TMS320LC15

The 'LC15 is a low-power version of the 'C15, utilizing a  $V_{DD}$  of only 3.3-V. This feature results in a 2.3: 1 power requirement reduction over the typical 5-V 'C1x device. It operates at a cycle time of 250 ns. The device is offered in 40-pin DIP or 44-lead PLCC packages.

#### TMS320C16

The 'C16 offers on-chip RAM of 256-words, an expanded program memory of 64K-words, and a fast instruction cycle time of 114 ns (8.77 MIPS). It is offered in a 64-pin quad flat-pack package.

### TMS320C17/E17/P17

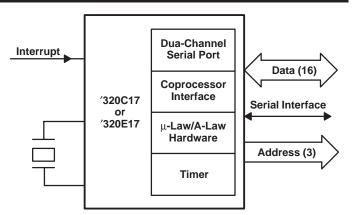

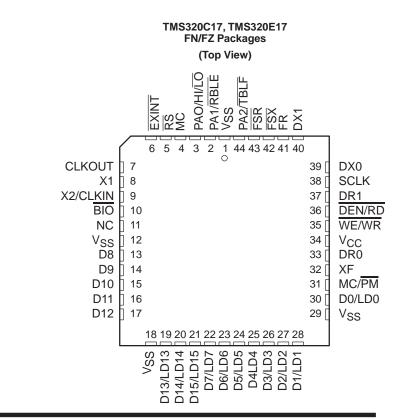

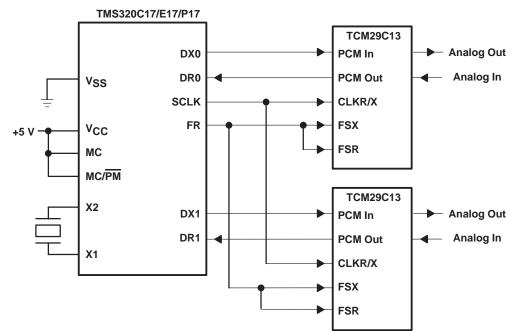

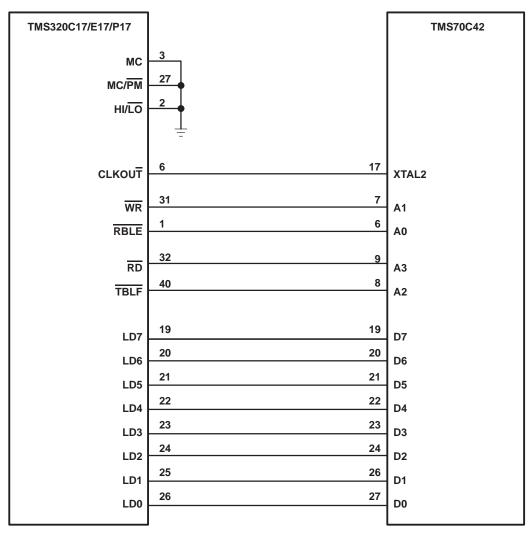

The 'C17/E17/P17 versions consist of five major functional units: the 'C15 microcomputer, a system control register, a full-duplex dual channel serial port,  $\mu$ -law/A-law companding hardware, and a coprocessor port. The dual-channel serial port is capable of full-duplex serial communication and offers direct interface to two combo-codecs. The hardware companding logic can operate in either  $\mu$ -law or A-law format with either sign-magnitude or twos complement numbers in either serial or parallel modes. The coprocessor port allows the 'C17/E17/P17 to act as a slave microcomputer or as a master to a peripheral microcomputer.

The 'P17 utilizes a one-time programmable (OTP) windowless EPROM version of the 'E17.

#### TMS320LC17

The 'LC17 is a low-power version of the 'C17, utilizing a  $V_{DD}$  of only 3.3-V. This feature results in a 2.3: 1 power requirement reduction over the typical 5-V 'C1x device. It operates at a cycle time of 278 ns.

# TMS320C1x DIGITAL SIGNAL PROCESSORS

SPRS009C-JANUARY 1987-REVISED JULY 1991

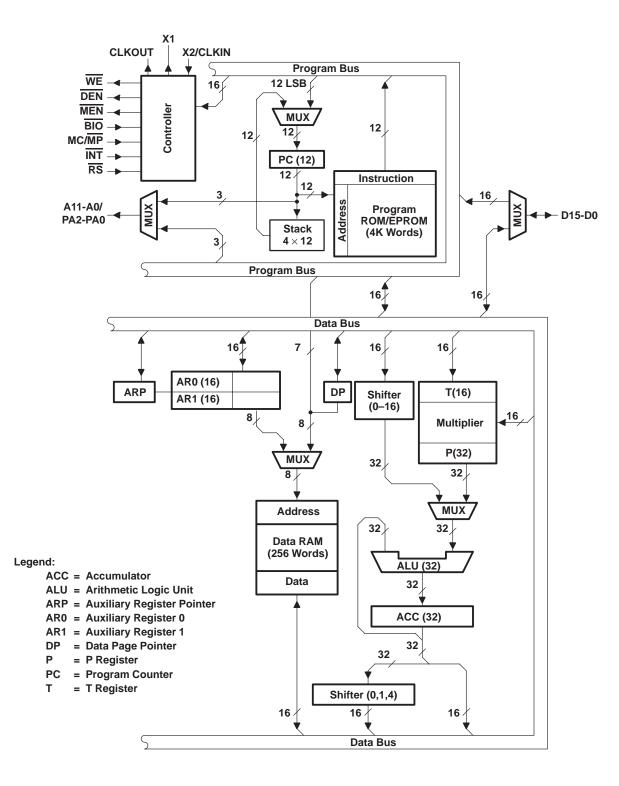

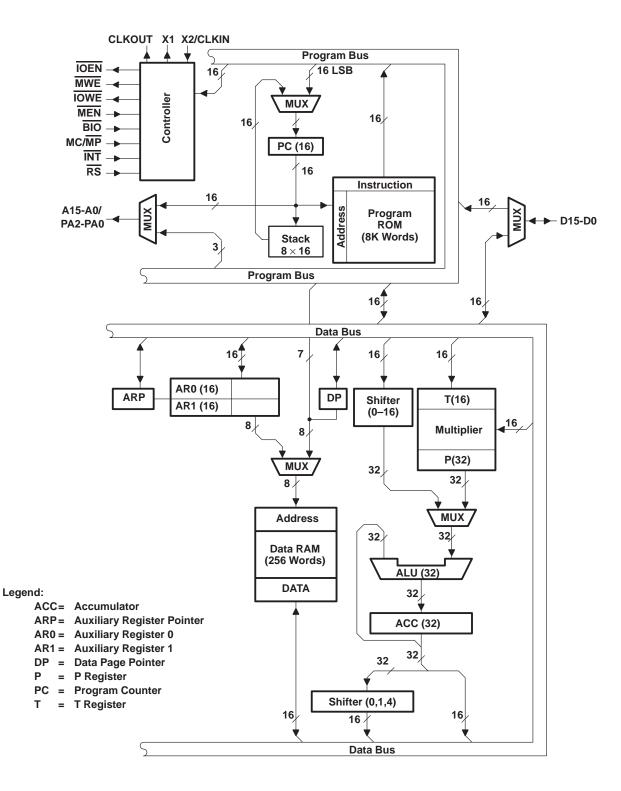

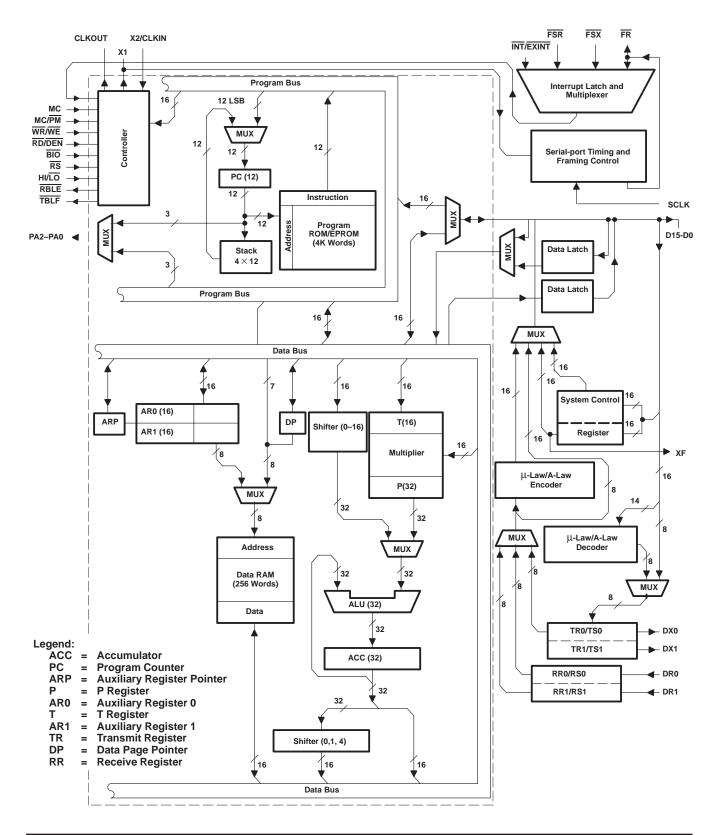

### architecture

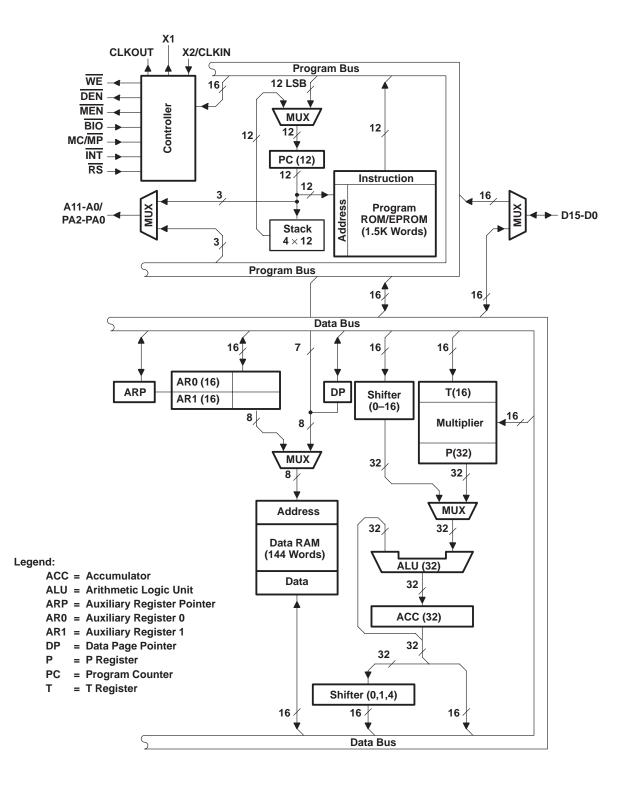

The 'C1x DSPs use a modified Harvard architecture for speed and flexibility. In a strict Harvard architecture, program and data memory lie in two separate spaces, permitting a full overlap of instruction fetch and one-cycle execution. The 'C1x DSPs modification allows transfers between program and data spaces, thereby increasing the flexibility of the device. This modification permits coefficients stored in program memory to be read into the RAM, eliminating the need for a separate coefficient ROM.

### 32-bit accumulator

All 'C1x devices contain a 32-bit ALU and accumulator for support of double-precision, twos-complement arithmetic. The ALU is a general-purpose arithmetic unit that operates on 16-bit words taken from the data RAM or derived from immediate instructions. In addition to the usual arithmetic instructions, the ALU can perform Boolean operations, providing the bit manipulation ability required of a high-speed controller. The accumulator stores the output from the ALU and is often an input to the ALU. It operates with a 32-bit word length. The accumulator is divided into a high-order word (bits 31 through 16) and a low-order word (bits 15 through 0). Instructions are provided for storing the high- and low-order accumulator words in memory.

## shifters

Two shifters are available for manipulating data. The ALU barrel shifter performs a left-shift of 0 to 16 places on data memory words loaded into the ALU. This shifter extends the high-order bit of the data word and zero-fills the low-order bits for twos-complement arithmetic. The accumulator parallel shifter performs a left-shift of 0, 1 or 4 places on the entire accumulator and places the resulting high-order accumulator bits into data RAM. Both shifters are useful for scaling and bit extraction.

#### $16 \times 16$ -bit parallel multiplier

The multiplier performs a  $16 \times 16$ -bit twos-complement multiplication with a 32-bit result in a single instruction cycle. The multiplier consists of three units: the T Register, P Register, and a multiplier array. The 16-bit T Register stores the multiplicand, and the P Register stores the 32-bit product. Multiplier values either come from the data memory or are derived immediately from the MPYK (multiply immediate) instruction word. The fast on-chip multiplier allows the device to perform fundamental operations such as convolution, correlation, and filtering.

#### data and program memory

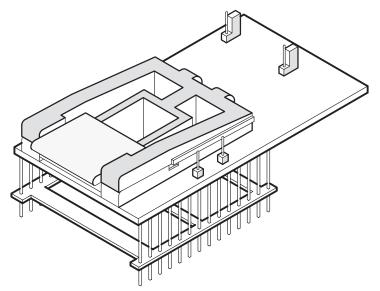

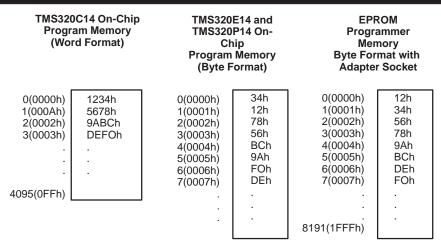

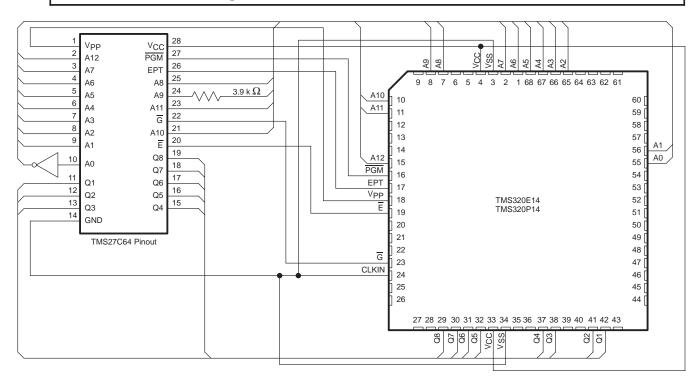

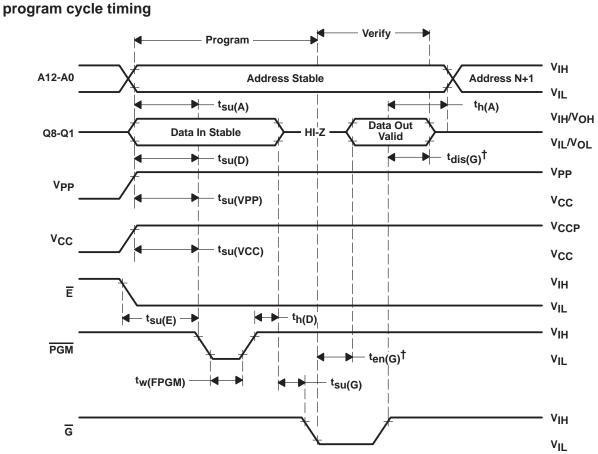

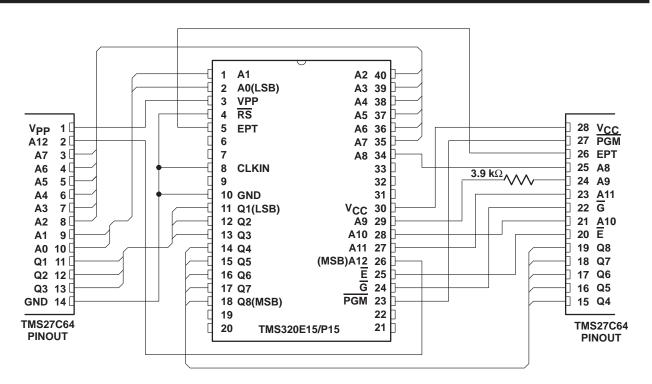

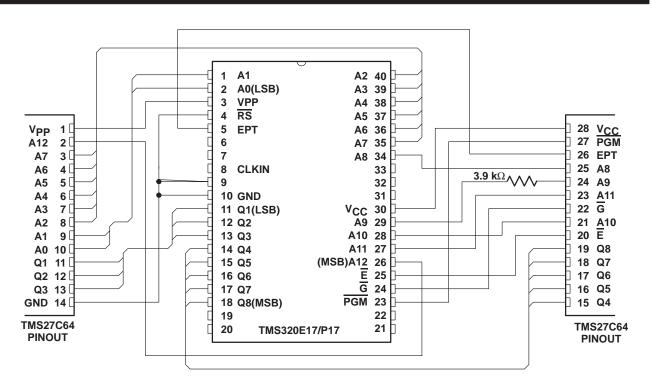

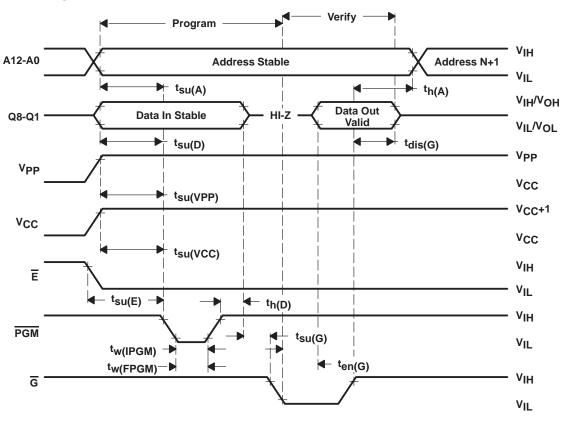

Since the 'C1x devices use a Harvard type architecture, data and program memory reside in two separate spaces. These DSP devices have 144-or 256-words of on-chip data RAM and 1.5K- to 8K-words of on-chip program ROM. On-chip program EPROM of 4K-words is provided in the 'E14/E15/E17 devices. An on-chip one-time programmable 4K-word EPROM is provided in the 'P14/P15/P17 devices. The EPROM cell utilizes standard PROM programmers and is programmed identically to a 64K CMOS EPROM (TMS27C64). (Reference Table 1.)

#### program memory expansion

All 'C1x devices except the 'C17/E17/LC17/P17 devices are capable of executing from off-chip external memory at full speed for those applications requiring external program memory space. This allows for external RAM-based systems to provide multiple functionality. The 'C17/E17/LC17/P17 devices provide no external memory expansion. (Reference Table 1.)

#### microcomputer/microprocessor operating modes

All devices except the 'x17 offer two modes of operation defined by the state of the MC/ $\overline{MP}$  pin: the microcomputer mode (MC/ $\overline{MP}$  = 1) or the microprocessor mode (MC/ $\overline{MP}$  = 0). In the microcomputer mode, on-chip ROM is mapped into the program memory space. In the microprocessor mode, all words of program memory are external.

# TMS320C1x DIGITAL SIGNAL PROCESSORS

SPRS009C-JANUARY 1987-REVISED JULY 1991

#### interrupts and subroutines

All devices except the 'C16 contain a four-level stack for saving the contents of the program counter during interrupts and subroutine calls. Because of the larger 64K program space, the 'C16's hardware stack has been increased to eight levels. Instructions are available for saving the device's complete context. PUSH and POP instructions permit a level of nesting restricted only by the amount of available RAM. The interrupts used in these devices are maskable.

#### input/output

The 16-bit parallel data bus can be utilized to perform I/O functions in two cycles. The I/O ports are addressed by the three LSBs on the address lines. In addition, a polling input for bit test and jump operations ( $\overline{BIO}$ ) and an interrupt pin ( $\overline{INT}$ ) have been incorporated for multitasking. The bit selectable I/O of the 'C14 is suitable for microcontroller applications.

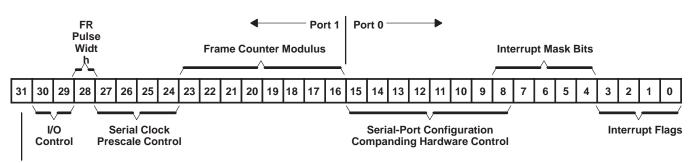

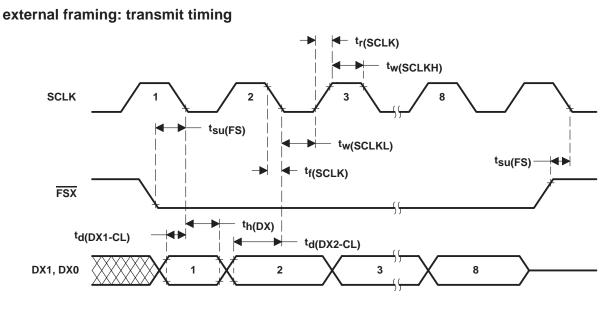

#### serial port (TMS320C17/E17)

Two of the I/O ports on the 'C17/E17 are dedicated to the serial port and companding hardware. I/O port 0 is dedicated to control register 0, which controls the serial port, interrupts, and companding hardware. I/O port 1 accesses control register 1, as well as both serial port channels, and companding hardware. The six remaining I/O ports are available for external parallel interfaces.

### serial port (TMS320C14/E14)

The 'C14/E14 devices include one I/O-mapped serial port that operates asynchronously. I/O-mapped control registers are used to configure port parameters such as inter-processor communication protocols and baud rate.

#### companding hardware (TMS320C17/E17)

On-chip hardware enables the 'C17/E17 to compand (COMpress/exPAND) data in either µ-law or A-law format. The companding logic operation is configured via the system control register. Data may be companded in either serial mode for operation on serial port data (converting between linear and logarithmic PCM) or a parallel mode for computation inside the device. The 'C17/E17 allows the hardware companding logic to operate with either sign-magnitude or twos-complement numbers.

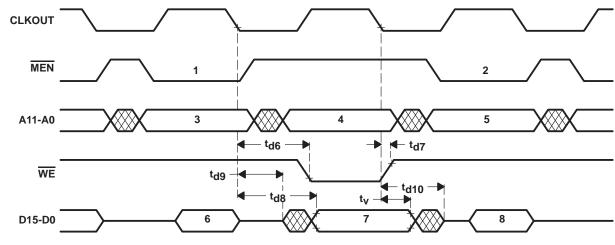

#### coprocessor port (TMS320C17/E17)

The coprocessor port on the 'C17/E17 provides a direct connection to most microcomputers and microprocessors. The port is accessed through I/O port 5 using IN and OUT instructions. The coprocessor interface allows the device to act as a peripheral (slave) microcomputer to a microprocessor, or as a master to a peripheral microcomputer. In the microcomputer mode, the 16 data lines are used for the 6 parallel 16-bit I/O ports. In the coprocessor mode, the 16-bit parallel port is reconfigured to operate as a 16-bit latched bus interface. For peripheral transfer, an 8-bit or 16-bit length of the coprocessor port can be selected.

### instruction set

A comprehensive instruction set supports both numeric-intensive operations, such as signal processing, and general-purpose operations, such as high-speed control. All of the 'C1x devices are object-code compatible and use the same 60 instructions. The instruction set consists primarily of single-cycle single-word instructions, permitting execution rates of more than six million instructions per second. Only infrequently used branch and I/O instructions are multicycle. Instructions that shift data as part of an arithmetic operation execute in a single cycle and are useful for scaling data in parallel with other operations.

### NOTE

The  $\overline{\text{BIO}}$  pin on other 'C1x devices is not available for use in the 'C14/E14/P14. An attempt to execute the BIOZ (Branch on  $\overline{\text{BIO}}$  low) instruction will result in a two cycle NOP action.

Three main addressing modes are available with the instruction set: direct, indirect, and immediate addressing.

#### direct addressing

In direct addressing, seven bits of the instruction word concatenated with the 1-bit data page pointer form the data memory address. This implements a paging scheme in which the first page contains 128 words, and the second page contains up to 128 words.

### indirect addressing

Indirect addressing forms the data memory address from the least-significant eight bits of one of the two auxiliary registers, AR0-AR1. The Auxiliary Register Pointer (ARP) selects the current auxiliary register. The auxiliary registers can be automatically incremented or decremented and the ARP changed in parallel with the execution of any indirect instruction to permit single-cycle manipulation of data tables. Indirect addressing can be used with all instructions requiring data operands, except for the immediate operand instructions.

### immediate addressing

Immediate instructions derive data from part of the instruction word rather than from the data RAM. Some useful immediate instructions are multiply immediate (MPYK), load accumulator immediate (LACK), and load auxiliary register immediate (LARK).

### instruction set summary

Table 2 lists the symbols and abbreviations used in Table 3, the instruction set summary. Table 3 contains a short description and the opcode for each 'C1x instruction. The summary is arranged according to function and alphabetized within each functional group.

| SYMBOL | MEANING                                           |

|--------|---------------------------------------------------|

| ACC    | Accumulator                                       |

| D      | Data memory address field                         |

| M      | Addressing mode bit                               |

| K      | Immediate operand field                           |

| PA     | 3-bit port address field                          |

| R      | 1-bit operand field specifying auxiliary register |

| S      | 4-bit left-shift code                             |

| X      | 3-bit accumulator left-shift field                |

Table 2. Instruction Symbols

# TMS320C1x DIGITAL SIGNAL PROCESSORS

SPRS009C-JANUARY 1987-REVISED JULY 1991

|          | ACCUM                                                           | ULATOR INS    | STRUCTION    | <u> </u> |      |     |    |    |      |      |      |     |      |   |   |           |   |   |

|----------|-----------------------------------------------------------------|---------------|--------------|----------|------|-----|----|----|------|------|------|-----|------|---|---|-----------|---|---|

|          |                                                                 | NO.           | NO.          |          |      |     |    |    |      | OP   | COE  | DE  |      |   |   |           |   |   |

| MNEMONIC | DESCRIPTION                                                     | CYCLES        | WORDS        |          |      |     |    |    | STRU |      |      |     | -    |   |   |           |   |   |

|          |                                                                 |               |              | 15       | 14   | 13  | 12 | 11 | 10   | 9    | 8    | 7   | 6    | 5 | 4 | · · · · · |   | 1 |

| ABS      | Absolute value of accumulator                                   | 1             | 1            | 0        | 1    | 1   | 1  | 1  | 1    | 1    | 1    | 1   | 0    | 0 | 0 | 1         | 0 | 0 |

| ADD      | Add to accumulator with shift                                   | 1             | 1            | 0        | 0    | 0   | 0  |    |      | — S  |      | М   |      |   |   | - U—      |   |   |

| ADDH     | Add to high-order accumulator bits                              | 1             | 1            | 0        | 1    | 1   | 0  | 0  | 0    | 0    | 0    | М   |      |   |   | - D—      |   |   |

| ADDS     | Add to accumulator with no sign extension                       | 1             | 1            | 0        | 1    | 1   | 0  | 0  | 0    | 0    | 1    | Μ   | •    |   |   | - D—      |   |   |

| AND      | AND with accumulator                                            | 1             | 1            | 0        | 1    | 1   | 1  | 1  | 0    | 0    | 1    | Μ   | •    |   |   | - D—      |   |   |

| LAC      | Load accumulator with shift                                     | 1             | 1            | 0        | 0    | 1   | 0  | •  |      | — S  | -    | Μ   | •    |   |   | - D—      |   |   |

| LACK     | Load accumulator immediate                                      | 1             | 1            | 0        | 1    | 1   | 1  | 1  | 1    | 1    | 0    |     | -    |   |   | - K—      |   |   |

| OR       | OR with accumulator                                             | 1             | 1            | 0        | 1    | 1   | 1  | 1  | 0    | 1    | 0    | Μ   | •    |   |   | - D—      |   |   |

| SACH     | Store high-order accumulator bits with shift                    | 1             | 1            | 0        | 1    | 0   | 1  | 1  | •    | — X  | •    | М   | •    |   |   | - D—      |   |   |

| SACL     | Store low-order accumulator bits                                | 1             | 1            | 0        | 1    | 0   | 1  | 0  | 0    | 0    | 0    | М   | ◀    |   |   | - D—      |   |   |

| SUB      | Subtract from accumulator with shift                            | 1             | 1            | 0        | 0    | 0   | 1  | •  |      | — s  | •    | М   | ◀    |   |   | - D—      |   |   |

| SUBC     | Conditional subtract (for divide)                               | 1             | 1            | 0        | 1    | 1   | 0  | 0  | 1    | 0    | 0    | М   | ◀    |   |   | - D—      | - |   |

| SUBH     | Subtract from high-order accumulator bits                       | 1             | 1            | 0        | 1    | 1   | 0  | 0  | 0    | 1    | 0    | М   | ◀    |   |   | - D—      |   |   |

| SUBS     | Subtract from accumulator with no sign extension                | 1             | 1            | 0        | 1    | 1   | 0  | 0  | 0    | 1    | 1    | М   | ◀    |   |   | - D—      |   |   |

| XOR      | Exclusive OR with accumulator                                   | 1             | 1            | 0        | 1    | 1   | 1  | 1  | 0    | 0    | 0    | М   | ◀    |   |   | – D—      |   |   |

| ZAC      | Zero accumulator                                                | 1             | 1            | 0        | 1    | 1   | 1  | 1  | 1    | 1    | 1    | 1   | 0    | 0 | 0 | 1         | 0 | 0 |

| ZALH     | Zero accumulator and load high-order bits                       | 1             | 1            | 0        | 1    | 1   | 0  | 0  | 1    | 0    | 1    | М   | ◀    |   |   | - D—      |   |   |

| ZALS     | Zero accumulator and load low-order bits with no sign extension | 1             | 1            | 0        | 1    | 1   | 0  | 0  | 1    | 1    | 0    | М   | ◀    |   |   | - D—      |   |   |

|          | AUXILIARY REGISTER A                                            | ND DATA PA    |              | R IN     | STRU | стю | NS |    |      |      |      |     |      |   |   |           |   |   |

|          |                                                                 |               |              |          |      |     |    |    |      | OP   | COL  | DE  |      |   |   |           |   |   |

| MNEMONIC | DESCRIPTION                                                     | NO.<br>CYCLES | NO.<br>WORDS |          |      |     |    | IN | STRU | істі | ON I | REG | ISTE | R |   |           |   |   |

|          |                                                                 |               |              | 15       | 14   | 13  | 12 | 11 | 10   | 9    | 8    | 7   | 6    | 5 | 4 | 3         | 2 | 1 |

| LAR      | Load auxiliary register                                         | 1             | 1            | 0        | 0    | 1   | 1  | 1  | 0    | 0    | R    | М   | •    | _ | _ | — D-      | _ |   |

| LARK     | Load auxiliary register immediate                               | 1             | 1            | 0        | 1    | 1   | 1  | 0  | 0    | 0    | R    | •   | -    |   |   | — K-      |   |   |

| LARP     | Load auxiliary register pointer immediate                       | 1             | 1            | 0        | 1    | 1   | 0  | 1  | 0    | 0    | 0    | 1   | 0    | 0 | 0 | 0         | 0 | 0 |

| LDP      | Load data memory page pointer                                   | 1             | 1            | 0        | 1    | 1   | 0  | 1  | 1    | 1    | 1    | М   | •    |   |   | — D-      |   |   |

| LDPK     | Load data memory page pointer immediate                         | 1             | 1            | 0        | 1    | 1   | 0  | 1  | 1    | 1    | 0    | 0   | 0    | 0 | 0 | 0         | 0 | 0 |

| MAR      | Modify auxiliary register and pointer                           | 1             | 1            | 0        | 1    | 1   | 0  | 1  | 0    | 0    | 0    | М   | 4    |   |   | — D-      |   |   |

| SAR      | Store auxiliary register                                        | 1             | 1            | 0        | 0    | 1   | 1  | 0  | 0    | 0    | R    | м   |      |   |   | — D-      |   |   |

# Table 3. TMS320C1x Instruction Set Summary

|          | BRA                                                                        | NCH INSTR     | UCTIONS      |      |       |     |    |    |      |      |    |     |                  |         |     |      |        |          |   |

|----------|----------------------------------------------------------------------------|---------------|--------------|------|-------|-----|----|----|------|------|----|-----|------------------|---------|-----|------|--------|----------|---|

|          |                                                                            |               |              |      |       |     |    |    |      | OP   | со | DE  |                  |         |     |      |        |          |   |

| MNEMONIC | DESCRIPTION                                                                | NO.<br>CYCLES | NO.<br>WORDS |      |       |     |    | IN | STRI | JCTI | ON | REC | SIST             | ER      |     |      |        |          |   |

|          |                                                                            |               | noneo        | 15   | 14    | 13  | 12 | 11 | 10   | 9    | 8  | 7   | 6                | 5       | 4   | 3    | 2      | 1        | ( |

| _        |                                                                            |               |              | 1    | 1     | 1   | 1  | 1  | 0    | 0    | 1  | 0   | 0                | 0       | 0   | 0    | 0      | 0        | ( |

| В        | Branch unconditionally                                                     | 2             | 2            | 0    | 0     | 0   | 0  | -  |      |      | _  | BRA | NCH              | I AD    | DRE | SS - | —      |          | - |

| BANZ     | Branch on auxiliary register not zero                                      | 2             | 2            | 1    | 1     | 1   | 1  | 0  | 1    | 0    | 0  | 0   | 0                | 0       | 0   | 0    | 0      | 0        | ( |

| DANZ     |                                                                            |               | 2            | 0    | 0     | 0   | 0  | 4  |      |      |    | BRA | NCH              | I AD    | DRE | SS - |        |          | - |

| BGEZ     |                                                                            |               | 2            | 1    | 1     | 1   | 1  | 1  | 1    | 0    | 1  | 0   | 0                | 0       | 0   | 0    | 0      | 0        |   |

| BGEZ     | Branch if accumulator $\geq 0$                                             | 2             | 2            | 0    | 0     | 0   | 0  | -  |      |      | _  | BRA | NCH              | I AD    | DRE | SS - |        |          | - |

| 007      | Describ if a summittee a                                                   |               |              | 1    | 1     | 1   | 1  | 1  | 1    | 0    | 0  | 0   | 0                | 0       | 0   | 0    | 0      | 0        |   |

| BGZ      | Branch if accumulator > 0                                                  | 2             | 2            | 0    | 0     | 0   | 0  | -  |      |      |    | BRA | NCH              | I AD    | DRE | SS - |        |          | - |

| BIOZ     | Branch on $\overline{BIO} = 0^{\dagger}$                                   | 2             | 2            | 1    | 1     | 1   | 1  | 0  | 1    | 1    | 0  | 0   | 0                | 0       | 0   | 0    | 0      | 0        |   |

| BIOZ     |                                                                            | 2             | 2            | 0    | 0     | 0   | 0  | -  |      |      |    | BRA | NCH              | I AD    | DRE | SS - |        |          | - |

| DI 57    |                                                                            |               |              | 1    | 1     | 1   | 1  | 1  | 0    | 1    | 1  | 0   | 0                | 0       | 0   | 0    | 0      | 0        |   |

| BLEZ     | Branch if accumulator $\leq 0$                                             | 2             | 2            | 0    | 0     | 0   | 0  | •  |      |      |    | BRA | NCH              | I AD    | DRE | ss - |        |          | - |

| BLZ      | Branch if accumulator < 0                                                  | 2             | 2            | 1    | 1     | 1   | 1  | 1  | 0    | 1    | 0  | 0   | 0                | 0       | 0   | 0    | 0      | 0        |   |

| DLL      |                                                                            | -             | 2            | 0    | 0     | 0   | 0  | •  |      |      | _  | BRA | NCH              | I AD    | DRE | SS - |        |          | - |

| BNZ      | Branch if accumulator ≠ 0                                                  | 2             | 2            | 1    | 1     | 1   | 1  | 1  | 1    | 1    | 0  | 0   | 0                | 0       | 0   | 0    | 0      | 0        |   |

| DINZ     |                                                                            |               | 2            | 0    | 0     | 0   | 0  | •  |      |      |    | BRA | NCH              | I AD    | DRE | SS - |        |          | - |

| BV       | Branch on overflow                                                         | 2             | 2            | 1    | 1     | 1   | 1  | 0  | 1    | 0    | 1  | 0   | 0                | 0       | 0   | 0    | 0      | 0        |   |

| 5.       |                                                                            | -             | -            | 0    | 0     | 0   | 0  | -  |      |      |    | BRA | NCH              | I AD    | DRE | SS - |        |          | - |

| BZ       | Branch if accumulator = 0                                                  | 2             | 2            | 1    | 1     | 1   | 1  | 1  | 1    | 1    | 1  | 0   | 0                | 0       | 0   | 0    | 0      | 0        |   |

|          |                                                                            |               | _            | 0    | 0     | 0   | 0  | -  |      |      | _  | BRA | NCH              | I AD    | DRE | SS - |        |          | - |

| CALA     | Call subroutine from accumulator                                           | 2             | 1            | 0    | 1     | 1   | 1  | 1  | 1    | 1    | 1  | 1   | 0                | 0       | 0   | 1    | 1      | 0        |   |

| CALL     | Call subroutine immediately                                                | 2             | 2            | 1    | 1     | 1   | 1  | 1  | 0    | 0    | 0  | 0   | 0                | 0       | 0   | 0    | 0      | 0        |   |

|          |                                                                            |               |              | 0    | 0     | 0   | 0  | •  |      |      |    |     | NCH              |         |     |      |        |          | - |

| RET      | Return from subroutine or interrupt routine                                | 2             | 1            | 0    | 1     | 1   | 1  | 1  | 1    | 1    | 1  | 1   | 0                | 0       | 0   | 1    | 1      | 0        | _ |

|          | T REGISTER, P REGI                                                         | STER, AND     | MULTIPLY I   | NSTF | RUCTI | ONS |    |    |      |      |    |     |                  |         |     |      | _      | _        |   |

|          | DESCRIPTION                                                                | NO.           | NO.          |      |       |     |    |    | OTD  |      | 00 |     | NOT              |         |     |      |        |          |   |

| MNEMONIC | DESCRIPTION                                                                | CYCLES        | WORDS        | 15   | 14    | 13  | 12 | 11 | STRI | 9    | 8  |     |                  | =R<br>5 | 4   | 2    | 2      | 1        |   |

| APAC     | Add P register to accumulator                                              | 1             | 1            | 0    | 14    | 13  | 12 | 1  | 1    | 1    | 1  | 1   | 0                | 0       | 4   | 1    | -<br>1 | 1        | - |

| LT       | Load T Register                                                            | 1             | 1            | 0    | 1     | 1   | 0  | 1  | 0    | 1    | 0  | M   |                  | 5       | 5   | - D- |        | <u> </u> | _ |

| LTA      | LTA combines LT and APAC into one instruction                              | 1             | 1            | 0    | 1     | 1   | 0  | 1  | 1    | 0    | 0  | M   | •                |         |     | — D- |        |          | _ |

| LTD      | LTD combines LT, APAC, and DMOV into one instruction                       | 1             | 1            | 0    | 1     | 1   | 0  | 1  | 0    | 1    | 1  | M   | 4                |         |     | — D- |        |          | _ |

| MPY      | Multiply with T register, store product in P register                      | 1             | 1            | 0    | 1     | 1   | 0  | 1  | 1    | 0    | 1  | M   | 4                |         |     | — D- |        |          | - |

| MPYK     | Multiply T register with immediate operand; store product<br>in P register | 1             | 1            | 1    | 0     | 0   | •  |    |      | -    |    |     | <b>ч</b><br>— К- |         |     |      |        |          |   |

| PAC      | Load accumulator from P register                                           | 1             | 1            | 0    | 1     | 1   | 1  | 1  | 1    | 1    | 1  | 1   | 0                | 0       | 0   | 1    | 1      | 1        |   |

| SPAC     | Subtract P register from accumulator                                       | 1             | 1            | 0    | 1     | 1   | 1  | 1  | 1    | 1    |    | 1   | 0                | 0       |     |      | 0      | 0        |   |

# Table 3. TMS320C1x Instruction Set Summary (continued)

<sup>†</sup>This instruction is a NOP on the '320C14/E14/P14.

# TMS320C1x DIGITAL SIGNAL PROCESSORS

SPRS009C-JANUARY 1987-REVISED JULY 1991

| Table 3. TMS320C1x Instruction Set Summary ( | (concluded) |

|----------------------------------------------|-------------|

|----------------------------------------------|-------------|

|          | CON                                                             | TROL INSTR    | UCTIONS      |                                |    |    |    |    |      |      |      |     |      |   |   |      |   |   |   |

|----------|-----------------------------------------------------------------|---------------|--------------|--------------------------------|----|----|----|----|------|------|------|-----|------|---|---|------|---|---|---|

| MNEMONIC | DESCRIPTION                                                     | NO.<br>CYCLES | NO.<br>WORDS | OPCODE<br>INSTRUCTION REGISTER |    |    |    |    |      |      |      |     |      |   |   |      |   |   |   |

|          |                                                                 |               |              | 15                             | 14 | 13 | 12 | 11 | 10   | 9    | 8    | 7   | 6    | 5 | 4 | 3    | 2 | 1 | 0 |

| DINT     | Disable interrupt                                               | 1             | 1            | 0                              | 1  | 1  | 1  | 1  | 1    | 1    | 1    | 1   | 0    | 0 | 0 | 0    | 0 | 0 | 1 |

| EINT     | Enable interrupt                                                | 1             | 1            | 0                              | 1  | 1  | 1  | 1  | 1    | 1    | 1    | 1   | 0    | 0 | 0 | 0    | 0 | 1 | 0 |

| LST      | Load status register                                            | 1             | 1            | 0                              | 1  | 1  | 1  | 1  | 0    | 1    | 1    | М   | ◀    |   |   | – D- |   |   | • |

| NOP      | No operation                                                    | 1             | 1            | 0                              | 1  | 1  | 1  | 1  | 1    | 1    | 1    | 1   | 0    | 0 | 0 | 0    | 0 | 0 | 0 |

| POP      | POP stack to accumulator                                        | 2             | 1            | 0                              | 1  | 1  | 1  | 1  | 1    | 1    | 1    | 1   | 0    | 0 | 1 | 1    | 1 | 0 | 1 |

| PUSH     | PUSH stack from accumulator                                     | 2             | 1            | 0                              | 1  | 1  | 1  | 1  | 1    | 1    | 1    | 1   | 0    | 0 | 1 | 1    | 1 | 0 | 0 |

| ROVM     | Reset overflow mode                                             | 1             | 1            | 0                              | 1  | 1  | 1  | 1  | 1    | 1    | 1    | 1   | 0    | 0 | 0 | 1    | 0 | 1 | 0 |

| SOVM     | Set overflow mode                                               | 1             | 1            | 0                              | 1  | 1  | 1  | 1  | 1    | 1    | 1    | 1   | 0    | 0 | 0 | 1    | 0 | 1 | 1 |

| SST      | Store status register                                           | 1             | 1            | 0                              | 1  | 1  | 1  | 1  | 1    | 0    | 0    | М   | ◀    |   |   | – D- |   |   | • |

|          | I/O AND D                                                       | ATA MEMOR     | Y OPERATI    | ONS                            |    |    |    |    |      |      |      |     |      |   |   |      |   | _ | _ |

|          |                                                                 |               |              |                                |    |    |    |    |      | OP   | COD  | ЭE  |      |   |   |      |   | _ | _ |

| MNEMONIC | DESCRIPTION                                                     | NO.<br>CYCLES | NO.<br>WORDS |                                |    |    |    | IN | STRU | јсті | ON I | REG | ISTE | R |   |      |   |   |   |

|          |                                                                 |               |              | 15                             | 14 | 13 | 12 | 11 | 10   | 9    | 8    | 7   | 6    | 5 | 4 | 3    | 2 | 1 | 0 |

| DMOV     | Copy contents of data memory location into next higher location | 1             | 1            | 0                              | 1  | 1  | 0  | 1  | 0    | 0    | 1    | Μ   | -    |   |   | – D- |   | _ | ► |

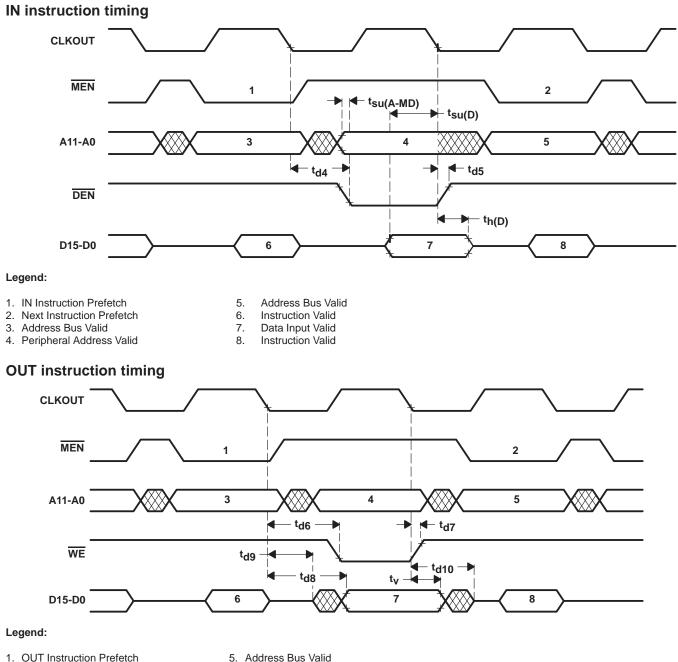

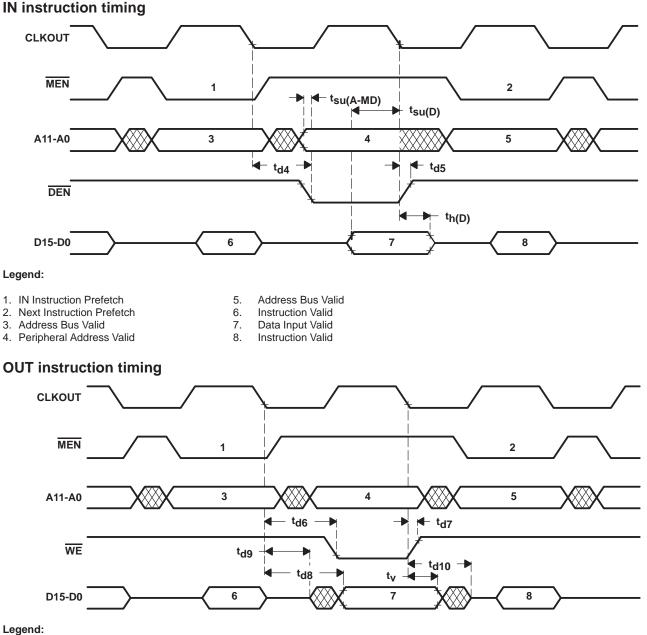

| IN       | Input data from port                                            | 2             | 1            | 0                              | 1  | 0  | 0  | 0  | -    | PA-  | •    | М   | ◀    |   |   | – D- |   |   | • |

| OUT      | Output data to port                                             | 2             | 1            | 0                              | 1  | 0  | 0  | 1  | -    | PA-  |      | М   | ◀    |   |   | – D- |   |   | ► |

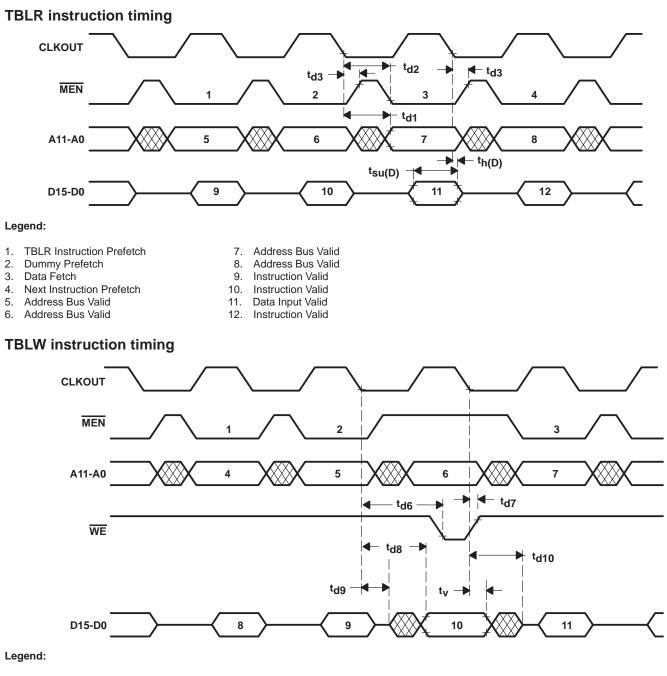

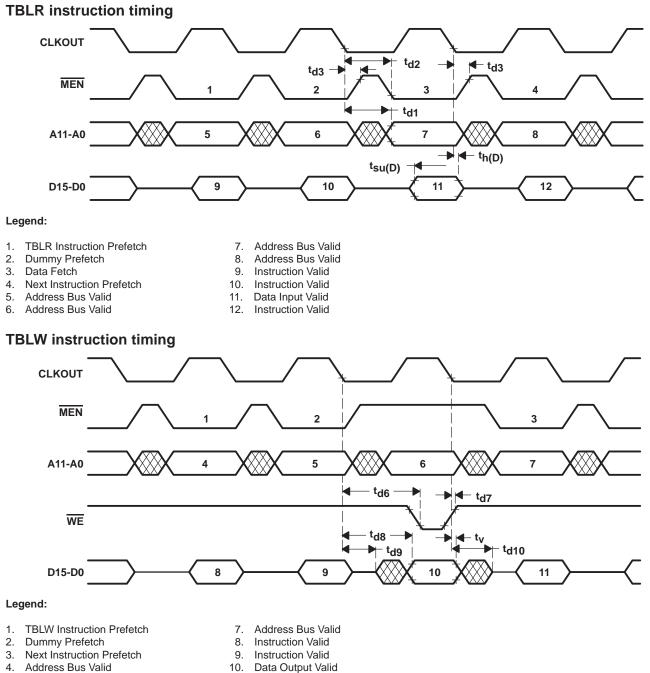

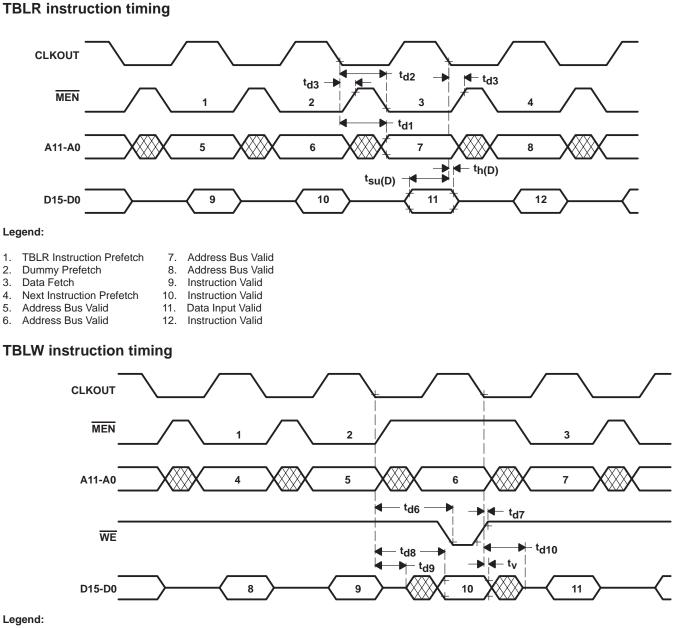

| TBLR     | Table read from program memory to data RAM                      | 3             | 1            | 0                              | 1  | 1  | 0  | 0  | 1    | 1    | 1    | М   | ◀    |   |   | – D- |   |   | • |

| TBLW     | Table write from data RAM to program memory                     | 3             | 1            | 0                              | 1  | 1  | 1  | 1  | 1    | 0    | 1    | М   | -    |   |   | – D- |   |   | • |

SPRS009C-JANUARY 1987-REVISED JULY 1991

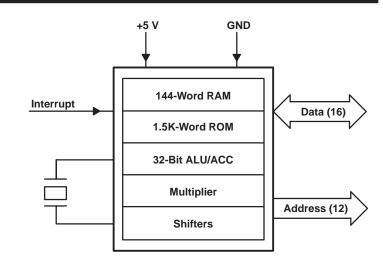

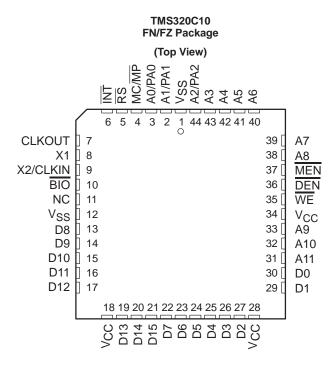

- Instruction Cycle Timing

- 160-ns (TMS320C10-25)

- 200-ns (TMS32010)

- 280-ns (TMS320C10-14)

- 144 Words of On-Chip Data RAM

- 1.5K Words On-Chip Program ROM

- External Memory Expansion up to 4K Words at Full Speed

- 16 × 16-Bit Multiplier With 32-Bit Product

- 0 to 16-Bit Barrel Shifter

- On-Chip Clock Oscillator

- Device Packaging:

- 40-Pin DIP

- 44-Lead PLCC

- Single 5-V Supply

- Operating Free-Air Temperature Range ... 0°C to 70°C

SPRS009C-JANUARY 1987-REVISED JULY 1991

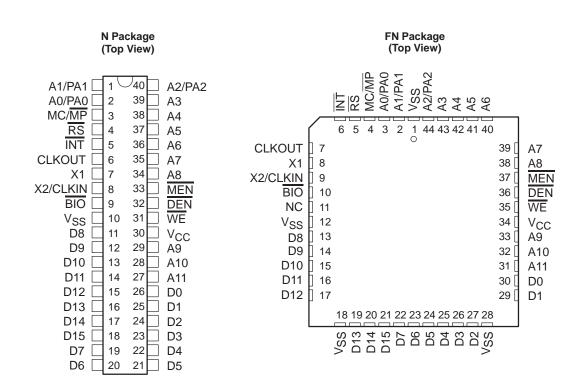

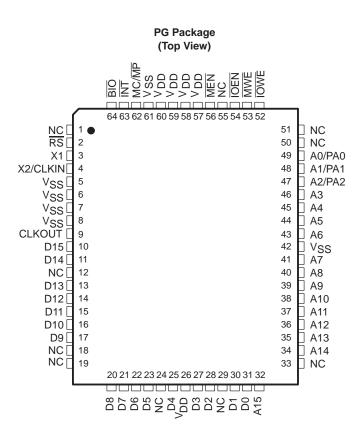

| NAME                  | <i>ı</i> /o† | DEFINITION                                                                                |

|-----------------------|--------------|-------------------------------------------------------------------------------------------|

| A11-A0/PA2-PA0        | 0            | External address bus. I/O port address multiplexed over PA2-PA0.                          |

| BIO                   | I            | External polling input                                                                    |

| CLKOUT                | 0            | System clock output, 1/4 crystal/CLKIN frequency                                          |

| D15-D0                | I/O          | 16-bit parallel data bus                                                                  |

| DEN                   | 0            | Data enable for device input data on D15-D0                                               |

| INT                   | I            | External interrupt input                                                                  |

| MC/MP                 | I            | Memory mode select pin. High selects microcomputer mode. Low selects microprocessor mode. |

| MEN                   | 0            | Memory enable indicates that D15-D0 will accept external memory instruction.              |

| NC                    | 0            | No connection                                                                             |

| RS                    | I            | Reset for initializing the device                                                         |

| VCC                   | I            | + 5 V supply                                                                              |

| V <sub>SS</sub><br>WE | I            | Ground                                                                                    |

| WE                    | 0            | Write enable for device output data on D15-D0                                             |

| X1                    | 0            | Crystal output for internal oscillator                                                    |

| X2/CLKIN              | Ι            | Crystal input internal oscillator or external system clock input                          |

# **TERMINAL FUNCTIONS**

† Input/Output/High-impedance state.

SPRS009C-JANUARY 1987-REVISED JULY 1991

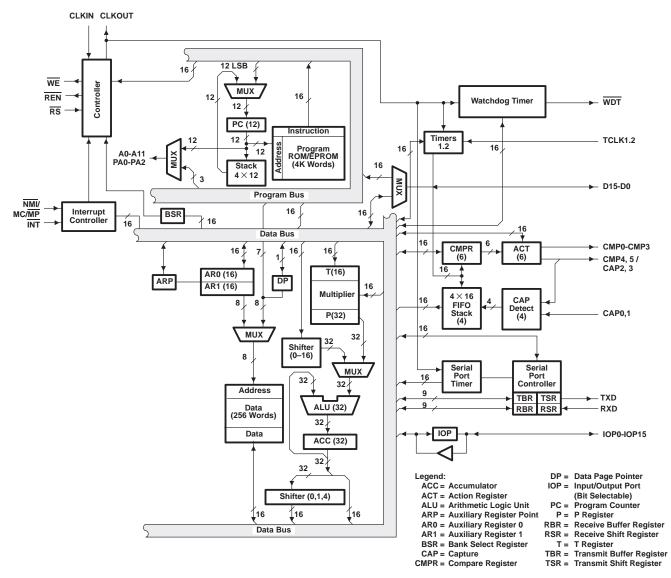

## functional block diagram

SPRS009C-JANUARY 1987-REVISED JULY 1991

#### electrical specifications

This section contains the electrical specifications for all speed versions of the 'C10 Digital Signal Processors, including test parameter measurement information.

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range V <sub>CC</sub> (see Note 6) | -0.3 V to 7 V  |

|---------------------------------------------------|----------------|

| Input voltage range                               | -0.3 V to 7 V  |

| Output voltage range                              | -0.3 V to 7 V  |

| Continuous power dissipation                      | 0.5 mW         |

| Operating free-air temperature: L suffix          | . 0°C to 70°C  |

| A suffix –                                        | - 40°C to 85°C |

| Storage temperature                               | 5 °C to 150 °C |

† Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTE 6: All voltage values are with respect to V<sub>SS</sub>.

## recommended operating conditions

|       |                                        |                      | MIN  | NOM | MAX  | UNIT |

|-------|----------------------------------------|----------------------|------|-----|------|------|

| VCC   | Supply voltage                         |                      | 4.5  | 5   | 5.25 | V    |

| VSS   | Supply voltage                         |                      |      | 0   |      | V    |

| Maria | High-level input voltage               | CLKIN                | 3    |     |      | V    |

| VIH   | High-level liput voltage               | All remaining inputs | 2    |     |      | V    |

|       | Low-level input voltage                | MC/MP                |      |     | 0.6  | V    |

| VIL   | Low-level input voltage                | All remaining inputs |      |     | 0.8  | V    |

| ЮН    | High-level output current, all outputs |                      |      |     | -300 | μA   |

| IOL   | Low-level output current               |                      |      |     | 2    | mA   |

| -     |                                        | L suffix             | 0    |     | 70   | °C   |

| TA    | Operating free-air temperature         | A suffix             | - 40 |     | 85   | °C   |

SPRS009C-JANUARY 1987-REVISED JULY 1991

# electrical characteristics over specified temperature range (unless otherwise noted)

|     | PARAMETER                   |            | TEST C                          | ONDITIONS               | MIN                                | TYP† | MAX | UNIT |

|-----|-----------------------------|------------|---------------------------------|-------------------------|------------------------------------|------|-----|------|

| ∨он | High-level output voltage   |            | I <sub>OH</sub> = MAX           |                         | 2.4                                | 3    |     | V    |

| VOH | Tigh-level output voltage   |            | I <sub>OH</sub> = 20 μA (see No | te 7)                   | V <sub>CC</sub> - 0.4 <sup>‡</sup> |      |     | V    |

| VOL | Low-level output voltage    |            | I <sub>OL</sub> = MAX           |                         |                                    | 0.3  | 0.5 | V    |

|     |                             |            | V <sub>CC</sub> = MAX           | V <sub>O</sub> = 2.4 V  |                                    |      | 20  |      |

| loz | Off-state output current    |            |                                 | V <sub>O</sub> = 0.4 V  |                                    |      | -20 | μA   |

|     | lanut aumant                |            |                                 | All inputs except CLKIN |                                    |      | ±20 | μA   |

| 1   | Input current               |            | $V_{CC} = V_{SS}$ to $V_{CC}$   | CLKIN                   |                                    |      | ±50 | μΛ   |

| C.  | Input consoitonco           | Data bus   |                                 |                         |                                    | 25‡  |     | pF   |

| Ci  | Input capacitance           | All others | f = 1 MHz, all other p          |                         |                                    | 15‡  |     | рг   |

| Co  | O data da serie si la serie | Data bus   | r = r w r z, an other p         |                         |                                    | 25‡  |     | pF   |

| 00  | Output capacitance          | All others |                                 |                         |                                    | 10‡  |     | рг   |

<sup>†</sup> All typical values are at  $V_{CC}$  = 5 V,  $T_A$  = 25°C. <sup>‡</sup> Values derived from characterization data and not tested.

NOTE 7: This voltage specification is included for interface to HC logic. However, note that all of the other timing parameters defined in this data sheet are specified for TTL logic levels and will differ for HC logic levels.

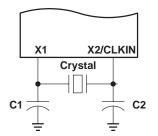

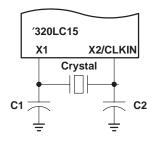

# **INTERNAL CLOCK OPTION**

**Figure 1. Internal Clock Option**

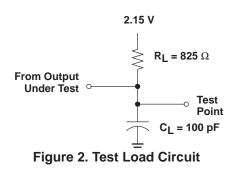

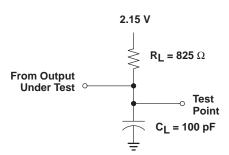

## PARAMETER MEASUREMENT INFORMATION

# TMS320C10, TMS320C10-25 DIGITAL SIGNAL PROCESSORS

SPRS009C-JANUARY 1987-REVISED JULY 1991

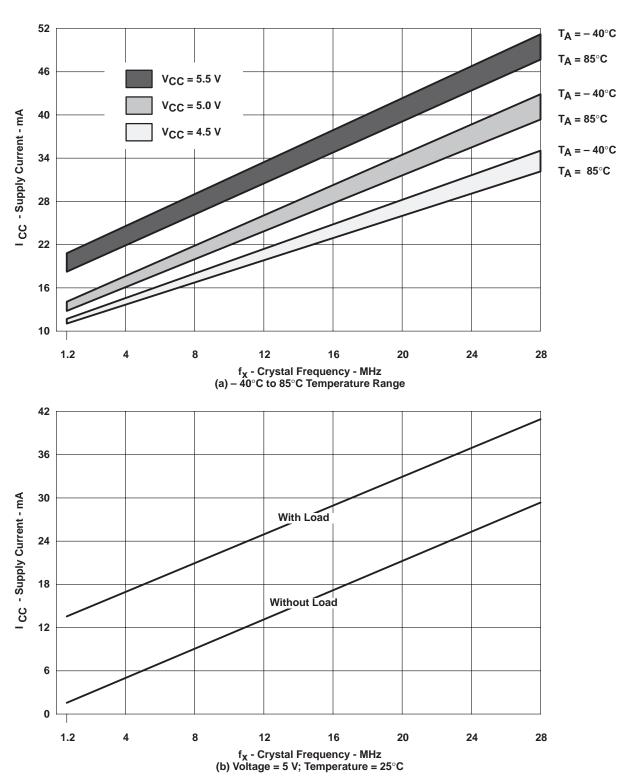

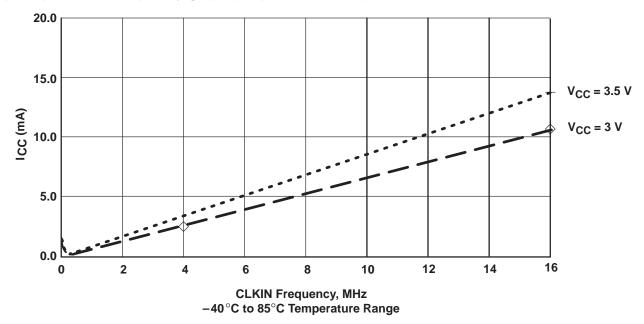

### electrical characteristics over specified temperature range (unless otherwise noted)

|      | PARAMET        | ER           | TEST CONDITIONS<br>(SEE FIGURE 2)                                      | MIN | түр† | MAX | UNIT |

|------|----------------|--------------|------------------------------------------------------------------------|-----|------|-----|------|

| Icc‡ | Supply current | TMS320C10    | f = 20.5 MHz, V <sub>CC</sub> = 5.5 V, T <sub>A</sub> = – 40°C to 85°C |     | 33   | 55  |      |

| 100+ | Supply current | TMS320C10-25 | f = 25.6 MHz, $V_{CC}$ = 5.5 V T <sub>A</sub> = - 0°C to 70°C          |     | 40   | 65  | mA   |

<sup>†</sup> All typical values are at  $T_A = 70^{\circ}$ C and are used for thermal resistance calculations.

<sup>‡</sup>I<sub>CC</sub> characteristics are inversely proportional to temperature. For I<sub>CC</sub> dependence on temperature, frequency, and loading.

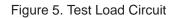

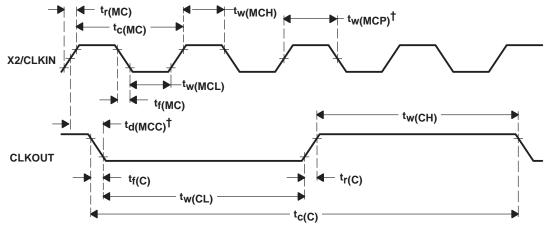

# **CLOCK CHARACTERISTICS AND TIMING**

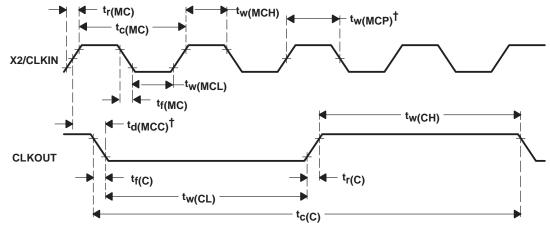

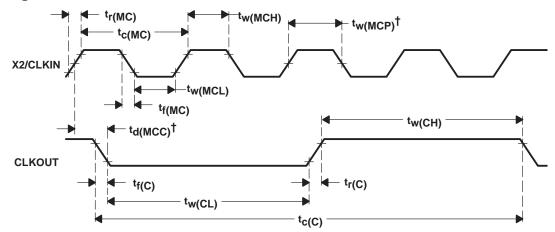

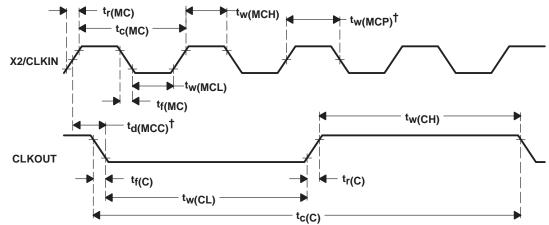

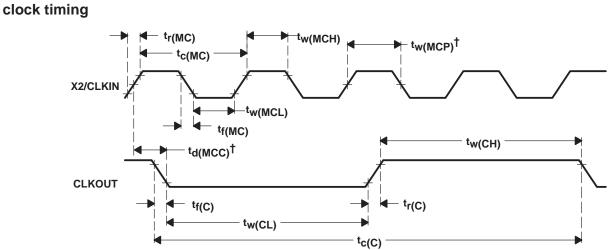

The 'C10/C10-25 can use either its internal oscillator or an external frequency source for a clock.

### internal clock option

The internal oscillator is enabled by connecting a crystal across X1 and X2/CLKIN (see Figure 1). The frequency of CLKOUT is one-fourth the crystal fundamental frequency. The crystal should be fundamental mode, and parallel resonant, with an effective series resistance of 30 ohms, a power dissipation of 1 mW, and should be specified at a load capacitance of 20 pF.

| PARAMET               | ER           | TEST CONDITIONS                       | MIN | NOM | MAX  | UNIT   |

|-----------------------|--------------|---------------------------------------|-----|-----|------|--------|

| Crystal frequency, fx | TMS320C10    | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | 6.7 |     | 20.5 | MHz    |

|                       | TMS320C10-25 | $T_A = 0^{\circ}C$ to $70^{\circ}C$   | 6.7 |     | 25.6 | 101112 |

| C1, C2                |              | $T_A = -40^{\circ}C$ to $85^{\circ}C$ |     | 10  |      | pF     |

#### external clock option

An external frequency source can be used by injecting the frequency directly into X2/CLKIN with X1 left unconnected. The external frequency injected must conform to the specifications listed in the table below.

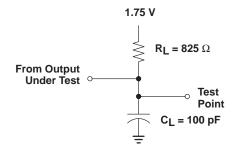

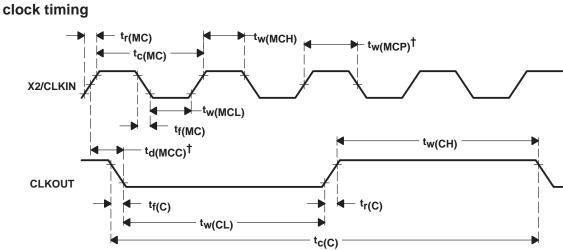

#### switching characteristics over recommended operating conditions

|                    | PARAMETER                                                          | TEST CONDITIONS                                    | Т      | MS320C10 |     | TM     | S320C10-2 | 25  | UNIT |

|--------------------|--------------------------------------------------------------------|----------------------------------------------------|--------|----------|-----|--------|-----------|-----|------|

|                    | FARAMETER                                                          | TEST CONDITIONS                                    | MIN    | NOM      | MAX | MIN    | NOM       | MAX | UNIT |

| <sup>t</sup> c(C)  | CLKOUT cycle time§                                                 |                                                    | 195.12 | 200      |     | 156.25 | 160       |     | ns   |

| tr(C)              | CLKOUT rise time                                                   | <b>D</b>                                           |        | 10¶      |     |        | 10¶       |     | ns   |

| <sup>t</sup> f(C)  | CLKOUT fall time                                                   | R <sub>L</sub> = 825 Ω,<br>C <sub>L</sub> = 100 pF |        | 8¶       |     |        | 8¶        |     | ns   |

| <sup>t</sup> w(CL) | Pulse duration, CLKOUT low                                         | (see Figure 2)                                     |        | 92¶      |     |        | 72¶       |     | ns   |

| <sup>t</sup> w(CH) | Pulse duration, CLKOUT high                                        |                                                    |        | 90¶      |     |        | 70¶       |     | ns   |

| td(MCC)            | Delay time, <code>CLKIN</code> to <code>CLKOUT</code> $\downarrow$ |                                                    | 25¶    |          | 60¶ | 25     |           | 50¶ | ns   |

$t_{c(C)}$  is the cycle time of CLKOUT, i.e.,  $4t_{c(MC)}$  (4 times CLKIN cycle time if an external oscillator is used). I Values derived from characterization data and not tested.

## timing requirements over recommended operating conditions

|                     |                                   | ٦        | MS320C1 | 0                                | TN                   | IS320C10-            | 25                               | UNIT |

|---------------------|-----------------------------------|----------|---------|----------------------------------|----------------------|----------------------|----------------------------------|------|

|                     |                                   | MIN      | NOM     | MAX                              | MIN                  | NOM                  | MAX                              | UNIT |

| <sup>t</sup> c(MC)  | Master clock cycle time           | 48.78    | 50      | 150                              | 39.06                | 40                   | 150¶                             | ns   |

| <sup>t</sup> r(MC)  | Rise time, master clock input     |          | 5¶      | 10¶                              |                      | 5¶                   | 10¶                              | ns   |

| <sup>t</sup> f(MC)  | Fall time, master clock input     |          | 5¶      | 10¶                              |                      | 5¶                   | 10¶                              | ns   |

| <sup>t</sup> w(MCP) | Pulse duration, master clock      | 0.4tc(MC | c)¶ 0.  | <sup>6t</sup> c(MC) <sup>¶</sup> | 0.45t <sub>c(M</sub> | C) <sup>¶</sup> 0.55 | <sup>it</sup> c(MC) <sup>¶</sup> | ns   |

| <sup>t</sup> w(MCL) | Pulse duration, master clock low  |          | 20¶     |                                  |                      | 15¶                  |                                  | ns   |

| <sup>t</sup> w(MCH) | Pulse duration, master clock high |          | 20¶     |                                  |                      | 15¶                  |                                  | ns   |

$\P$  Values derived from characterization data and not tested.

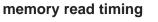

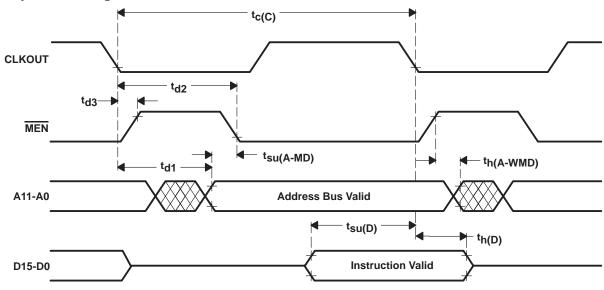

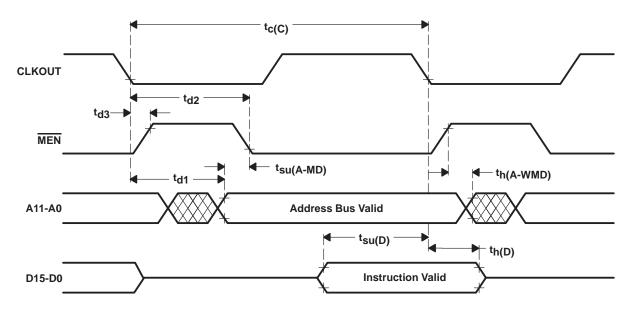

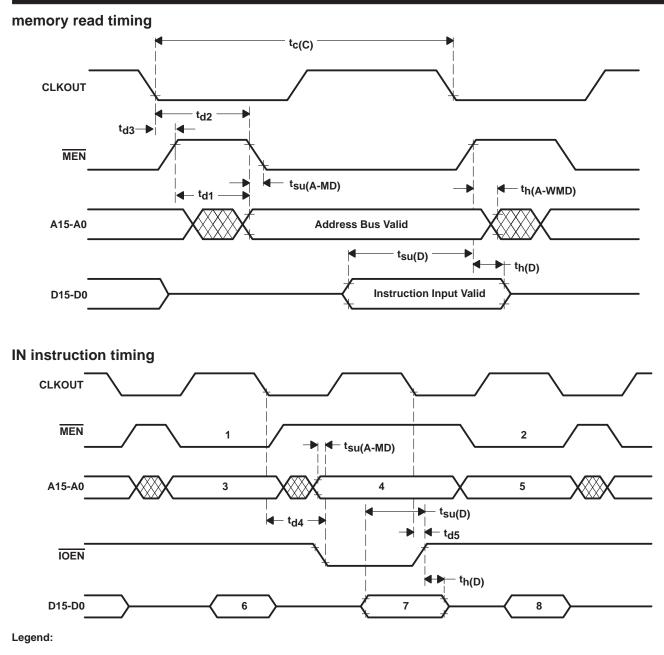

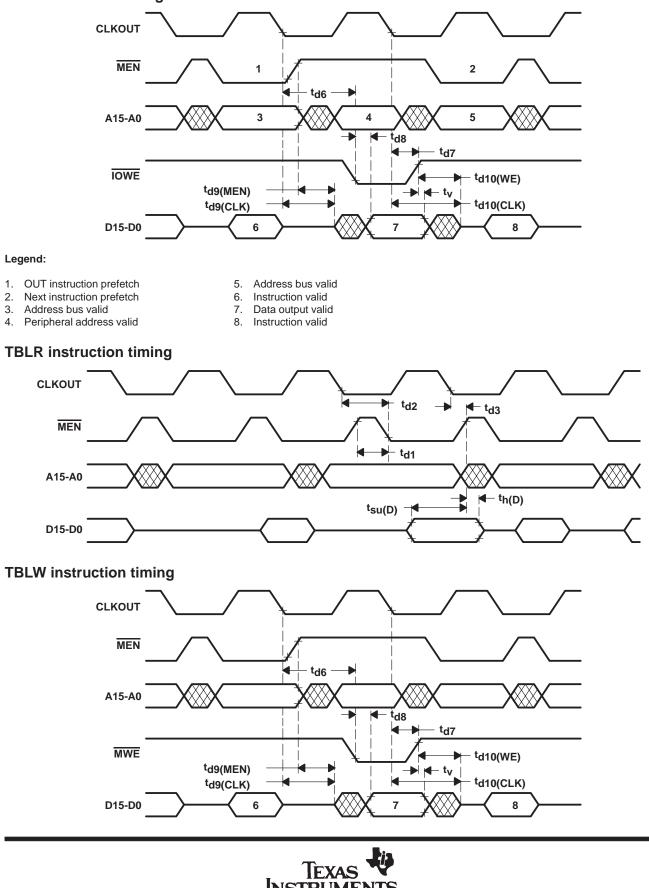

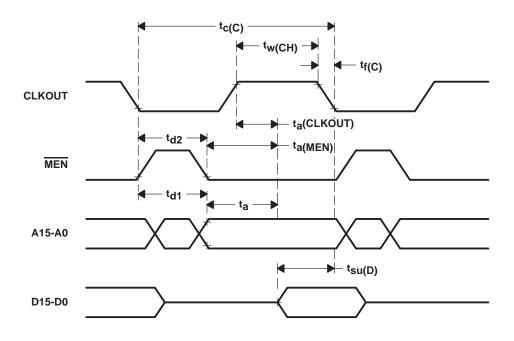

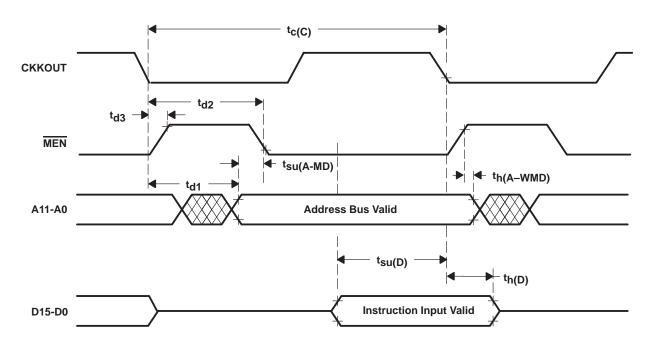

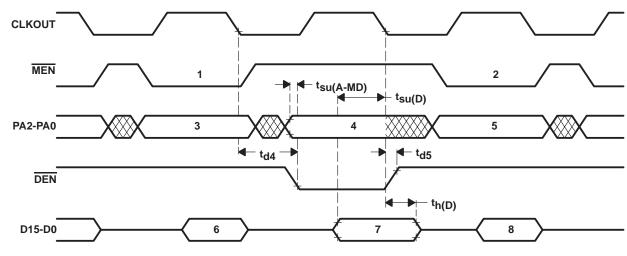

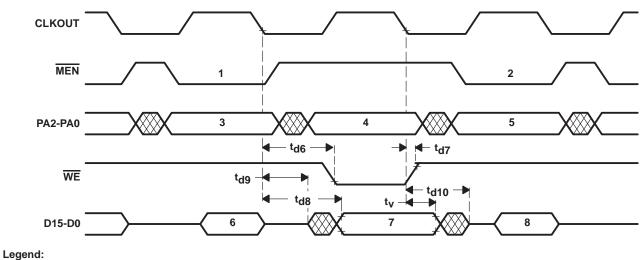

# MEMORY AND PERIPHERAL INTERFACE TIMING

# switching characteristics over recommended operating conditions

|                       | DADAMETED                                                                                            | TEST                      | тм                          | 6320C10                                            | TMS3                                  | 20C10-25                               |      |

|-----------------------|------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------|----------------------------------------------------|---------------------------------------|----------------------------------------|------|

|                       | PARAMETER                                                                                            | CONDITIONS                | MIN                         | TYP MAX                                            | MIN                                   | TYP MAX                                | UNIT |

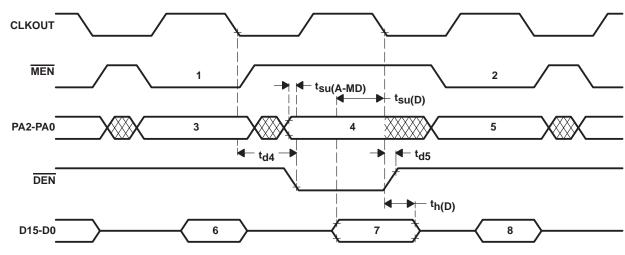

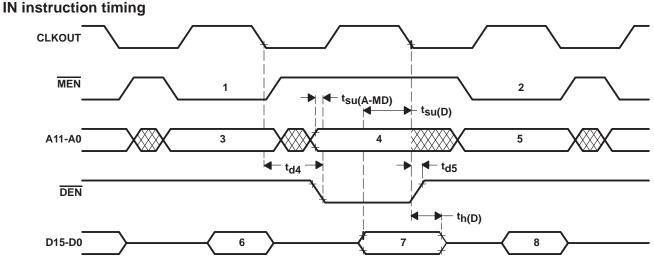

| <sup>t</sup> d1       | Delay time, CLKOUT↓ to<br>address bus valid                                                          |                           | 10†                         | 50                                                 | 10†                                   | 40                                     | ns   |

| t <sub>d2</sub>       | Delay time, CLKOUT↓ to MEN↓                                                                          |                           | 1/4t <sub>c(C)</sub> - 5†   | 1/4t <sub>c(C)</sub> + 15                          | 1/4t <sub>C(C)</sub> - 5 <sup>†</sup> | $1/4t_{C(C)} + 12$                     | ns   |

| td3                   | De <u>lay ti</u> me, CLKOUT↓<br>to MEN↑                                                              | ]                         | -10†                        | 15                                                 | -10†                                  | 12                                     | ns   |

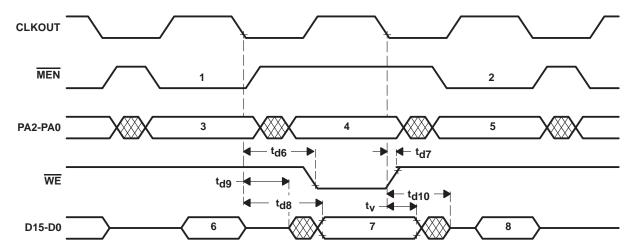

| t <sub>d4</sub>       | Delay time, CLKOUT↓ to DEN↓                                                                          | ]                         | 1/4t <sub>C(C)</sub> - 5†   | <sup>1</sup> / <sub>4</sub> t <sub>c(C)</sub> + 15 | 1/4t <sub>C(C)</sub> - 5 <sup>†</sup> | $1/4t_{C(C)} + 12$                     | ns   |

| td5                   | Delay time, CLKOUT↓<br>to DEN↑                                                                       | ]                         | -10†                        | 15                                                 | -10†                                  | 12                                     | ns   |

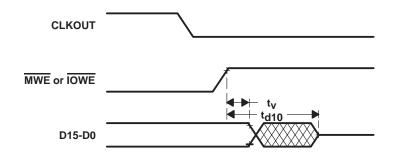

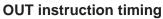

| <sup>t</sup> d6       | Delay time, CLKOUT $\downarrow$ to $\overline{WE}\downarrow$                                         | R <sub>I</sub> = 825 Ω    | $1/2t_{C(C)} - 5^{\dagger}$ | $1/2t_{c(C)} + 15$                                 | 1/2t <sub>c(C)</sub> -5†              | 1/2t <sub>C(C)</sub> + 12              | ns   |

| t <sub>d7</sub>       | Delay time, CLKOUT $\downarrow$ to $\overline{WE}\uparrow$                                           | $C_{L} = 100 \text{ pF},$ | -10†                        | 15                                                 | -10†                                  | 12                                     | ns   |

| <sup>t</sup> d8       | Delay time, CLKOUT↓ to data<br>bus OUT valid                                                         | (see Figure 2)            |                             | 1/4t <sub>C(C)</sub> + 65                          |                                       | 1/4t <sub>c(C)</sub> + 52 <sup>†</sup> | ns   |

| t <sub>d9</sub>       | Time after CLKOUT $\downarrow$ that data bus starts to be driven                                     | ]                         | 1/4t <sub>C(C)</sub> - 5†   |                                                    | 1/4t <sub>C(C)</sub> - 5 <sup>†</sup> |                                        | ns   |

| <sup>t</sup> d10      | Time after CLKOUT $\downarrow$ that data bus stops being driven                                      | ]                         |                             | <sup>1/4t</sup> c(C) + 40 <sup>†</sup>             |                                       | $1/4t_{C(C)} + 40^{\dagger}$           | ns   |

| t <sub>V</sub>        | Data bus OUT valid after<br>CLKOUT↓                                                                  | ]                         | 1/4t <sub>c(C)</sub> -10    |                                                    | 1/4t <sub>C(C)</sub> -10              |                                        | ns   |

| <sup>t</sup> h(A-WMD) | Address hold time after $\overline{WE}\uparrow$ ,<br>MEN $\uparrow$ , or DEN $\uparrow$ (see Note 8) | ]                         | -10†                        |                                                    | -10†                                  |                                        | ns   |

| <sup>t</sup> su(A-MD) | Ad <u>dress</u> bus <u>setu</u> p time prior<br>to MEN↓ or DEN↓                                      | ]                         | 1/4t <sub>c(C)</sub> -45    |                                                    | 1/4t <sub>C(C)</sub> -35              |                                        | ns   |

<sup>†</sup> Values derived from characterization data and not tested. NOTE 8: For interfacing I/O devices, see Figure 3.

# TMS320C10, TMS320C10-25 DIGITAL SIGNAL PROCESSORS

SPRS009C-JANUARY 1987-REVISED JULY 1991

## timing requirements over recommended operating conditions

|                   |                                                                       | TEST CONDITION                | TN  | /IS320C1 | 0   | TM  | S320C10 | -25 |      |

|-------------------|-----------------------------------------------------------------------|-------------------------------|-----|----------|-----|-----|---------|-----|------|

|                   |                                                                       | TEST CONDITION                | MIN | NOM      | MAX | MIN | NOM     | MAX | UNIT |

| tsu(D)            | Setup time, data bus valid prior to <code>CLKOUT</code> $\downarrow$  | R <sub>L</sub> = 825 Ω,       | 50  |          |     | 40  |         |     | ns   |

| <sup>t</sup> h(D) | Hold time, data bus held valid after CLKOUT $\downarrow$ (see Note 9) | CL = 100 pF<br>(see Figure 2) | 0   |          |     | 0   |         |     | ns   |

NOTE 9: Data may be removed from the data bus upon  $\overline{MEN}^{\uparrow}$  or  $\overline{DEN}^{\uparrow}$  preceding CLKOUT  $\downarrow$ .

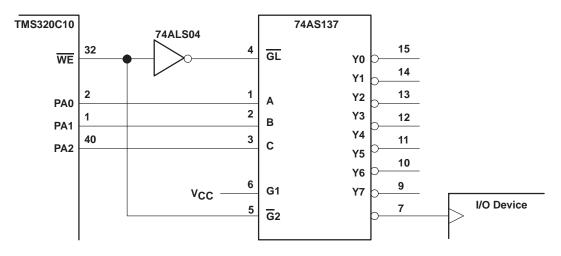

# SUGGESTED I/O DECODE CIRCUIT

The circuit shown in Figure 3 is a design example for interfacing I/O devices to the 'C10/C10-25. This circuit decodes the address for output operations using the OUT instruction. The same circuit can be used to decode input and output operations if the inverter ('ALS04) is replaced with a NAND gate and both DEN and WE are connected. Inputs and outputs can be decoded at the same port provided the output of the decoder ('AS137) is gated with the appropriate signal (DEN or WE) to select read or write (using an 'ALS32). Access times can be increased when the circuit shown in Figure 3 is repeated to support IN instructions with DEN connected rather than  $\overline{WE}$ .

The table write (TBLW) function requires a different circuit. A detailed discussion of an example circuit for this function is described in the application report, "Interfacing External Memory to the TMS32010", published in the book, *Digital Signal Processing Applications with the TMS320 Family* (SPRA012A).

Figure 3. I/O Decode Circuit

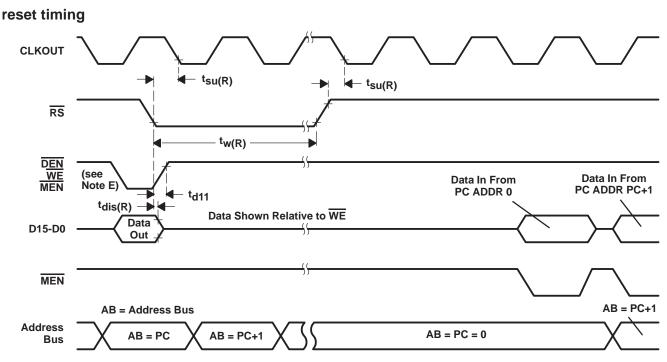

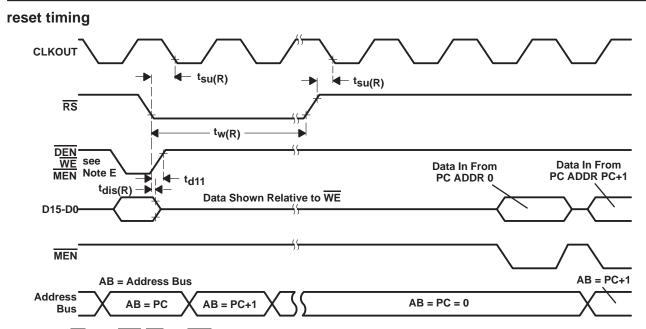

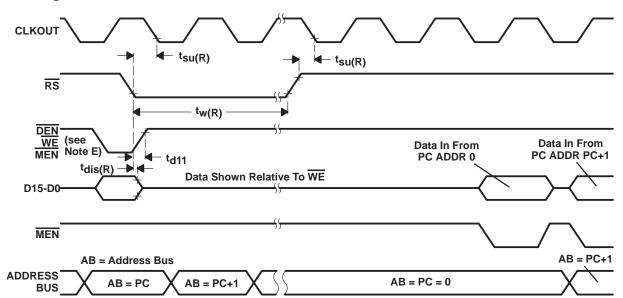

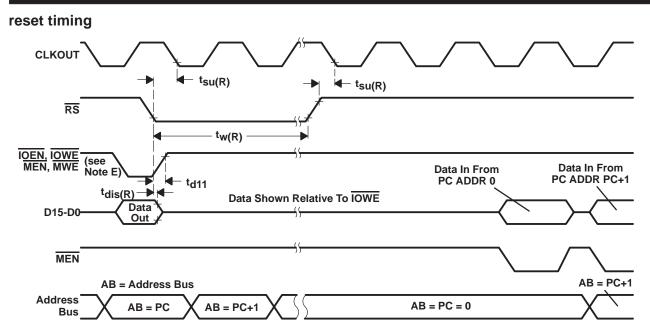

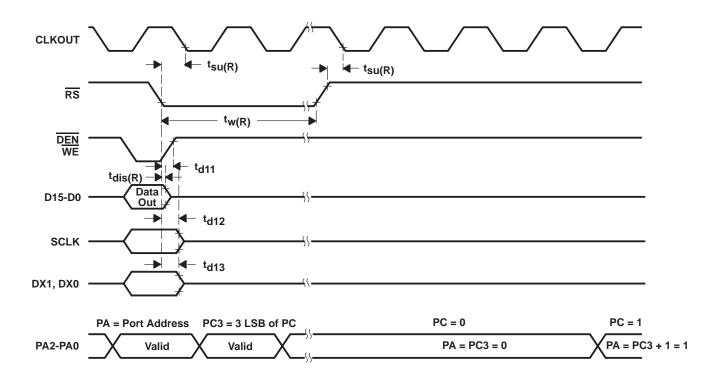

# **RESET (RS) TIMING**

# switching characteristics over recommended operating conditions

|                     | PARAMETER                                                                                  | TEST CONDITIONS                                   | MIN | TYP               | MAX                 | UNIT |

|---------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------|-----|-------------------|---------------------|------|

| <sup>t</sup> d11    | Delay time, $\overline{DEN}$ , $\overline{WE}$ , and $\overline{MEN}$ from $\overline{RS}$ | R <sub>L</sub> 825 Ω,<br>C <sub>L</sub> = 100 pF, |     | 1/2t <sub>C</sub> | (C)+50†             | ns   |

| <sup>t</sup> dis(R) | Data bus disable time after RS                                                             | (see Figure 2)                                    |     | 1/4t <sub>C</sub> | (C)+50 <sup>†</sup> | ns   |

<sup>†</sup> Values derived from characterization data and not tested.

## timing requirements over recommended operating conditions

|                     |                                                     | 1                  | TMS320C10 |     | TMS320C10-25        |     |     |      |

|---------------------|-----------------------------------------------------|--------------------|-----------|-----|---------------------|-----|-----|------|

|                     | PARAMETER                                           | MIN                | NOM       | MAX | MIN                 | NOM | MAX | UNIT |

| t <sub>su</sub> (R) | Reset (RS) setup time prior to CLKOUT (see Note 10) | 50                 |           |     | 40                  |     |     | ns   |

| <sup>t</sup> w(R)   | RS pulse duration                                   | 5t <sub>C(C)</sub> |           |     | 5t <sub>C</sub> (C) |     |     | ns   |

NOTE 10: RS can occur anytime during a clock cycle. Time given is minimum to ensure synchronous operation.

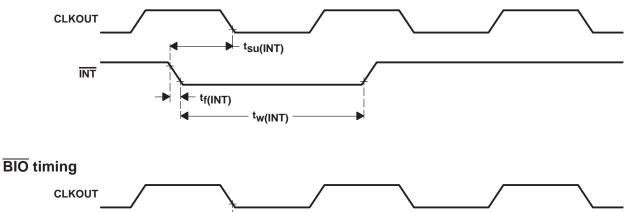

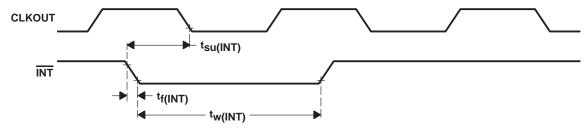

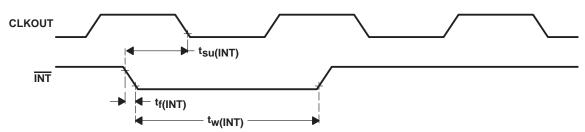

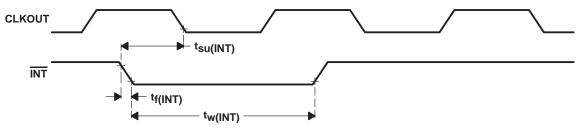

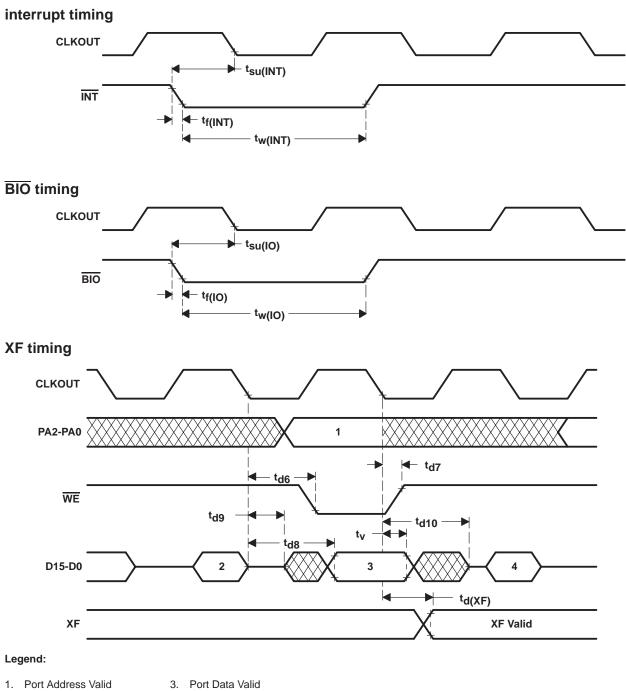

# INTERRUPT (INT) TIMING

## timing requirements over recommended operating conditions

|                      |                                                                   | -                 | TMS320C10 |     | TMS320C10-25      |     |     |      |

|----------------------|-------------------------------------------------------------------|-------------------|-----------|-----|-------------------|-----|-----|------|

|                      |                                                                   | MIN               | NOM       | MAX | MIN               | NOM | MAX | UNIT |

| <sup>t</sup> f(INT)  | Fall time, INT                                                    |                   |           | 15  |                   |     | 15  | ns   |

| <sup>t</sup> w(INT)  | Pulse duration, INT                                               | <sup>t</sup> c(C) |           |     | <sup>t</sup> c(C) |     |     | ns   |

| <sup>t</sup> su(INT) | Setup time, $\overline{INT}\downarrow$ before CLKOUT $\downarrow$ | 50                |           |     | 40                |     |     | ns   |

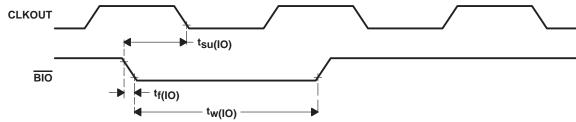

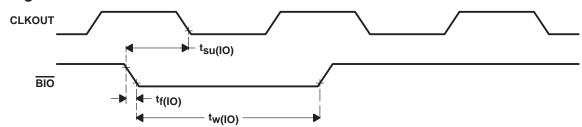

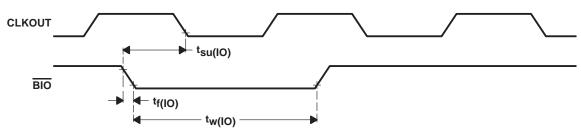

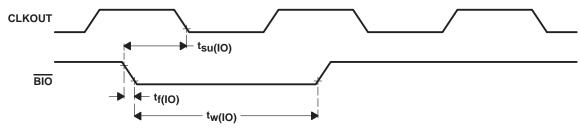

# IO (BIO) TIMING

## timing requirements over recommended operating conditions

|                      |                                                                   | -                 | TMS320C10 |     | TMS320C10-25      |     |     |      |

|----------------------|-------------------------------------------------------------------|-------------------|-----------|-----|-------------------|-----|-----|------|

|                      |                                                                   | MIN               | NOM       | MAX | MIN               | NOM | MAX | UNIT |

| <sup>t</sup> f(IO)   | Fall time, BIO                                                    |                   |           | 15  |                   |     | 15  | ns   |

| <sup>t</sup> w(IO)   | Pulse duration, BIO                                               | <sup>t</sup> c(C) |           |     | <sup>t</sup> c(C) | -   |     | ns   |

| t <sub>su</sub> (IO) | Setup time, $\overline{BIO}\downarrow$ before CLKOUT $\downarrow$ | 50                |           |     | 40                |     |     | ns   |

# TMS320C10-14 DIGITAL SIGNAL PROCESSORS

SPRS009C-JANUARY 1987-REVISED JULY 1991

### electrical characteristics over specified temperature range (unless otherwise noted)

| PARAMETER                                   | TEST CONDITIONS                                      | MIN | TYP† | MAX | UNIT |

|---------------------------------------------|------------------------------------------------------|-----|------|-----|------|

| I <sub>CC</sub> <sup>‡</sup> Supply current | f = 14.4, MHz, $V_{CC}$ = 5.5 V, $T_A$ = 0°C to 70°C |     | 28   | 65  | mA   |

<sup>†</sup> All typical values are at  $T_A = 70^{\circ}$ C and are used for thermal resistance calculations.

<sup>‡</sup>I<sub>CC</sub> characteristics are inversely proportional to temperature; i.e., I<sub>CC</sub> decreases approximately linearly with temperature.

## **CLOCK CHARACTERISTICS AND TIMING**

The TMS320C10-14 can use either its internal oscillator or an external frequency source for a clock.

### internal clock option

The internal oscillator is enabled by connecting a crystal across X1 and X2/CLKIN (see Figure 1). The frequency of CLKOUT is one-fourth the crystal fundamental frequency. The crystal should be fundamental mode, and parallel resonant, with an effective series resistance of 30 ohms, a power dissipation of 1 mW, and be specified at a load capacitance of 20 pF.

| PARAMETER                         | TEST CONDITIONS                     | MIN | NOM | MAX  | UNIT |

|-----------------------------------|-------------------------------------|-----|-----|------|------|

| Crystal frequency, f <sub>X</sub> | $T_A = 0^{\circ}C$ to $70^{\circ}C$ | 6.7 |     | 14.4 | MHz  |

| C1, C2                            | $T_A = 0^{\circ}C$ to $70^{\circ}C$ |     | 10  |      | pF   |

## external clock option

An external frequency source can be used by injecting the frequency directly into X2/CLKIN with X1 left unconnected. The external frequency injected must conform to the specifications listed in the table below.

#### switching characteristics over recommended operating conditions

|                    |                                                     | TEST CONDITIONS                                     | MIN    | NOM | MAX | UNIT |

|--------------------|-----------------------------------------------------|-----------------------------------------------------|--------|-----|-----|------|

| <sup>t</sup> c(C)  | CLKOUT cycle time§                                  |                                                     | 277.78 |     |     | ns   |

| <sup>t</sup> r(C)  | CLKOUT rise time                                    |                                                     |        | 10  |     | ns   |

| <sup>t</sup> f(C)  | CLKOUT fall time                                    | R <sub>L</sub> = 825 Ω,<br>C <sub>L</sub> = 100 pF, |        | 8   |     | ns   |

| <sup>t</sup> w(CL) | Pulse duration, CLKOUT low                          | (see Figure 2)                                      |        | 131 |     | ns   |

| <sup>t</sup> w(CH) | Pulse duration, CLKOUT high                         |                                                     |        | 129 |     | ns   |

| td(MCC)            | Delay time, CLKIN $\uparrow$ to CLKOUT $\downarrow$ |                                                     | 25¶    |     | 60¶ | ns   |

$t_{c(C)}$  is the cycle time of CLKOUT, i.e.,  $4t_{c(MC)}$  (4 times CLKIN cycle time if an external oscillator is used). Values derived from characterization data and not tested.

## timing requirements over recommended operating conditions

|                     |                                                               | MIN                     | NOM                           | MAX    | UNIT |

|---------------------|---------------------------------------------------------------|-------------------------|-------------------------------|--------|------|

| <sup>t</sup> c(MC)  | Master clock cycle time                                       | 69.5                    |                               | 150    | ns   |

| <sup>t</sup> r(MC)  | Rise time, master clock input                                 |                         | 5¶                            | 5¶ 10¶ |      |

| <sup>t</sup> f(MC)  | Fall time, master clock input                                 |                         | 5¶                            | 10¶    | ns   |

| <sup>t</sup> w(MCP) | Pulse duration, master clock                                  | 0.4t <sub>c(MC)</sub> ¶ | $0.4t_{c(MC)}$ $0.6t_{c(MC)}$ |        | ns   |

| <sup>t</sup> w(MCL) | Pulse duration, master clock low, $t_{C(MC)} = 50 \text{ ns}$ | 20¶                     |                               |        | ns   |

| <sup>t</sup> w(MCH) | Pulse duration, master clock high, $t_{C(MC)} = 50$ ns        | 20¶                     |                               |        | ns   |

$\P$  Values derived from characterization data and not tested.

# MEMORY AND PERIPHERAL INTERFACE TIMING

# switching characteristics over recommended operating conditions

|                       | PARAMETER                                                                                                                                  | TEST CONDITIONS          | MIN NO                                           | XAM MC                                | UNIT |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------|---------------------------------------|------|

| <sup>t</sup> d1       | Delay time, CLKOUT $\downarrow$ to address bus valid                                                                                       |                          | 10†                                              | 50                                    | ns   |

| t <sub>d2</sub>       | Delay time, CLKOUT $\downarrow$ to $\overline{MEN}\downarrow$                                                                              | 1                        | $1/_{4t_{C(C)}} - 5^{\dagger}$                   | 1/4t <sub>C(C)</sub> +15              | ns   |

| t <sub>d3</sub>       | Delay time, CLKOUT↓ to MEN↑                                                                                                                | ]                        | -10†                                             | 15                                    | ns   |

| t <sub>d4</sub>       | Delay time, CLKOUT $\downarrow$ to $\overline{DEN}\downarrow$                                                                              | 1                        | $1/_4 t_{C(C)} - 5^{\dagger} $ $1/_4 t_{C(C)} +$ |                                       | ns   |

| td5                   | Delay time, CLKOUT↓ to DEN↑                                                                                                                | 1                        | -10†                                             | 15                                    | ns   |

| <sup>t</sup> d6       | Delay time, CLKOUT $\downarrow$ to $\overline{WE}\downarrow$                                                                               | RL = 825 Ω,              | $1/2t_{C(C)} - 5^{\dagger}$                      | 1/2tc(C)+15                           | ns   |

| t <sub>d7</sub>       | Delay time, CLKOUT $\downarrow$ to $\overline{WE}\uparrow$                                                                                 | $C_{L} = 100 \text{ pF}$ | -10†                                             | 15                                    | ns   |

| t <sub>d8</sub>       | Delay time, CLKOUT $\downarrow$ to data bus OUT valid                                                                                      | (see Figure 2)           |                                                  | 1/4t <sub>c(C)</sub> +65              | ns   |

| t <sub>d</sub> 9      | Time after CLKOUT $\downarrow$ that data bus starts to be driven                                                                           | 1                        | 1/4t <sub>C(C)</sub> - 5 <sup>†</sup>            |                                       | ns   |

| <sup>t</sup> d10      | Time after CLKOUT $\downarrow$ that data bus stops being driven                                                                            | 1                        |                                                  | 1/4t <sub>c(C)</sub> +40 <sup>†</sup> | ns   |

| t <sub>v</sub>        | Data bus OUT valid after <code>CLKOUT</code>                                                                                               | 1                        | $1/4t_{C(C)} - 10$                               |                                       | ns   |

| <sup>t</sup> h(A-WMD) | Address hold time after $\overline{\text{WE}}\uparrow$ , $\overline{\text{MEN}}\uparrow$ , or $\overline{\text{DEN}}\uparrow$ (see Note 8) |                          | -10†                                             |                                       | ns   |