出货

WWW.DZS

# **OKI** Semiconductor

## **MSM6690**

**ROM Interface IC**

#### **GENERAL DESCRIPTION**

The MSM6690 can drive three devices of 131,072 x 8-bit EPROM or Mask ROM.

The MSM6690 contains a built-in internal address generator circuit and one external clock input that enables continued serial read operations. The internal address counter is automatically incremented by one each read operation. The external serial address input allows 1,024 words to be addressed in the X-direction, and 1,024 words in the Y-direction.

\* ROM is selected through  $\overline{CS1}$ ,  $\overline{CS2}$  and  $\overline{CS3}$  pins.

#### **FEATURES**

Capable of driving three devices of 1 Mbit EPROM

• Capable of driving three devices of 1 Mbit Mask ROM

• Supply voltage : Single 5 V

Package options : 42-pin plastic DIP (DIP42-P-600) (Product name: MSM6690RS)

44-pin plastic QFP (QFP44-P-910-2K) (Product name: MSM6690GS-2K)

\* Available combinations

Note: When driving the MSM6690 with the MSM6388 or the MSM6588, a serial register (MSM6389, MSM6688 or MSM6586) is required.

In the case of the MSM6688, MSM6788 and MSM6789A, a playback system can be constructed without a serial register (MSM6684 or MSM6685).

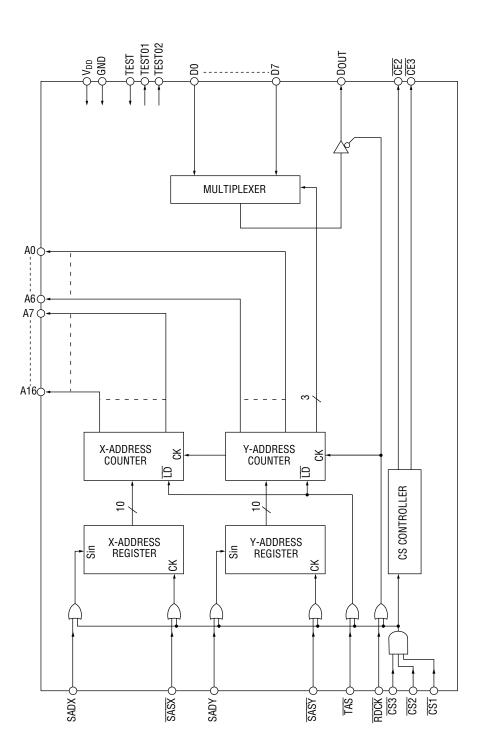

### **BLOCK DIAGRAM**

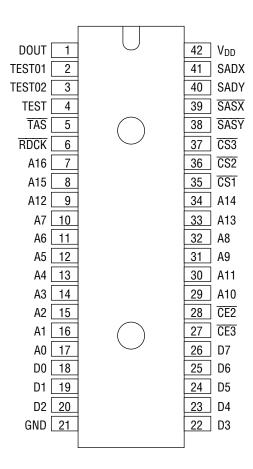

### **PIN CONFIGURATION (TOP VIEW)**

**42-Pin Plastic DIP**

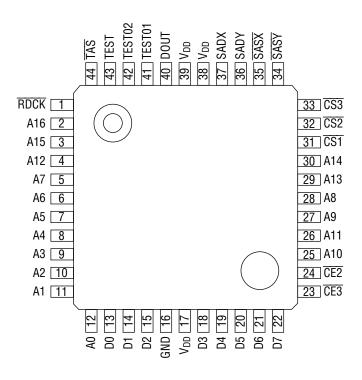

## PIN CONFIGURATION (TOP VIEW) (Continued)

44-Pin Plastic QFP

## **PIN DESCRIPTIONS**

| Symbol   | Туре | Description                                                                          |  |  |  |  |

|----------|------|--------------------------------------------------------------------------------------|--|--|--|--|

| $V_{DD}$ | _    | Power Supply                                                                         |  |  |  |  |

| GND      | _    | Ground                                                                               |  |  |  |  |

| SADX     | I    | (SERIAL ADDRESS) Starting X address.                                                 |  |  |  |  |

|          |      | 1024 words are addressed, and 1024 address data can be input as serial data          |  |  |  |  |

|          |      | of 10 bit (AX0 to AX9) via SADX pin.                                                 |  |  |  |  |

| SADY     | Į    | (SERIAL ADDRESS) Starting Y address.                                                 |  |  |  |  |

|          |      | 1024 words are addressed, and 1024 address data can be input as serial data          |  |  |  |  |

|          |      | of 10 bit (AY0 to AY9) via SADY pin.                                                 |  |  |  |  |

| SASX     | Į    | (SERIAL ADDRESS STROBE) Clock to load X address's serial address data to             |  |  |  |  |

|          |      | internal register.                                                                   |  |  |  |  |

| SASY     | I    | (SERIAL ADDRESS STROBE) Clock to load Y address's serial address data to             |  |  |  |  |

|          |      | internal register.                                                                   |  |  |  |  |

| TAS      | 1    | (TRANSFER ADDRESS STROBE) Serial address data loaded in address                      |  |  |  |  |

|          |      | register, to internal address counter.                                               |  |  |  |  |

|          |      | X address and Y address data are loaded at fall of TAS pin.                          |  |  |  |  |

| RDCK     | I    | (READ CLOCK) Clock to read data in data register.                                    |  |  |  |  |

|          |      | Internal operation starts on falling edge of RDCK, and data in the data register     |  |  |  |  |

|          |      | is output via DOUT pin. And internal address counter is automatically                |  |  |  |  |

|          |      | incremented by one due to the falling of RDCK.                                       |  |  |  |  |

| DOUT     | 0    | (DATA OUT) In case CS1, CS2 and CS3 are all at "H" level, or RDCK is at "H"          |  |  |  |  |

|          |      | level data output pin is always at high impedance state.                             |  |  |  |  |

|          |      | When "H" level data or "L" level data is read out, output pin is set to "H" level or |  |  |  |  |

|          |      | "L" level and its read data is kept until RDCK turns to "H" level.                   |  |  |  |  |

| CS1      | I    | (CHIP SELECT) Three ROMS selection.                                                  |  |  |  |  |

| CS2      |      | CS1 CS2 CS3 CE2 CE3                                                                  |  |  |  |  |

| CS3      |      | L — H H                                                                              |  |  |  |  |

|          |      | H L — L H                                                                            |  |  |  |  |

|          |      | H H L H L                                                                            |  |  |  |  |

|          |      | H H H H                                                                              |  |  |  |  |

|          |      | When CS1, CS2 and CS3 are all set to "H" level, all input/output pins become         |  |  |  |  |

|          |      | disabled. By use of these pins, three ROM data output pins can be connected          |  |  |  |  |

|          |      | in parallel.                                                                         |  |  |  |  |

|          |      | iii paraller.                                                                        |  |  |  |  |

| CE2      | 0    | (CHIP ENABLE) ROM enable.                                                            |  |  |  |  |

| CE3      |      | Connect it to ROM's CE.                                                              |  |  |  |  |

| A0 - A16 | 0    | (ADDRESS OUT) ROM address.                                                           |  |  |  |  |

| D0 - D7  | 1    | (DATA IN) ROM data.                                                                  |  |  |  |  |

| TEST     | 1    | IC test.                                                                             |  |  |  |  |

|          |      | Input "L" level data.                                                                |  |  |  |  |

| TEST01   | 0    | IC test.                                                                             |  |  |  |  |

| TEST02   |      | Set to open                                                                          |  |  |  |  |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol           | Condition | Rating                       | Unit |

|----------------------|------------------|-----------|------------------------------|------|

| Power Supply Voltage | V <sub>DD</sub>  |           | -0.3 to +7.0                 | V    |

| Input Voltage        | VI               | Ta = 25°C | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output Voltage       | V <sub>0</sub>   | Typical:  | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Input Current        | II               | GND = 0 V | -10 to +10                   | mA   |

| Output Current       | I <sub>0</sub>   |           | -20 to +20                   | mA   |

| Storage Temperature  | T <sub>STG</sub> | _         | -55 to +150                  | °C   |

#### RECOMMENDED OPERATING CONDITIONS

(GND = 0 V)

| Parameter             | Symbol          | Range        | Unit |

|-----------------------|-----------------|--------------|------|

| Power Supply Voltage  | $V_{DD}$        | +3.0 to +6.0 | V    |

| Operating Temperature | T <sub>op</sub> | -40 to +85   | °C   |

### **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

$(V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ GND} = 0 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                   | Symbol           | Condition                                       | Min. | Typ.* | Max.                 | Unit |

|-----------------------------|------------------|-------------------------------------------------|------|-------|----------------------|------|

| "H" level Input Voltage     | V <sub>IH</sub>  | CMOS level input                                | 3.5  | _     | V <sub>DD</sub> +0.3 | V    |

| "L" level Input Voltage     | V <sub>IL</sub>  | CMOS level input                                | -0.3 | _     | 1.5                  | V    |

| "H" level Input Current     | I <sub>IH</sub>  | $V_{IH} = V_{DD}$                               | _    | 0.01  | 10                   | μΑ   |

| "L" level Input Current     | I <sub>IL</sub>  | V <sub>IL</sub> = GND                           | -10  | -0.01 | _                    | μΑ   |

| 3-state Output Leak Current | I <sub>OZH</sub> | $V_{OH} = V_{DD}$                               | _    | 0.01  | 10                   | ۸    |

| (with open drain output)    | I <sub>OZL</sub> | V <sub>OL</sub> = GND                           | -10  | -0.01 | _                    | μΑ   |

| "H" level Output Voltage    | V <sub>OH</sub>  | $I_{OH} = -5.0 \text{ mA}$                      | 2.4  | 4.2   | V <sub>DD</sub>      | V    |

| "L" level Output Voltage    | V <sub>OL</sub>  | $I_{0L} = 5.0 \text{ mA}$                       | GND  | 0.24  | 0.5                  | V    |

| Supply Current at Standby   | I DS             | Output open $V_{IH} = V_{DD}$<br>$V_{IL} = GND$ | _    | 0.1   | 100                  | μΑ   |

| Supply Current at Operating | I <sub>DD</sub>  | _                                               |      | _     | 2                    | mA   |

<sup>\*</sup> Typical operation is with  $V_{DD} = 5.0 \text{ V}$ ,  $Ta = 25^{\circ}\text{C}$

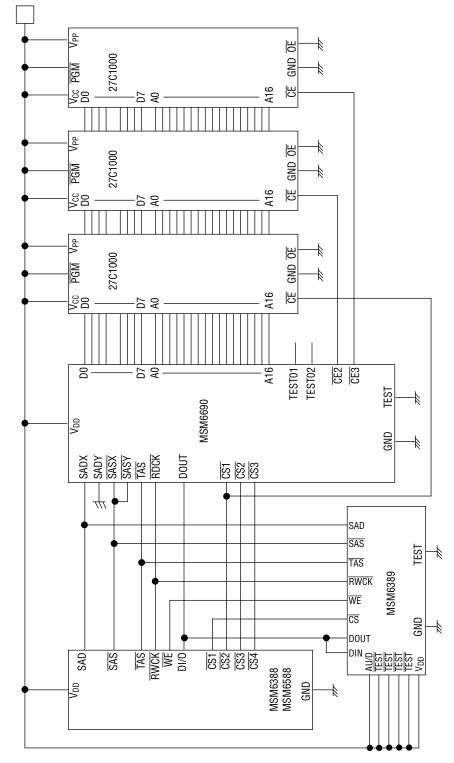

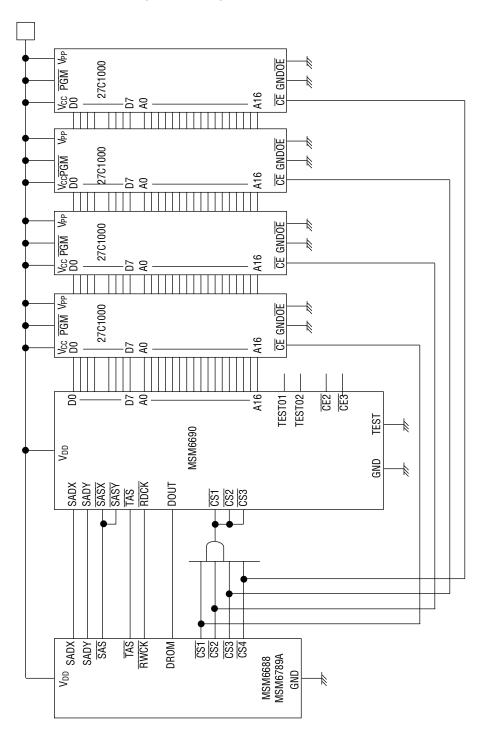

#### **APPLICATION CIRCUITS**

Example of application circuit where MSM6388/6588,a 1-Mbit serial register, and three 1-Mbit EPROMs are connected.

## **APPLICATION CIRCUITS (Continued)**

Example of application circuit where MSM6688/6789A and four 1-Mbit EPROMs are connected.