June 2002

## LM2466

# Monolithic Triple 7.5 ns CRT Driver

## **General Description**

The LM2466 is an integrated high voltage CRT driver circuit designed for use in color monitor applications. The IC contains three high input impedance, wide band amplifiers which directly drive the RGB cathodes of a CRT. Each channel has its gain internally set to –20 and can drive CRT capacitive loads as well as resistive loads present in other applications, limited only by the package's power dissipation.

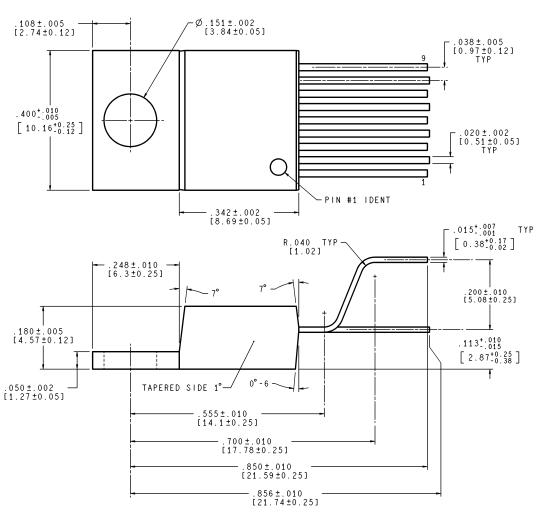

The IC is packaged in an industry standard 9-lead TO-220 molded plastic power package. See the Thermal Considerations section for more information.

# **Features**

- Higher gain to match LM126X CMOS preamplifiers

- 0V to 3.75V input range

- Stable with 0–20 pF capacitive loads and inductive peaking networks

- Convenient TO-220 staggered lead package style

- Maintains standard LM243X Family pinout which is designed for easy PCB layout

# **Applications**

- 1024 x 768 displays up to 85 Hz refresh

- Pixel clock frequencies up to 95 MHz

- Monitors using video blanking

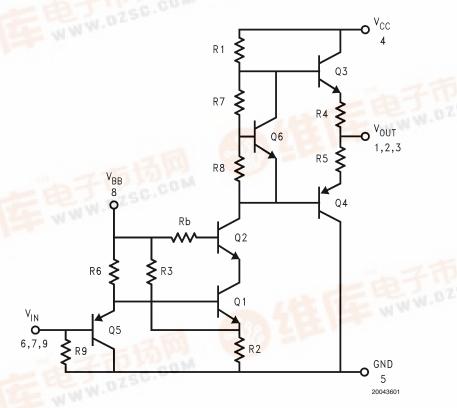

## **Schematic Diagram**

FIGURE 1. Simplified Schematic Diagram (One Channel)

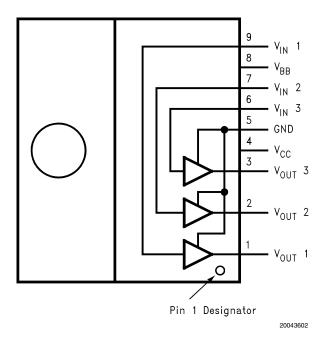

# **Connection Diagram**

Note: Tab is at GND

Top View Order Number LM2466TA

250V

# **Absolute Maximum Ratings (Notes 1,**

Machine Model

3)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$\begin{array}{lll} \text{Supply Voltage (V}_{\text{CC}}) & +90\text{V} \\ \text{Bias Voltage (V}_{\text{BB}}) & +16\text{V} \\ \text{Input Voltage (V}_{\text{IN}}) & 0\text{V to 4.5V} \\ \text{Storage Temperature Range (T}_{\text{STG}}) & -65\,^{\circ}\text{C to +150}\,^{\circ}\text{C} \\ \end{array}$

Lead Temperature

(Soldering, <10 sec.) 300°C ESD Tolerance, Human Body

Model

# Operating Ranges (Note 2)

$\begin{array}{ccc} V_{CC} & +60 \text{V to } +85 \text{V} \\ V_{BB} & +8 \text{V to } +15 \text{V} \\ V_{IN} & +0 \text{V to } +3.75 \text{V} \\ V_{OUT} & +15 \text{V to } +75 \text{V} \\ Case Temperature & -20 ^{\circ}\text{C to } +100 ^{\circ}\text{C} \end{array}$

Do not operate the part without a heat sink.

#### **Electrical Characteristics**

(See Figure 2 for Test Circuit) Unless otherwise noted:  $V_{CC}$  = +80V,  $V_{BB}$  = +12V,  $C_L$  = 8 pF,  $T_C$  = 50°C DC Tests:  $V_{IN}$  = 2.25VDC AC Tests: Output =  $40V_{PP}(25V - 65V)$  at 1MHz

2 kV

| Symbol           | Parameter         | Conditions                                             | LM2466 |         |     | Units           |

|------------------|-------------------|--------------------------------------------------------|--------|---------|-----|-----------------|

|                  |                   |                                                        | Min    | Typical | Max | Units           |

| I <sub>CC</sub>  | Supply Current    | All Three Channels, No Input Signal,<br>No Output Load |        | 30      |     | mA              |

| I <sub>BB</sub>  | Bias Current      | All Three Channels                                     |        | 18      |     | mA              |

| V <sub>OUT</sub> | DC Output Voltage | No AC Input Signal, V <sub>IN</sub> = 1.25V            | 62     | 65      | 68  | V <sub>DC</sub> |

| A <sub>V</sub>   | DC Voltage Gain   | No AC Input Signal                                     | -18    | -20     | -22 |                 |

| $\Delta A_V$     | Gain Matching     | (Note 4), No AC Input Signal                           |        | 1.0     |     | dB              |

| LE               | Linearity Error   | (Notes 4, 5), No AC Input Signal                       |        | 5       |     | %               |

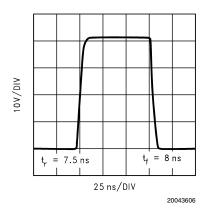

| t <sub>R</sub>   | Rise Time         | (Note 6), 10% to 90%                                   |        | 7.5     |     | ns              |

| t <sub>F</sub>   | Fall Time         | (Note 6), 90% to 10%                                   |        | 8       |     | ns              |

| OS               | Overshoot         | (Note 6)                                               |        | 1       |     | %               |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

**Note 2:** Operating ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may change when the device is not operated under the listed test conditions.

Note 3: All voltages are measured with respect to GND, unless otherwise specified.

Note 4: Calculated value from Voltage Gain test on each channel.

Note 5: Linearity Error is the variation in dc gain from  $V_{IN}=1.0V$  to  $V_{IN}=3.5V$ .

Note 6: Input from signal generator:  $t_r$ ,  $t_f < 1$  ns.

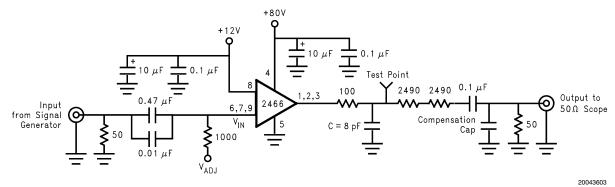

# **AC Test Circuit**

Note: 8 pF load includes parasitic capacitance.

#### FIGURE 2. Test Circuit (One Channel)

Figure 2 shows a typical test circuit for evaluation of the LM2466. This circuit is designed to allow testing of the LM2466 in a  $50\Omega$  environment without the use of an expensive FET probe. The two  $2490\Omega$  resistors form a 200:1 divider with the  $50\Omega$  resistor and the oscilloscope. A test point is included for easy use of an oscilloscope probe. The compensation capacitor is used to compensate the stray capacitance of the two  $2490\Omega$  resistors to achieve flat frequency response.

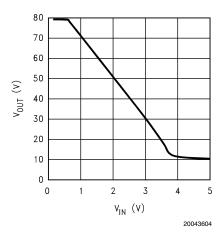

FIGURE 3.  $V_{\rm OUT}$  vs  $V_{\rm IN}$

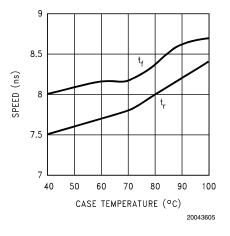

FIGURE 4. Speed vs Temp.

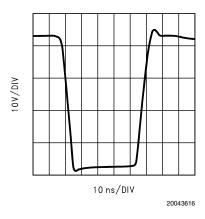

FIGURE 5. LM2466 Pulse Response

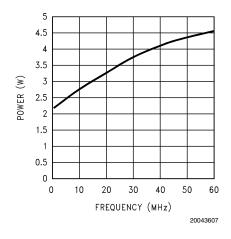

FIGURE 6. Power Dissipation vs Frequency

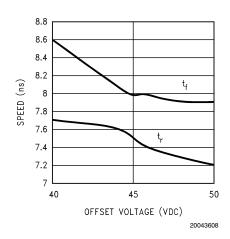

FIGURE 7. Speed vs Offset

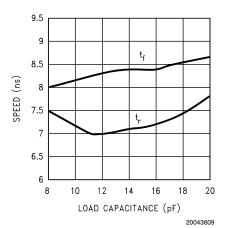

Speed vs Load Capacitance

FIGURE 8.

## Theory of Operation

The LM2466 is a high voltage monolithic three channel CRT driver suitable for high resolution display applications. The LM2466 operates with 80V and 12V power supplies. The part is housed in the industry standard 9-lead TO-220 molded plastic power package.

The circuit diagram of the LM2466 is shown in *Figure 1*. The PNP emitter follower, Q5, provides input buffering. Q1 and Q2 form a fixed gain cascode amplifier with resistors R1 and R2 setting the gain at –20. Emitter followers Q3 and Q4 isolate the high output impedance of the cascode stage from the capacitance of the CRT cathode which decreases the sensitivity of the device to load capacitance. Q6 provides biasing to the output emitter follower stage to reduce crossover distortion at low signal levels.

Figure 2 shows a typical test circuit for evaluation of the LM2466. This circuit is designed to allow testing of the LM2466 in a  $50\Omega$  environment without the use of an expensive FET probe. In this test circuit, the two  $2.49k\Omega$  resistors form a 200:1 wideband, low capacitance probe when connected to a  $50\Omega$  coaxial cable and a  $50\Omega$  load (such as a  $50\Omega$  oscilloscope input). The input signal from the generator is ac coupled to the base of Q5.

## **Application Hints**

#### INTRODUCTION

National Semiconductor (NSC) is committed to provide application information that assists our customers in obtaining the best performance possible from our products. The following information is provided in order to support this commitment. The reader should be aware that the optimization of performance was done using a specific printed circuit board designed at NSC. Variations in performance can be realized due to physical changes in the printed circuit board and the application. Therefore, the designer should know that component value changes may be required in order to optimize performance in a given application. The values shown in this document can be used as a starting point for evaluation purposes. When working with high bandwidth circuits, good layout practices are also critical to achieving maximum performance.

#### IMPORTANT INFORMATION

The LM2466 performance is targeted for the VGA (640  $\times$  480) to XGA (1024  $\times$  768, 85 Hz refresh) resolution market. The application circuits shown in this document to optimize

performance and to protect against damage from CRT arcover are designed specifically for the LM2466. If another member of the LM246X family is used, please refer to its datasheet.

#### **POWER SUPPLY BYPASS**

Since the LM2466 is a wide bandwidth amplifier, proper power supply bypassing is critical for optimum performance. Improper power supply bypassing can result in large overshoot, ringing or oscillation. 0.1  $\mu F$  capacitors should be connected from the supply pins,  $V_{CC}$  and  $V_{BB}$ , to ground, as close to the LM2466 as is practical. Additionally, a 47  $\mu F$  or larger electrolytic capacitor should be connected from both supply pins to ground reasonably close to the LM2466.

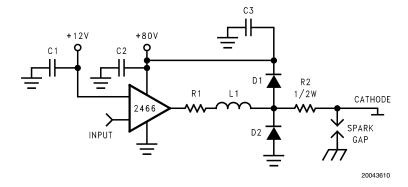

#### **ARC PROTECTION**

During normal CRT operation, internal arcing may occasionally occur. Spark gaps, in the range of 200V, connected from the CRT cathodes to CRT ground will limit the maximum voltage, but to a value that is much higher than allowable on the LM2466. This fast, high voltage, high energy pulse can damage the LM2466 output stage. The application circuit shown in Figure 9 is designed to help clamp the voltage at the output of the LM2466 to a safe level. The clamp diodes, D1 and D2, should have a fast transient response, high peak current rating, low series impedance and low shunt capacitance. FDH400 or equivalent diodes are recommended. Do not use 1N4148 diodes for the clamp diodes. D1 and D2 should have short, low impedance connections to  $V_{\rm CC}$  and ground respectively. The cathode of D1 should be located very close to a separately decoupled bypass capacitor (C3 in Figure 9). The ground connection of D2 and the decoupling capacitor should be very close to the LM2466 ground. This will significantly reduce the high frequency voltage transients that the LM2466 would be subjected to during an arcover condition. Resistor R2 limits the arcover current that is seen by the diodes while R1 limits the current into the LM2466 as well as the voltage stress at the outputs of the device. R2 should be a ½W solid carbon type resistor. R1 can be a ¼W metal or carbon film type resistor. Having large value resistors for R1 and R2 would be desirable, but this has the effect of increasing rise and fall times. Inductor L1 is critical to reduce the initial high frequency voltage levels that the LM2466 would be subjected to. The inductor will not only help protect the device but it will also help minimize rise and fall times as well as minimize EMI. For proper arc protection, it is important to not omit any of the arc protection components shown in Figure 9.

FIGURE 9. One Channel of the LM2466 with the Recommended Application Circuit

#### **OPTIMIZING TRANSIENT RESPONSE**

Referring to Figure 9, there are three components (R1, R2 and L1) that can be adjusted to optimize the transient response of the application circuit. Increasing the values of R1 and R2 will slow the circuit down while decreasing overshoot. Increasing the value of L1 will speed up the circuit as well as increase overshoot. It is very important to use inductors with very high self-resonant frequencies, preferably above 300 MHz. Ferrite core inductors from J.W. Miller Magnetics (part # 78FR--k) were used for optimizing the performance of the device in the NSC application board. The values shown in Figure 11 and Figure 12 can be used as a good starting point for the evaluation of the LM2466. Using variable resistors for R1 and the parallel resistor will simplify finding the values needed for optimum performance in a given application. Once the optimum values are determined the variable resistors can be replaced with fixed values.

#### **EFFECT OF LOAD CAPACITANCE**

Figure 8 shows the effect of increased load capacitance on the speed of the device. This demonstrates the importance of knowing the load capacitance in the application.

#### **EFFECT OF OFFSET**

Figure 7 shows the variation in rise and fall times when the output offset of the device is varied from 40 to 50  $V_{\rm DC}$ . The rise time shows a maximum variation relative to the center data point (45  $V_{\rm DC}$ ) less than 5%. The fall time shows a variation of less than 8% relative to the center data point.

#### THERMAL CONSIDERATIONS

Figure 4 shows the performance of the LM2466 in the test circuit shown in Figure 2 as a function of case temperature. The figure shows that the rise time of the LM2466 increases by approximately 10% as the case temperature increases from 50°C to 100°C. This corresponds to a speed degradation of 2% for every 10°C rise in case temperature. The fall time increases by approximately 7% as the case temperature increases from 50°C to 100°C.

*Figure 6* shows the maximum power dissipation of the LM2466 vs. Frequency when all three channels of the device are driving an 8 pF load with a 40  $V_{p-p}$  alternating one pixel on, one pixel off signal. The graph assumes a 72% active time (device operating at the specified frequency) which is typical in a monitor application. The other 28% of the time the device is assumed to be sitting at the black level (65V in

this case). This graph gives the designer the information needed to determine the heat sink requirement for his application. The designer should note that if the load capacitance is increased the AC component of the total power dissipation will also increase.

The LM2466 case temperature must be maintained below 100°C. If the maximum expected ambient temperature inside the monitor is 70°C and the power dissipation is 4.4W (from *Figure 6*, 50 MHz max. video frequency), then a maximum heat sink thermal resistance can be calculated:

$$R_{TH} = \frac{100^{\circ}C - 70^{\circ}C}{4.4W} = 6.8^{\circ}C/W$$

This example assumes a capacitive load of 8 pF and no resistive load.

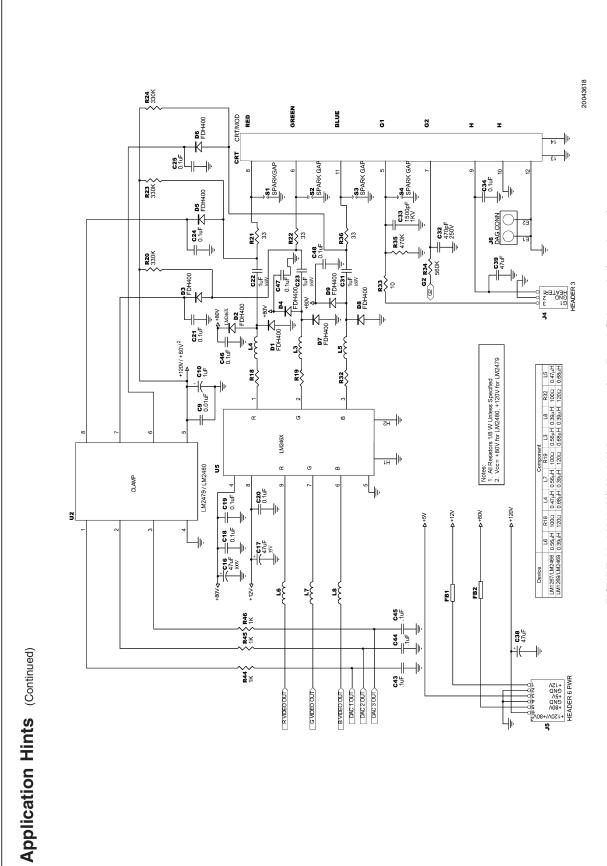

#### TYPICAL APPLICATION

A typical application of the LM2466 is shown in *Figure 11* and *Figure 12*. Used in conjunction with an LM1267, a complete video channel from monitor input to CRT cathode can be achieved. Performance is ideal for 1024 x 768 resolution displays with pixel clock frequencies up to 95 MHz. *Figure 11* and *Figure 12* are the schematic for the NSC demonstration board that can be used to evaluate the LM1267/2466 combination in a monitor, and *Figure 10* shows the typical response at the red cathode for this application. The input video rise time is 3.2ns, and the peaking component values are those recommended in *Figure 12*. *Table 1* shows the typical cathode response of all three channels.

FIGURE 10. Red Cathode Response

TABLE 1. LM2466 Cathode Response

| Channel | t <sub>r</sub> /OS | t <sub>f</sub> /OS |

|---------|--------------------|--------------------|

| Red     | 6.3ns / 7%         | 6.3ns / 3%         |

| Green   | 6.1ns / 6%         | 5.9ns / 4%         |

| Blue    | 6.5ns / 3%         | 6.4ns / 2%         |

#### PC BOARD LAYOUT CONSIDERATIONS

For optimum performance, an adequate ground plane, isolation between channels, good supply bypassing and minimizing unwanted feedback are necessary. Also, the length of the signal traces from the preamplifier to the LM2466 and from the LM2466 to the CRT cathode should be as short as possible. The following references are recommended:

Ott, Henry W., "Noise Reduction Techniques in Electronic Systems", John Wiley & Sons, New York, 1976.

"Video Amplifier Design for Computer Monitors", National Semiconductor Application Note 1013.

Pease, Robert A., "Troubleshooting Analog Circuits", Butterworth-Heinemann, 1991.

Because of its high small signal bandwidth, the part may oscillate in a monitor if feedback occurs around the video channel through the chassis wiring. To prevent this, leads to the video amplifier input circuit should be shielded, and input circuit wiring should be spaced as far as possible from output circuit wiring.

#### **NSC DEMONSTRATION BOARD**

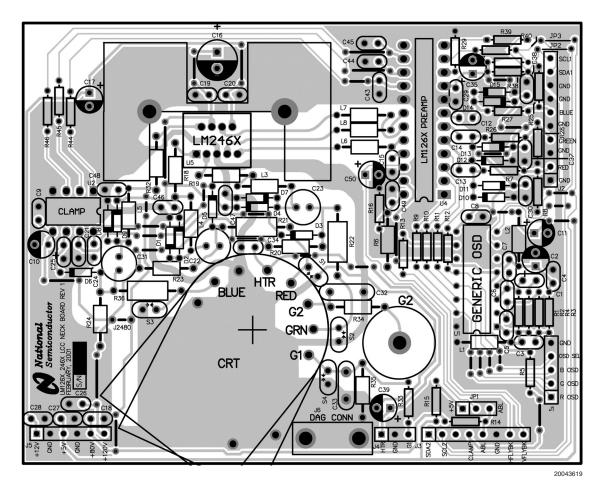

Figure 13 shows the routing and component placement on the NSC LM1267/2466 demonstration board. The schematic of the board is shown in Figure 11 and Figure 12. This board provides a good example of a layout that can be used as a guide for future layouts. Note the location of the following components:

- C19—V<sub>CC</sub> bypass capacitor, located very close to pin 4 and ground pins

- C20—V<sub>BB</sub> bypass capacitors, located close to pin 8 and ground

- C46, C47, C48—V<sub>CC</sub> bypass capacitors, near LM2466 and V<sub>CC</sub> clamp diodes. Very important for arc protection.

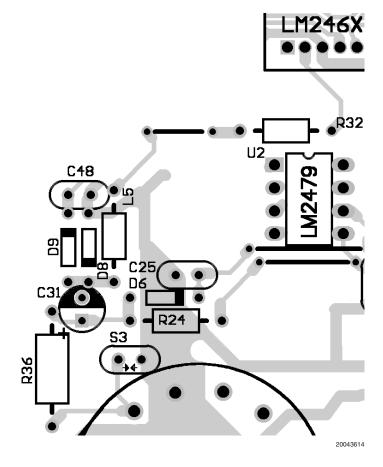

The routing of the LM2466 outputs to the CRT is very critical to achieving optimum performance. Figure 14 shows the routing and component placement from pin 1 of the LM2466 to the blue cathode. Note that the components are placed so that they almost line up from the output pin of the LM2466 to the blue cathode pin of the CRT connector. This is done to minimize the length of the video path between these two components. Note also that D8, D9, R24 and D6 are placed to minimize the size of the video nodes that they are attached to. This minimizes parasitic capacitance in the video path and also enhances the effectiveness of the protection diodes. The anode of protection diode D8 is connected directly to a section of the the ground plane that has a short and direct path to the LM2466 ground pins. The cathode of D9 is connected to  $V_{\mbox{\scriptsize CC}}$  very close to decoupling capacitor C19 (see Figure 14) which is connected to the same section of the ground plane as D8. The diode placement and routing is very important for minimizing the voltage stress on the LM2466 during an arcover event. Lastly, notice that S3 is placed very close to the blue cathode and is tied directly to CRT ground.

# - RVIDEO OUT | DACTOUT | | DACZOUT | | ξŮ [B] + 538 47⊌F 130K R16 — C49 B VIDEO OUT -DIGITAL GND -DAC 1 OUT -DAC 3 OUT -DAC 4 OUT --Application Hints (Continued)

FIGURE 11. LM126X/LM246X Demonstration Board Schematic

FIGURE 12. LM126X/LM246X Demonstration Board Schematic (continued)

FIGURE 13. LM126X/LM246X Demo Board Layout

FIGURE 14. Trace Routing and Component Placement for Blue Channel Output

# **Physical Dimensions** inches (millimeters) unless otherwise noted

CONTROLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS

TA09A (Rev C)

CONTROLLING DIMENSION IS INCH VALUES IN [ ] ARE MILLIMETERS

> **NS Package Number TA09A** Order Number LM2466TA

#### **Notes**

#### **LIFE SUPPORT POLICY**

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Email: support@nsc.com

www.national.com

National Semiconductor Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466 Fax: 65-2504466

Email: ap.support@nsc.com

**National Semiconductor** Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507