捷多邦,专业PCB打样工厂,24小时加急出货

PORTABLE PENTIUM<sup>®</sup> II & III POWER SUPPLY CONTROLLER

SC1406A

January 28, 2000

TEL:805-498-2111 FAX:805-498-3804 WEB:http://www.semtech.com

## DESCRIPTION

The SC1406A is a High Speed, High performance Hysteretic Mode controller. It is part of a two chip solution, with the SC1405 Smart Driver, providing power to advanced micro-processors. It uses a Dynamic Set Point switching technique along with an ultra-fast comparator to provide the control signal to an external high speed Mosfet driver. A 5-bit DAC sets the output voltage, thus providing a voltage resolution of 25mV.

SC1406A has two on-chip linear regulators which drive external PNP transistors with output voltage settings of 1.5V and 2.5Vdc. The linear regulator drivers have a separate soft start. A PWRGD TTL level signal is asserted when all voltages are within specifications. The part features Low Battery Detect and Undervoltage Lock-Out for the main Hysteretic controller to assure V-DC is within acceptable limits. An Over-Current comparator disables the main controller during an overcurrent condition using an externally programmable threshold.

### **FEATURES**

- High Speed Hysteretic controller provides high efficiency over a wide operating load range

- Inherently stable

- Complete power solution with two LDO drivers

- Programmable output voltage for Pentium<sup>®</sup> II & III Processors

### APPLICATIONS

- Laptop and Notebook computers

- High performance Microprocessor based systems

- High efficiency distributed power supplies

### ORDERING INFORMATION

| DEVICE     | PACKAGE  | TEMP. (T <sub>J</sub> ) |  |  |

|------------|----------|-------------------------|--|--|

| SC1406ACTS | TSSOP-28 | 0 - 125°C               |  |  |

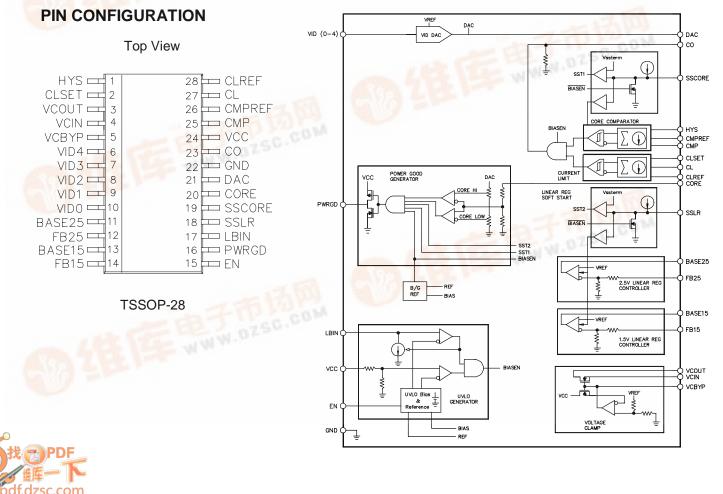

# BLOCK DIAGRAM

1

# **PIN DESCRIPTION**

| Pin | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | HYS      | Core comparator hysteresis settling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2   | CLSET    | Current limit setting pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3   | VCOUT    | Voltage clamp output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4   | VCIN     | Voltage clamp input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5   | VCBYP    | Voltage clamp bypass pin. Needs to have a 1500pF cap from this pin to ground to ensure proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6   | VID4     | VID most significant bit main controller voltage programming DAC input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7   | VID3     | VID input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8   | VID2     | VID input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9   | VID1     | VID input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10  | VID0     | VID least significant bit main controller voltage programming DAC input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11  | BASE25   | 2.5V Linear regulator drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12  | FB25     | 2.5V Linear regulator output feedback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13  | BASE15   | 1.5V Linear regulator drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14  | FB15     | 1.5V Linear regulator output feedback.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15  | EN       | Enable. SC1406A is enabled when this signal is High. This is capable of accepting 5.0V signal level. When used with the SC1405 driver, this pin can be connected to the PWRDY pin of the SC1405 to include UVLO feature on the V_5 (Intel Smart Driver's $V_{cc}$ ).                                                                                                                                                                                                                                                                                                                                             |

| 16  | PWRGD    | Power Good. When the main converter output approaches and stays within ±12% of the VID DAC setting, and both soft-start circuits periods for the main core controller and linear regulator controllers have been terminated, this signal is driven high to VCC level. During UVLO, this signal is undefined.                                                                                                                                                                                                                                                                                                     |

| 17  | LBIN     | Low battery input. This pin is used to set the minimum voltage to the converter through an external resistor divider. When the input to this pin is less than 1.225V, typical, Tamky is held in an Under-Voltage-Lock-Out mode regardless of the status of EN.                                                                                                                                                                                                                                                                                                                                                   |

| 18  | SSLR     | Linear regulators soft start. During power-up with EN high and not in UVLO, the external soft start capacitor (1200pF, typ) is charged by an internal 1µA current source to set the ramp up time of the linear regulator outputs, 1.5V and 2.5V. This ramp up time is typically 2ms, 6ms max. This is discharged through an internal switch when BIASEN is low, EN low or enter UVLO region. Enabling internal bias and soft start requires the pin voltage to drop below a threshold of 150mV typical (200mV max). Linear regulator soft start current tolerance tracks the core soft start current within 10%. |

| 19  | SSCORE   | Main controller CORE output soft start. During power-up with EN high and not in UVLO, the external soft start capacitor (1800pF, typ) is charged by an internal 1µA current source to set the ramp up time of the main converter output. This ramp up time is typically 3ms, 6ms max. This is discharged by an internal switch when BIASEN is low, EN pin is low or in UVLO. Enabling internal bias and soft start requires the pin voltage to drop below a threshold of 150mV typical (200mV max). Core soft start current tolerance tracks the LDO soft start current to within 10%.                           |

# **PIN DESCRIPTION (Cont.)**

| Pin | Pin Name | Pin Function                                                                                         |

|-----|----------|------------------------------------------------------------------------------------------------------|

| 20  | CORE     | Main CORE converter output feedback.                                                                 |

| 21  | DAC      | Main controller digital to analog output.                                                            |

| 22  | GND      | Ground                                                                                               |

| 23  | СО       | Comparator output. Main regulator controller output used to drive the input of the SC1405 driver IC. |

| 24  | VCC      | Input power. Supply voltage input. This input is capable of accepting 3.3V or 5.0V supply voltage.   |

| 25  | CMP      | Core comparator input pin.                                                                           |

| 26  | CMPREF   | Core comparator reference input pin.                                                                 |

| 27  | CL       | Current limit input pin.                                                                             |

| 28  | CLREF    | Current limit reference input pin.                                                                   |

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                               | SYMBOL              | MAXIMUM                            | UNITS |

|-----------------------------------------|---------------------|------------------------------------|-------|

| VCC Supply Voltage                      | Vmax <sub>vcc</sub> | 7                                  | V     |

| Low Battery Input                       | LBIN                | 7                                  | V     |

| Input & Output Pins                     |                     | V <sub>cc</sub> + 0.3<br>GND - 0.3 | V     |

| Enable                                  | EN                  | 7                                  | V     |

| Operating Junction Temperature          | TJ                  | 0 to +125                          | °C    |

| Lead Temperature (Soldering) 10 seconds | TL                  | 300                                | °C    |

| Storage Temperature                     | T <sub>STG</sub>    | -65 to 150                         | °C    |

## **ELECTRICAL CHARACTERISTICS**

Unless specified:  $0 < T_A < 100^{\circ}C$ ;  $V_{CC} = 3.3V$  (See Note 1)

| PARAMETER                                         | SYMBOL                              | CONDITIONS                                               | MIN                      | TYP   | MAX                  | UNITS |

|---------------------------------------------------|-------------------------------------|----------------------------------------------------------|--------------------------|-------|----------------------|-------|

| SUPPLY, BIAS, UVLO, VD                            | C MONITOR                           | AND POWERGOOD                                            |                          |       | 1                    |       |

| Supply (VCC, GND)                                 |                                     |                                                          |                          |       |                      |       |

| VCC Supply Voltage<br>Range                       | V <sub>CCMAX</sub>                  |                                                          | 3.0                      | 3.3   | 6.0                  | V     |

| VCC Quiescent Current                             | I <sub>CCQ</sub>                    | EN is low, $3.0V \le V_{CC} \le 3.6V$                    |                          |       | 10                   | μA    |

|                                                   |                                     | EN is high and in UVLO                                   |                          |       | 350                  |       |

| VCC Operating Current                             | I <sub>cc</sub>                     | EN is high                                               |                          | 10.0  | 15                   | mA    |

| Under Voltage Lock Out C                          | ircuit                              |                                                          | •                        |       |                      | •     |

| Threshold                                         | V <sub>HCC</sub>                    |                                                          |                          |       | 2.95                 | V     |

|                                                   | V <sub>LCC</sub>                    |                                                          | 2.7                      |       |                      |       |

| Hysteresis                                        | V <sub>HYSTCC</sub>                 |                                                          | 20                       |       |                      | mV    |

| Enable Input                                      |                                     |                                                          |                          |       |                      |       |

| Input High                                        | Vih                                 | $3.0 \le V_{CC} \le 5V$                                  | 0.7*V <sub>CC</sub>      |       |                      | V     |

| Input Low                                         | Vil                                 |                                                          |                          |       | 0.8                  | V     |

| Low Battery Monitor                               |                                     |                                                          |                          |       | L                    |       |

| Threshold                                         | V <sub>THDC</sub>                   |                                                          | 1.175                    | 1.225 | 1.275                | V     |

| Input Bias Current                                | I <sub>BDC</sub>                    | $V_{LB_{IN}} > V_{THDC}$                                 |                          |       | ±0.3                 | μA    |

|                                                   |                                     | $V_{LB_{IN}} < V_{THDC}$                                 | 0.6                      | 1.0   | 10.5                 |       |

| VCORE Power Good Gene                             | erator                              |                                                          |                          |       |                      |       |

| Input Threshold                                   | V <sub>HCORE</sub>                  | V <sub>DAC</sub> = 0.9V - 1.675V                         | 1.08*V <sub>cc</sub>     |       | 1.12*V <sub>cc</sub> | V     |

|                                                   | V <sub>LCORE</sub>                  |                                                          | 0.88*V <sub>CC</sub>     |       | 0.92*V <sub>CC</sub> | V     |

| Output Voltage                                    | V <sub>HPWRGD</sub><br>(Active Hi)  | $I_{PWRGD}$ = 10µa (source) EN is high                   | 0.95*<br>V <sub>cc</sub> |       |                      | V     |

| Note that during the<br>latency time of any VID   | V <sub>LPWRGD</sub><br>(Active low) | $I_{PWRGD} = 10\mu A$ (sink), EN is high                 |                          |       | 0.4                  | V     |

| code change, the PWRGD output signal is not valid | V <sub>PWRGD</sub>                  | I <sub>PWRGD</sub> = 10μA (sink), UVLO                   |                          |       | 0.8                  | V     |

|                                                   | V <sub>OUT</sub>                    | During the latency time (50µs) of<br>any VID code change |                          |       |                      |       |

Note 1: Specification refers to application circuit (Figure 1.).

# **ELECTRICAL CHARACTERISTICS (CONT.)**

Unless specified:  $-0 < T_A < 100^{\circ}$ C;  $V_{CC} = 3.3$ V (See test circuit)

| PARAMETER                                                                                            | SYMBOL                                                                                                                                                                    | CONDITIONS                                                                                                                 | MIN          | TYP          | MAX          | UNITS |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|-------|

|                                                                                                      | CORE CO                                                                                                                                                                   | ONVERTER CONTROLLER                                                                                                        |              | 1            |              |       |

| Core Converter Soft Start Current                                                                    |                                                                                                                                                                           |                                                                                                                            |              |              |              |       |

| Core Converter Soft Start Current                                                                    | I <sub>SSCORE</sub> Charge (Source) current                                                                                                                               |                                                                                                                            | 0.6          | 1            | 1.45         | μA    |

|                                                                                                      |                                                                                                                                                                           | Discharge (Sink) current                                                                                                   | 0.30         | 1            |              | mA    |

| V <sub>SSCORE</sub> Soft Start Termination<br>Threshold                                              | V <sub>SSTERM</sub>                                                                                                                                                       |                                                                                                                            | 1.53         | 1.70         | 1.87         | V     |

| V <sub>SSCORE</sub> Discharge Threshold                                                              | V <sub>SSDIS</sub>                                                                                                                                                        |                                                                                                                            |              | 150          | 400          | mV    |

| VID DAC                                                                                              |                                                                                                                                                                           |                                                                                                                            |              |              |              |       |

| VID Input Threshold                                                                                  | $V_{\text{VID}_{\text{IH}}}$                                                                                                                                              | $3.0V < V_{CC} < 3.6V$                                                                                                     | $0.7*V_{CC}$ |              |              | V     |

|                                                                                                      | V <sub>VID_IL</sub>                                                                                                                                                       |                                                                                                                            |              |              | 0.8          | -     |

| VID Input-Pull-up Current,VID (0-4)                                                                  | I <sub>VID</sub>                                                                                                                                                          | VID (0-4) = 0000011111                                                                                                     | 6            |              | 40           | μA    |

| Output Voltage Accuracy                                                                              | $V_{DAC\_ERR}$                                                                                                                                                            | $I_{DAC} = 0, VID(0-4) = 0000011111$                                                                                       | -0.85        |              | +0.85        | %     |

| Settling Time*                                                                                       | t <sub>pdVID_DAC</sub>                                                                                                                                                    | C <sub>DAC</sub> = 1000pF<br>VID is set to change VCORE from<br>1.30V to 1.45V or 1.45V to 1.30V                           |              |              | 35           | μs    |

| CORE Comparator (CMP, CMPRE                                                                          | F, HYS, CO                                                                                                                                                                |                                                                                                                            |              |              |              |       |

| Input Bias Current                                                                                   | I <sub>BCMP</sub>                                                                                                                                                         | $V_{CMP} = V_{CMPREF} = 1.3V$                                                                                              |              |              | ±2           | μA    |

| Input Offset Voltage                                                                                 | V <sub>CPM-</sub><br>VCPMREF                                                                                                                                              | $V_{CMPREF} = 1.3V$                                                                                                        |              | ±1.5         | ±3           | mV    |

| Hysteresis Setting Current                                                                           |                                                                                                                                                                           | R <sub>HYS</sub> = open                                                                                                    |              |              | <u>+</u> 2   |       |

|                                                                                                      | I <sub>CMPREF</sub>                                                                                                                                                       | $R_{HYS} = 17k\Omega$                                                                                                      | ±85          | <u>+</u> 100 | <u>+</u> 115 | μA    |

|                                                                                                      |                                                                                                                                                                           | $R_{HYS} = 170 k\Omega$                                                                                                    | ±7           | <u>+</u> 10  | <u>+</u> 13  | -     |

| Output Voltage                                                                                       | V <sub>HCO</sub><br>CMP <cmpref< td=""><td>Load Impedance = 100k in parallel with 10pF, <math>V_{cc}</math> = 3.0V</td><td>2.5</td><td></td><td></td><td>V</td></cmpref<> | Load Impedance = 100k in parallel with 10pF, $V_{cc}$ = 3.0V                                                               | 2.5          |              |              | V     |

|                                                                                                      | V <sub>LCO</sub><br>CMP>CMPREF                                                                                                                                            | Load Impedance = 100k in parallel with 10pF, $V_{CC}$ = 3.6V                                                               |              |              | 0.4          | V     |

| Propagation Delay Time**<br>Measured at device pins, from the<br>trip point to 50% of CO transition. | T <sub>pd CMP-CO</sub>                                                                                                                                                    | $V_{CMPREF} = 1.3V \Delta V_{CMP} = +40mV$<br>step with +20mV, overdrive<br>$T_{A} = 25^{\circ}C,$<br>$T_{A} = full range$ |              |              | 20<br>30     | ns    |

|                                                                                                      |                                                                                                                                                                           | $V_{CMPREF} = 1.3V \Delta V_{CMP} = 40mV$<br>step with 20mV overdrive,<br>$T_{A} = 25^{\circ}C,$<br>$T_{A} = full range$   |              |              | 20<br>30     |       |

| Output Rise/Fall Times**<br>Measured between 30% and 70%<br>points of CO transition                  | T <sub>R</sub>                                                                                                                                                            | $C_{co} = 10 pF$<br>$V_{cc} = 3.0V$                                                                                        |              | 7            | 10           | ns    |

|                                                                                                      | T <sub>F</sub>                                                                                                                                                            | R <sub>co</sub> = 100K                                                                                                     |              | 7            | 10           | 1     |

# **ELECTRICAL CHARACTERISTICS (CONT.)**

Unless specified:  $-0 < T_A < 100^{\circ}$ C;  $V_{CC} = 3.3$ V (See test circuit)

| PARAMETER                                                                                                  | R SYMBOL CONDITIONS                     |                                                                                      |                                 | MIN   | TYP | MAX   | UNITS |  |  |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------|---------------------------------|-------|-----|-------|-------|--|--|

| Current Limit Comparator (CL, CLREF, CLSET)                                                                |                                         |                                                                                      |                                 |       |     |       |       |  |  |

| Input Bias Current                                                                                         | <u>+</u> I <sub>CL</sub>                | $V_{CS} = 1.3V$                                                                      |                                 |       |     | 5     | μA    |  |  |

| Current Limit Setting Current                                                                              | <b> </b> ±I <sub>CLREF</sub>            | $R_{CLSET} = open$                                                                   | $V_{CLREF}-V_{CL}$<br>= 10mV    |       |     | 7.5   | μA    |  |  |

| *The Tamky device is required to meet the CL setting current                                               |                                         |                                                                                      | $V_{CLRER} - V_{CL}$<br>= -10mV |       |     | 5.0   |       |  |  |

| requirements for $R_{CLSET}$ of "17k $\Omega$ and 170k $\Omega$ or "42.5k $\Omega$ and                     |                                         | $R_{CLSET} = 17k\Omega*$                                                             | $V_{CLREF} - V_{CL}$<br>= 10mV  | 262.5 | 300 | 337.5 | μA    |  |  |

| 20k $\Omega$ ". Supplier production testing will use the 17k $\Omega$ /170k $\Omega$                       |                                         |                                                                                      | $V_{CLREF} - V_{CL}$<br>= -10mV | 175   | 200 | 225   |       |  |  |

| combination or the 42.5k $\Omega$ /20k $\Omega$ combination.                                               |                                         | $R_{CLSET} = 170 k\Omega *$                                                          | $V_{CLREF} - V_{CL}$<br>= 10mV  | 19.5  | 30  | 40.5  | μA    |  |  |

|                                                                                                            |                                         |                                                                                      | $V_{CLREF} - V_{CL}$<br>= -10mV | 13    | 20  | 27    |       |  |  |

|                                                                                                            |                                         | $R_{CLSET} = 42.5 k\Omega *$                                                         | $V_{CLRER} - V_{CL}$<br>= 10mV  | 100.5 | 120 | 139.5 | μA    |  |  |

|                                                                                                            |                                         |                                                                                      | $V_{CLRER} - V_{CL}$<br>= -10mV | 67    | 80  | 93    |       |  |  |

|                                                                                                            |                                         | $R_{CLSET} = 20k\Omega*$                                                             | $V_{CLREF}-V_{CL}$<br>= 10mV    | 222   | 255 | 288   | μA    |  |  |

|                                                                                                            |                                         |                                                                                      | $V_{CLRER} - V_{CL}$<br>= -10mV | 148   | 170 | 192   |       |  |  |

| Input Offset Voltage                                                                                       | V <sub>cl -</sub><br>V <sub>clref</sub> | $V_{CLREF} = 1.3V$                                                                   |                                 |       | ±4  | ±6    | mV    |  |  |

| Propagation Delay Time**<br>Measured at the device pins, from<br>the trip point to 50% of CO<br>transition | T <sub>pd_CL-CO</sub>                   | $V_{CMPREF} = 1.3V, \Delta V_{CMP} =$<br>step with +20mV ove<br>$T_A = 25^{\circ}C,$ |                                 |       |     | 100   |       |  |  |

|                                                                                                            |                                         | T <sub>A</sub> = full range                                                          | •                               |       |     | 150   | ns    |  |  |

|                                                                                                            |                                         | $V_{CMPREF} = 1.3V, \Delta V$<br>-50mV step with -20mV<br>$T_A = 25^{\circ}C,$       |                                 |       |     | 100   |       |  |  |

|                                                                                                            |                                         | T <sub>A</sub> = full range                                                          | •                               |       |     | 150   |       |  |  |

# **ELECTRICAL CHARACTERISTICS (CONT.)**

Unless specified: -0 <  $T_{\rm A}$  < 100°C;  $V_{\rm CC}$  = 3.3V (See test circuit)

| PARAMETER                                                                                                                               | AMETER SYMBOL CONDITIONS                      |                                                                                                                                                                                                                                            | MIN                 | TYP               | MAX  | UNIT  |    |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|------|-------|----|

|                                                                                                                                         | LINEAR R                                      | EGULATOR CONTRO                                                                                                                                                                                                                            | LLERS               |                   |      |       |    |

| 1.5V Linear Regulator Controller                                                                                                        |                                               |                                                                                                                                                                                                                                            |                     |                   |      |       |    |

| Input Bias Current                                                                                                                      | I <sub>LR15</sub>                             | V <sub>FB_15</sub> = 1                                                                                                                                                                                                                     | .5V                 |                   |      | 1     | mA |

| Output Voltage<br>$C_{0_{-1.5}} = 56\mu$ F, 20m $\Omega$ ESR max<br>or 150 $\mu$ F, 45m $\Omega$ ESR max<br>Capacitance tolerance = 20% | V <sub>0_1.5,</sub><br>Imin =<br>0.1mA        | $I_{o}$ = 500mA, pnp BJT with $B_{MIN} \ge 50$ @<br>$I_{c}$ = 500mA                                                                                                                                                                        |                     |                   | 1.50 | 1.54  | V  |

| Base Drive Output Current                                                                                                               | I <sub>BASE_1.5</sub>                         | @ 25°0                                                                                                                                                                                                                                     | C                   | 10                |      | 120   | mA |

| 2.5V Linear Regulator Controller                                                                                                        |                                               |                                                                                                                                                                                                                                            |                     |                   |      |       |    |

| Input Bias Current                                                                                                                      | I <sub>LR25</sub>                             | V <sub>FB_25</sub> = 2                                                                                                                                                                                                                     | .5V                 |                   |      | 1     | mΑ |

| Output Voltage<br>$C_{0.2.5} = 1\mu$ Fceramic<br>ESR range = $1m\Omega - 30m\Omega$<br>Capacitance tolerance = 20%                      | V <sub>0_2.5,</sub><br>Imin = 0A<br>Imax=0.1A | 0                                                                                                                                                                                                                                          |                     |                   | 2.50 | 2.55  | V  |

| Base Drive Output Current                                                                                                               | I <sub>BASE_2.5</sub>                         |                                                                                                                                                                                                                                            |                     | 2.5               |      | 20    | mA |

| Linear Regulator Soft Start (LRS                                                                                                        | S)                                            |                                                                                                                                                                                                                                            |                     |                   |      |       |    |

| Linear Reg Soft-Start Current                                                                                                           | I <sub>LRSS</sub>                             | Charge Current, V <sub>LRSS</sub> = 0V                                                                                                                                                                                                     |                     | -0.6              | -1   |       | μA |

|                                                                                                                                         |                                               | Discharge Current,<br>EN is low or in                                                                                                                                                                                                      |                     | 0.3               | 1    |       | mA |

| Enable Threshold                                                                                                                        | $V_{SSLR_{EN}}$                               |                                                                                                                                                                                                                                            |                     |                   | 150  | 400   | mV |

| Soft Start Termination Threshold                                                                                                        | V <sub>TH_LRSS</sub>                          |                                                                                                                                                                                                                                            |                     | 1.53              | 1.70 | 1.87  | V  |

| Voltage Clamp (VCIN, VCOUT, V                                                                                                           | CBYP)                                         | I                                                                                                                                                                                                                                          |                     |                   |      |       |    |

| Input Voltage                                                                                                                           | V <sub>H_VCIN</sub>                           |                                                                                                                                                                                                                                            |                     | 0.93              | 1.5  | 1.60  | V  |

| Output Voltage<br>Imin = 10µA                                                                                                           | V <sub>H_VCOUT</sub>                          | $R_{VCOUT} = 150\Omega$<br>tied to V <sub>S</sub> = 2.5V<br>$I_{VGIN} = -10\mu A$                                                                                                                                                          | VCIN is open        | 0.8V <sub>s</sub> |      | Vs    | V  |

|                                                                                                                                         | V <sub>L_VCOUT</sub>                          |                                                                                                                                                                                                                                            | $V_{VCIN} = 0.175V$ |                   |      | 0.375 |    |

| Progagation Delay**                                                                                                                     | T <sub>pd</sub><br>VCIN_VCOUT                 | $R_{\text{VCOUT}} = 150\Omega \text{ tied to } V_{\text{S}} = 2.5\text{V}$ $C_{\text{VCBYP}} = 1500\text{pF}, \text{ VCIN steps from}$ $0.175\text{V to } 1.50\text{V and back.}$ Measured from 50% of VCIN step to 50% of VCOUT transient |                     |                   |      | 10    | ns |

\* Guaranteed by design.

\*\*Guaranteed by characterization.

SC1406A

January 28, 2000

# VID vs. $V_{\text{DAC}}$ VOLTAGE

|   |   | VID |   |   | MIN                 | ТҮР         | МАХ                 |

|---|---|-----|---|---|---------------------|-------------|---------------------|

| 4 | 3 | 2   | 1 | 0 | 1% < V <sub>o</sub> | Vo          | 1% > V <sub>o</sub> |

| 0 | 0 | 0   | 0 | 0 | 1.658               | 1.675       | 1.692               |

| 0 | 0 | 0   | 0 | 1 | 1.633               | 1.633 1.650 |                     |

| 0 | 0 | 0   | 1 | 0 | 1.609               | 1.625       | 1.641               |

| 0 | 0 | 0   | 1 | 1 | 1.584               | 1.600       | 1.616               |

| 0 | 0 | 1   | 0 | 0 | 1.560               | 1.575       | 1.591               |

| 0 | 0 | 1   | 0 | 1 | 1.534               | 1.550       | 1.565               |

| 0 | 0 | 1   | 1 | 0 | 1.510               | 1.525       | 1.540               |

| 0 | 0 | 1   | 1 | 1 | 1.485               | 1.500       | 1.515               |

| 0 | 1 | 0   | 0 | 0 | 1.460               | 1.475       | 1.490               |

| 0 | 1 | 0   | 0 | 1 | 1.435               | 1.450       | 1.464               |

| 0 | 1 | 0   | 1 | 0 | 1.411               | 1.425       | 1.439               |

| 0 | 1 | 0   | 1 | 1 | 1.386               | 1.400       | 1.414               |

| 0 | 1 | 1   | 0 | 0 | 1.361               | 1.375       | 1.389               |

| 0 | 1 | 1   | 0 | 1 | 1.336               | 1.350       | 1.363               |

| 0 | 1 | 1   | 1 | 0 | 1.312               | 1.325       | 1.338               |

| 0 | 1 | 1   | 1 | 1 | 1.287               | 1.300       | 1.313               |

| 1 | 0 | 0   | 0 | 0 | 1.262               | 1.275       | 1.288               |

| 1 | 0 | 0   | 0 | 1 | 1.237               | 1.250       | 1.262               |

| 1 | 0 | 0   | 1 | 0 | 1.213               | 1.225       | 1.237               |

| 1 | 0 | 0   | 1 | 1 | 1.188               | 1.200       | 1.212               |

| 1 | 0 | 1   | 0 | 0 | 1.163               | 1.175       | 1.187               |

| 1 | 0 | 1   | 0 | 1 | 1.138               | 1.150       | 1.161               |

| 1 | 0 | 1   | 1 | 0 | 1.114               | 1.125       | 1.136               |

| 1 | 0 | 1   | 1 | 1 | 1.089               | 1.100       | 1.111               |

| 1 | 1 | 0   | 0 | 0 | 1.064               | 1.075       | 1.086               |

| 1 | 1 | 0   | 0 | 1 | 1.039               | 1.050       | 1.060               |

| 1 | 1 | 0   | 1 | 0 | 1.015               | 1.025       | 1.035               |

| 1 | 1 | 0   | 1 | 1 | 0.99                | 1.00        | 1.01                |

| 1 | 1 | 1   | 0 | 0 | 0.965               | 0.975       | 0.984               |

| 1 | 1 | 1   | 0 | 1 | 0.940               | 0.950       | 0.959               |

| 1 | 1 | 1   | 1 | 0 | 0.916               | 0.925       | 0.934               |

| 1 | 1 | 1   | 1 | 1 | 0.891               | 0.900       | 0.909               |

January 28, 2000

### FUNCTIONAL DESCRIPTION

#### SUPPLY

The chip is optimized to operate from a  $3.3V \pm 5\%$  rail but is also designed to work up to 6V maximum supply voltage. If V<sub>CC</sub> is out of the  $3.3V \pm 5\%$  voltage range, the quiescent current will increase somewhat and slight degradation of line regulation is expected.

#### UNDER VOLTAGE LOCK-OUT CIRCUIT

The under voltage lockout circuit consists of two comparators, the low battery and low  $V_{CC}$  (low supply voltage) comparators. The output of the comparator gated with the Enable signal turns on or off the internal bias, enables or disables the CO output, and initiates or resets the soft start timers.

#### POWER GOOD GENERATOR

If the chip is enabled but not in UVLO condition, and the core voltage gets within  $\pm 10\%$  of the VID programmed value, then a high level Power Good signal is generated on the PWRGD pin to trigger the CPU power up sequence. If the chip is either disabled or enabled in UVLO condition, then PWRGD stays low. This condition is satisfied by the presence of an internal 200k $\Omega$  pull-down resistor connected from PWRGD to ground.

During soft start, PWRGD stays low independently from the status of Vcore voltage. During this time, PWRGD status is "don't care".

#### **BAND GAP REFERENCE**

A better than  $\pm 1\%$  precision band gap reference acts as the internal reference voltage standard of the chip, which all critical biasing voltages and currents are derived from. All references to VREF in the equations to follow will assume V<sub>REF</sub> = 1.7V.

#### CORE CONVERTER CONTROLLER

#### **Precision VID DAC Reference**

The 5-bit digital to analog converter (DAC) serves as the programmable reference source of the core comparator. Programming is accomplished by CMOS logic level VID code applied to the DAC inputs. The VID code vs. the DAC output is shown in the Output Voltage Table. The accuracy of the VID DAC is maintained on the same level as the band gap reference. There is a 10 $\mu$ A pull-up current on each DAC input while EN is high.

#### **Core Comparator**

This is an ultra-fast hysteretic comparator with a typical propagation delay of approximately 20ns at a 20mV overdrive. Its hysteresis is determined by the resistance ratio of two external resistors,  $R_{HYS}$  and  $R_{OH}$ , and the high accuracy internal reference voltage,  $V_{REF}$ .

$$V_{HYS} = \frac{R_{OH}}{R_{HYS}} \bullet V_{REF}$$

This chip can be used in standard hysteretic mode controller configuration and in DSPS (Dynamic Set Point Switching) hysteretic controller scheme.

In standard hysteretic controller configuration, the core comparator compares the output voltage of the core converter,  $V_{\text{CORE}}$  to the VID code programmed DAC voltage,  $V_{\text{DAC}}$ .

$$V_{CORE}(t) = V_{DAC} + V_{HYST}(t)$$

The core voltage ramps up and down between the two thresholds determined by the hysteresis of the comparator:

$$V_{HCORE} = V_{DAC} + V_{HYST}$$

$V_{LCORE} = V_{DAC} - V_{HYST}$

In DSPS hysteretic controller configuration, the core comparator compares the core voltage,  $V_{CORE}$ , not to the DAC voltage,  $V_{DAC}$  directly but rather to a voltage less than the DAC voltage by a DSPS voltage,  $V_{DSPS}$ .

$V_{CORE}(t) = V_{DAC} - V_{DSPS}(t) + V_{HYST}(t)$

The DSPS voltage is a function of the load current. It is generated from the current sense voltage,  $V_{CS}$ , developed across a sense resistor,  $R_{CS}$ , which is inserted in series with the main buck inductor and also used for current sensing for the cycle-by-cycle current limiting. The sense voltage is scaled up by the DSPS gain,  $A_{DSPS}$ , which is set by the resistance ratio of two external resistors,  $R_{DAC}$  and  $R_{CORE}$ .

$$V_{\text{DSPS}}(t) = A_{\text{DSPS}} \bullet V_{\text{CS}}(t) = (1 + \frac{R_{\text{DAC}}}{R_{\text{CORE}}}) \bullet R_{\text{CS}} \bullet i_{\text{CORE}}(t)$$

January 28, 2000

# In DSPS hysteretic controller configuration (Cont'd)

The comparator reference voltage positioning is such that an increasing current sense voltage, VCS, i,e, an elevating load current, causes the reference voltage to decrease, and as a consequence, the core output voltage also droops. At no load current, there is no droop while a maximum load, the droop is likewise maximum.

In order for the core voltage to be positioned around the nominal  $V_{DAC}$  voltage symmetrically and not just one way downward from the nominal value, a DSPS offset voltage,  $V_{DSPSOFFS}$ , can be introduced. The offset voltage moves the comparator reference voltage upward at no load. At optimal offsetting, the reference voltage is above the nominal level for load currents less than half of the maximum load, and below the nominal value for currents higher than that. The maximum amount of core voltage positioning can be determined from the constrain which says the output voltage at no load condition must still remain below the upper threshold of the core voltage regulation window, and at maximum load, it must be above the lower threshold.

The offset voltage can be generated across a resistor,  $R_{OH}$ , which is also used to create the hysteresis voltage by forcing a unipolar DSPS offsetting current through it. The offsetting current is conveniently provided by a high value resistor,  $R_{OFFSET}$ , connected from the comparator CMP pin to the ground.

$$V_{DSPSOFFS} = R_{OH} \bullet I_{DSPS} = R_{OH} \bullet \frac{V_{CS} + V_{CORE}}{R_{OH} + R_{OFFSET}}$$

$$VCS << VCORE, VCORE = VDAC, ROH << ROFFSET \approx \frac{R_{OH}}{R_{OFFSET}} \bullet V_{DAC}$$

In DSPS hysterestic controller configuration, the comparator thresholds can be calculated from the DAC voltage, V<sub>DAC</sub>, the DSPS offsetting voltage, V<sub>DSPSOFFS</sub>, the DSPS voltage V<sub>DSPS</sub>, and the bipolar hysteresis voltage, V<sub>HYST</sub> by summing them at the comparator inputs at the appropriate load current levels:

#### **Core Voltage Offsetting**

In order for the core voltage to be positioned around the nominal  $V_{DAC}$  voltage symmetrically and not just always one direction downward, a core offset voltage,  $V_{OFFS}$  can be introduced. The offset voltage moves the comparator reference voltage upwards. Using optimal offsetting, the core comparator reference voltage will be above the VID programmed nominal DAC voltage for load currents less than half of the maximum load, and below that for higher current. The maximum amount of the core voltage positioning can be determined from the constraint that the output voltage regulation window, and at maximum load, it has to be above the lower threshold.

The positioning offset voltage can be generated across the same resistor, ROH also used to create the hysteresis voltage, by forcing a unipolar offsetting current through it. The offsetting current is conveniently provided by a high value resistor, ROFFS connected from the comparator CMP pin to the ground.

#### **Current Limit Comparator**

The current limit comparator monitors the core converter output current and turns the high side switch off when the current exceeds the upper current limit threshold, VHCL and re-enable only if the load current drops below the lower current limit threshold, VLCL. The current is sensed by monitoring the voltage drop across the current sense resistor,  $R_{CS}$ , connected in series with the core converter main inductor (the same resistor used for DSPS input signal generation). The thresholds have the following relationships:

$$V_{HCL} = 3 \bullet \frac{R_{CLOH}}{R_{CLSET}} \bullet V_{REF}$$

$$V_{LCL} = 2 \bullet \frac{R_{CLOH}}{R_{CLSET}} \bullet V_{REF}$$

$$V_{HYSCL} = \frac{R_{CLOH}}{R_{CLSET}} \bullet V_{REF}$$

$$Vcore := \frac{Vdac \bullet (Roffset + Roh) \bullet Rcore - Rcs \bullet Icore \bullet Roffset \bullet (Rcore + Rdac)}{Rcore \bullet Roffset - Rdac \bullet Roh}$$

$$\Delta Vcore := 2 \bullet Vhys \bullet \frac{Rcore \bullet (Roffset + Roh)}{Rcore \bullet Roffset - Rdac \bullet Roh} \bullet \frac{Re sr}{Re sr + \frac{Rcore \bullet (Roffset + Roh)}{Rcore \bullet Roffset - Rdac \bullet Roh}}$$

#### **Core Converter Soft Start Timer**

The main purpose of this block is to control the rampup time of the core voltage in order to reduce the initial inrush current on the core input voltage (battery) rail. The soft start circuit consists of an internal current source, external soft start timing capacitor, internal switch across the capacitor, and a comparator monitoring the capacitor voltage.

#### LINEAR REGULATOR CONTROLLER

#### 1.5V Linear Regulator

This block is a linear regulator controller, which drives an external PNP bipolar transistor as a pass element. The linear regulator is capable of delivering 500mA steady state DC current and should support transient current of 1A, assuming the output filtering capacitor is properly selected to provide enough charge for the duration of the load transient.

#### 2.5V Linear Regulator

This block is a low drop-out (LDO) linear regulator controller, which drives an external PNP bipolar transistor as a pass element. The LDO linear regulator is capable of delivering 100mA steady DC current and should support transient current of 100mA, assuming the output filtering capacitor is properly selected to provide enough charge for the duration of the load transient.

# **APPLICATION INFORMATION**

#### **Power on/off Sequence**

# V\_DC V\_5 VCC(V\_3) EN DAC CO Vcore,

1.5V, 2.5V

See Application note AN99-12 for further information.

#### Linear Regulator Soft Start Timer

A soft start timer circuit of the linear regulators is similar to that of the core converter, and is used to control the ramp up time of the linear regulator output voltages. For maximum flexibility in controlling the start up sequence, the soft start function of the linear regulators is separated from that of the core converter.

#### **VOLTAGE CLAMP**

The level translator converts an input voltage swing on the IO rail, into a voltage swing on the CLK or VCC rail depending on where the open drain output of the translator is tied to through an external pull-up resistor. The level translator has to track the input in phase, and must be able to switch in 5ns (typical) following an input threshold intercept.

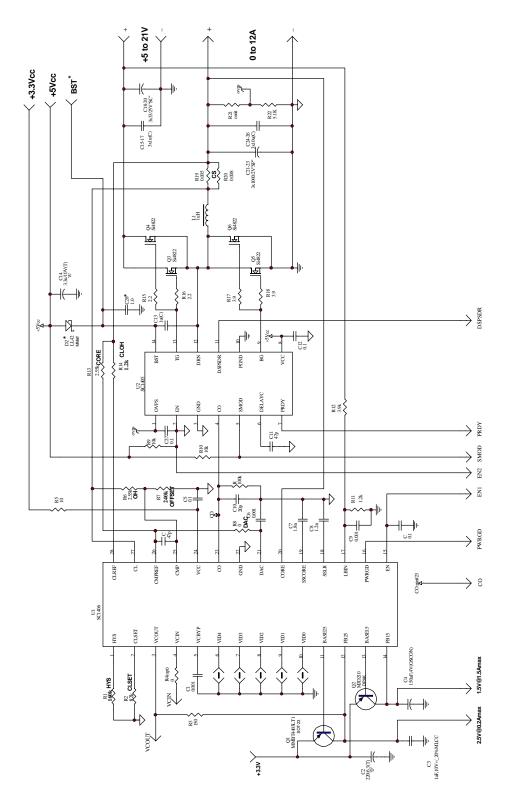

# **TYPICAL APPLICATION SCHEMATIC**

Refer to application note AN99-12 for further information.

12

January 28, 2000

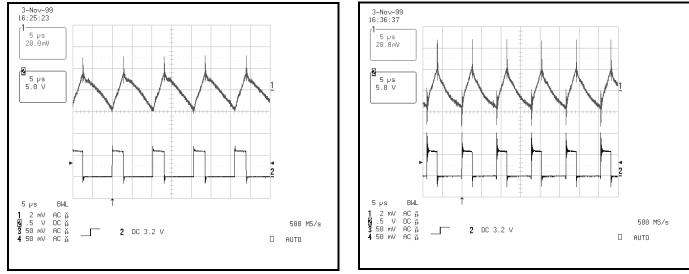

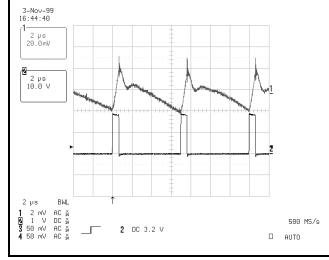

$V_{OUT} = 1.6V, I_{OUT} = 2.0A$

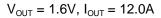

$V_{OUT} = 1.6V, I_{OUT} = 12.0A$

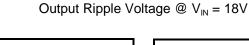

$V_{OUT} = 1.6V, I_{OUT} = 2.0A$

#### Load Regulation & Efficiency

$V_{IN} = 12V, V_{O} = 1.6V$

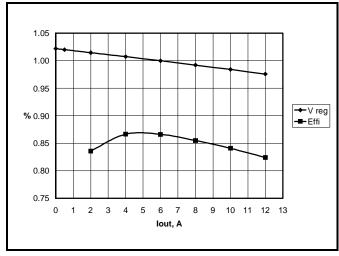

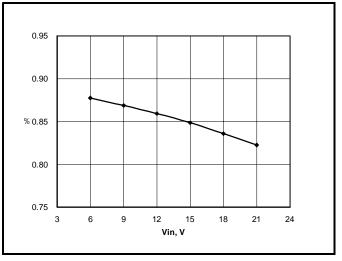

Line Regulation & Efficiency

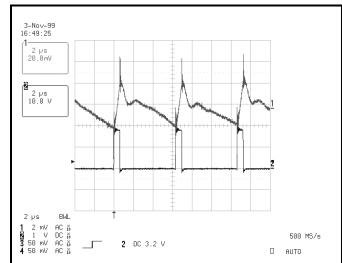

$V_{OUT} = 1.6V, I_{OUT} = 8.0A$

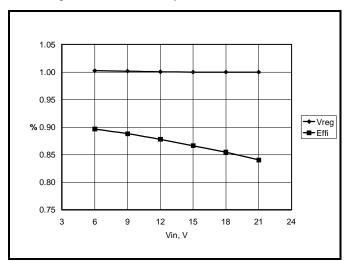

Efficiency vs Output Voltage

$V_{\text{IN}} = 12V, \ I_{\text{OUT}} = 8.0A$

Efficiency vs Input Line

SC1406A

#### January 28, 2000

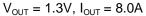

Supply Current vs V<sub>IN</sub>, Temperature @ UVLO mode

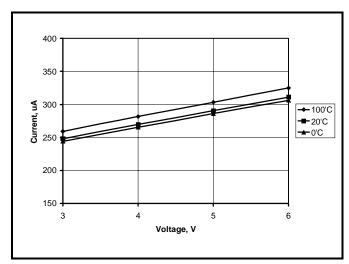

Supply Current vs V<sub>IN</sub>. Temperature @ Operating mode

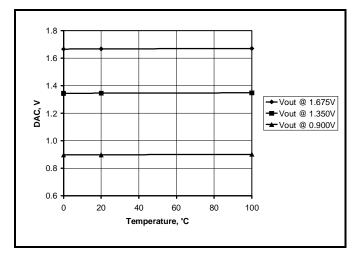

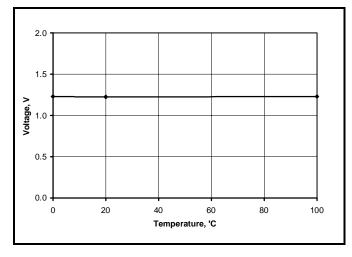

### DAC Output vs Temperature

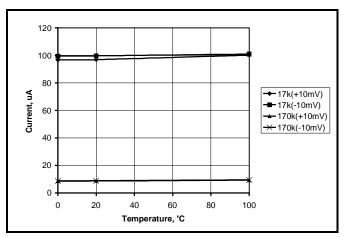

Hysteresis Setting Current vs Temperature

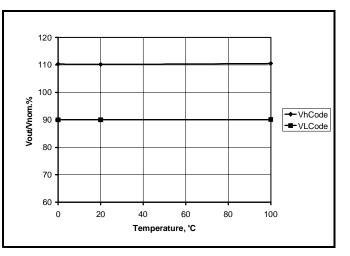

Power Good Threshold vs Temperature

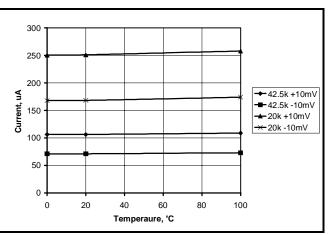

#### Current Limit Threshold vs Temperature

SC1406A

January 28, 2000

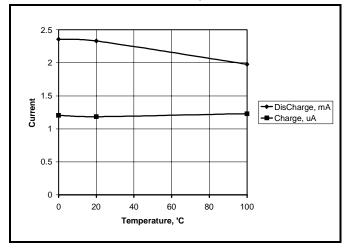

Core Soft Start Current vs Temperature

#### Low Battery Monitor Threshold vs Temperature

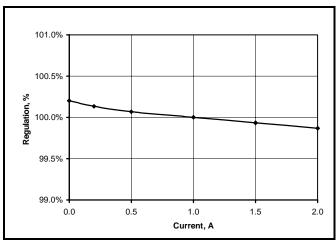

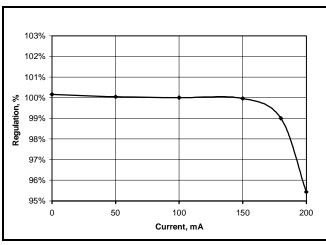

### I/O LDO Load Regulation-Normalized for 1A

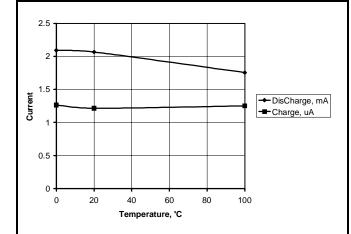

LDOs Soft Start Current vs Temperature

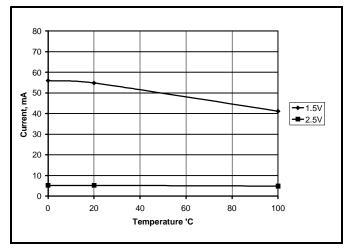

#### LDOs Drive Currents vs Temperature

#### CLK LDO Load Regulation-Normalized for 100mA

SC1406A

January 28, 2000

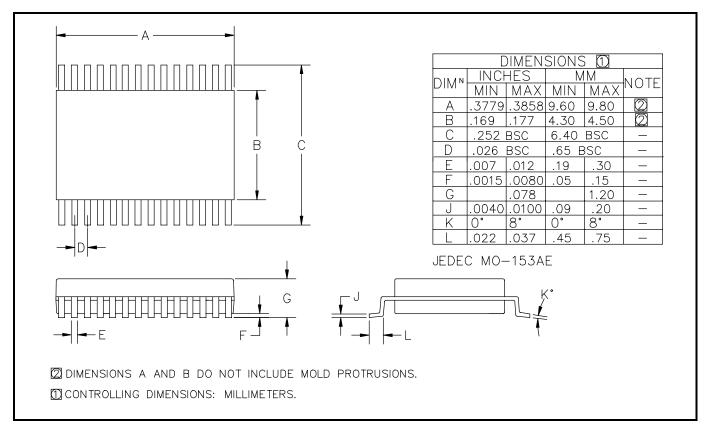

### **OUTLINE DRAWING - TSSOP-28**