# **Product Preview**

# Single-Chip 300-Baud Modem with DTMF Transceiver

The MC145446A is a silicon gate CMOS frequency shift keying (FSK) modern intended for use with telemeter systems or remote control systems over the telephone network. It replaces the MC145446.

This device is compatible with CCITT V.21 and contains the entire circuit that provides a full–duplex or half–duplex 300–baud data communication over a pair of telephone lines. This device also includes the DTMF generator/receiver and call progress tone detector (CPTD).

The differential line driver has the capability of driving 0 dBm into a  $600 \Omega$  load with a single 5 V power supply. The transmit level is controlled by the programmable attenuator in 1 dB steps.

This device also includes a serial control interface and internal control and status registers that permit a CPU to exercise the following built—in features:

- Single 5 V Power Supply

- Compatible with CCITT V.21

- DTMF Generator and Receiver for All 16 Standard Digits

- Capable of Driving 0 dBm into a 600 Ω Load (V<sub>CC</sub> = 5 V)

- AGC (Auto Gain Control) Amplifier for DTMF Receiver

- Imprecise Call Progress Tone (400 Hz) Detector

- A Transmit Attenuator Programmable in 1 dB Steps

- 2100 Hz Answer Tone Generator

- Serial Control Interface

17/96SC.COM

- · Analog Loopback Configuration for Self Test

- Power–Down Mode, Less than 1 μA

# MC145446A

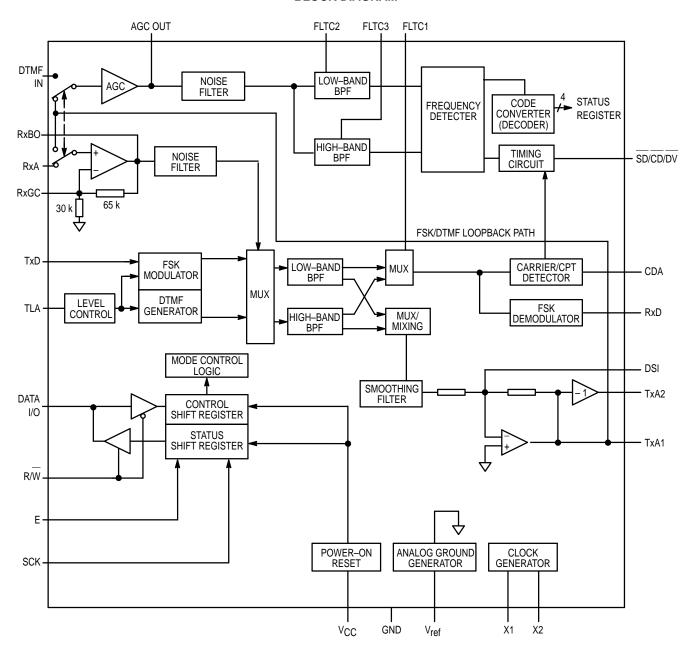

#### **BLOCK DIAGRAM**

#### ABSOLUTE MAXIMUM RATINGS (Voltages referenced to VSS)

| Rating                      | Symbol                            | Value                    | Unit |

|-----------------------------|-----------------------------------|--------------------------|------|

| DC Supply Voltage           | VCC                               | - 0.5 to 7.0             | V    |

| DC Input Voltage            | V <sub>in</sub>                   | $-0.5$ to $V_{CC} + 0.5$ | V    |

| DC Output Voltage           | V <sub>out</sub>                  | $-0.5$ to $V_{CC} + 0.5$ | V    |

| Clamp Diode Current per Pin | I <sub>IK</sub> , I <sub>OK</sub> | ± 20                     | mA   |

| DC Current per Pin          | l <sub>out</sub>                  | ± 25                     | mA   |

| Power Dissipation           | PD                                | 500                      | mW   |

| Storage Temperature Range   | T <sub>stg</sub>                  | - 65 to 150              | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid applications of any voltage higher than the maximum rated voltages to this high impedance circuit.

For proper operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \le (V_{in} \text{ or } V_{out}) \le V_{DD}$ . Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either  $V_{SS}$  or  $V_{DD}$ ).

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                   | Symbol           | Min | Тур      | Max | Unit |

|-----------------------------|------------------|-----|----------|-----|------|

| DC Supply Voltage           | Vcc              | 4.5 | 5        | 5.5 | V    |

| DC Input Voltage            | V <sub>in</sub>  | 0   | _        | Vcc | V    |

| DC Output Voltage           | V <sub>out</sub> | 0   | _        | Vcc | V    |

| Input Rise Time             | t <sub>r</sub>   | 0   | _        | 500 | ns   |

| Input Fall Time             | t <sub>f</sub>   | 0   | _        | 500 | ns   |

| Crystal Frequency           | f <sub>osc</sub> | _   | 3.579545 | 1   | MHz  |

| Operating Temperature Range | T <sub>A</sub>   | -20 | 25       | 70  | °C   |

## DC ELECTRICAL CHARACTERISTICS (VCC = $5.0~V \pm 10\%$ , TA = $-20~to~70^{\circ}C$ )

| Characteristic                  |          | Symbol          | Conditions                                        | Min                   | Тур                    | Max        | Unit |

|---------------------------------|----------|-----------------|---------------------------------------------------|-----------------------|------------------------|------------|------|

| Input Voltage                   | H Level  | VIH             |                                                   | 3.15                  | _                      | _          | V    |

|                                 | L Level  | V <sub>IL</sub> |                                                   | _                     | _                      | 1.1        | 1    |

| Output Voltage                  | H Level  | Voн             | I <sub>OH</sub> = 20 μA                           | V <sub>CC</sub> - 0.1 | V <sub>CC</sub> – 0.01 | _          | V    |

|                                 | L Level  | VOL             | I <sub>OL</sub> = 20 μA<br>I <sub>OL</sub> = 2 mA | _                     | 0.01<br>—              | 0.1<br>0.4 |      |

| Input Current TxD, E, SCK, DATA | I/O, R/W | l <sub>in</sub> | V <sub>in</sub> = V <sub>CC</sub> or GND          | _                     | ± 1.0                  | ± 10.0     | μΑ   |

| Quiescent Supply Current        |          | Icc             | FSK Mode                                          | _                     | 8                      | _          | mA   |

|                                 |          |                 | DCMF Receive Mode                                 | _                     | 10                     | _          | 1    |

| Power–Down Supply Current       |          | Icc             | Power–Down Mode 1                                 | _                     | _                      | 500        | μА   |

| Fower-Down Supply Current       |          |                 | Power–Down Mode 2                                 | _                     | _                      | 1          | μΑ   |

#### TRANSMIT CARRIER CHARACTERISTICS (V $_{CC}$ = 5.0 V $\pm$ 10%, T $_{A}$ = - 20 to 70°C)

| Characteristic                            |           | Symbol            | Conditions                                                     | Min  | Тур  | Max  | Unit |

|-------------------------------------------|-----------|-------------------|----------------------------------------------------------------|------|------|------|------|

| Carrier Frequency Channel 1               | Mark "1"  | f1M               | Crystal Frequency                                              | 974  | 980  | 986  | Hz   |

|                                           | Space "0" | f <sub>1S</sub>   | 3.579545 MHz                                                   | 1174 | 1180 | 1186 |      |

| Carrier Frequency Channel 2               | Mark "1"  | f <sub>2</sub> M  |                                                                | 1644 | 1650 | 1656 |      |

|                                           | Space "0" | f <sub>2</sub> S  |                                                                | 1844 | 1850 | 1856 |      |

| Answer Tone                               |           | fans              |                                                                | 2090 | 2100 | 2110 |      |

| Transmit Carrier Level                    |           | VO*               | Attenuator = 0 dB                                              | _    | 7    | _    | dBm  |

| Second Harmonic Energy Out-of-Band Energy |           | V <sub>2h</sub> * | $R_{TLA} = \infty$ , $R_L = 1.2 kΩ$ ,<br>$V_{TxA1} - V_{TxA2}$ | _    | - 46 | _    | dBm  |

|                                           |           | V <sub>OE</sub> * | 12/11 12/12                                                    |      | dBm  |      |      |

<sup>\*</sup>  $V_{TxA1} - V_{TxA2}$ ,  $R_L = 1.2 \text{ k}\Omega$

# TRANSMIT ATTENUATOR CHARACTERISTICS (V $_{CC}$ = 5.0 V $\pm$ 10%, $T_A$ = - 20 to 70°C)

| Characteristi       | С             | Symbol | Conditions | Min        | Тур | Max | Unit |

|---------------------|---------------|--------|------------|------------|-----|-----|------|

| Attenuator Range    |               | ARNG   |            | 0          | _   | 15  | dB   |

| Attenuator Accuracy | 1 dB – 5 dB   | AACC   |            | - 0.5      | _   | 0.5 | dB   |

|                     | 6 dB – 9 dB   |        |            | <b>–</b> 1 | _   | 1   | ]    |

|                     | 10 dB – 15 dB | 1      |            | - 1.7      | _   | 1   | 1    |

### RECEIVER CHARACTERISTICS (INCLUDES HYBRID, DEMODULATOR, AND CARRIER DETECTOR)

(V<sub>CC</sub> = 5.0 V  $\pm$  10%, T<sub>A</sub> = - 20 to 70°C)

| Characteristic                                      |                                       | Symbol             | Conditions                | Min  | Тур  | Max | Unit |

|-----------------------------------------------------|---------------------------------------|--------------------|---------------------------|------|------|-----|------|

| Input Impedance                                     |                                       | R <sub>IRX</sub>   | RxA Pin                   | 50   | _    | _   | kΩ   |

| Receiver Carrier Amplitude                          | Carrier Amplitude VIRX                | - 48               | _                         | - 12 | dBm  |     |      |

| Carrier Detect Threshold                            | OFF to ON                             | VCDON              | CDA = 1.2 5V              | _    | - 44 | _   | dBm  |

|                                                     | ON to OFF                             | <sup>V</sup> CDOF  | f <sub>in</sub> = 1.0 kHz | _    | - 47 | _   |      |

| Hysterisis (V <sub>CDON</sub> – V <sub>CDOF</sub> ) |                                       | HYS                | ]                         | 2    | _    | _   | dB   |

| Carrier Detect Timing                               | Carrier Detect Timing OFF to ON TCDON |                    | CD1 = 0, CD0 = 0          | _    | 450  | _   | ms   |

|                                                     |                                       |                    | CD1 = 0, CD0 = 1          | _    | 10   | _   |      |

|                                                     |                                       |                    | CD1 = 1, CD0 = 0          | _    | 10   | _   |      |

|                                                     |                                       |                    | CD1 = 1, CD0 = 1          | _    | 70   | _   |      |

| ON to OFF                                           |                                       | T <sub>CDOFF</sub> | CD1 = 0, CD0 = 0          | _    | 35   | _   |      |

|                                                     |                                       |                    | CD1 = 0, CD0 = 1          | _    | 35   | _   |      |

|                                                     |                                       |                    | CD1 = 1, CD0 = 0          | _    | 20   | _   | ]    |

|                                                     |                                       |                    | CD1 = 1, CD0 = 1          | _    | 15   | _   |      |

## CPTD CHARACTERISTICS (V $_{CC}$ = 5.0 V $\pm$ 10%, $T_{A}$ = - 20 to 70°C)

| Characteristic                   |           | Symbol            | Conditions               | Min | Тур  | Max | Unit |

|----------------------------------|-----------|-------------------|--------------------------|-----|------|-----|------|

| Bandpass Filter Center Frequency | 1         | f <sub>C</sub>    |                          | _   | 400  | _   | Hz   |

| Bandpass Filter – 3 dB Band Widt | h         | $\Delta$ BW       |                          | _   | 140  | _   | Hz   |

| Tone Detect Level                | OFF to ON | VTDON             | CDA = 1.25 V             | _   | - 44 | _   | dBm  |

|                                  | ON to OFF | VTDOF             | f <sub>in</sub> = 400 Hz | _   | - 47 | _   | ]    |

| Tone Detect Timing               | OFF to ON | T <sub>TDON</sub> |                          | _   | 10   | _   | ms   |

|                                  | ON to OFF | T <sub>TDOF</sub> |                          | _   | 25   | _   | 1    |

## DTMF TRANSMIT CHARACTERISTICS (V $_{CC}$ = 5.0 V $\pm$ 10%, $T_A$ = - 20 to 70°C)

| Characteristic              |            | Symbol          | Conditions                        | Min | Тур      | Max | Unit |

|-----------------------------|------------|-----------------|-----------------------------------|-----|----------|-----|------|

| Tone Output Level Low Group |            | V <sub>fl</sub> | Attenuator = 0 dB                 | _   | 2.5      | _   | dBm  |

|                             | High Group | V <sub>fh</sub> | Vfh RTLA = ∞<br>Crystal Frequency |     | 3.5      | _   |      |

| High Group Pre–Emphasis     |            | PE              | 3.579545 MHz                      | 0   | _        | 3   | dB   |

| DTMF Distortion             |            | DIST            | Single Tone Mode VTxA1 - VTxA2,   | _   | 5        | _   | %    |

| DTMF Frequency Variation    |            | Δfγ             | $R_L = 1.2 \text{ k}\Omega$       | - 1 | _        | 1   | %    |

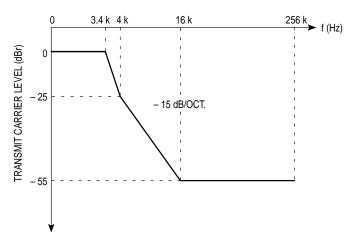

| Out-of-Band Energy VO       |            | VOE             | ]                                 |     | Figure 1 |     | dB   |

| Setup Time                  |            | tosc            |                                   | _   | 4        | _   | ms   |

# DTMF RECEIVER CHARACTERISTICS (V<sub>CC</sub> = $5.0 \text{ V} \pm 10\%$ , T<sub>A</sub> = $-20 \text{ to } 70^{\circ}\text{C}$ )

| Characteristic                            |           | Symbol | Conditions       | Min        | Тур | Max   | Unit |

|-------------------------------------------|-----------|--------|------------------|------------|-----|-------|------|

| Input Impedance                           |           |        |                  | 50         | _   | _     | kΩ   |

| Detect Signal Level (Each Tone)           |           |        |                  | - 48       | _   | 0     | dBm  |

| Twist (High Group Tone/Low Group          | ıp Tone   |        |                  | - 10       | _   | 10    | dB   |

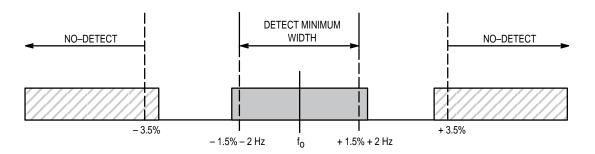

| Frequency Detect Band Width (Fig.         | gure 4)   |        |                  | ±1.5% ±2Hz | _   | _     | _    |

| Frequency No-Detect Band Width (Figure 4) |           |        |                  | _          | _   | ± 3.5 | %    |

| DTMF Detect Timing                        | OFF to ON | TCDON  | CD1 = 0, CD0 = 1 | _          | 25  | _     | ms   |

|                                           |           |        | CD1 = 1, CD0 = 0 | _          | 30  | _     | ]    |

|                                           |           |        | CD1 = 1, CD0 = 1 | _          | 40  | _     | ]    |

| ON to OFF                                 |           | TCDOFF | CD1 = 0, CD0 = 1 | _          | 25  | _     | ]    |

|                                           |           |        | CD1 = 1, CD0 = 0 | _          | 35  | _     | 1    |

|                                           |           |        | CD1 = 1, CD0 = 1 | _          | 25  | _     | 1    |

# **DEMODULATOR CHARACTERISTICS** (V<sub>CC</sub> = 5.0 V $\pm$ 10%, T<sub>A</sub> = - 20 to 70°C)

| Characteristic                                             | Symbol | Conditions             | Min | Тур     | Max | Unit |

|------------------------------------------------------------|--------|------------------------|-----|---------|-----|------|

| Bit Bias                                                   | ID     | Input Level = – 24 dBm | _   | 5       | _   | %    |

| Bit Error Rate<br>(CCITT Line Simulation, 511–Bit Pattern) | BER    | S/N = 4 dB             | _   | 0.00001 | _   | _    |

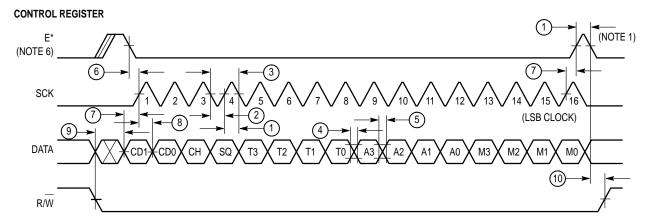

# SWITCHING CHARACTERISTICS (V $_{CC}$ = 5.0 V $\pm$ 10%, TA = - 20 to 70°C)

| Characteristic               |              | Symbol           | Timing<br>Diagram<br>Reference<br>No. | Min | Тур | Max | Unit |

|------------------------------|--------------|------------------|---------------------------------------|-----|-----|-----|------|

| Input Pulse Width (H) E, SCK |              | t <sub>wh</sub>  | 1                                     | 50  | _   | _   | ns   |

| Input Pulse Width (L) E, SCK |              | t <sub>Wl</sub>  | 2                                     | 50  | _   | _   | ns   |

| Clock Cycle                  |              | t <sub>C</sub>   | 3                                     | 100 | _   | _   | ns   |

| Input Rise Time              |              | t <sub>r</sub>   | 4                                     | _   | _   | 2   | μs   |

| Input Fall Time              |              | tf               | 5                                     | _   | _   | 2   | μs   |

| Recovery Time E to SCK       |              | t <sub>rec</sub> | 6, 18                                 | 50  | _   | _   | ns   |

| Setup Time                   | DATA to SCK  | t <sub>su</sub>  | 7                                     | 50  | _   | _   | ns   |

|                              | R/W↓ to DATA |                  | 9                                     | 100 | _   | _   | ns   |

|                              | R/W↑ to DATA |                  | 12                                    | 50  | _   | _   | ns   |

| Hold Time                    | SCK to DATA  | th               | 8                                     | 50  | _   | _   | ns   |

|                              | E to R/W     |                  | 10                                    | 50  | _   | _   | ns   |

|                              | DATA to R/W  |                  | 14                                    | 50  | _   | _   | ns   |

|                              | R/W to DATA  |                  | 15                                    | 50  | _   | _   | ns   |

| Read Data Delay Time         | E to DATA    | t <sub>d</sub>   | 13                                    | _   | _   | 50  | ns   |

|                              | SCK to DATA  |                  | 17                                    | _   | _   | 50  | ns   |

| Enable Minimum Interval      |              | t <sub>we</sub>  | 11                                    | _   | _   | 450 | ns   |

| Mode Switch Minimum Interval |              | twm              | 16                                    | _   | _   | 600 | ns   |

<sup>\*</sup> The enable signal corresponds to preceding data format.

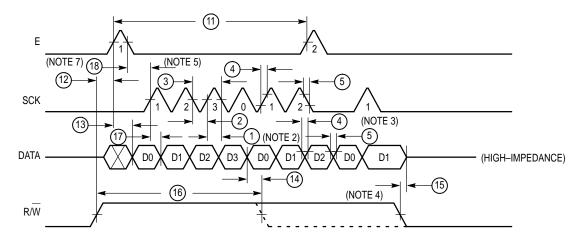

#### STATUS REGISTER

#### NOTES:

- 1. The data in front of the enable signal pulse will be latched.

- 2. The latched data will be repeated until there is an enable pulse.

- 3. The detected data will be updated with the next enable pulse.

- 4. After the R/W pin becomes INACTIVE, the data will be lost.

- 5. D1 corresponds to Clock1.

- 6. The enable and the SCK signals need to be set at the logic low level when the R/W signal changes.

- 7. The SCK must be held at low level when the enable signal is at high level.

Figure 1. Serial Data Input Timing

Figure 2. Out-of-Band Energy

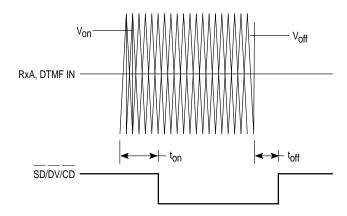

Figure 3. FSK, DTMF Carrier Detect Timing

Figure 4. DTMF Frequency Detect Bandwidth

#### PIN DESCRIPTIONS

#### **VCC**

#### Positive Power Supply (Pins 1, 13, 21)

The digital supply pins, which are connected to the positive power supply (5 V).

#### **GND**

#### Ground Pins (Pins 2, 12)

The ground pins are connected to the system ground.

#### V<sub>ref</sub>

#### **Reference Analog Ground (Pin 3)**

This pin provides the analog ground voltage, which is internally regulated to VCC/2. It should be decoupled to the GND with 0.1  $\mu$ F and 100  $\mu$ F capacitors.

#### **X1**

#### **Crystal Oscillator Output (Pin 9)**

A 3.579545 MHz  $\pm$  0.1% crystal oscillator is tied to this pin with the other end connected to X2.

#### **X2**

#### **Crystal Oscillator Input (Pin 10)**

A 3.579545 MHz  $\pm$  0.1% crystal oscillator is tied to this pin with the other end connected to X1. X2 may also be driven directly from an appropriate external source.

#### SCK

#### Serial Clock Input (Pin 19)

This pin is the clock input for the 16-bit control resistor and the 4-bit status resistor. The serial data is captured into the control register, or is shifted out of the status register on the rising edge of SCK.

#### DATA I/O

#### Serial Data Input/Output (Pin 18)

This pin is the 16-bit control register input, which determines the operation mode, DTMF tone, transmit attenuation (receiver gain), carrier detect time, channel, and transmit squelch. This pin is also the four-bit status register output which indicates the received DTMF tone (hexadecimal codes).

#### E

#### **Enable Input (Pin 20)**

When the R/W pin is at logic low, high level on the E pin makes the 16-bit control register data transparent to the mode control logic so that the device operation is changed. While this pin is at logic low, the control register and the mode control logic are isolated. The E pin must NOT be held high while the control register data is being changed.

When the R/W pin is at logic high, the rising edge of E transfers the four–bit DTMF data from the DTMF decoder to the status register. Then the first bit (LSB = D0) is presented at the Data I/O pin.

#### R/W

#### Read/Write Data Switch (Pin 14)

This pin is used for controlling the I/O direction of the Data I/O pin.

#### **TxD**

#### **Transmit Data Input (Pin 17)**

This pin is the transmit data input. When the device is in FSK mode, the mark frequency is generated when this pin is at the logic high level. The space frequency is generated when the pin is at a logic low.

#### **RxD**

#### Receive Data Output (Pin 16)

This pin is the receive data output. When the device is in the FSK mode, a high logic level of this pin indicates that the mark carrier frequency has been received, and a low logic level indicates the space carrier frequency has been received.

#### SD/CD/DV

# Carrier/Call Progress Tone Detect/DTMF Data Valid Detect (Pin 15)

This pin works as a carrier detector in the FSK mode, whereas it works as the call progress tone detector in the CPTD mode and as the receive DTMF detector in the DTMF Rx mode. The output goes to a logic low level when the input signal reaches the minimum threshold of the detect level that is adjusted by the CDA voltage. When this pin is logic high, the receive data output (RxD) is clamped high to avoid the error that may occur with the loop noise.

In DTMF Rx mode, the logic low on this pin indicates that the valid DTMF frequencies are detected. The received tone is decoded to four–bit <u>data</u>, then stored in the DTMF decoder by the falling edge of DV.

#### TxA1

#### Non-Inverting Transmit Analog Carrier Output (Pin 24)

This pin is the line driver non–inverting output. A 7 dBm (typ) differential output voltage can be obtained by connecting a 1.2 k $\Omega$  load resistor between Tx1 and Tx2. Attention must be paid so as not to exceed this level when an external input is added to the DSI pin. A telephone line (600  $\Omega$ ) is driven through an external 600  $\Omega$  resistor (see the Application Circuit). In this case, the output level becomes about a half of the differential output.

#### TxA2

#### **Inverting Transmit Analog Carrier Output (Pin 23)**

This pin is the line driver inverting output. The signal is equal in magnitude, but 180° out of phase with the TxA1 (refer to TxA1).

#### RxA

#### Receive Signal Input (Pin 25)

This pin is the carrier signal input, and is enabled when the device is in FSK or CPTD mode.

#### **RxGC**

#### Receive Gain Adjust (Pin 26)

This pin is used to adjust the receive buffer gain. To adjust the gain, a resistor may be added between this pin and the RxBO pin (refer to the Block Diagram). This pin may be held open when the gain adjustment is not needed.

#### **RxBO**

#### **Receive Buffer Output (Pin 27)**

This pin is the receive buffer output.

#### **DTMF IN**

#### DTMF Receive Input (AGC Amp Input) (Pin 5)

This pin is the receive DTMF signal input. It is enabled when the device is in the DTMF receive mode.

# AGC OUT AGC Output (Pin 6)

This pin is used by the manufacturer to test the auto gain control amplifier. It should be held open in normal operation.

#### DSI

#### **Driver Summing Input (Pin 22)**

This pin is the inverting input of the line driver. An external signal may be transmitted through an external series resistor RDSI. The differential gain GDSI =  $(V_{TxA1} - V_{TxA2})/V_{DSI}$  is determined by the following equation:

$$G_{DSI} = -2Rf/R_{DSI}$$

,  $Rf \sim 20 k\Omega$

Note that the programmable transmit attenuator does not affect in this case.

The DSI pin should be held open when not in use.

#### CDA

#### Carrier Detect Level/CPTD Level Control (Pin 4)

The carrier/call progress tone detect level is adjusted by the CDA pin voltage.

When this pin is held open, the CDA voltage is set to 1.25 V (V<sub>CC</sub> =  $\pm$  5 V) by an internal divider. Then the detect level is set at – 44 dBm (typ) for off to on, and – 47 dBm (typ) for on to off, and the hysteresis is set minimum 2 dB. This pin has a very high input impedance so it should be connected to GND with a 0.1  $\mu F$  capacitor to keep it under the regulations. An external voltage may be applied to this pin to adjust the carrier detect threshold. The following equations may be used to find the CDA voltage required for a given threshold voltage:

$$V_{CDA} = 245 \times V_{on}$$

$V_{CDA} = 347 \times V_{off}$

#### TLA

#### **Transmit Carrier Level Adjust (Pin 11)**

This pin is used to adjust the transmit carrier level that is determined by the value of the resistor (RTLA) connected between this pin and the GND. The maximum level can be obtained when this pin is shorted to GND (RTLA = 0).

#### FTLC1 FSK Filter Test (Pin 28)

This pin is a high–impedence filter output. It may be used for testing the FSK filter characteristics, and is reserved for manufacturer's use only. In normal operation, this pin should be decoupled to  $V_{\text{ref}}$  with a 0.1  $\mu\text{F}$  capacitor.

#### FTLC2

#### **DTMF Receive Low Group Filter Test (Pin 7)**

This pin is a high–impedence filter output. It may be used for testing the DTMF receive high goup bandpass filter characteristics, and is reserved for manufacturer's use only. In normal operation, this pin should be decoupled to  $V_{ref}$  with a 0.1  $\mu$ F capacitor.

#### FTLC3

#### **DTMF Receive High Group Filter Test (Pin 8)**

This pin is a high–impedence filter output. It may be used for testing the DTMF receive high group bandpass filter characteristics, and is reserved for manufacturer's use only. In normal operation, this pin should be decoupled to  $V_{\text{ref}}$  with a 0.1  $\mu\text{F}$  capacitor.

#### SERIAL CONTROL INTERFACE

The following six functions are determined by the 16 bits of serial data in the control register.

#### CONTROL REGISTER

| CONTROL REGISTER           |               |

|----------------------------|---------------|

| FUNCTION MODE              | : M3 M2 M1 M0 |

| TRANSMIT ATTENUATOR        | : A3 A2 A1 A0 |

| TRANSMIT TONE<br>FREQUENCY | . T3 T2 T1 T0 |

| TRANSMIT SQUELCH           | : SQ          |

| CHANNEL                    | : CH          |

| CARRIER DETECT TIME        | : CD1 CD0     |

The received DTMF tones are indicated by the four bits of data in the status register.

#### STATUS REGISTER

| RECEIVE TONE FREQUENCY: | D3 | D2 | D1 | D0 |

|-------------------------|----|----|----|----|

Figure 1 presents the timing diagram of 16–bit control register input and four–bit status output. When the R/W pin is in logic low, the 16–bit data is captured into the control register at the rising edge of SCK and latched in the mode control logic to update the function mode at logic high input to the E pin. When the R/W pin is in logic high, the status register is selected to read out the received DTMF data, the four–bit data in the DTMF decoder is loaded into the status register, and the first bit (D0) is presented at the Data I/O on the rising edge of E. The following bits are repeatedly shifted out as D1–D2–D3–D0–D1–... by the rising edges of SCK.

#### **CONTROL REGISTER BIT MAP DESCRIPTION**

#### **FUNCTION MODE (M3 to M0)**

One of the following modes is selected from the four–bit data (M3 to M0) shown in Table 1. Table 2 presents each output status; the functions are described below.

**Table 1. Function Mode Truth Table**

| М3 | M2 | M1 | МО | Function Mode        |

|----|----|----|----|----------------------|

| 0  | 0  | 0  | 0  | FSK                  |

| 0  | 0  | 0  | 1  | FSK Analog Loopback  |

| 0  | 0  | 1  | 0  | CPTD                 |

| 0  | 0  | 1  | 1  | Answer Tone          |

| 0  | 1  | 0  | 0  | DTMF Transmit        |

| 0  | 1  | 0  | 1  | Single Tone          |

| 0  | 1  | 1  | 0  | Power–Down 1         |

| 0  | 1  | 1  | 1  | Power–Down 2         |

| 1  | 0  | 0  | 0  | DTMF Receive         |

| 1  | 0  | 0  | 1  | DTMF Analog Loopback |

#### **FSK Mode**

The transmitter and the receiver work as an FSK modulator/demodulator. The SD pin goes low when a valid FSK signal is detected.

#### **DTMF Transmit Mode**

The transmitter works as a DTMF tone generator. The receiver is disabled.

#### **CPTD (Call Progress Tone Detect) Mode**

The receiver works as a 400 Hz call progress tone detector. The CD pin goes low when a valid call progress tone is detected.

#### **Answer Tone Mode**

The transmitter works as a 2100 Hz answer tone generator. The receiver is disabled.

#### **FSK Analog Loopback Mode**

The transmitter, working as the FSK modulator, is internally connected to the receiver working as the FSK demodulator. This feature is used for the device self test.

#### **DTMF Receive Mode**

The receiver works as a DTMF tone receiver. The DV goes low when a valid DTMF tone is detected. The transmitter is disabled.

#### **DTMF Analog Loopback Mode**

The transmitter, working as a DTMF tone generator, is internally connected to the receiver working as DTMF tone receiver. The DV goes low when the receiver detects a valid DTMF tone. This feature is used for the device self test.

#### **Single Tone Mode**

The transmitter generates one of the eight frequencies of the DTMF tone. The receiver is disabled.

#### Power-Down Mode 1

Whole internal circuits, except the oscillator, are disabled and all outputs except the X1 pin go to the high-impedance state. The supply current decreases to 500 µA (max).

#### Power-Down Mode 2

Whole internal circuits, including the oscillator, are disabled and all outputs go to the high–impedance state. The supply current decreases to  $1.0 \,\mu\text{A}$  (max).

#### Transmit Attenuator/AGC Gain Set (A3 to A0)

Four–bit serial data (A3 – A0) sets up the analog transmit level in the FSK, answer tone, DTMF, analog loopback, and single tone mode. The range of the transmit attenuator is 0 to 15 dB in 1 dB steps. The attenuator, however, does not affect the external signal input from the DSI. These bits also determine the AGC amplifier gain in the DTMF receive mode. In normal operation, "Automatic" may be selected so that the gain is automatically adjusted corresponding to the input signal level. See Table 3 for a detailed description.

#### Transmit Tone Frequency (T3 to T0)

These four bits (T3 to T0) determine the DTMF tone frequencies in DTMF transmit and DTMF analog loopback mode, and determine the single tone frequency in the single tone mode. Tone frequency assignments with reference to T3 – T0 are shown in Table 4.

**Table 2. Output Status**

|                    | Output Pin     |                |                    |  |  |

|--------------------|----------------|----------------|--------------------|--|--|

| Function Mode      | RxD            | SD/CD/DV       | TxA1, TxA2         |  |  |

| FSK                | Receive        | Carrier        | FSK                |  |  |

| FSK Loopback       | Digital Data   | Detect Signal  |                    |  |  |

| Call Progress Tone | Н              | CPTD Signal    | V <sub>CC</sub> /2 |  |  |

| Answer Tone        | Н              | Н              | Answer Tone        |  |  |

| DTMF Transmit      | Н              | Н              | DTMF Tone          |  |  |

| Single Tone        | Н              | Н              | Single Tone        |  |  |

| Power–Down 1, 2    | High Impedance | High Impedance | High Impedance     |  |  |

| DTMF Receive       | Н              | DV Signal      | V <sub>CC</sub> /2 |  |  |

| DTMF Loopback      |                |                | DTMF Tone          |  |  |

Table 3. Transmit Attenuator/AGC Gain Set Truth Table

| А3 | A2 | A1 | Α0 | Attenuation (dB) | AGC Gain<br>Step (dB) |

|----|----|----|----|------------------|-----------------------|

| 0  | 0  | 0  | 0  | 0                | - 5.0                 |

| 0  | 0  | 0  | 1  | 1                | - 2.5                 |

| 0  | 0  | 1  | 0  | 2                | 0.0                   |

| 0  | 0  | 1  | 1  | 3                | 2.5                   |

| 0  | 1  | 0  | 0  | 4                | 5.0                   |

| 0  | 1  | 0  | 1  | 5                | 7.5                   |

| 0  | 1  | 1  | 0  | 6                | 10.0                  |

| 0  | 1  | 1  | 1  | 7                | 12.5                  |

| 1  | 0  | 0  | 0  | 8                | 15.0                  |

| 1  | 0  | 0  | 1  | 9                | 17.5                  |

| 1  | 0  | 1  | 0  | 10               | 20.0                  |

| 1  | 0  | 1  | 1  | 11               | Clamp                 |

| 1  | 1  | 0  | 0  | 12               | Automatic             |

| 1  | 1  | 0  | 1  | 13               |                       |

| 1  | 1  | 1  | 0  | 14               |                       |

| 1  | 1  | 1  | 1  | 15               |                       |

**Table 4. Tone Frequency Truth Table**

|       |       |       |       | Tone Frequency (Hz) |               |                        |                     |

|-------|-------|-------|-------|---------------------|---------------|------------------------|---------------------|

|       |       |       |       |                     |               |                        |                     |

| T3/D3 | T2/D2 | T1/D1 | T0/D0 | Low<br>Group        | High<br>Group | Keyboard<br>Equivalent | Single<br>Tone Mode |

| 0     | 0     | 0     | 0     | 941                 | 1633          | D                      | 941                 |

| 0     | 0     | 0     | 1     | 697                 | 1209          | 1                      | 697                 |

| 0     | 0     | 1     | 0     | 697                 | 1336          | 2                      | 697                 |

| 0     | 0     | 1     | 1     | 697                 | 1477          | 3                      | 697                 |

| 0     | 1     | 0     | 0     | 770                 | 1209          | 4                      | 770                 |

| 0     | 1     | 0     | 1     | 770                 | 1336          | 5                      | 770                 |

| 0     | 1     | 1     | 0     | 770                 | 1477          | 6                      | 770                 |

| 0     | 1     | 1     | 1     | 852                 | 1209          | 7                      | 852                 |

| 1     | 0     | 0     | 0     | 852                 | 1336          | 8                      | 1336                |

| 1     | 0     | 0     | 1     | 852                 | 1477          | 9                      | 1477                |

| 1     | 0     | 1     | 0     | 941                 | 1336          | 0                      | 1336                |

| 1     | 0     | 1     | 1     | 941                 | 1209          | *                      | 1209                |

| 1     | 1     | 0     | 0     | 941                 | 1477          | #                      | 1477                |

| 1     | 1     | 0     | 1     | 697                 | 1633          | А                      | 1633                |

| 1     | 1     | 1     | 0     | 770                 | 1633          | В                      | 1633                |

| 1     | 1     | 1     | 1     | 852                 | 1633          | С                      | 1633                |

#### **Transmit Squelch**

The 1–bit serial data (SQ) controls the transmit analog squelch. The FSK signal, DTMF tones, single tone, and answer tone are disabled, then TxA1 and TxA2 will be clamped to  $V_{CC}/2$  when the transmit squelch goes to the Enable (SQ = 1) state. The transmit squelch does not affect the external signal from the DSI.

**Table 5. Transmit Squelch Truth Table**

| SQ | Squelch |  |  |

|----|---------|--|--|

| 1  | Enable  |  |  |

| 0  | Disable |  |  |

#### Channel

When the function mode is either on the FSK or analog loopback mode, the transmit and receive channel is set up with a 1-bit serial data (CH).

**Table 6. Channel Truth Table**

|   | СН | Channel       |  |

|---|----|---------------|--|

| I | 1  | 1 (Originate) |  |

| I | 0  | 2 (Answer)    |  |

#### **Carrier Detect Time**

The carrier and DTMF tone detect timing are determined by two-bit serial data (CD1, CD0). The timing diagram is shown in Figure 3.

Table 7. Carrier/DTMF Detect Time Truth Table

|   |     |     | FSK Mode<br>Carrier Detect Time<br>(typ)   |    | DTMF Rec<br>Carrier De<br>(ty |           |

|---|-----|-----|--------------------------------------------|----|-------------------------------|-----------|

|   | CD1 | CD0 | t <sub>on</sub> (ms) t <sub>off</sub> (ms) |    | ton (ms)                      | toff (ms) |

| I | 0   | 0   | 450                                        | 35 | Reserved                      |           |

| I | 0   | 1   | 10                                         | 35 | 25                            | 25        |

|   | 1   | 0   | 10                                         | 20 | 30                            | 35        |

|   | 1   | 1   | 70                                         | 15 | 40                            | 25        |

#### Power-On Reset

When the power is switched on, this device is entered into Power–Down Mode 2 by the internal power–on reset circuit.

#### STATUS REGISTER BIT MAP DESCRIPTION

#### Received Tone Frequency (D3 to D0)

This four–bit data (D3 to D0) indicates the received DTMF tones. The first bit (D0) is presented at Data I/O on the rising edge of E, and the following bits (D1–D2–D3–D0–D1– ...) are shifted out and presented on the next rising edge of SCK.

The data configuration corresponding to each tone is shown in Table 4.

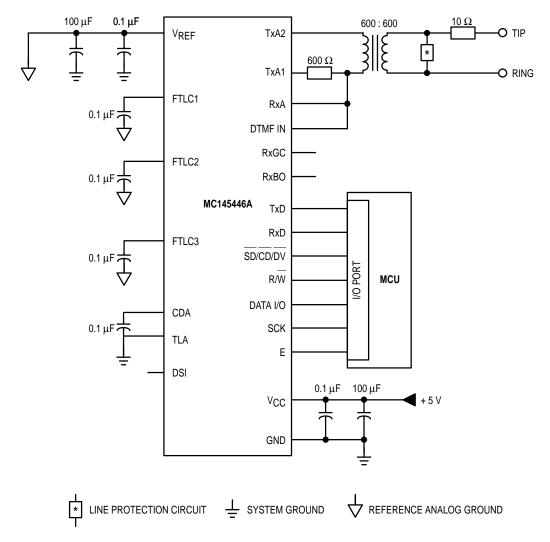

Figure 5. Application Circuit

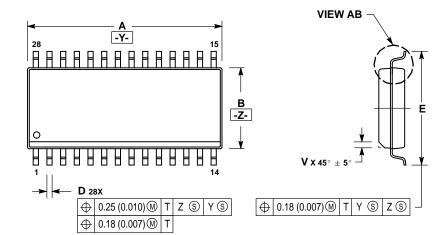

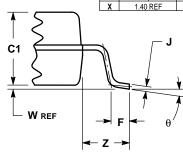

#### PACKAGE DIMENSIONS

#### FW SUFFIX SOP CASE 751M-01

#### NOTES

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- CONTROLLING DIMENSION, MICHINETER.

DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION. MAXIMUM MOLD PROTRUSION SHALL NOT EXCEPT 0.15 (0.006) PER SIDE.

- SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

4. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED 0.65 (0.026).

|     | MILLIN | IETERS | INC       | HES   |

|-----|--------|--------|-----------|-------|

| DIM | MIN    | MAX    | MIN       | MAX   |

| Α   | 17.80  | 18.03  | 0.701     | 0.710 |

| В   | 7.40   | 7.62   | 0.291     | 0.300 |

| С   |        | 2.65   |           | 0.104 |

| C1  | 2.25   | 2.45   | 0.090     | 0.096 |

| D   | 0.35   | 0.51   | 0.014     | 0.020 |

| E   | 10.00  | 10.60  | 0.394     | 0.414 |

| F   | 0.40   | 0.70   | 0.016     | 0.028 |

| G   | 1.27   | BSC    | 0.050 BSC |       |

| J   | 0.10   | 0.25   | 0.004     | 0.010 |

| L   | 0.635  | BSC    | 0.025 BSC |       |

| θ   |        | 8°     |           | 8°    |

| ٧   | 0.25   | 0.75   | 0.010     | 0.030 |

| W   | 0.05   | 0.20   | 0.002     | 0.008 |

| Х   | 1.40   | REF    | 0.110     | REF   |

**VIEW AB**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

**USA/EUROPE/Locations Not Listed**: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 or 602–303–5454

**MFAX**: RMFAX0@email.sps.mot.com – TOUCHTONE 602–244–6609 **INTERNET**: http://Design\_NET.com

**JAPAN**: Nippon Motorola Ltd.; Tatsumi–SPD–JLDC, 6F Seibu–Butsuryu–Center, 3–14–2 Tatsumi Koto–Ku, Tokyo 135, Japan. 03–81–3521–8315

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852–26629298