19-2016: Rev 0: 5/01

###

### Ultra-Small, Rail-to-Rail I/O with Disable, Single-/Dual-Supply, Low-Power Op Amps

#### **General Description**

The MAX4245/MAX4246/MAX4247 family of low-cost op amps offer Rail-to-Rail® inputs and outputs, draw only 320µA of quiescent current, and operate from a single +2.5V to +5.5V supply. For additional power conservation, the MAX4245/MAX4247 offer a low-power shutdown mode that reduces supply current to 50nA, and puts the amplifiers' outputs in a high-impedance state. These devices are unity-gain stable with a 1MHz gain-bandwidth product driving capacitive loads up to 470pF.

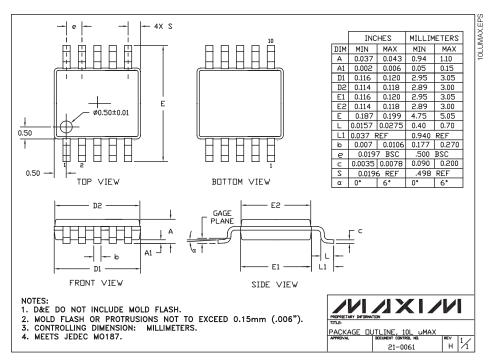

The MAX4245/MAX4246/MAX4247 family is specified from -40°C to +125°C, making them suitable for use in a variety of harsh environments, such as automotive applications. The MAX4245 single amplifier is available in ultra-small 6-pin SC70 and space-saving 6-pin SOT23 packages. The MAX4246 dual amplifier is available in 8-pin SOT23 and µMAX packages. The MAX4247 dual amplifier comes in a tiny 10-pin µMAX package.

#### **Applications**

Selector Guide

Portable Communications

Single-Supply Zero-Crossing Detectors

Instruments and Terminals

**Electronic Ignition Modules**

Infrared Receivers

Sensor-Signal Detection

#### **Features**

- ♦ Rail-to-Rail Input and Output Voltage Swing

- 50nA (max) Shutdown Mode (MAX4245/MAX4247)

- ♦ 320µA (typ) Quiescent Current Per Amplifier

- ♦ Single +2.5V to +5.5V Supply Voltage Range

- ♦ 110dB Open-Loop Gain with 2kΩ Load

- ♦ 0.01% THD with 100kΩ Load

- ♦ Unity-Gain Stable up to CLOAD = 470pF

- No Phase Inversion for Overdriven Inputs

- Available in Space-Saving Packages 6-Pin SC70 or 6-Pin SOT23 (MAX4245) 8-Pin SOT23 or 8-Pin µMAX (MAX4246) **10-Pin μMAX (MAX4247)**

### **Ordering Information**

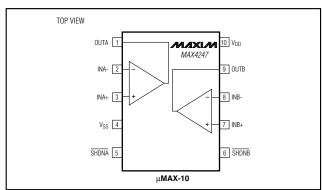

Pin Configurations

MAXIM

| PART         | TEMP. RANGE     | PIN-<br>PACKAGE | TOP<br>MARK |

|--------------|-----------------|-----------------|-------------|

| MAX4245AXT-T | -40°C to +125°C | 6 SC70-6        | AAZ         |

| MAX4245AUT-T | -40°C to +125°C | 6 SOT23-6       | AAUB        |

| MAX4246AKA-T | -40°C to +125°C | 8 SOT23-8       | AAIN        |

| MAX4246AUA   | -40°C to +125°C | 8 µMAX          | _           |

| MAX4247AUB   | -40°C to +125°C | 10 μMAX         | _           |

OUTA 1

INA- 2

INA+ 3

6 V<sub>DD</sub>

5 SHDN

4 OUT

TOP VIEW

| PART         | AMPLIFIERS<br>PER PACKAGE | SHUTDOWN<br>MODE |

|--------------|---------------------------|------------------|

| MAX4245AXT-T | 1                         | Yes              |

| MAX4245AUT-T |                           | Yes              |

| MAX4246AKA-T | 2                         | No               |

| MAX4246AUA   | 2                         | No               |

| MAX4247AUB   | 2                         | Yes              |

SC70-6/SOT23-6 V<sub>SS</sub> 4 SOT23-8/uMAX-8 Pin Configurations continued at end of data sheet. ail-to-Rail is a registered trademark of Nippon Motorola Ltd.

Maxim Integrated Products 1

7 OUTB

6 INB-

#### **ABSOLUTE MAXIMUM RATINGS**

| Power Supply Voltage (VDD to V                       | ss)0.3V to +6V             |

|------------------------------------------------------|----------------------------|

| All Other Pins                                       |                            |

| Output Short-Circuit Duration                        | (199 9.91) to (100 1 9.91) |

|                                                      |                            |

| (OUT shorted to V <sub>SS</sub> or V <sub>DD</sub> ) | Continuous                 |

| Continuous Power Dissipation (T                      | $A = +70^{\circ}C$         |

| 6-Pin SC70 (derate 3.1mW/°C                          | above +70°C)245mW          |

| 6-Pin SOT23 (derate 8.7mW/°                          | C above +70°C)695mW        |

| 8-Pin SOT23 (derate 9.1mW/°                          | C above +70°C)727mW        |

| 8-Pin µMAX (derate 4.5mW/°C                          | C above +70°C)362mW        |

| 10-Pin µMAX (derate 5.6mW/                           | °C above +70°C)444mW       |

|                                                      |                            |

| Operating Temperature Range       | 40°C to +125°C |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +160°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +2.7V, V_{SS} = 0, V_{CM} = 0, V_{OUT} = V_{DD}/2, R_L \text{ connected from OUT to } V_{DD}/2, \overline{SHDN}_ = V_{DD} \text{ (MAX4245/MAX4247 only)}, T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                          | SYMBOL                | СО                                                                                                                   | NDITIONS                | MIN                   | TYP   | MAX                   | UNITS |

|------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|-------|-----------------------|-------|

| Supply Voltage Range               | $V_{DD}$              | Inferred from PSRR test                                                                                              |                         | 2.5                   |       | 5.5                   | V     |

| Constitution (Para Association)    |                       | $V_{DD} = +2.7V$                                                                                                     |                         |                       | 320   | 650                   | ^     |

| Supply Current (Per Amplifier)     | I <sub>DD</sub>       | $V_{DD} = +5.5V$                                                                                                     |                         |                       | 375   | 700                   | μΑ    |

| Supply Current in Shutdown         | ISHDN_                | SHDN_ = V <sub>SS</sub> (Not                                                                                         | e 2)                    |                       | 0.05  | 0.5                   | μΑ    |

| Input Offset Voltage               | Vos                   | V <sub>SS</sub> - 0.1V ≤ V <sub>CM</sub> ≤                                                                           | V <sub>DD</sub> + 0.1V  |                       | ±0.4  | ±1.5                  | mV    |

| Input Bias Current                 | IB                    | V <sub>SS</sub> - 0.1V ≤ V <sub>CM</sub> ≤                                                                           | V <sub>DD</sub> + 0.1V  |                       | ±10   | ±50                   | nA    |

| Input Offset Current               | los                   | V <sub>SS</sub> - 0.1V ≤ V <sub>CM</sub> ≤                                                                           | √V <sub>DD</sub> + 0.1V |                       | ±1    | ±6                    | nA    |

| Input Resistance                   | RIN                   | $ V_{IN+} - V_{IN-}  \le 10 \text{m}^{3}$                                                                            | V                       |                       | 4000  |                       | kΩ    |

| Input Common-Mode Voltage<br>Range | V <sub>CM</sub>       | Inferred from CMR                                                                                                    | R test                  | V <sub>SS</sub> - 0.1 |       | V <sub>DD</sub> + 0.1 | V     |

| Common-Mode Rejection Ratio        | CMRR                  | V <sub>SS</sub> - 0.1V ≤ V <sub>CM</sub> ≤                                                                           | V <sub>DD</sub> + 0.1V  | 65                    | 80    |                       | dB    |

| Power-Supply Rejection Ratio       | PSRR                  | $2.5V \le V_{DD} \le 5.5V$                                                                                           |                         | 75                    | 90    |                       | dB    |

| Large-Signal Voltage Gain          | A <sub>V</sub>        | $V_{SS} + 0.05V \le V_{OUT} \le V_{DD} - 0.05V$ , $R_L = 100k\Omega$                                                 |                         |                       | 120   |                       | dB    |

|                                    |                       | $V_{SS} + 0.2V \le V_{OUT} \le V_{DD} - 0.2V, R_L = 2k\Omega$                                                        |                         | 95                    | 110   |                       |       |

| Cutout Valtage Cuing High          | \/                    | Specified as                                                                                                         | $R_L = 100k\Omega$      |                       | 1     |                       | \/    |

| Output Voltage Swing High          | VoH                   | V <sub>DD</sub> - V <sub>OUT</sub>                                                                                   | $R_L = 2k\Omega$        |                       | 35    | 60                    | mV    |

| Cutout Valtage Cuing Law           | 1/                    | Specified as                                                                                                         | $R_L = 100k\Omega$      |                       | 1     |                       | \/    |

| Output Voltage Swing Low           | VoL                   | V <sub>OUT</sub> - V <sub>SS</sub>                                                                                   | $R_L = 2k\Omega$        |                       | 30    | 60                    | mV    |

| Output Short Circuit Current       | 1                     | \/ F.O\/                                                                                                             | Sourcing                |                       | 11    |                       | m ^   |

| Output Short-Circuit Current       | I <sub>OUT</sub> (SC) | $V_{DD} = +5.0V$                                                                                                     | Sinking                 | 30                    |       |                       | mA    |

| Output Leakage Current in Shutdown | I <sub>OUT(SH)</sub>  | Device in Shutdown Mode<br>(SHDN_ = V <sub>SS</sub> ), V <sub>SS</sub> ≤ V <sub>OUT</sub> ≤ V <sub>DD</sub> (Note 2) |                         |                       | ±0.01 | ±0.5                  | μΑ    |

| SHDN_ Logic Low                    | V <sub>IL</sub>       | (Note 2)                                                                                                             |                         |                       | C     | .3 x V <sub>DD</sub>  | V     |

| SHDN_ Logic High                   | VIH                   | (Note 2)                                                                                                             |                         | 0.7 x V <sub>DD</sub> |       |                       | V     |

| SHDN_ Input Current                | IL/IH                 | V <sub>SS</sub> ≤ SHDN_ ≤ V <sub>DD</sub> (Note 2)                                                                   |                         |                       | 0.5   | 50                    | nA    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7V, V_{SS} = 0, V_{CM} = 0, V_{OUT} = V_{DD}/2, R_L \text{ connected from OUT to } V_{DD}/2, \overline{SHDN}_ = V_{DD} \text{ (MAX4245/MAX4247 only)}, T_A = +25^{\circ}C, unless otherwise noted.) (Note 1)$

| PARAMETER                   | SYMBOL          | CONDITIONS                                                                                          | MIN | TYP  | MAX | UNITS   |

|-----------------------------|-----------------|-----------------------------------------------------------------------------------------------------|-----|------|-----|---------|

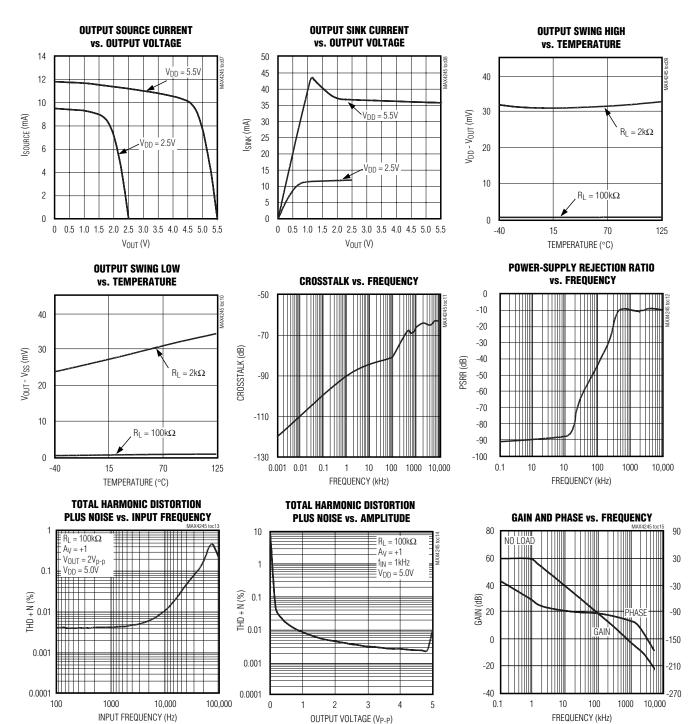

| Gain-Bandwidth Product      | GBW             |                                                                                                     |     | 1.0  |     | MHz     |

| Phase Margin                | φм              |                                                                                                     |     | 70   |     | degrees |

| Gain Margin                 | G <sub>M</sub>  |                                                                                                     |     | 20   |     | dB      |

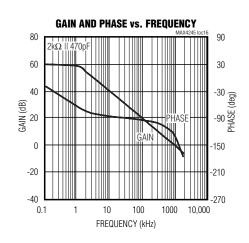

| Slew Rate                   | SR              |                                                                                                     |     | 0.4  |     | V/µs    |

| Input Voltage Noise Density | en              | f = 10kHz                                                                                           |     | 52   |     | nV/√Hz  |

| Input Current Noise Density | in              | f = 10kHz                                                                                           |     | 0.1  |     | pA/√Hz  |

| Capacitive-Load Stability   | CLOAD           | $A_V = 1$ (Note 3)                                                                                  |     |      | 470 | рF      |

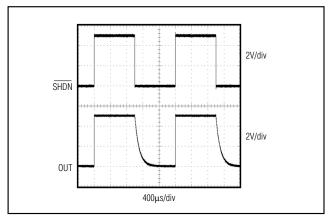

| Shutdown Delay Time         | t(SH)           | (Note 2)                                                                                            |     | 3    |     | μs      |

| Enable Delay Time           | t(EN)           | (Note 2)                                                                                            |     | 4    |     | μs      |

| Power-On Time               | ton             |                                                                                                     |     | 4    |     | μs      |

| Input Capacitance           | C <sub>IN</sub> |                                                                                                     |     | 2.5  |     | рF      |

| Total Harmonic Distortion   | THD             | $f = 10kHz$ , $V_{OUT} = 2Vp-p$ , $A_V = +1$ , $V_{DD} = +5.0V$ , Load = $100k\Omega$ to $V_{DD}/2$ |     | 0.01 |     | %       |

| Settling Time to 0.01%      | ts              | $V_{OUT} = 4V \text{ step}, V_{DD} = +5.0V, A_V = +1$ 10                                            |     |      | μs  |         |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +2.7V, V_{SS} = 0, V_{CM} = 0, V_{OUT} = V_{DD}/2, R_L \text{ connected from OUT to } V_{DD}/2, \overline{SHDN}_ = V_{DD} \text{ (MAX4245/MAX4247 only)}, T_A = -40°C to +125°C, unless otherwise noted.) (Note 1)$

| PARAMETER                          | SYMBOL               | CONDITIONS                                                                                                           | MIN                                                          | TYP  | MAX      | UNITS |

|------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|----------|-------|

| Supply Voltage Range               | $V_{DD}$             | Inferred from PSRR test                                                                                              | 2.5                                                          |      | 5.5      | V     |

| Supply Current (Per Amplifier)     | I <sub>DD</sub>      | $V_{DD} = +2.7V$                                                                                                     |                                                              |      | 800      | μА    |

| Supply Current in Shutdown         | ISHDN_               | SHDN_ = V <sub>SS</sub> (Note 2)                                                                                     |                                                              |      | 1        | μА    |

| Input Offset Voltage               | Vos                  | V <sub>SS</sub> ≤ V <sub>CM</sub> ≤ V <sub>DD</sub> (Note 4)                                                         |                                                              |      | ±3.0     | mV    |

| Input Offset Voltage Drift         | TCVOS                | V <sub>SS</sub> ≤ V <sub>CM</sub> ≤ V <sub>DD</sub> (Note 4)                                                         |                                                              | ±2   |          | μV/°C |

| Input Bias Current                 | ΙΒ                   | V <sub>SS</sub> ≤ V <sub>CM</sub> ≤ V <sub>DD</sub> (Note 4)                                                         |                                                              |      | ±100     | nA    |

| Input Offset Current               | los                  | V <sub>SS</sub> ≤ V <sub>CM</sub> ≤ V <sub>DD</sub> (Note 4)                                                         | V <sub>SS</sub> ≤ V <sub>CM</sub> ≤ V <sub>DD</sub> (Note 4) |      | ±10      | nA    |

| Input Common-Mode Voltage<br>Range | V <sub>CM</sub>      | Inferred from CMRR test (Note 4) VSS                                                                                 |                                                              |      | $V_{DD}$ | V     |

| Common-Mode Rejection Ratio        | CMRR                 | $V_{SS} \le V_{CM} \le V_{DD}$ (Note 4) 60                                                                           |                                                              |      | dB       |       |

| Power-Supply Rejection Ratio       | PSRR                 | $2.5V \le V_{DD} \le 5.5V$ 70                                                                                        |                                                              |      | dB       |       |

| Large-Signal Voltage Gain          | Av                   | $V_{SS} + 0.2V \le V_{OUT} \le V_{DD} - 0.2V,$ $R_L = 2k\Omega$ 85                                                   |                                                              |      |          | dB    |

| Output Voltage Swing High          | VoH                  | Specified as $V_{DD}$ - $V_{OUT}$ , $R_L = 2k\Omega$                                                                 |                                                              | 90   | mV       |       |

| Output Voltage Swing Low           | V <sub>OL</sub>      | Specified as $V_{OUT}$ - $V_{SS}$ , $R_L = 2k\Omega$                                                                 |                                                              | 90   | mV       |       |

| Output Leakage Current in Shutdown | I <sub>OUT(SH)</sub> | Device in Shutdown Mode (SHDN_ = V <sub>SS</sub> ),<br>V <sub>SS</sub> ≤ V <sub>OUT</sub> ≤ V <sub>DD</sub> (Note 3) |                                                              | ±1.0 | μА       |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7V, V_{SS} = 0, V_{CM} = 0, V_{OUT} = V_{DD}/2, R_L \text{ connected from OUT to } V_{DD}/2, \overline{SHDN}_ = V_{DD} \text{ (MAX4245/MAX4247 only), } T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.)} \text{ (Note 1)}$

| PARAMETER           | SYMBOL          | CONDITIONS                                             | MIN                 | TYP | MAX                 | UNITS |

|---------------------|-----------------|--------------------------------------------------------|---------------------|-----|---------------------|-------|

| SHDN_ Logic Low     | V <sub>IL</sub> | (Note 2)                                               |                     |     | $0.3 \times V_{DD}$ | V     |

| SHDN_ Logic High    | VIH             | (Note 2)                                               | $0.7 \times V_{DD}$ |     |                     | V     |

| SHDN_ Input Current | IL/IH           | V <sub>SS</sub> ≤ SHDN_ ≤ V <sub>DD</sub> (Notes 2, 3) |                     |     | 100                 | nA    |

Note 1: Specifications are 100% tested at T<sub>A</sub> = +25°C. All temperature limits are guaranteed by design.

Note 2: Shutdown mode is only available in MAX4245 and MAX4247.

Note 3: Guaranteed by design, not production tested.

**Note 4:** For -40°C to +85°C, Input Common Mode Range is  $V_{SS}$  - 0.1V  $\leq$   $V_{CM}$   $\leq$   $V_{DD}$  + 0.1V

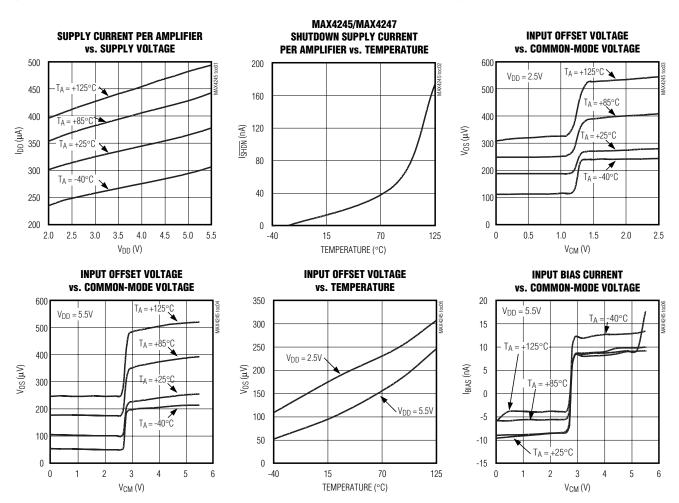

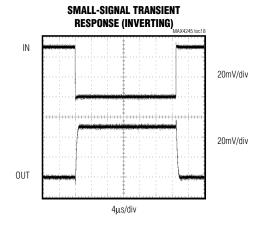

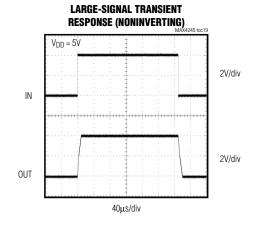

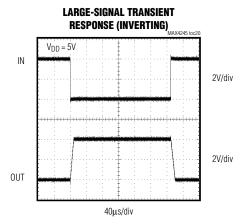

#### Typical Operating Characteristics

$(V_{DD} = 2.7V, V_{SS} = V_{CM} = 0, V_{OUT} = V_{DD}/2, \text{ no load, } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

#### Typical Operating Characteristics (continued)

(VDD = 2.7V, VSS = VCM = 0, VOUT = VDD/2, no load, TA = +25°C, unless otherwise noted.)

#### Typical Operating Characteristics (continued)

(V<sub>DD</sub> = 2.7V, V<sub>SS</sub> = V<sub>CM</sub> = 0, V<sub>OUT</sub> = V<sub>DD</sub>/2, no load, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### **Pin Description**

| PIN     |         | NAME    | FUNCTION        |                              |

|---------|---------|---------|-----------------|------------------------------|

| MAX4245 | MAX4246 | MAX4247 | NAME            | FUNCTION                     |

| 1       | _       | _       | IN+             | Noninverting Input           |

| 2       | 4       | 4       | V <sub>SS</sub> | Ground or Negative Supply    |

| 3       | _       | _       | IN-             | Inverting Input              |

| 4       | _       | _       | OUT             | Amplifier Output             |

| 5       | _       | _       | SHDN            | Shutdown                     |

| 6       | 8       | 10      | $V_{DD}$        | Positive Supply              |

| _       | 1       | 1       | OUTA            | Amplifier Output Channel A   |

| _       | 2       | 2       | INA-            | Inverting Input Channel A    |

| _       | 3       | 3       | INA+            | Noninverting Input Channel A |

| _       | 5       | 7       | INB+            | Noninverting Input Channel B |

| _       | 6       | 8       | INB-            | Inverting Input Channel B    |

| _       | 7       | 9       | OUTB            | Amplifier Output Channel B   |

| _       | _       | 5       | SHDNA           | Shutdown Channel A           |

| _       | _       | 6       | SHDNB           | Shutdown Channel B           |

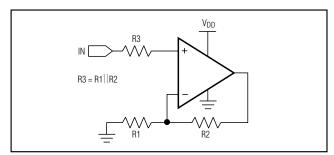

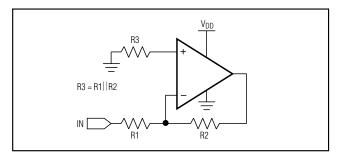

Figure 1a. Minimizing Offset Error Due to Input Bias Current (Noninverting)

#### **Detailed Description**

#### Rail-to-Rail Input Stage

The MAX4245/MAX4246/MAX4247 have rail-to-rail input and output stages that are specifically designed for low-voltage, single-supply operation. The input stage consists of composite NPN and PNP differential stages, which operate together to provide a common-mode range extending to both supply rails. The crossover region of these two pairs occurs halfway between  $V_{\rm DD}$  and Vss. The input offset voltage is typically  $\pm 400 \mu V$ . Low-operating supply voltage, low supply current and rail-to-rail outputs make this family of operational amplifiers an excellent choice for precision or general-purpose, low-voltage, battery-powered systems.

Since the input stage consists of NPN and PNP pairs, the input bias current changes polarity as the common-

Figure 1b. Minimizing Offset Error Due to Input Bias Current (Inverting)

mode voltage passes through the crossover region. Match the effective impedance seen by each input to reduce the offset error caused by input bias currents flowing through external source impedance (Figures 1a and 1b).

The combination of high-source impedance plus input capacitance (amplifier input capacitance plus stray capacitance) creates a parasitic pole that can produce an underdamped signal response. Reducing input capacitance or placing a small capacitor across the feedback resistor improves response in this case.

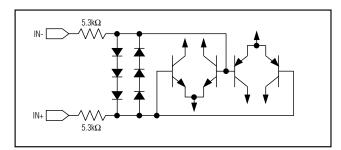

The MAX4245/MAX4246/MAX4247 family's inputs are protected from large differential input voltages by internal  $5.3k\Omega$  series resistors and back-to-back triple-diode stacks across the inputs (Figure 2). For differential-input voltages much less than 2.1V (triple-diode drop),

Figure 2. Input Protection Circuit

input resistance is typically  $4M\Omega$ . For differential voltages greater than 2.1V, input resistance is around  $10.6k\Omega$ , and the input bias current can be approximated by the following equation:

$$I_B = (V_{DIFF} - 2.1V) / 10.6k\Omega$$

In the region where the differential input voltage approaches 2.1V, the input resistance decreases exponentially from  $4M\Omega$  to  $10.6k\Omega$  as the diodes begin to conduct. It follows that the bias current increases with the same curve.

In unity-gain configuration, high slew-rate input signals may capacitively couple to the output through the triple-diode stacks.

#### Rail-to-Rail Output Stage

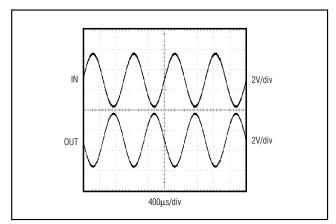

The MAX4245/MAX4246/MAX4247 can drive a  $2k\Omega$  load and still typically swing within 35mV of the supply rails. Figure 3 shows the output voltage swing of the MAX4245 configured with Ay = -1V/V.

#### **Applications Information**

#### **Power-Supply Considerations**

The MAX4245/MAX4246/MAX4247 operate from a single +2.5V to +5.5V supply (or dual ±1.25V to ±2.75V supplies) and consume only 320μA of supply current per amplifier. A 90dB power-supply rejection ratio allows the amplifiers to be powered directly off a decaying battery voltage, simplifying design and extending battery life.

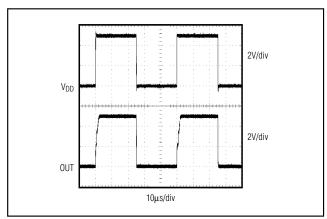

#### Power-Up

The MAX4245/MAX4246/MAX4247 output typically settles within 4µs after power-up. Figure 4 shows the output voltage on power-up and power-down.

#### **Shutdown Mode**

The MAX4245/MAX4247 feature a low-power shutdown mode. When SHDN\_ is pulled low, the supply current drops to 50nA per amplifier, the amplifier is disabled, and the output enters a high-impedance state. Pulling

Figure 3. Rail-to-Rail Input/Output Voltage Range

Figure 4. Power-Up/Power-Down Waveform

SHDN\_ high enables the amplifier. Figure 5 shows the MAX4245/MAX4247's shutdown waveform.

Due to the output leakage currents of three-state devices and the small internal pullup current for SHDN\_, do not let the SHDN\_ float. Floating SHDN\_ may result in indeterminate logic levels, and could adversely affect op amp operation. The logic threshold for SHDN\_ is referred to Vss. When using dual supplies, pull SHDN\_ to Vss, not GND, to shut down the op amp.

#### **Driving Capacitive Loads**

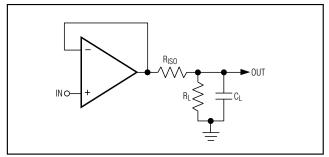

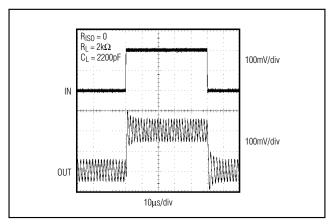

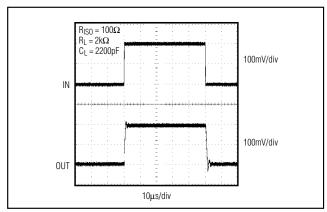

The MAX4245/MAX4246/MAX4247 are unity-gain stable for loads up to 470pF. Applications that require greater capacitive drive capability should use an isolation resistor between the output and the capacitive load

Figure 5. Shutdown Waveform

(Figure 6a-6c). Note that this alternative results in a loss of gain accuracy because R<sub>ISO</sub> forms a voltage divider with the R<sub>LOAD</sub>.

#### Power-Supply Bypassing and Layout

The MAX4245/MAX4246/MAX4247 family operates from either a single +2.5V to +5.5V supply or dual  $\pm 1.25$ V to  $\pm 2.75$ V supplies. For single-supply operation, bypass the power supply with a 100nF capacitor to Vss (in this case GND). For dual-supply operation, both the VDD and the Vss supplies should be bypassed to ground with separate 100nF capacitors.

Good PC board layout techniques optimize performance by decreasing the amount of stray capacitance at the op amp's inputs and output. To decrease stray capacitance, minimize trace lengths and widths by placing external components as close to the device as possible. Use surface-mount components when possible.

#### Pin Configurations (continued)

Figure 6a. Using a Resistor to Isolate a Capacitive Load from the Op Amp

Figure 6b. Pulse Response Without Isolating Resistor

Figure 6c. Pulse Response With Isolating Resistor

#### \_Chip Information

MAX4245 TRANSISTOR COUNT: 207

MAX4246/MAX4247 TRANSISTOR COUNT: 414

PROCESS: BiCMOS

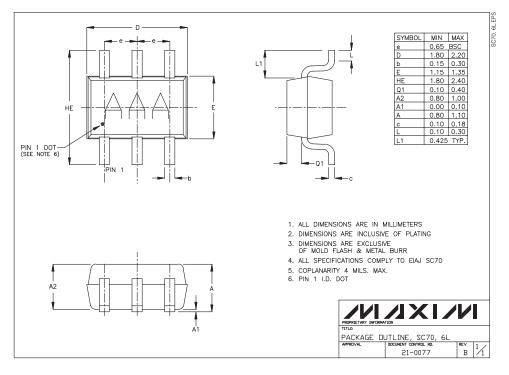

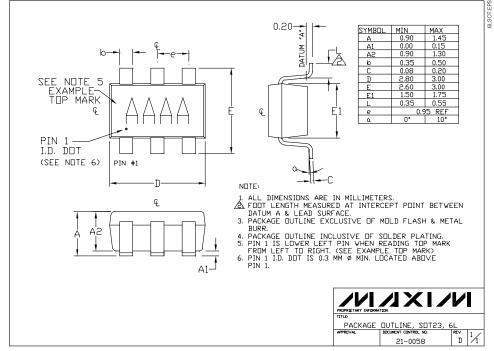

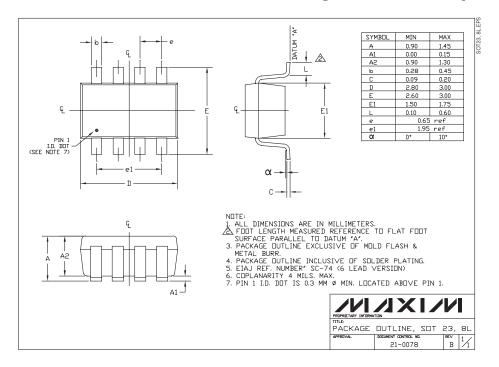

#### Package Information

#### Package Information (continued)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.