专业PCB打样工厂 **キタキ**7 24/// 마카미스 비신

**BICMOS STATIC RAM** 64K (8K x 8-BIT) CACHE-TAG RAM

**IDT71B74**

### **FEATURES:**

- High-speed address to MATCH comparison time Commercial: 8/10/12/15/20ns (max.)

- · High-speed address access time Commercial: 8/10/12/15/20ns (max.)

- · High-speed chip select access time WW.DZSC.COM Commercial: 6/7/8/10ns (max.)

- Power-ON Reset Capability

- Low power consumption

- 830mW (typ.) for 12ns parts

- 880mW (typ.) for 10ns parts

- 920mW (typ.) for 8ns parts

- Produced with advanced BiCMOS high-performance technology

- · Input and output directly TTL-compatible

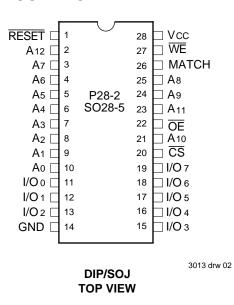

- Standard 28-pin plastic DIP and 28-pin SOJ (300 mil)

### **DESCRIPTION:**

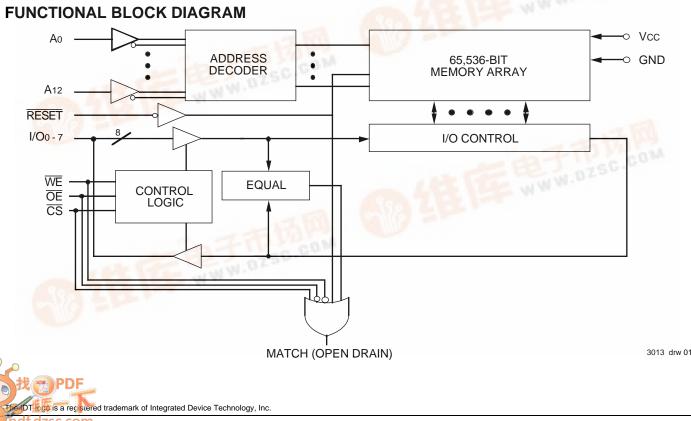

The IDT71B74 is a high-speed cache address comparator subsystem consisting of a 65,536-bit static RAM organized as 8K x 8 and an 8-bit comparator. A single IDT71B74 can map 8K cache words into a 2 megabyte address space by using the 21 bits of address organized with the 13 LSBs for the cache address bits and the 8 higher bits for cache data bits. Two IDT71B74s can be combined to provide 29 bits of address comparison, etc. The IDT71B74 also provides a single RAM clear control, which clears all words in the internal RAM to zero when activated. This allows the tag bits for all locations to be cleared at power-on or system-reset, a requirement for cache comparator systems. The IDT71B74 can also be used as a resettable 8K x 8 high-speed static RAM.

The IDT71B74 is fabricated using IDT's high-performance, high-reliability BiCMOS technology. Address access times as fast as 8ns, chip select times of 6ns and address-to-match times of 8ns are available.

The MATCH pin of several IDT71B74s can be wired-ORed together to provide enabling or acknowledging signals to the data cache or processor, thus eliminating logic delays and increasing system throughput.

#### COMMERCIAL TEMPERATURE RANGE

# PIN CONFIGURATION

### TRUTH TABLE<sup>(1, 2)</sup>

| WE | <u>CS</u> | ŌĒ | RESET | МАТСН | I/O  | Function              |

|----|-----------|----|-------|-------|------|-----------------------|

| х  | х         | Х  | L     | HIGH  | —    | Reset all bits to LOW |

| Х  | Н         | Х  | н     | HIGH  | Hi-Z | Deselect chip         |

| Н  | L         | Н  | н     | LOW   | DIN  | No MATCH              |

| Н  | L         | Н  | н     | HIGH  | DIN  | MATCH                 |

| Н  | L         | L  | Н     | HIGH  | Dout | Read                  |

| L  | L         | Х  | Н     | HIGH  | DIN  | Write                 |

NOTES:

1. H = VIH, L = VIL, X = DON'T CARE

2. HIGH = High-Z (pulled up by an external resistor), and LOW = Vol.

#### **PIN DESCRIPTIONS**

| Pin Names | Description                    |

|-----------|--------------------------------|

| A0-12     | Address                        |

| I/O0-7    | Data Input/Output              |

| CS        | Chip Select                    |

| RESET     | Memory Reset                   |

| МАТСН     | Data/Memory Match (Open Drain) |

| WE        | Write Enable                   |

| ŌĒ        | Output Enable                  |

| GND       | Ground                         |

| Vcc       | Power                          |

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol               | Rating                                  | Com'l.       | Unit |

|----------------------|-----------------------------------------|--------------|------|

| Vterm <sup>(2)</sup> | Terminal Voltage with<br>Respect to GND | -0.5 to +7.0 | V    |

| Та                   | Operating Temperature                   | 0 to +70     | °C   |

| TBIAS                | Temperature Under Bias                  | -55 to +125  | °C   |

| TSTG                 | Storage Temperature                     | -55 to +125  | °C   |

| Рт                   | Power Dissipation                       | 1.0          | W    |

| Ιουτ                 | DC Output Current                       | 50           | mA   |

NOTES:

3013 tbl 01

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. VTERM must not exceed Vcc + 0.5V.

#### CAPACITANCE

(TA = +25°C, f = 1.0MHz, SOJ Package)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| CIN    | Input Capacitance        | VIN = 3dV  | 6    | pF   |

| Соит   | Output Capacitance       | Vout = 3dV | 7    | pF   |

NOTE:

1. This parameter is determined by device characterization, but is not production tested.

3013 tbl 02

3013 tbl 04

# RECOMMENDED DC OPERATING CONDITIONS

| Symbol | Parameter                         | Min.                | Тур. | Max.               | Unit       |

|--------|-----------------------------------|---------------------|------|--------------------|------------|

| Vcc    | Supply Voltage                    | 4.5                 | 5.0  | 5.5                | V          |

| GND    | Supply Voltage                    | 0                   | 0    | 0                  | V          |

| Viн    | Input HIGH Voltage <sup>(1)</sup> | 2.2                 | _    | 6.0 <sup>(4)</sup> | V          |

| Vihr   | RESET Input Voltage               | 2.5 <sup>(2)</sup>  | _    | 6.0                | V          |

| VIL    | Input LOW Voltage                 | -0.5 <sup>(3)</sup> | _    | 0.8                | V          |

| NOTES: |                                   |                     |      | 30                 | 013 tbl 05 |

1. All inputs except RESET.

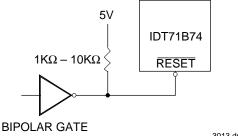

When using bipolar devices to drive the RESET input, a pullup resistor of 1kΩ–10kΩ is usually required to assure this voltage.

3. VIL (min.) = -1.5V for pulse width less than 10ns, once per cycle.

4. VTERM must not exceed Vcc + 0.5V.

### DC ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

$(VCC = 5.0V \pm 10\%, VLC = 0.2V, VHC = VCC - 0.2V)$

| Symbo | Parameter                                  |                       | 71B74S8 | 71B74S10 | 71B74S12 | 71B74S15 | 71B74S20 | Unit |

|-------|--------------------------------------------|-----------------------|---------|----------|----------|----------|----------|------|

| Icc   | Dynamic Operating Current                  | $\overline{WE} = VLC$ | 230     | 210      | 200      | 190      | 180      | mA   |

|       | Outputs Open, Vcc = Max., $f = fMAX^{(2)}$ | $\overline{WE} = VHC$ | 210     | 200      | 170      | 160      | 150      | mA   |

NOTES:

1. All values are maximum guaranteed values.

2. fMAX = 1/tRC, only input addresses are cycling at fMAX.

## DC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE

**AND SUPPLY VOLTAGE** (Vcc = 5.0V ± 10%)

|        |                        |                                                         | IDT7 <sup>,</sup> | 1B74S |      |

|--------|------------------------|---------------------------------------------------------|-------------------|-------|------|

| Symbol | Parameter              | Test Condition                                          | Min.              | Max.  | Unit |

| ILI    | Input Leakage Current  | Vcc = Max., VIN = GND to Vcc                            | —                 | 5     | μΑ   |

| Ilo    | Output Leakage Current | Vcc = Max., $\overline{CS}$ = VIH,<br>Vout = GND to Vcc |                   | 5     | μΑ   |

| Vol    | Output LOW Voltage     | Io∟ = 22mA MATCH                                        | —                 | 0.5   | V    |

|        |                        | Io∟ = 18mA MATCH                                        | —                 | 0.4   |      |

|        |                        | IoL = 10mA, Vcc = Min. (Except MATCH)                   | —                 | 0.5   |      |

|        |                        | IOL = 8mA, VCC = Min. (Except MATCH)                    | —                 | 0.4   |      |

| Vон    | Output HIGH Voltage    | Iон = -4mA, Vcc = Min. (Except MATCH)                   | 2.4               | _     | V    |

3013 tbl 08

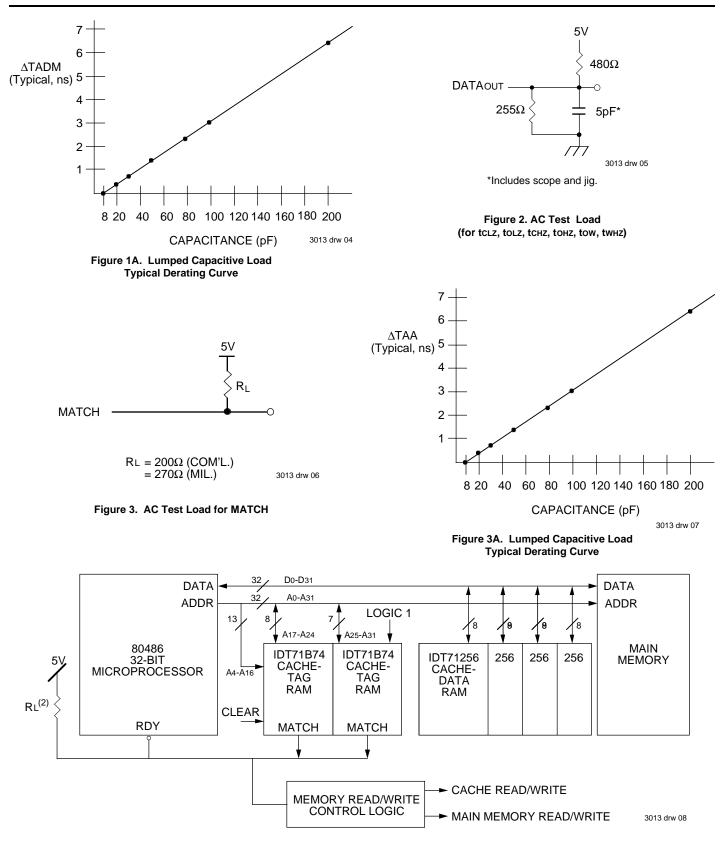

### AC TEST CONDITIONS

| Input Pulse Levels            | GND to 3.0V             |

|-------------------------------|-------------------------|

| Input Rise/Fall Times         | 3ns                     |

| Input Timing Reference Levels | 1.5V                    |

| Output Reference Levels       | 1.5V                    |

| AC Test Load                  | See Figures 1, 2, and 3 |

3013 tbl 09

### RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| Grade      | Ambient Temperature | GND | Vcc         |

|------------|---------------------|-----|-------------|

| Commercial | 0°C to +70°C        | 0V  | $5V\pm10\%$ |

3013 tbl 06

3013 tbl 07

DATAOUT

1.5V

50Ω

3013 drw 03

#### IDT71B74 BICMOS STATIC RAM 64K (8K x 8-BIT) CACHE-TAG RAM

#### **COMMERCIAL TEMPERATURE RANGE**

#### NOTES:

1. For more information refer to IDT Application Notes AN-07 and AN-78 and Technical Notes TN-11 and TN-13.

2. RL = 200Ω.

### **AC ELECTRICAL CHARACTERISTICS** (Vcc = $5.0V \pm 10\%$ )

|                     |                                    | 71B74S8 |      | 71B74S10 |      | 71B74S12 |      | 71B74S15 |      | 71B74S20 |      |      |

|---------------------|------------------------------------|---------|------|----------|------|----------|------|----------|------|----------|------|------|

| Symbol              | Parameter                          | Min.    | Max. | Min.     | Max. | Min.     | Max. | Min.     | Max. | Min.     | Max. | Unit |

| Read Cyc            | le                                 |         |      |          |      |          |      |          |      |          |      |      |

| tRC                 | Read Cycle Time                    | 8       | _    | 10       | —    | 12       |      | 15       | —    | 20       |      | ns   |

| tAA                 | Address Access Time                | _       | 8    | _        | 10   | _        | 12   | _        | 15   | _        | 20   | ns   |

| tACS                | Chip Select Access Time            | _       | 6    | _        | 7    | _        | 8    | _        | 8    | Ι        | 10   | ns   |

| tCLZ <sup>(1)</sup> | Chip Select to Output in Low-Z     | 2       | _    | 2        | —    | 2        |      | 3        | —    | 3        |      | ns   |

| tOE                 | Output Enable to Output Valid      | _       | 5    | _        | 6    | _        | 6    | _        | 8    |          | 9    | ns   |

| toLz <sup>(1)</sup> | Output Enable to Output in Low-Z   | 2       | _    | 2        | —    | 2        |      | 2        | —    | 2        |      | ns   |

| tCHZ <sup>(1)</sup> | Chip Select to Output in High-Z    | _       | 4    | _        | 5    | _        | 5    | _        | 7    |          | 8    | ns   |

| tonz <sup>(1)</sup> | Output Disable to Output in High-Z | —       | 4    | _        | 4    | _        | 5    | _        | 5    | _        | 8    | ns   |

| tон                 | Output Hold from Address Change    | 3       | _    | 3        | _    | 3        |      | 3        | _    | 3        | _    | ns   |

NOTE:

1. This parameter is guaranteed with the AC Load (Figure 2) by device characterization, but is not production tested.

3013 tbl 10

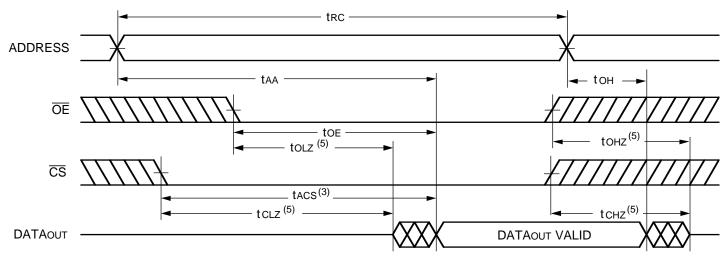

### TIMING WAVEFORM OF READ CYCLE NO. 1<sup>(1)</sup>

3013 drw 09

3013 drw 10

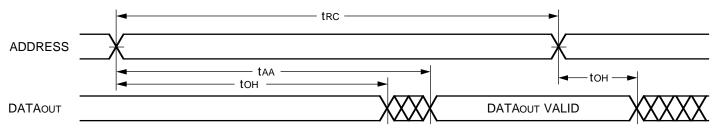

### TIMING WAVEFORM OF READ CYCLE NO. 2 (1, 2, 4)

#### NOTES:

- 1.  $\overline{\text{WE}}$  is HIGH for Read cycle.

- 2. Device is continuously selected,  $\overline{CS}$  is LOW.

3. Address valid prior to or coincident with  $\overline{\text{CS}}$  transition LOW; otherwise tAA is the limiting parameter.

4.  $\overline{OE}$  is continuously active,  $\overline{OE}$  is LOW.

5. Transition is measured  $\pm 200 \text{mV}$  from steady state.

#### COMMERCIAL TEMPERATURE RANGE

|                     |                                                           | 71B  | 71B74S8 |      | 74S10 | 71B74S12 |      | 71B74S15 |      | 71B74S20 |      |      |

|---------------------|-----------------------------------------------------------|------|---------|------|-------|----------|------|----------|------|----------|------|------|

| Symbol              | Parameter                                                 | Min. | Max.    | Min. | Max.  | Min.     | Max. | Min.     | Max. | Min.     | Max. | Unit |

| Write Cyc           | le                                                        | •    |         |      |       |          |      |          |      |          |      |      |

| twc                 | Write Cycle Time                                          | 8    | —       | 10   | —     | 12       | —    | 15       | _    | 20       | _    | ns   |

| tcw                 | Chip Select to End of Write                               | 7    | —       | 8    | _     | 9        | —    | 10       |      | 15       |      | ns   |

| taw                 | Address Valid to End of Write                             | 7    | _       | 8    | _     | 9        | —    | 10       | _    | 15       | _    | ns   |

| tAS                 | Address Set-up Time                                       | 0    | —       | 0    | _     | 0        | _    | 0        | _    | 0        | -    | ns   |

| tWP                 | Write Pulse Width                                         | 7    | —       | 8    | _     | 9        |      | 10       |      | 15       | _    | ns   |

| twr                 | Write Recovery Time ( $\overline{CS}$ , $\overline{WE}$ ) | 0    | —       | 0    | _     | 0        | _    | 0        |      | 0        | _    | ns   |

| twnz <sup>(1)</sup> | Write Enable to Output in High-Z                          | —    | 5       | _    | 5     |          | 5    | _        | 5    | _        | 5    | ns   |

| tDW                 | Data Valid to End of Write                                | 5    | —       | 5    | _     | 6        | _    | 8        |      | 10       | _    | ns   |

| tDH                 | Data Hold from Write Time                                 | 0    | _       | 0    |       | 0        | _    | 0        | _    | 0        | _    | ns   |

| tow <sup>(1)</sup>  | Output Active from End of Write                           | 2    | _       | 2    | _     | 2        | _    | 2        | _    | 2        | _    | ns   |

#### AC ELECTRICAL CHARACTERISTICS (Vcc = $5.0V \pm 10\%$ )

#### NOTE:

1. This parameter is guaranteed with the AC Load (Figure 2) by device characterization, but is not production tested.

3013 tbl 11

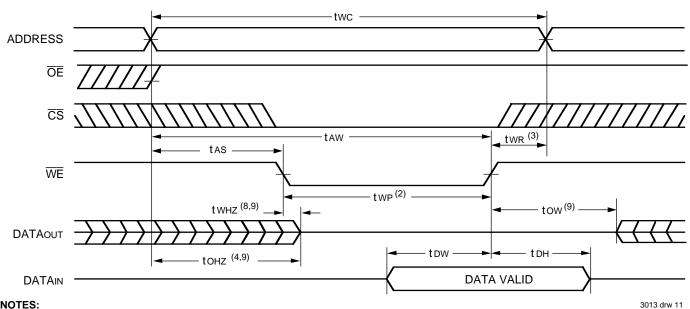

### TIMING WAVEFORM OF WRITE CYCLE NO. 1 (WE Controlled Timing, OE HIGH During Write)<sup>(1, 6)</sup>

#### NOTES:

- 1.  $\overline{\text{WE}}$ ,  $\overline{\text{CS}}$  must be inactive during all address transitions.

- 2. A write occurs during the overlap of a LOW  $\overline{\text{WE}}$  and a LOW  $\overline{\text{CS}}$ .

- 3. twe is measured from the earlier of  $\overline{CS}$  or  $\overline{WE}$  going HIGH to the end of the write cycle.

- 4. During this period, I/O pins are in the output state and input signals must not be applied.

- 5. If the CS LOW transition occurs simultaneously with or after the WE LOW transition, the outputs remain in a high-impedance state.

- 6.  $\overline{OE}$  is continuously HIGH,  $\overline{OE} \ge V_{H}$ . If during the  $\overline{WE}$  controlled write cycle the  $\overline{OE}$  is LOW, two must be greater or equal to twHz + tow to allow the I/O drivers to turn off and the data to be placed on the bus for the required tow. If OE is HIGH during the WE controlled write cycle, this requirement does not apply and the minimum write pulse is the specified twp. For a CS controlled write cycle, OE may be LOW with no degradation to tcw timing.

- 7. DATAOUT is never enabled, therefore the output is in High-Z state during the entire write cycle.

- 8. twHz is not included if OE remains HIGH during the write cycle. If OE is LOW during the Write Enabled write cycle then twHz must be added to twP and tcw.

- 9. Transition is measured  $\pm 200$  mV from steady state.

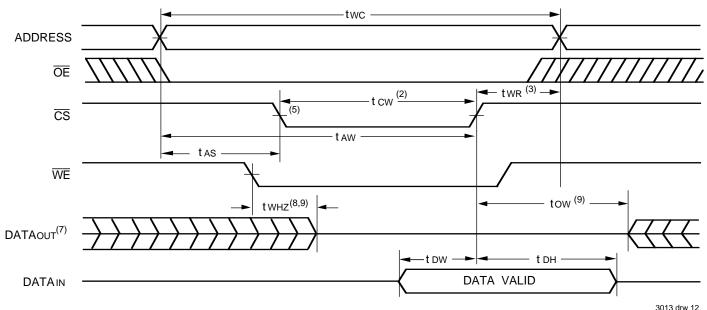

# TIMING WAVEFORM OF WRITE CYCLE NO. 2 (CS Controlled Timing)<sup>(1, 6)</sup>

#### NOTES:

- 1.  $\overline{\text{WE}}$ ,  $\overline{\text{CS}}$  must be inactive during all address transitions.

- 2. A write occurs during the overlap of a LOW  $\overline{\text{WE}}$  and a LOW  $\overline{\text{CS}}$ .

- 3. two is measured from the earlier of  $\overline{CS}$  or  $\overline{WE}$  going HIGH to the end of the write cycle.

- 4. During this period, I/O pins are in the output state and input signals must not be applied.

- 5. If the CS LOW transition occurs simultaneously with or after the WE LOW transition, the outputs remain in a high-impedance state.

- 6. OE is continuously HIGH, OE ≥ VIH. If during the WE controlled write cycle the OE is LOW, twp must be greater or equal to twHz + tbw to allow the I/O drivers to turn off and the data to be placed on the bus for the required tbw. If OE is HIGH during the WE controlled write cycle, this requirement does not apply and the minimum write pulse is the specified twp. For a CS controlled write cycle, OE may be LOW with no degradation to tcw timing.

- 7. DATAOUT is never enabled, therefore the output is in High-Z state during the entire write cycle.

- 8. twhz is not included if OE remains HIGH during the write cycle. If OE is LOW during the Write Enabled write cycle then twhz must be added to twp and tcw.

- 9. Transition is measured  $\pm 200 \text{mV}$  from steady state.

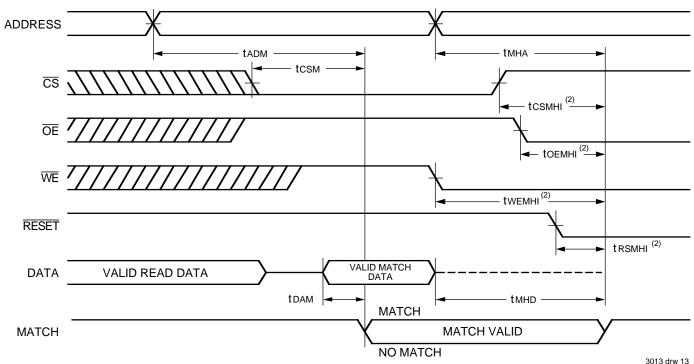

|                       |                               | 71B74S8 |      | 71B74S10 |      | 71B74S12 |      | 71B74S15 |      | 71B74S20 |      |      |

|-----------------------|-------------------------------|---------|------|----------|------|----------|------|----------|------|----------|------|------|

| Symbol                | Parameter                     | Min.    | Max. | Min.     | Max. | Min.     | Max. | Min.     | Max. | Min.     | Max. | Unit |

| Match Cy              | cle                           |         |      |          |      |          |      |          |      |          |      |      |

| tadm                  | Address to MATCH Valid        | _       | 8    | _        | 10   | —        | 12   | _        | 15   | —        | 20   | ns   |

| tCSM                  | Chip Select to MATCH Valid    | _       | 7    | _        | 7    | _        | 8    | _        | 10   | _        | 10   | ns   |

| tCSMHI <sup>(1)</sup> | Chip Select to MATCH HIGH     | _       | 7    |          | 8    |          | 8    | _        | 8    | —        | 8    | ns   |

| <b>t</b> DAM          | Data Input to MATCH Valid     | _       | 7    | _        | 8    | _        | 10   | _        | 12   | _        | 12   | ns   |

| toemhi <sup>(1)</sup> | OE LOW to MATCH HIGH          | _       | 7    |          | 8    | _        | 10   | _        | 10   | _        | 10   | ns   |

| twemhi <sup>(1)</sup> | WE LOW to MATCH HIGH          | _       | 7    | _        | 8    | _        | 10   | _        | 10   | _        | 10   | ns   |

| trsmhi <sup>(1)</sup> | RESET LOW to MATCH HIGH       | _       | 8    | _        | 10   | _        | 10   | _        | 12   | _        | 15   | ns   |

| tмна                  | MATCH Valid Hold From Address | 2       | —    | 2        | —    | 2        | —    | 2        | —    | 2        | —    | ns   |

| tмнD                  | MATCH Valid Hold From Data    | 2       | _    | 2        | _    | 2        | _    | 2        | _    | 2        | _    | ns   |

#### AC ELECTRICAL CHARACTERISTICS (Vcc = $5.0V \pm 10\%$ )

1. This parameter is guaranteed with the AC Load (Figure 3) by device characterization, but is not production tested.

NOTE:

### MATCH TIMING<sup>(1)</sup>

#### NOTES:

1. It is not recommended to float data and address input pins while the MATCH pin is active.

2. Transition is measured at ±200mV from steady state.

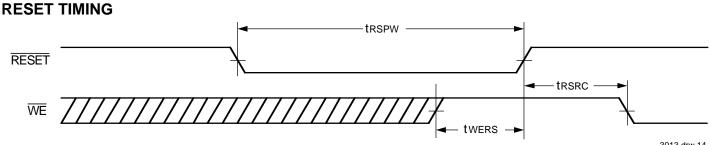

### AC ELECTRICAL CHARACTERISTICS (Vcc = $5.0V \pm 10\%$ )

|                      |                       | 71B74S8 |      | 71B74S10 |      | 71B74S12 |      | 71B74S15 |      | 71B74S20   |      |      |

|----------------------|-----------------------|---------|------|----------|------|----------|------|----------|------|------------|------|------|

| Symbol               | Parameter             | Min.    | Max. | Min.     | Max. | Min.     | Max. | Min.     | Max. | Min.       | Max. | Unit |

| Reset Cycle          |                       |         |      |          |      |          |      |          |      |            |      |      |

| trspw <sup>(1)</sup> | Reset Pulse Width     | 30      | —    | 35       |      | 35       | _    | 40       |      | 45         | —    | ns   |

| twers                | WE HIGH to Reset HIGH | 5       | _    | 5        | _    | 5        | _    | 5        |      | 5          | _    | ns   |

| tRSRC                | Reset HIGH to WE LOW  | 25      | _    | 25       | _    | 25       | _    | 30       |      | 30         | _    | ns   |

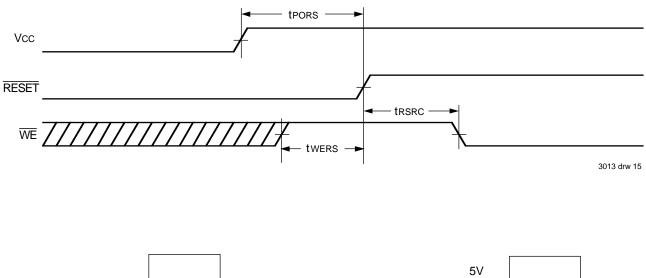

| tpors <sup>(2)</sup> | Power On Reset        | 100     |      | 100      | _    | 100      |      | 120      |      | 120        | _    | ns   |

| NOTES:               |                       |         |      |          |      |          |      |          |      | 3013 tbl 1 |      |      |

1. Recommended duty cycle = 10% maximum.

2. This parameter is guaranteed with the AC Load (Figure 1) by device characterization, but is not production tested.

3013 drw 14

#### **POWER ON RESET TIMING**

3013 drw 17

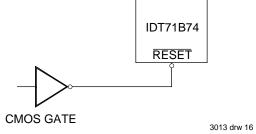

Driving the  $\overline{\text{RESET}}$  pin with CMOS logic.

Driving the RESET pin with bipolar logic.

Figure 5.

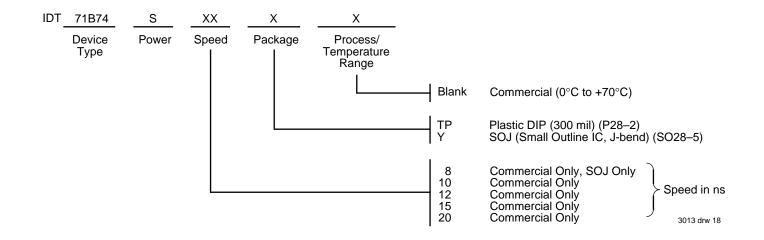

### **ORDERING INFORMATION**