# ST7271

# 8-BIT HCMOS MCUs WITH EEPROM AND TV/MONITOR DEDICATED FUNCTIONS

#### PRELIMINARY DATA

- 5V ± 10% supply operating range

- 4MHz Maximum Internal Clock Frequency

- Fully static operation

- 0 to +70°C Operating Temperature Range

- Run, Wait, and Stop Modes

- User ROM: up to

Data RAM: up to

EEPROM: up to

EWPCC EEPROM: 256 bytes

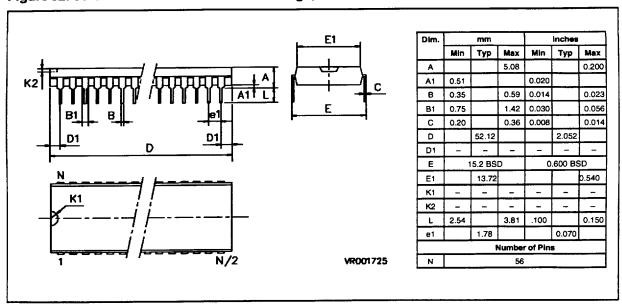

- 56 pin Shrink Dual In Line Package (ST7271N)

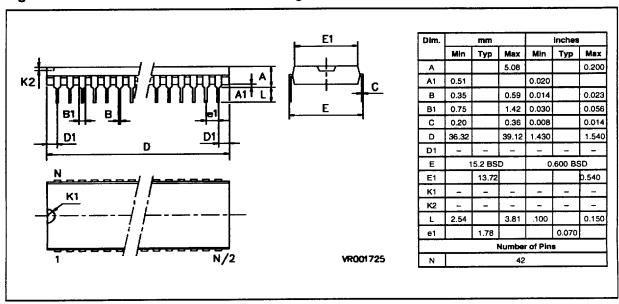

42 pin Shrink Dual In Line Package (ST7271J)

- up to 27 I/O lines8 I/O Open Drain with 12V capability

- up to 8 lines programmable as interrupt wake-up inputs

- 16-bit timer with 2 input capture and 2 output compare functions

- Sync Processor for video timing analysis

- East/West Pin Cushion Automatic Correction with DAC output.

- Watchdog for system reliability and integrity

- 8-bit Analog to Digital Converter with up to 8 channels

- 16 10-bit PWM/BRM Digital to Analog outputs

- 2 12-bit PWM/BRM Digital to Analog outputs

- Industry Standard Serial Peripheral Interface

- User mask options:

- SPI Data Rate

- Watchdog enable/disable after Reset

- Watchdog enable during WAIT mode

- Master Reset and Power-on reset

- Full Hardware Emulator

- 8-bit data manipulation

- 74 basic instructions

- 10 main addressing modes

- 8x8 unsigned multiply instruction

- true bit manipulation

- Complete development support on Real-time emulator with PC/DOS

- Full software package (Cross Assembler, debugger)

## **DEVICE SUMMARY**

| DEVICE   | ROM<br>(Bytes) | RAM<br>(Bytes) | EEPROM<br>(Bytes) | PACKAGE |

|----------|----------------|----------------|-------------------|---------|

| ST7271N5 | 16K            | 256            | 512               | PSDIP56 |

| ST7271N3 | 12K            | 256            | 512               | PSDIP56 |

| ST7271N1 | 8K             | 192            | 384               | PSDIP56 |

| ST7271J1 | 8K             | 192            | 384               | PSDIP42 |

December 1993

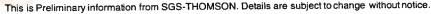

Figure 1a. 56 Pin Shrink DIP Pinout

ST7271N Pin Description

| Pin | Name             |         | Pin | Name       |

|-----|------------------|---------|-----|------------|

| 1   | V <sub>DDA</sub> | 1       | 56  | Vssa       |

| 2   | EWPCC            | 1       | 55  | Vss        |

| 3   | DA0              | 1       | 54  | PC5/SS     |

| 4   | DA1              | 1       | 53  | PC4/SCK    |

| 5   | DA2              | 1       | 52  | PC3/MOSI   |

| 6   | DA3              | 1       | 51  | PC2/MISO   |

| 7   | DA4              | 11      | 50  | PC1        |

| 8   | DA5              | ]       | 49  | PC0/OCMP   |

| 9   | DA6              | ]       | 48  | TEST       |

| 10  | DA7              | ] ]     | 47  | DA17       |

| 11  | DA8              | ]       | 46  | DA16       |

| 12  | DA9              | 11      | 45  | DA15       |

| 13  | PB7              | ] [     | 44  | DA14       |

| 14  | PB6              | ] [     | 43  | PA0        |

| 15  | PB5              | ] [     | 42  | PA1        |

| 16  | PB4              | ] [     | 41  | PA2        |

| 17  | PB3              | ]       | 40  | PA3        |

| 18  | PB2              | ]       | 39  | PA4        |

| 19  | PB1              | ]       | 38  | PA5        |

| 20  | VFBACK/PB0       | ][      | 37  | PA6        |

| 21  | PD4              | $\prod$ | 36  | PA7        |

| 22  | CLMPO/PD3        | ]       | 35  | DA13       |

| 23  | DA10             | ]       | 34  | DA12       |

| 24  | DA11             |         | 33  | OSCIN      |

| 25  | RESET            |         | 32  | OSCOUT     |

| 26  | VSYNCO/PD2       | ] [     | 31  | CSYNCI/PDO |

| 27  | VSYNCI           |         | 30  | HSYNCO/PD1 |

| 28  | V <sub>DD</sub>  |         | 29  | HSYNCI     |

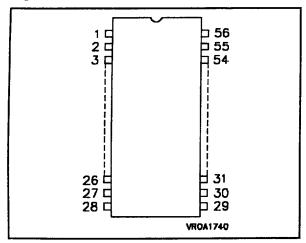

Figure 1b. 42 Pin Shrink DIP Pinout

ST7271J Pin Description

| Pin | Name             |

|-----|------------------|

| 1   | V <sub>DDA</sub> |

| 2   | EWPCC            |

| 3   | DA0              |

| 4   | DA1              |

| 5   | DA2              |

| 6   | DA3              |

| 7   | DA4              |

| 8   | DA5              |

| 9   | DA6              |

| 10  | DA7              |

| 11  | DA8              |

| 12  | DA9              |

| 13  | PB3              |

| 14  | PB2              |

| 15  | PB1              |

| 16  | VFBACK/PB0       |

| 17  | CLMPO/PD3        |

| 18  | RESET            |

| 19  | VSYNCO/PD2       |

| 20  | VSYNCI           |

| 21  | V <sub>DD</sub>  |

| Pin | Name             |

|-----|------------------|

| 42  | V <sub>SSA</sub> |

| 41  | V <sub>SS</sub>  |

| 40  | PC5/SS           |

| 39  | PC4/SCK          |

| 38  | PC3/MOSI         |

| 37  | PC2/MISO         |

| 36  | PC0/OCMP         |

| 35  | TEST             |

| 34  | PA0              |

| 33  | PA1              |

| 32  | PA2              |

| 31  | PA3              |

| 30  | PA4              |

| 29  | PA5              |

| 28  | PA6              |

| 27  | PA7              |

| 26  | OSCIN            |

| 25  | OSCOUT           |

| 24  | CSYNCI/PDO       |

| 23  | HSYNCO/PD1       |

| 22  | HSYNCI           |

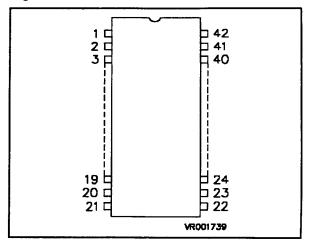

## 1 GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

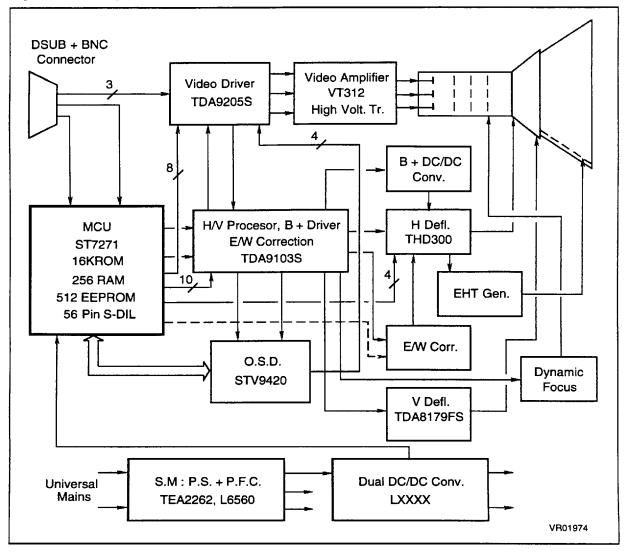

The ST7271 is a HCMOS microcontroller unit (MCU) from the ST72 family with dedicated peripherals for TV and Monitor applications.

It is based around an industry standard 8-bit core and offers an enhanced instruction set. The processor runs with an external clock at 8 MHz with a 5V supply. Due to the fully static design of this device, operation down to DC is possible. Under software control the ST7271 can be placed in WAIT or STOP mode thus reducing power consumption. The enhanced instruction set and addressing modes afford real programming potential.

In addition to standard 8-bit data management

Figure 2. ST7271 Block Diagram

the ST7271 feature strue bit manipulation, 8x8 unsigned multiplication and indirect addressing modes.

The device includes an on-chip oscillator, CPU, ROM, RAM, EEPROM, I/O, a timer with 2 input capture and 1 output compare signals, an 8-channel Analog to Digital Converter and an industry standard SPI as standard peripherals.

Dedicated functions include a Sync Processor for video timing analysis, East-West Pin Cushion automatic correction and 18 PWM/BRM outputs for analog control of external functions.

Note 1: ROM is replaced by EPROM for EPROM/OTP versions

SGS-THOMSON

#### 1.2 PIN DESCRIPTION

V<sub>DD</sub>. Power supply voltage

Vss. Digital Ground

**V<sub>DDA</sub>**. Analog V<sub>DD</sub> and reference for EWPCC Digital to Analog Converter (DAC, 8 Volts).

Vssa. Analog Vss for EWPCC DAC.

**OSCIN, OSCOUT.** Oscillator input and output pins. These pins are to be connected to a parallel resonant crystal or ceramic resonator. An external clock source can also be input on OSCIN.

**RESET.** The active low input signal forces the initialization of the MCU. This event is the top priority non maskable interrupt. This pin is switched low when the Watchdog has triggered. It can be used to reset external peripherals.

TEST. This pin must be held low for normal operation

**VFBACK (PB0).** Vertical Flyback signal (TTL level). This pin accepts the Vertical Flyback signal used for timing correlation for the East-west Pin Cushion correction when this is used or is PB0.

**EWPCC.** Analogoutput of correction signal from East-West Pin Cushion controller (2-6V, lout = 1mA).

**OCMP (PC0).** Output compare signal coming from the TIMER. This output signal, according to a register bit option, can be the OCMP pin (for output compare 1 of the timer) or the PC0 pin.

MISO (PC2). SPI Master Out/Slave In Data Output/Input when SPI is enabled or PC2.

MOSI (PC3). SPI Master In/Slave Out Data Input/Output when SPI is enabled or PC3.

**SCK (PC4).** SPI Serial Clock when SPI is enabled or PC4

**SS (PC5).** SPI Slave Select when SPI is enabled or PC5.

**VSYNCI**. Vertical Sychronization Input (TTL level)

HSYNCI. Horizontal Sychronization Input (TTL level)

**CSYNCI (PD0).** Composite Sychronization Input (TTL level). This pin accepts the composite synchronisation input when the Sync Processor I/O functions are enabled or is PD0.

**HSYNCO (PD1).** Horizontal Sychronization Output. This pin outputs the horizontal synchronisation output from the Sync Processor (or HSYNCI) when the Sync Processor I/O functions are enabled or is PD1.

VSYNCO (PD2). Vertical Sychronization Output. This pin outputs the vertical synchronisation output from the Sync Processor (or VSYNCI) when the Sync Processor I/O functions are enabled or is PD2.

**CLMPO (PD3).** Clamp Output. This pin outputs the clamping (back porch) output signal from the Sync Processor (or HSYNCI) when the Sync Processor I/O functions are enabled or is PD3.

DA2-DA17 (56-pin package),

DA2-DA9 (42-pin package), 10-bit PWM/BRM outputs (for Analog controls, after external filtering)

**DA0, DA1.** 12-bit PWM/BRM outputs (for Analog Controls, after external filtering).

**PA0-PA7, PB0-PB7, PC0-PC5, PD0-PD4** (56 pin package). These 27 lines are standard I/O lines, programmable as either input or output.

- PORT A. 8 I/O lines, bit programmable, accessed through DDRA and DRA Registers. Each bit can be defined as a standard input port bit without pull-up resistor or as an open drain output port (up to 12V).

- PORT B. 8 Standard I/O lines bit programmable accessed through DDRB and DRB Registers. Each bit can be programmed as an analog input (by control bits in the PORT B Configuration register), digital input (with internal pull-up resistor), push-pull digital output or as interrupt wake-up (with pull-up). These negative edge or low-level sensitive interrupt lines can wake-up the ST7271 from WAIT or STOP mode. This feature allows to build low power applications when the ST7271 can be waken-up from keyboard push.

PB0 is used for the East-West Pin cushion controller VFBACK input as shown above when the EWPCC is used.

- PORT C. 6 Standard I/O lines accessed through DDRC and DRC Registers. Each bit can be programmed as digital input (with or without pull-up internal resistor), open drain output or SPI control and data signals (as shown for the dedicated SPI signals above). Whenever the SPI is active, the outputs are in the pull-pull configuration.

The pull-up resistor is enabled for all bits present by one control bit in the Programmable Input/Output Configuration Register. The resistor is automatically disabled for the pins used for the SPI when the SPI is enabled.

- PORT D. 4 Standard I/O lines bit programmable accessed through DDRD and DRD Registers. Each bit can be programmed as an input (with internal pull-up resistor), push-pull output or Synchronization inputs and outputs to/from the Sync Processor. When programmed as inputs, Video Synchronisation signals can be directly inspected. The inputs may also be passed through the Sync Processor to the Timer Input Captures

These pin functions are also summarised in the following table, which also indicates the availability of functions for the 42-pin SDIP package.

4/95

SGS-THOMSON

## PIN DESCRIPTION (Continued)

## Table 1. ST7271 Pin Description

| Pin Name         | Pin Function(s)                  | 56<br>Pins | 42<br>Pins |

|------------------|----------------------------------|------------|------------|

| V <sub>DDA</sub> | Analog V <sub>DD</sub> for EWPCC | 1          | 1          |

| EWPCC            | EWPCC output voltage             | 2          | 2          |

| DA0              | 12-bit PWM/BRM output*           | 3          | 3          |

| DA1              | 12-bit PWM/BRM output            | 4          | 4          |

| DA2              | 10-bit PWM/BRM output*           | 5          | 5          |

| DA3              | 10-bit PWM/BRM output            | 6          | 6          |

| DA4              | 10-bit PWM/BRM output            | 7          | 7          |

| DA5              | 10-bit PWM/BRM output            | 8          | 8          |

| DA6              | 10-bit PWM/BRM output            | 9          | 9          |

| DA7              | 10-bit PWM/BRM output            | 10         | 10         |

| DA8              | 10-bit PWM/BRM output            | 11         | 11         |

| DA9              | 10-bit PWM/BRM output            | 12         | 12         |

| PB7              | I/O Port PB7                     | 13         |            |

| PB6              | I/O Port PB6                     | 14         |            |

| PB5              | I/O Port PB5                     | 15         |            |

| PB4              | I/O Port PB4                     | 16         |            |

| PB3              | I/O Port PB3                     | 17         | 13         |

| PB2              | I/O Port PB2                     | 18         | 14         |

| PB1              | I/O Port PB1                     | 19         | 15         |

| VFBACK/PB0       | I/O Port PB0<br>/VFBACK Input    | 20         | 16         |

| PD4              | I/O Port PD4                     | 21         |            |

| CLMPO/PD3        | I/O Port PD3/Clamp Output        | 22         | 17         |

| DA10             | 10-bit PWM/BRM output 10         | 23         |            |

| DA11             | 10-bit PWM/BRM output 11         | 24         |            |

| RESET            | Reset Input/Output               | 25         | 18         |

| VSYNCO/PD2       | I/O Port PD2/VSYNC<br>Output     | 26         | 19         |

| VSYNCI           | VSYNC Input to Sync<br>Processor | 27         | 20         |

| $V_{DD}$         | Power Supply                     | 28         | 21         |

| HSYNCI           | HSYNC Input to Sync<br>Processor | 29         | 22         |

| Pin Name   | Pin Function(s)                       | 56<br>Pins | 42<br>Pins |

|------------|---------------------------------------|------------|------------|

| HSYNCO/PD1 | I/O Port PD1/HSYNC<br>Output          | 30         | 23         |

| CSYNCI/PDO | I/O Port PD0/CSYNC Input              | 31         | 24         |

| OSCOUT     | Oscillator Output                     | 32         | 25         |

| OSCIN      | Oscillator Input                      | 33         | 26         |

| DA12       | 10-bit PWM/BRM output 12              | 34         |            |

| DA13       | 10-bit PWM/BRM output 13              | 35         |            |

| PA7        | I/O Port PA7                          | 36         | 27         |

| PA6        | I/O Port PA6                          | 37         | 28         |

| PA5        | I/O Port PA5                          | 38         | 29         |

| PA4        | I/O Port PA4                          | 39         | 30         |

| PA3        | I/O Port PA3                          | 40         | 31         |

| PA2        | I/O Port PA2                          | 41         | 32         |

| PA1        | I/O Port PA1                          | 42         | 33         |

| PA0        | I/O Port PA0                          | 43         | 34         |

| DA14       | 10-bit PWM/BRM output 14              | 44         |            |

| DA15       | 10-bit PWM/BRM output 15              | 45         |            |

| DA16       | 10-bit PWM/BRM output 16              | 46         |            |

| DA17       | 10-bit PWM/BRM output 17              | 47         |            |

| TEST       | TEST input,<br>must be held to Vss    | 48         | 35         |

| PC0/OCMP   | I/O Port PC0,<br>Timer Output Compare | 49         | 36         |

| PC1        | I/O Port PC1                          | 50         |            |

| PC2/MISO   | I/O Port PC2, SPI Data                | 51         | 37         |

| PC3/MOSI   | I/O Port PC3, SPI Data                | 52         | 38         |

| PC4/SCK    | I/O Port PC4,<br>SPI Clock output     | 53         | 39         |

| PC5/SS     | I/O Port PC5,<br>SPI Slave Select     | 54         | 40         |

| Vss        | Digital ground                        | 55         | 41         |

| VSSA       | Analog ground for EWPCC               | 56         | 42         |

Note \*: Open Drain

#### 1.3 CENTRAL PROCESSING UNIT

#### 1.3.1 Introduction

The CPU has a full 8-bit parallel architecture. Six internal registers allow efficient 8-bit data manipulations. The CPU is able to execute 74 basic instructions with 9 main addressing modes. It is able to address 16k bytes of memory and registers with its program counter.

## 1.3.2 CPU Registers

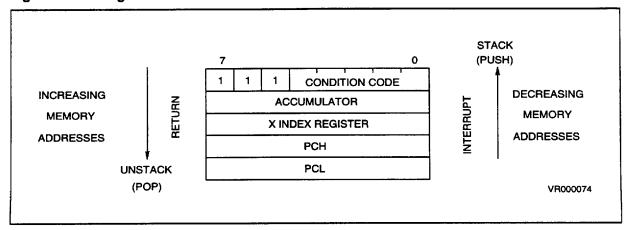

The 6 CPU registers are shown in the programming model in Figure 3. Following an interrupt, all registers except Y are pushed onto the stack in the order shown in Figure 4. They are popped from stack in the reverse order.

The Y register is not affected by these automatic procedures. The interrupt routine must therefore handle Y, if needed, through the POP and PUSH instructions.

Accumulator (A). The accumulator is an 8-bit general purpose register used to hold operands

and the results of the arithmetic and logic calculations as well as data manipulations.

Index Registers (X and Y). These 8-bit registers are used to create effective addresses or as temporary storage area for data manipulations. The Y register is never automatically stacked. Interrupt routines must push or pop it by using the POP and PUSH instructions.

**Program Counter (PC).** The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. In the ST7271, only the 14 low order bits are used, bits 14 and 15 are forced to '0' giving an addressing range of 0-3FFFh.

Stack Pointer (SP). The stack pointer is a 16-bit register. The 6 least significant bits contain the address of the next free location of the stack. The 10 most significant bits are forced as indicated in Figure 3.

Figure 3. Programming Model

| ACCUMULATOR:             | 7 0                                               |

|--------------------------|---------------------------------------------------|

|                          | RESET VALUE:                                      |

|                          | $x \; x \; x \; x \; x \; x \; x$                 |

|                          | 7 0                                               |

| X INDEX REGISTER:        |                                                   |

|                          | RESET VALUE:                                      |

|                          | X X X X X X X X 7 0                               |

| Y INDEX REGISTER:        | <del>– – – – – – – – – – – – – – – – – – – </del> |

| I INDEXTIGATED.          | RESET VALUE:                                      |

|                          | XXXXXXX                                           |

|                          | 15 , 7 0                                          |

| PROGRAM COUNTER:         | 0 0                                               |

|                          | RESET VALUE:                                      |

|                          | RESET VECTOR (3FFEh:3FFFh)                        |

|                          | 15 7 0                                            |

| STACK POINTER:           |                                                   |

|                          | RESET VALUE:<br>0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1   |

|                          | 7 6 5 4 3 2 1 0                                   |

| CONDITION CODE REGISTER: | 7 0 3 4 3 2 T 0                                   |

| CONSTROIT COSE REGIOTER. | RESET VALUE:                                      |

| X = Undefined            | 1 1 1 0 1 0 1 0                                   |

|                          | VR01971                                           |

6/95

SCS-THOMSON

## **CENTRAL PROCESSING UNIT (Continued)**

The stack is used to save the CPU context on subroutines calls or interrupts. The user can also directly manipulate the stack through the PUSH and POP instructions.

After a MCU reset or after the reset stack pointer instruction (RSP), the stack pointer is set to its upper value (FFh). It is then decremented after data has been pushed onto the stack and incremented after data is popped from the stack. When the lower limit is exceeded, the stack pointer wraps around to the stack upper limit. The previously stored information is then overwritten and therefore lost.

A subroutine call occupies two stack locations and an interrupt five locations.

## 1.3.3 Condition Code Register (CC).

The condition code register is a 5 bit register which indicates the result of the instruction just executed as well as the state of the processor. These bits can be individually tested by a program and specified action taken as a result of their state. The following paragraphs describe each bit.

Half carry bit (H). The H bit is set to 1 when a carry occurs between the bits 3 and 4 of the ALU during an ADD, ACC, SUB or SBC instructions. The H bit is useful in BCD arithmetic subroutines.

Interrupt mask (I). When the I bit is set to 1, all interrupts except the TRAP software interrupt are disabled. Clearing this bit enables interrupts to be passed to the core. Interrupts requested while I is set are latched and can be processed when I is cleared (only one interrupt request per interrupt enable flag can be latched).

**Negative (N).** When set to 1, this bit indicates that the result of the last data manipulation is negative (i.e. the most significant bit is a logic 1).

**Zero (Z).** When set to 1, this bit indicates that the result of the last data manipulation is zero.

Carry/Borrow (C). When set, C indicates that a carry or borrow out of the ALU occurred during the last arithmetic operation. This bit is also affected during bit test and branch, shift and rotate instructions.

Figure 4. Stacking Order

#### 1.4 MEMORY MAP

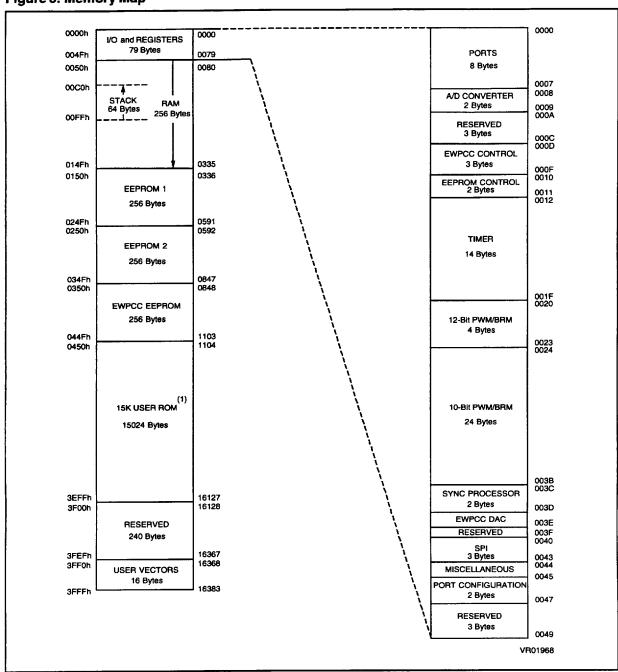

As shown in Figure 5, the MCU is capable of addressing 16K bytes of memory and I/O registers. In the ST7271, 16383 of these bytes are user accessible.

The available memory locations consist of 80 bytes of I/O registers, 256 bytes of RAM, 512 bytes of

EEPROM, 256 bytes of EWPCC EEPROM and 15Kbytes of user ROM. The RAM space includes 64 bytes for the stack from 00FFh to 00C0h.

The highest address bytes contain the user defined reset and interrupt vectors

Figure 5. Memory Map

Note 1: ROM is replaced by EPROM for EPROM/OTP versions.

8/95

SGS-THOMSON

## 1.5 I/O and REGISTER MAP

| Address         | Register Name                    |

|-----------------|----------------------------------|

| 0000h           | PORT A DATA REGISTER             |

| 0001h           | PORT B DATA REGISTER             |

| 0002h           | PORT C DATA REGISTER             |

| 0003h           | PORT D DATA REGISTER             |

| 0004h           | PORT A DATA DIRECTION REGISTER   |

| 0005h           | PORT B DATA DIRECTION REGISTER   |

| 0006h           | PORT C DATA DIRECTION REGISTER   |

| 0007h           | PORT D DATA DIRECTION REGISTER   |

| 0008h           | A/D DATA REGISTER                |

| 0009h           | A/D CONTROL/STATUS REGISTER      |

| 000Ah-<br>000Ch | Reserved                         |

| 000Dh           | EWPCC0 REGISTER                  |

| 000Eh           | EWPCC1 REGISTER                  |

| 000Fh           | EWPCC EEPROM CONTROL REGISTER    |

| 0010h           | EEPROM 1 CONTROL REGISTER        |

| 0011h           | EEPROM 2 CONTROL REGISTER        |

| 0012h           | TIMER CONTROL REGISTER           |

| 0013h           | TIMER STATUS REGISTER            |

| 0014h           | INPUT CAPTURE REGISTER 1, High   |

| 0015h           | INPUT CAPTURE REGISTER 1, Low    |

| 0016h           | OUTPUT COMPARE REGISTER 1, High  |

| 0017h           | OUTPUT COMPARE REGISTER 1, Low   |

| 0018h           | COUNTER REGISTER, High           |

| 0019h           | COUNTER REGISTER, Low            |

| 001Ah           | ALTERNATE COUNTER REGISTER, High |

| 001Bh           | ALTERNATE COUNTER REGISTER, Low  |

| 001Ch           | INPUT CAPTURE REGISTER 2, High   |

| 001Dh           | INPUT CAPTURE REGISTER 2, Low    |

| 001Eh           | OUTPUT COMPARE REGISTER 2, High  |

| 001Fh           | OUTPUT COMPARE REGISTER 2, Low   |

| 0020h           | PWM0 - 12 bit PWM/BRM            |

| 0021h           | BRM0 - 12 bit PWM/BRM            |

| 0022h           | PWM1 - 12 bit PWM/BRM            |

| 0023h           | BRM1 - 12 bit PWM/BRM            |

| 0024h           | PWM2 - 10 bit PWM/BRM            |

| 0025h           | BRM3+BRM2                        |

| Address       | Register Name                                       |

|---------------|-----------------------------------------------------|

| 0026h         | PWM3                                                |

| 0027h         | PWM4                                                |

| 0028h         | BRM5+BRM4                                           |

| 0029h         | PWM5                                                |

| 002Ah         | PWM6                                                |

| 002Bh         | BRM7+BRM6                                           |

| 002Ch         | PWM7                                                |

| 002Dh         | PWM8                                                |

| 002Eh         | BRM9+BRM8                                           |

| 002Fh         | PWM9                                                |

| 0030h         | PWM10                                               |

| 0031h         | BRM11+BRM10                                         |

| 0032h         | PWM11                                               |

| 0033h         | PWM12                                               |

| 0034h         | BRM13+BRM12                                         |

| 0035h         | PWM13                                               |

| 0036h         | PWM14                                               |

| <b>0037</b> h | BRM15+BRM14                                         |

| 0038h         | PWM15                                               |

| <b>00</b> 39h | PWM16                                               |

| 003Ah         | BRM17+BRM16                                         |

| 003Bh         | PWM17                                               |

| 003Ch         | SYNC MUX CONTROL REGISTER                           |

| 003Dh         | SYNC COUNTER CONTROL REGISTER                       |

| 003Eh         | EWPCC DAC REGISTER                                  |

| 003Fh         | Reserved                                            |

| 0040h         | SPI DATA I/O REGISTER                               |

| 0041h         | Reserved                                            |

| 0042h         | SPI CONTROL REGISTER                                |

| 0043h         | SPI STATUS REGISTER                                 |

| 0044h         | MISCELLANEOUS REGISTER                              |

| 0045h         | PORT B CONFIGURATION REGISTER                       |

| 0046h         | PROGRAMMABLE INPUT/OUTPUT<br>CONFIGURATION REGISTER |

| 0047h         | Reserved                                            |

| 0048h         | Reserved                                            |

| 0049h         | Reserved                                            |

SGS-THOMSON NICE

#### 1.6 WATCHDOG SYSTEM

The watchdog system consists in a divider-by-8 counter and a fixed divide-by-1024 prescaler. It is controlled through bit WDOG of the Misœllaneous Register.

Two mask options are provided:

- The WATCHDOG ENABLE mode mask option

- The WATCHDOG DURING WAIT mask option

The Watchdog Enable Mode mask option selects the state of the watchdog system after an external or a power-on reset. In the "programmable enable" option, a reset causes the watchdog to be disabled and the counter to be forced to zero. In the "auto enable" option, the watchdog is automatically enabled after the start-up procedure.

When the watchdog is configured with the "programmable enable" option, the watchdog system is enabled by setting the WDOG bit of the Miscellaneous Register (0044h). Only an external or a power-on reset can clear WDOG and disable the watchdog system.

Whatever the option, when the watchdog counter is enabled, it is driven by the CPU clock through the divide-by-1024 prescaler (i.e. the counter clock period is 1024 CPU clock cycles). It is reset to zero by writing WDOG at 1. A system reset is generated if the counter reaches its maximum count (8). To avoid a system reset, the software must therefore regularly reset the counter at least before the watchdog time from the last clear or from the time the watchdog system has been enabled.

Care has to be taken when enabling the counter ("programmable enable" option only). The prescaler is in an unknown state at the time WDOG is set. The first rising edge can thus be sent to the watchdog counter after a time comprised between 0 and 1024 CPU clock cycles. In this mode, the first reset of the watchdog counter should therefore not occur later than 6x1024 to 7x1024 CPU clock cycles after it has been enabled.

The system reset is generated by pulling down the RESET pin for at least one and a half CPU clock cycle. The state of the RESET pin is re-entered to the reset logic, thus causing an external reset to be issued.

The Watchdog During Wait mask option determines the watchdog function during the WAIT low power mode. In the "active during WAIT" option, the watchdog is kept active, thus able to reset the MCU if it remains in WAIT mode longer than the watchdog timeout period. In the "suspended during WAIT" option, it suspends operation during the WAIT mode and resets its counter. It will then resume operation when exiting the WAIT mode.

The STOP mode is inhibited when the watchdog system is enabled. However if a STOP instruction is executed while it is enabled, a watchdog reset is immediately generated.

## **MISCELLANEOUS REGISTER** (0044h)

Read/Write

Reset Value: 1111 1010 (FAh)

|   |   |   | 0 |   |       |     |      |

|---|---|---|---|---|-------|-----|------|

| 1 | 1 | 1 | 1 | 1 | VSYNC | INT | WDOG |

b7-b3 = Unused, read "1" when accessed.

b2 = **VSYNCI:** Internal Vsync (Read-Only) This bit shows the state of the Vsync output by the Sync Processor.

b1 = INT: Interrupt Request. This bit sets the interrupt configuration for the PORT B wakeup Interrupt Request:

INT = 0 : selects the falling edge option only

INT = 1 : selects the falling edge or low-level option

**WARNING.** This bit can only be written ONCE after reset. Writing to INT is disabled after the first write to the Miscellaneous Register. Bit manipulation instructions should be used with extreme caution when writing to this register.

b0 = WDOG: Watchdog System. Whatever the WATCHDOG ENABLE MODE mask option, the watchdog counter is reset when WDOG is written at 1. When the MCU is configured with the "programmable enable" option, the WDOG bit is low after a reset. It must be set to enable the watchdog system. Writing a '0' clears the WDOG bit, but does not change the watchdog condition. Only a reset can clear WDOG.

#### 1.7 SYSTEM CLOCK

#### General description.

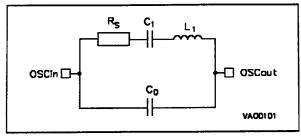

The MCU accepts either a Crystal/Ceramic resonator or an external clock to provide the internal oscillator.

The internal clock (fint) is derived by a divide-by-2 from the internal oscillator frequency (fosc).

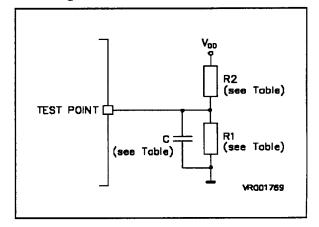

Crystal. The internal oscillator is designed to interface with an AT cut parallel resonant quartz crystal resonator in the frequency range specified for bsc. The circuit shown on Figure 6 is recommended when using a crystal. Use of an external CMOS oscillator is recommended when crystals outside the specified ranges are to be used. The crystal and components should be mounted as close as possible to the input pins to minimize output distortion and startup stabilization time.

Ceramic Resonator. A ceramic resonator may be used in place of the crystal in low cost applications. The circuit on Figure 6 is recommended when using a ceramic resonator. The manufacturer of the particular ceramic resonator being considered should be consulted for specific information.

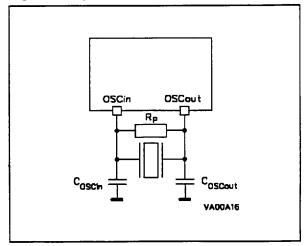

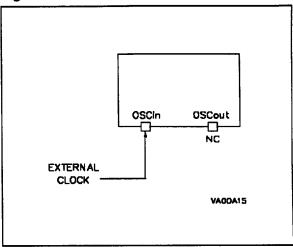

External Clock. An external clock should be applied to the OSCIN input with the OSCOUT pin not connected as shown figure 7. The Crystal clock specifications do not apply when using an external clock input. The equivalent specification of the external clock source should be used.

Figure 8. Equivalent Crystal Circuit

## **Recommended Settings for Crystal**

|                | 2MHz  | 4MHz  | Unit            |

|----------------|-------|-------|-----------------|

| RSMAX          | 400   | 75    | Ω               |

| Co             | 5     | 7     | pF              |

| C <sub>1</sub> | 0.008 | 0.012 | рF              |

| Coscin         | 15-40 | 15-30 | pF              |

| Coscout        | 15-30 | 15-25 | pF              |

| R <sub>P</sub> | 10    | 10    | МΩ              |

| Q              | 30    | 40    | 10 <sup>3</sup> |

Figure 6. Crystal/Ceramic Resonator

Figure 7. External Clock Source Connections

## **Recommended Settings for Ceramic** Resonator

|                   | 2-4MHz | Unit |

|-------------------|--------|------|

| R <sub>SMAX</sub> | 10     | Ω    |

| Co                | 40     | pF   |

| C <sub>1</sub>    | 4.3    | pF   |

| Coscin            | 30     | pF   |

| Coscout           | 30     | pF   |

| Rp                | 1-10   | МΩ   |

| Q                 | 1250   |      |

#### **1.8 RESET AND INTERRUPTS**

The Reset procedure is used to provide an orderly software startup or to quit low power modes.

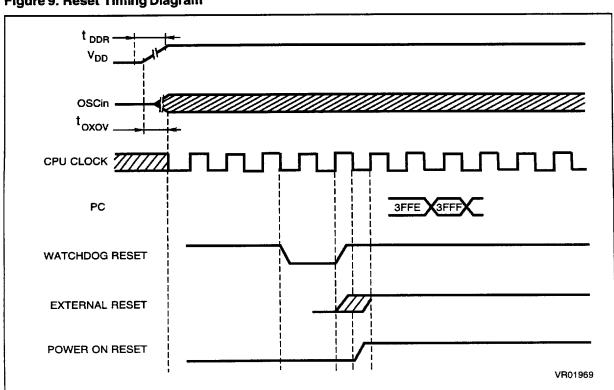

Two reset modes are provided: a power-on reset and an external reset at the RESET pin. The watchdog reset is considered as an external interrupt as the watchdog system generates the MCU reset by pulling down the RESET pin.

#### 1.8.1 Power-on Reset (POR)

The power-on reset is generated upon detection of a positive transition on  $V_{DD}$  (refer to Figure 9). It causes the reset vector to be fetched from addresses 3FFEh and 3FFFh in order to be loaded into the PC and with program execution starting from this point.

An internal circuitry provides a 4096 CPU clock cycle delay from the time that the oscillator becomes active. At the end of the power-on reset, the MCU can be maintained in the reset condition by holding the external reset low. The RESET pin can therefore be used to ensure  $V_{DD}$  has risen to a point where the MCU can properly operate before running the MCU program.

During the POR, the RESET pin is pulled low, thus

permitting the MCU to reset other devices.

The power-on reset is strictly used for power up conditions and should not be used to detect any drop in the power supply voltage. There is no internal provision for a power-down reset.

#### 1.8.2 External Reset

The external reset is an active low input signal applied to the RESET pin of the MCU.

As shown in Figure 9, the RESET signal must stay low for a minimum of one and a half CPU clock cycles. A reset causes the reset vector to be fetched at addresses 3FFEh and 3FFFh in order to be loaded into the PC and with program execution starting from this point.

The external reset is also used by the watchdog system to reset the MCU. When active, the power-on reset circuitry pulls down the RESET pin. In both cases, the RESET pin can be used as an output to reset other devices. However, the pull-down circuitry includes current limitation to allow the connection of any input signal, including from an RC type circuit.

An internal Schmitt trigger at the RESET pin is provided to improve immunity to noise.

Table 2. List of sections affected by RESET, WAIT and STOP

| Section                                  |           |             | RESE | t        | POR | WAIT | STOP |   |

|------------------------------------------|-----------|-------------|------|----------|-----|------|------|---|

| Timer Prescaler reset to zero            |           | Х           |      | k        |     | -    | _    |   |

| Timer Counter set to FFFCh               |           | X           | )    | <b>{</b> | -   |      |      |   |

| All Timer enable bit set to 0 (disable)  |           |             | X    | >        | (   | -    | -    |   |

| Data Direction Registers set to 0 (as Ir | nputs)    |             |      | x        |     | x    | - ,  | - |

| Set Stack Pointer to 00FFh               |           | X           | X    |          | -   | -    |      |   |

| Force Internal Address Bus to restart v  | ector 3F  | FEh, 3FF    | Fh   | x        |     | х    | -    | - |

| Set Interrupt Mask Bit (I-Bit, CCR) to 1 | (Interrup | ot Disable) |      | x        |     | x    | -    | - |

| Set Interrupt Mask Bit (I-Bit, CCR) to 0 | (Interru  | ot Enable)  |      | -        |     | -    | х    | х |

| Reset STOP Latch                         | ×         | X           |      | -        |     | -    |      |   |

| Reset INT Latch                          | x         | X           |      | ļ-       |     | -    |      |   |

| Reset WAIT Latch                         | X         | X           |      | -        |     | -    |      |   |

| Disable Oscillator (for 4096 cycles)     |           |             | -    | x        |     | -    | ×    |   |

| Set Timer Clock to 0                     | -         |             | ×    | -        |     | X    |      |   |

| Watchdog counter reset                   |           | X           | X    |          | -   | х    |      |   |

| Watchdog WDOG-BIT reset                  |           | X           | >    | {        | _   | ×    |      |   |

| EEPROM control bits reset                |           | X           | ×    |          | -   | -    |      |   |

| PWM/BRM registers reset                  |           | X           | X    |          | -   | -    |      |   |

| EWPCC DAC register reset                 |           | x           | Х    |          | -   | -    |      |   |

| SYNC registers reset                     | X         |             | X    | -        |     | •    |      |   |

12/95

SCS-THOMSON

## **RESET AND INTERRUPTS (Continued)**

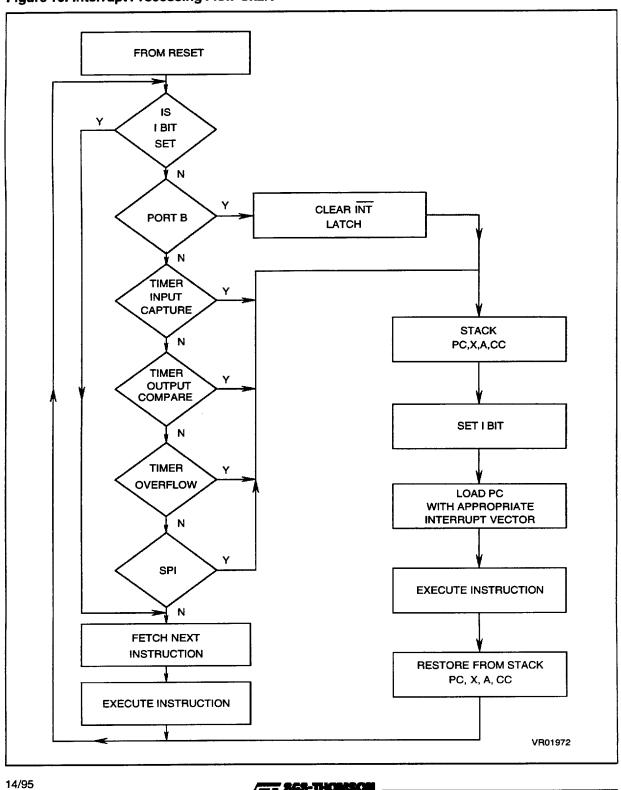

## 1.8.3 Interrupts

The ST7271 may be interrupted by one of three different methods: three maskable hardware interrupts (PORT B, SPI or TIMER) and a non-maskable software interrupt (TRAP). The Interrupt processing flowchart is shown in Figure 10.

The maskable interrupts must be enabled in order to be serviced. However, disabled interrupts can be latched and processed when they are enabled. When an interrupt has to be serviced, the PC, X, A and CC registers are saved onto the stack and the interrupt mask (I bit of the Condition Code Register) is set to prevent additional interrupts. The Y register is not automatically saved.

The PC is then loaded with the interrupt vector of the interrupt to service and the interrupt service routine runs (refer to Table 3 for vector addresses). The interrupt service routine should finish with the IRET instruction which causes the contents of the registers to be recovered from the stack and normal processing to resume. Note that the I bit is then cleared if and only if the corresponding bit stored in the stack is zero.

Though many interrupts can be simultaneously pending, a priority order is defined (see Table 3). The RESET pin has the highest priority.

If the I bit is set, TRAP is the only enabled interrupt. Interrupts allow the processor to leave the Wait low power mode.

**Software Interrupt**. The software interrupt is the executable instruction TRAP. The interrupt is recognized when the TRAP instruction is executed, regardless of the state of the I bit. When the interrupt is recognized, it is serviced according to the flowchart on Figure 10.

PORTB Interrupt. The PORTB Interrupt can be generated on the falling edge of any pin of PB0-PB7 if it is defined as an interrupt source. When an enabled interrupt occurs, normal processing is suspended at the end of the current instruction execution. It is then processed according to the flowchart on Figure 10.

If the interrupt is disabled (I high), the triggering edge of the wake-up interrupt sources logical-ORed is internally latched and the interrupt

Figure 9. Reset Timing Diagram

## **RESET AND INTERRUPTS (Continued)**

Figure 10. Interrupt Processing Flow-Chart

## **RESET AND INTERRUPTS (Continued)**

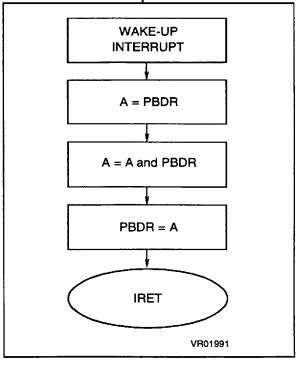

remains pending to be processed as soon as the interrupt is enabled. This internal latch is cleared in the first part of the service routine. Therefore, only one external interrupt can be latched and serviced as soon as possible. When the PORTB wake-up function is enabled, care should be taken after a Reset condition interrupt. The flowchart proposed in Figure 11 should be used in these cases.

**Timer Interrupt.** Five different timer interrupt flags are able to cause a timer interrupt when they are active if both the I bit of the CCR is reset and if the corresponding enable bit is set. If either of these conditions is false, the interrupt is latched and thus remains pending.

The interrupt flags are located in the Timer Status Register (0013h). The Enable bit are in the Timer Control Register (0012h).

When an enabled interrupt occurs, normal processing is suspended at the end of the current instruction execution. It is then serviced according to the flowchart on Figure 10. Software in the timer service routine must determine the priority and cause of the timer interrupt by examining the interrupt flags and the status bits located in the TSR.

The general sequence for clearing an interrupt is an access to the status register while the flag is set followed by a read or write of an associated register. Note that the clearing sequence resets the internal latch. A pending interrupt (i.e. waiting for being enabled) will therefore be lost if the clear sequence is executed.

## Serial Peripheral Interface (SPI) Interrupts

An interrupt in the serial peripheral interface (SPI) occurs when one of the interrupt flag bits in the serial peripheral status register (location 0043h) is set, provided the I bit in the condition code register

Figure 11. Proposed Wake-up Interrupt routine when wake-up feature is not used

cleared and the enable bit in the serial peripheral control register (location 0042h) is enabled.

When the interrrupt is recognized, the current state of the machine is pushed into the stack and I bit in the condition code register is set. These masks further interrupt until the present one is serviced. The SPI interrupt causes the program counter to vector to memory location 3FF2 and 3FF3 which contains the starting address of the interrupt service routine.

Table 3. Interrupt and Reset priorities

| Vector Address | Interrupt Source                | Masked by | Priority |         |

|----------------|---------------------------------|-----------|----------|---------|

| 3FFEh.3FFFh    | RESET and POWER-ON (POR)        |           | none     | Highest |

| 3FFCh,3FFDh    | SOFTWARE Interrupt (TRAP)       |           | none     | †       |

| 3FFAh,3FFBh    | PORT B Wake up                  |           | i-Bit    |         |

| 3FF8h,3FF9h    | TIMER INPUT Capture (1 and 2)   |           | I-Bit    |         |

| 3FF6h,3FF7h    | TIMER OUTPUT Compares (1 and 2) |           | I-Bit    |         |

| 3FF4h,3FF5h    | TIMER OVERFLOW                  |           | I-Bit    |         |

| 3FF2h,3FF3h    | SPI                             |           | I-Bit    |         |

| 3FF0h,3FF1h    | Reserved                        |           | -        | Lowest  |

#### 1.9 LOW POWER MODES

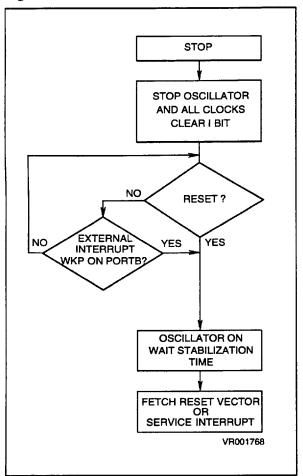

STOP Mode. The STOP mode is the MCU lowest power consumption mode. The STOP mode is entered by executing the STOP instruction. The internal oscillator is then turned off, causing all internal processing to be stopped, including the operation of the on-chip peripherals. The STOP mode cannot be used when the watchdog is enabled, if the STOP instruction is executed while the watchdog system is enabled, a watchdog reset is generated thus resetting the entire MCU.

When entering the STOP mode, the I bit in the Condition Code Register cleared. Thus, the external interrupts are allowed and the MCU is placed at its nominal speed (see CLOCK SYSTEM). All other registers and memory remain unaltered and all I/O lines remain unchanged.

The MCU can exit the STOP mode upon reception of either an external interrupt on PORTB or a power-on or external reset. The oscillator is then turned on and a stabilization time is provided before releasing CPU operation. The stabilization time is 4096 CPU clock cycles.

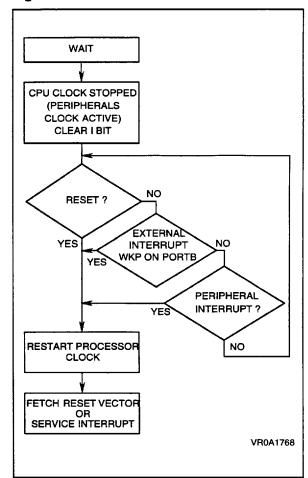

After the start up delay, the CPU continues operation by servicing the interrupt which wakes it up or by fetching the reset vector if a reset wakes it up. **WAIT Mode.** This mode is a low power consumption mode, but the power consumption is higher than in the STOP mode. The consumption can be further reduced by entering the slow mode.

The WFI instruction places the MCU in the WAIT mode.

In the WAIT mode, the internal clock remains active but all CPU processing is stopped; however, all other peripherals are still running. The watchdog can either be active or not according to the WATCHDOG DURING WAIT mask option.

During the WAIT mode, the I bit in the condition code register is cleared to enable all interrupts.

All other registers and memory remain unaltered and all parallel I/O lines remain unchanged.

An interrupt or a reset causes the MCU to exit the WAIT mode. An interrupt while the MCU is in the WAIT mode causes the corresponding interrupt vector to be fetched, the interrupt routine to be executed and normal processing to resume. A reset causes the program counter to fetch the reset vector and processing starts as for a normal reset.

Table 2 gives a list of the different sections affected by the low power modes. For detailed information on a particular devices, please refer to the corresponding parts.

## **LOW POWER MODES (Continued)**

Figure 12a. STOP Flow Chart

Figure 12b. WAIT Flow Chart

**NOTES**

# PAGE(S) INTENTIONALLY BLANK

## **2 FUNCTIONS DESCRIPTION**

#### 2.1 EEPROM

#### 2.1.1 Introduction

The on-chip EEPROM provides a non-volatile storage of user programmed data. It is read as a normal Read-only memory location, however user programs must not run from the EEPROM.

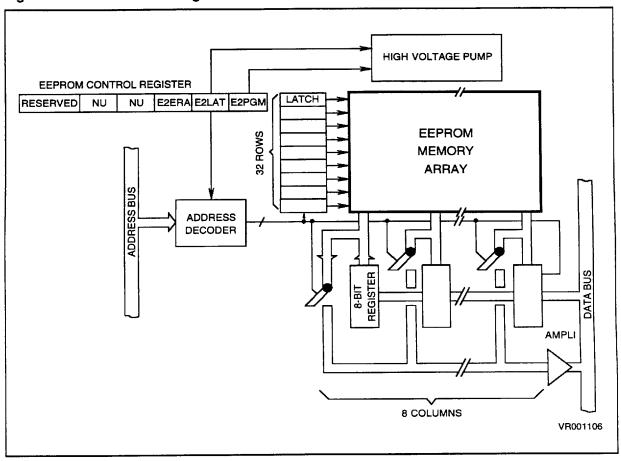

Programming and erasure are made in conjuction with the EEPROM control registers while 8 data latches allow simultaneous write or erase of 1 to 8 bytes in the EEPROM memory in the same programming cycle. The constraint is that all addressed memory bytes must be on the same row of the EEPROM memory array, that is up to eight bytes with the address bits A7, A6, A5, A4 and A3 constant, and with A2, A1 and A0 selecting the address(es) to be written within the row.

The EEPROM cell includes an internal charge pump to avoid the need of an external high voltage supply for the erase and programming functions.

## 2.1.2 Functional Description

As shown in Figure 13, the EEPROM is a 8 columns by 32 rows array. The row is selected by the A7, A6, A5, A4, A3 bits. Each column is associated to an 8-bit data register.

## Read Operation (E2LAT="0").

The EEPROM can be read as a normal ROM location when the E2LAT bit of the Control Register is low. When E2LAT is low, the E2PGM and E2ERA bits are forced low.

Figure 12. EEPROM Block Diagram

SGS-THOMSON

#### **EEPROM** (Continued)

## Write/Erase Operation. (E2LAT="1")

When E2LAT is set to "1", a write to an EEPROM location latches the data written in the 8-bit register corresponding to the decoded column and sets an internal flag for the decoded row.

As there are 8 columns in each row, up to 8 locations (having the same A7, A6, A5, A4, A3 address bits) can be simultaneously written or erased.

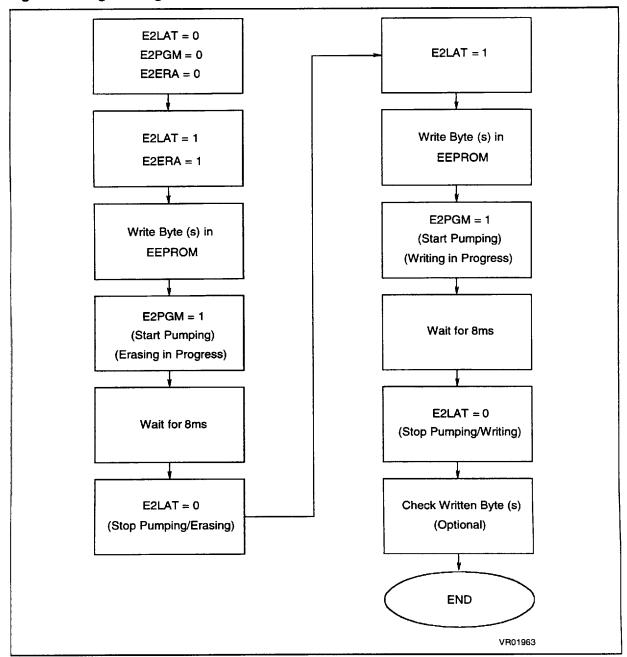

To erase bytes, the E2LAT and E2ERA bits are set to "1", and an instruction is made to write to the EEPROM addresses to be erased (the data value is not significant). The E2PGM bit must have been set after this operation to turn the charge pump on.

To write bytes, the E2LAT bit is set to "1", and the data is written to the appropriate EEPROM address(es). The E2PGM bit must have been set after this operation to turn the charge pump on.

WARNING a minimum delay of 20µs must be maintained after a programming operation (the falling edge of E2LAT) before the next read or write of the EEPROM. This time is required to discharge the high voltage in the array.

#### **Notes**

- Each block of 256 bytes of EEPROM is controlled by an independant EEPROM Control Register. Please refer to the Memory Map for both EEPROM memory block locations.

- It is mandatory to erase bytes before writing them.

- E2LAT must be kept high for the programming time tprog and then be cleared.

- When E2LAT is high, access to the EEPROM array is not possible.

- It is not allowed to perform successive write or erase cycles without clearing E2LAT between each write/erase (see Warning above).

## 2.1.3 Register Description

EEPROM CONTROL REGISTER 1 (0010h) EEPROM CONTROL REGISTER 2 (0011h)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     | 0 |   |       |       |       |

|-----|-----|-----|---|---|-------|-------|-------|

| Res | Res | Res | _ | _ | E2ERA | E2LAT | E2PGM |

This register contains the bits required to read, erase and program the EEPROM. They are defined as follow:

b7-5 = Reserved, must be held to "0"

#### b4.3 = Unused

b2 = **E2ERA:** EEPROM Erase. E2ERA must be set to "1" for an erase operation. It must be set after or at the same time as E2LAT. It cannot be changed once an EEPROM address is selected. It is held low when E2LAT is low. It is therefore automatically reset when E2LAT is reset.

b1 = **E2LAT**: EEPROM Latch Enable. When E2LAT is reset to "0", data can be read from the EEPROM. When it is set to "1" and E2PGM reset to "0", a write into the EEPROM array causes the data to be latched, according to the address into one of 8 data registers. An additional internal flag is latched to select the row. The selected columns and row determine the locations involved in the next erase or programming operation. E2LAT must be cleared after each programming or erase operation. E2ERA and E2PGM are forced low when E2LAT is low.

b0 = **E2PGM:** EEPROM Program Mode. This bit allows the internal charge pump to be switched on or off. When set to "1", the charge pump generator is on and the high voltage is applied to the EEPROM array. When low, the charge pump generator is off. E2PGM can only be reset by resetting E2LAT.

20/95

SGS-THOMSON

## **EEPROM** (Continued)

Figure 13. Programming Flow-chart of a basic routine

#### **2.2 VO PORTS**

#### 2.2.1 Introduction

The I/O ports allow the transfer of data through digital inputs and outputs, and, for specific pins, the input of analog signals or the Input/Output of dedicated signals for the on-chip peripherals (e.g. SPI, EWPCC and Timer). Please refer to the following table for a summary of these Alternate functions.

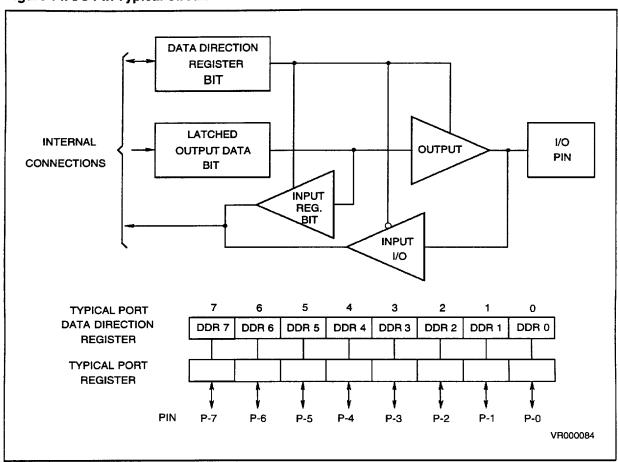

## 2.2.2 Functional Description

Each port pin of the I/O Ports can be individually configured under software control as either input or output. Ports A, B are 8-bit I/O ports, Port C is a 6-bit I/O port and Port D is a 5-bit port.

Each bit of a Data Direction Register (DDR) corresponds to an I/O pin of the associated port. This corresponding bit must be set to configure its associated pin as output and must be cleared to config-

ure its associated pin as input. The Data Direction Registers can be written or read.

The typical I/O circuit is shown on Figure 15. Any write to an I/O port updates the port output register even if it is configured as input. Any read of an I/O port returns either the data latched in the port output register (pins configured as output) or the value at the I/O pin (pins configured as input) (see Table 6).

At power-on or external reset, all DDR registers are cleared, which configures all Ports B, C and D pins as inputs with pull-ups and Port A as inputs without pull-ups but the port output registers are not initialized. Thus, the I/O port should be written before setting the DDR bit to avoid undefined output levels.

Figure 14. I/O Pin Typical Circuit

22/95

SGS-THOMSON

## **I/O PORTS** (Continued)

#### **PORT A**

Each Port A bit can be defined as an Input line (no pull-up) or as an Output Open drain line capable of handling typical current Isink of 10 mA for LED driving.

#### PORT B

Each bit of PORT B bit can be used as the Analog source to the Analog to Digital converter by selecting each individual bit independently in the Port B Configuration Register (address 0045h).

When the Analog function is selected for an I/O pin, the pull-up of the respective pin of Port B is disconnected and both the Data and Direction (DDR) registers of the respective pin are reset. Any further accesses to the respective DDR bit is blocked until the pin status is returned to normal I/O.

PORT B bit can also be configured on a bit basis as a wake-up interrupt input with an internal pull-up resistor. This mode is enabled by setting the corresponding Port B bit as a DIGITAL input (its bit in DDR set to '0' and its Analog function disabled) and the corresponding bit in the Port B Data Register must be set to '1'.

When this bit is subsequently forced low, an interrupt will be generated according to the status of the INT bit in the Miscellaneous Register.

Port B, bit 0 is only available for output if the East-West Pin-Cushion controller (EWPCC) is not used. If the EWPCC function is selected, Port B bit 0 MUST be set as input to enable the VFBACK timing input.

The pins not available for the 42 pin package (but present for the 56 pin package) are internally connected as standard digital inputs with pull-ups enabled.

All unused I/O lines should be tied to an appropriate logic level (either VDD or Vss).

#### PORT C

The available port pins of Port C may be used as general purpose I/O or as the I/O pins of the on-chip SPI and Timer Output Compare.

When used as digital Input, pull-up resistors may be switched on for ALL Port C inputs by setting the PUPC bit of the Programmable Input/Output Configuration Register (PCR).

When used as output the Open Drain mode is automatically set if the SPI is disabled.

Port C, bit 0 is switched from the normal I/O functionality to the output of the Timer Output Compare signal by resetting to '0' the OCOP bit of the PCR.

When the SPI is enabled, Port C bits 2-5 output bits are forced to the push-pull output configuration for high speed data transmission, while pins set to input have the pull-up resistor disconnected, regardless of the state of PUPC.

The default condition of open drain output (SPI not enabled) allows software emulation of communication using the PC-bus protocol.

#### PORT D

The I/O pins of Port D normally are used for the input and output of video synchronization signals to the Sync Processor, but are set to I/O Input with pull-up upon reset. The I/O mode can be set individually for each port bit to Input with pull-up and output push-pull through the Port D DDR.

The configuration to support the Sync Processor required that the SYNOP bit of the PCR be reset to '0'; this enables Port D bits 0, 1 and 2 to the sync inputs and outputs.

Note that as these inputs are switched from normal I/O functionality, the video synchronization signals may also be monitored directly through the Port D Data Register for such tasks as checking for the presence of video signals or checking the polarity of Horizontal and Vertical synchronization signals (when the Sync Inputs are switched directly to the outputs using the multiplexors of the Sync Processor).

Table 6. I/O Pin Functions

| R/W+ | DDR | VO Pin Functions                                                          |

|------|-----|---------------------------------------------------------------------------|

| 0    | 0   | The I/O pin is in input mode. Data is written into the output data latch. |

| О    | 1   | Data is written into the output data latch and output the I/O pin.        |

| 1    | 0   | The state of the I/O pin to read.                                         |

| 1    | 1   | The I/O pin is in an output mode. The output data latch is read.          |

<sup>\*</sup> R/W is an internal signal.

SGS-THOMSON

## **VO PORTS** (Continued)

## 2.2.3 Register Description

DATA REGISTERS

Port A: 0000h Port B: 0001h Port C: 0002h Port D: 0003h Read/Write

Reset Value: Undefined

| 7   |  | 0   |  |  |

|-----|--|-----|--|--|

| мѕв |  | LSB |  |  |

## **DATA DIRECTION REGISTERS**

Port A: 0004h Port B: 0005h Port C: 0006h Port D: 0007h Read/Write

Reset Value: 0000 0000 (00h) (as inputs)

| 7   |  | 0   | <br> |  |

|-----|--|-----|------|--|

| MSB |  | LSB |      |  |

## PORT B CONFIGURATION REGISTER (0045h)

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     | 0   |     |     |     |     |

|-----|-----|-----|-----|-----|-----|-----|-----|

| AD7 | AD6 | AD5 | AD4 | AD3 | AD2 | AD1 | AD0 |

b7-0 = **AD7-AD0:** Port B Digital/Analog Input Configuration Bits. When AD#i is set (i = 7-0), the pullup on the respective pin #i of Port B is disconnected and the pin is configured as analog input; otherwise the pull-up is connected and pin configured as digital input (RESET condition) with no power consumption in the A/D channel.

**Note.** On the 42-pin package option, PB7-PB4 are not externally connected and are internally configured as standard digital inputs with pull-up.

# PROGRAMMABLE INPUT/OUTPUT CONFIGURATION REGISTER (0046h)

Programmable Input/Output Configuration

Read/Write

Reset Value: 1111 1000 (F8h)

| 7   |       |      | 0     |      |      |      |      |

|-----|-------|------|-------|------|------|------|------|

| Res | CLMOP | ОСОР | SYNOP | PUPC | POC2 | POC1 | POC0 |

b7 = Res: Reserved.

b6 = **CLMOP:** Clamping Signal Output Select. This bit selects either the PD3 I/O Pin Option or the output of the Clamping signal.

CLMOP = 0 : Clamping Signal

CLMOP = 1 : PD3 as Pull-up Input or Push-pull Output

b5 = **OCOP**: Timer Output Compare Select. This bit selects either the PC0 I/O Pin Option or the output of the Timer Output Compare.

OCOP = 0: Timer Output Compare

OCOP = 1: PC0 Input (with/no pull-up) or Output (push-pull)

b4 = **SYNOP**: SYNC Processor Function Select. This bit selects either the Sync Processor or PD0, PD1, PD2 I/O Pin Options.

SYNOP = 0: PD0 = CSYNCI, PD1 = HSYNCO and PD2 = VSYNCO

SYNOP = 1: PD0/PD1/PD2 Inputs (Pull-up) OR Outputs (Push-Pull).

**Note.** HSYNCO and VSYNCO can be directly read as Port bits by configuring PD1 and PD2 as inputs.

b3 = **PUPC:** PORT C Input Configuration Bit. This bit selects the input configuration for present bits of I/O Port C.

PUPC = 1 : Pull-up

PUPC = 0: No Pull-up.

Whenever the SPI is active, the pull-up is disconnected from SPI input pins regardless of the state of PUPC and SPI outputs are set to push-pull.

b2-b0 = POC2-POC0: PWM/BRM Output Configuration Bits. These bits select the PWM/BRM output configuration.

| PWM          |      | Value     |            |  |  |

|--------------|------|-----------|------------|--|--|

| Group Chani  | nels | 0         | 1          |  |  |

| A2 DA1, D3-6 | P0C0 | push-pull | open drain |  |  |

| B1 DA7-11    | P0C1 | push-pull | open drain |  |  |

| B2 DA12-DA17 | P0C2 | push-pull | open drain |  |  |

In the case of uncomplete ports (Port C and Port D), non-implemented bits are read '0' whenever accessed.

24/95

SGS-THOMSON

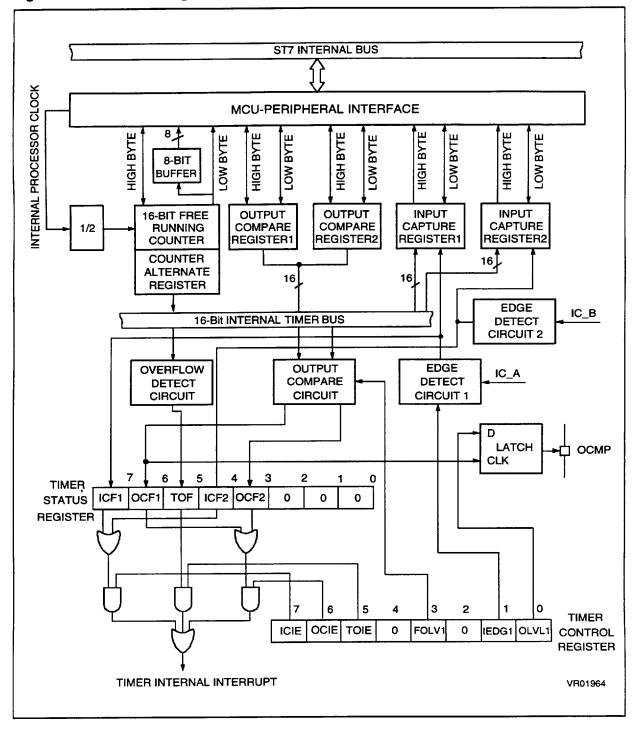

#### 2.3 16 BIT TIMER

#### 2.3.1 Introduction

The 16-bit programmable timer consists of a 16-bit free running counter driven by a prescaler and control logic for two input captures and two output compare registers. It can be used for many purposes including pulse length measurement of input signals and generation of one output waveform.

The two input capture functions are dedicated to the timing functions of the Sync Processor and are internally connected to this source. They are thus not available for timing of other external signals.

When used with an 8MHz external oscillator frequency, the timer has a resolution of 0.5µs.

## 2.3.2 Functional Description

As the timer has a 16-bit architecture, each of its specific function blocks is represented by two registers. These registers contain the high order byte and low order byte of that function. However any access to the high order byte inhibits that specific timer capability until the low order byte is also accessed.

Note that correct software procedures should set the I bit of the Condition Code Register before accessing the high order byte to prevent an interrupt from occurring between the accesses to the high and low order bytes of any register.

**Counter.** The key element of the programmable timer is a 16-bit free running counter or counter register. It is preceded by a prescaler which divides the internal clock by two giving an operational frequency of 2MHz.

Software can read the counter at any time without affecting its value. It can be read from two locations, the Counter Register (0018h, 0019h) and Alternate Counter Register (001Ah, 001Bh). The only difference between these two read-only registers is the way the overflow flag TOF is handled during a read sequence.

A read sequence containing only a read of the least significant byte of the free running counter (from either the Counter Register or the Alternate Counter Register) will receive the LSB of the count value at the time of the read. A read of the most significant byte (from either the Counter Register or the Alternate Counter Register) simultaneously returns the MSB of the count value and causes the LSB to be transferred into a buffer.

The buffered value remains unchanged until the 16-bit read sequence is completed, even if the user reads the MSB several times. The read sequence is completed by reading the free running counter LSB, which actually returns the buffered value.

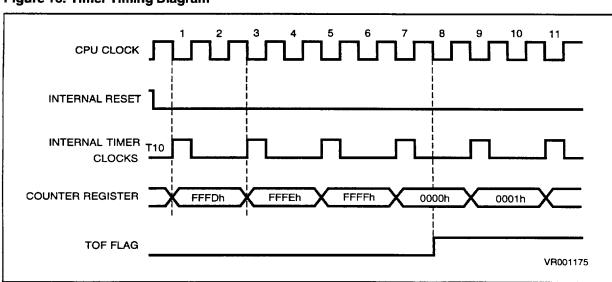

As shown in Figure 17 the free running counter is configured to FFFCh during reset, after RESET goes high. During a power-on reset (POR), the counter is also configured to FFFCh and begins running after the oscillator startup delay.

When the counter rolls over from FFFFh to 0000h, the Timer Overflow flag (TOF) of the Timer Status Register (TSR) is set. A timer interrupt is then generated if the TOIE enable bit of the Timer Control Register (TCR) is set, provided the I bit of the CCR is cleared. If one of these conditions is false, the interrupt remains pending to be issued as soon as they are both true. The interrupt request is cleared by reading TSR while TOF is set followed by an access (read or write) to the LSB of the Counter Register.

The TOF flag is not affected by accesses to the Alternate Counter Register. This feature allows simultaneous use of the overflow function and reads of the free running counter at random times (for example, to measure on elapsed time) without risking the cleaning of the TOF flag erroneously. Accesses to the timer without the intention of servicing the TOF flag should therefore be performed to the Alternate Counter Register while only the TOF service routine accesses the Counter Register.

The free running counter can be reset under software control. This is performed by writing to the LSB of either the Counter Register or the Alternate Counter Register. The counter and the prescaler are then configured to their reset conditions. This reset also completes any 16-bit access sequence. All flags and enable bits are unchanged.

The value in the counter registers repeats every 131072 internal processor clock cycles (32 ms for f<sub>INT</sub> = 4 MHz). As shown in Figure 17, the counter increment is triggered by a falling edge of the CPU clock.

The timer is not affected by the WAIT mode. In the HALT mode, the counter stops counting until the mode is exited. Counting then resumes from previous count (MCU woken by an interrupt) or from reset count (MCU woken by a reset).

Input Capture.

Figure 15. Timer Block Diagram

26/95

SGS-THOMSON

NICEOUTICE PONCES

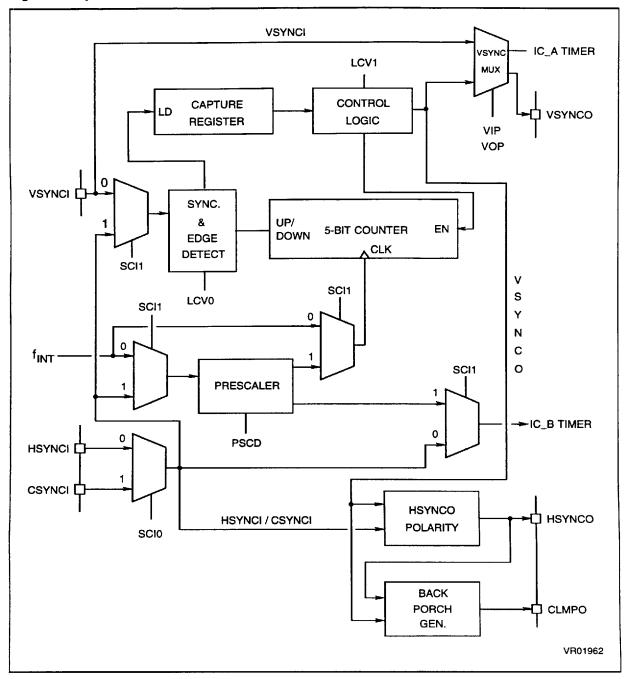

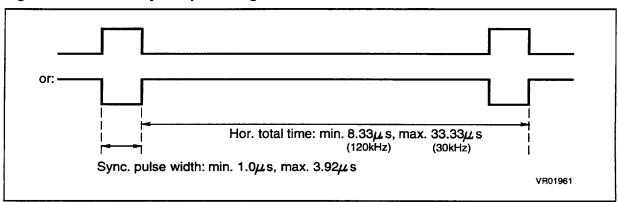

The ST7271 features two input capture registers and two input capture interrupt enable bits. The input capture inputs IC\_A and IC\_B are connected through the VSYNCI and HSYNCI (OR CSYNCI) input pins respectively. When the SYNC processor is not being used these pins may be used for the external input captures of the timer. The input on HSYNCI may optionally be passed through a /256 prescaler before being passed to the IC\_B input capture.

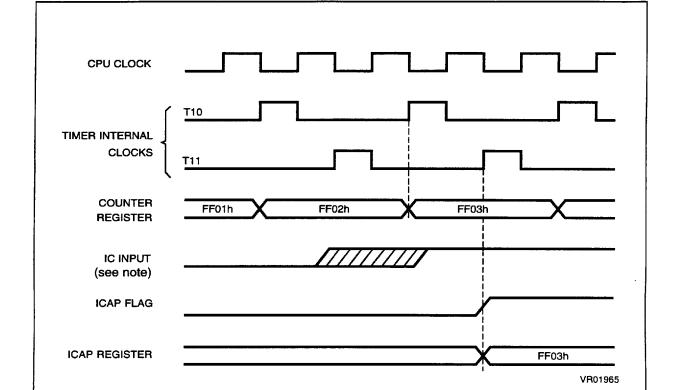

Input Capture Register 1 (ICR1) is a 16-bit register made up of two 8-bit registers: the most significant byte register (ICHR1), located at 0014h, and the least significant byte register (ICLR1) located at 0015h.

ICR1 is a read-only register used to latch the value of the free running counter after a defined transition is sensed by the input capture edge detector at IC\_A. This transition is software programmable through the IEDG1 bit of the Timer Control Register (TCR). When IEDG1 is set, a rising edge triggers the capture; when IEDG1 is low, the capture is triggered by a falling edge. Care must be taken with the external circuitry to avoid unwanted interrupts when changing the interrupt edge.

When an input capture occurs, the flag ICF1 in Timer Status Register (TSR) is set. An interrupt is requested if the interrupt enable bit ICIE of TCR is set, provided the I bit of the CCR is cleared. Otherwise, the interrupt remains pending until both conditions become true. It is cleared by reading the Timer Status Register TSR followed by an access (read or write) to the LSB of ICR1.

The result stored in ICR1 is one more than the value of the free running counter on the rising edge of the internal processor clock preceding the active transition at pin IC\_A (see Figure 17). This delay is required for internal synchronization. Therefore, the timing resolution of the input capture system is one count of the free running counter, i.e. 2 internal clock cycles.

The free running counter is transferred to ICR1 on each proper signal transition regardless of whether the Input Capture Flag ICF1 is set or cleared. The ICR1 always contains the free running counter value which corresponds to the most recent input capture.

After a read of the MSB of ICR1 (ICHR1), counter transfer of input capture is inhibited until the LSB of ICR1 (ICLR1) is also read. This characteristic forces the minimum pulse period attainable to be determined by the time to service the interrupt and to execute the interrupt routine.

A read of ICLR1 does not inhibit the counter transfer. Again, minimum pulse periods are the ones which allow software to read the least significant byte and perform needed operations. There is no conflict between the read of ICR1 and the running counter transfer since they occur on opposite edges of the internal processor clock (see Figure 17).

The ICR1 is undetermined at power-on and is not affected by an external reset. Hardware circuitry has to provide protection from generating a wrong input capture when changing the edge sensitivity option of IC\_A input through the IEDG1 bit.

Figure 16. Timer Timing Diagram

During the HALT mode, if at least one valid input capture edge occurs at the IC\_A input, the input capture detect circuitry is armed. This action does not set any timer flags nor "wake-up" the MCU. If the MCU is awaken by an interrupt, there is an active input capture flag and data from the first valid edge that occurred during the HALT mode. If the HALT mode is exited by a reset, the input capture detect circuitry is reset and thus, any active edge that happenedduring the HALT mode is lost.

**Input Capture Register 2** (ICR2) is a 16-bit register made up of two 8-bit registers: the most significant byte register (ICHR2), located at 001Ch, and the least significant byte register (ICLR2) located at 001Dh.

The previous description shown for Input Capture Register 1 is also applicable for the Input Capture Register 2, with the exception that Input Capture Register 2 is triggered only on a negative edge on input IC\_B and with the substitution of the appro-

priate index in the bit and register names.

## **Output Compare.**

There are two output compare registers: Output Compare Register 1 and 2 (OCR1 and OCR2). They can be used for several purposes such as controlling an output waveform or indicating when a period of time has elapsed. OCMP1 pin is associated with output compare 1; no pin is associated with Output Compare 2 which can be used for the generation of timer interrupts.

The Output Compare Registers are unique because all bits are readable and writable and are not affected by the timer hardware and reset. If a compare function is not used, the two bytes of the corresponding Output Compare Registers can be used as storage locations. Note that the same output compare interrupt enable bit is used for both output compares.

Figure 17. Input Capture Timing Diagram

Note. The diagram represents the case of a rising edge sensitivity (IEDG1=1). The capture is performed at the next rising edge of T11, if the action edge of ICAP happened before the previous T10 falling edge.

28/95

SGS-THOMSON

Output Compare Register 1. The Output Compare Register 1 (OCR1) is a 16-bit register, which is made up of two 8-bit registers: The most significant byte register (OCHR1) at address 0016h and the least significant byte register (OCLR1) at address 0017h.

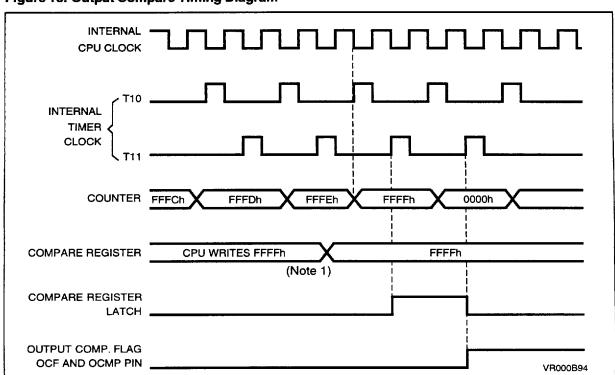

The content of OCR1 is compared with the content of the free running counter once during every timer clock cycles, i.e. every 2 internal processor clock periods. If a match is found, the Output Compare Flag OCF1 of the TSR is set and the Output Level bit (OLVL1) of the TCR is clocked to the OCMP1 pin (see output compare timing diagram on Figure 19).

OLVL1 is copied to the corresponding output level latch and hence, to the OCMP1 pin regardless of whether the Output Compare Flag (OCF1) is set or not. The value in the OCR1 and the OLVL1 bit should be changed after each successful comparison in order to control an output waveform or establish a new elapsed timeout.

An interrupt follows a successful output compare if the corresponding interrupt enable bit OCIE of the TCR is set, provided the I-bit of the CCR is cleared. Otherwise, the interrupt remains pending until both conditions are true. It is cleared by a read of TSR followed by an access to the LSB of the OCR1.

After a processor write cycle to the OCHR1 register, the output compare function is inhibited until the OCLR1 is also written. Thus, the user must write both bytes if the MSB is written first. A write made to only the LSB will not inhibit the compare function. The minimum time between two successive edges on the OCMP1 pin is a function of the software program.

The OCMP1 output latch is forced low during reset and stays low until valid compares change it to a high level. Because the OCF1 flag and the OCR1 are undeterminate at power-on and are not affected by an external reset, care must be exercised when initiating the output compare function with software. The following procedure is recommended to prevent the OCF1 flag from being set between the time it is read and the write to OCR1:

Write to OCHR1 (further compares are inhibited).

Read the TSR (first step of the clearance of OCF1 [it may be already set]).

Write to OCLR1 (enables the output compare function and clears OCF1).

Figure 18. Output Compare Timing Diagram

Note 1. The CPU write to the compare registers may take place at any time but a compare only occurs at timer state T11. Thus a 2-cycles difference may exist between the write to the compare register and the actual compare.

SGS-THOMSON NICROSLICTRONICS

Output Compare Register 2. The Output Compare Register 2 (OCR2) is a 16-bit register, which is made up of two 8-bit registers: the most significant byte register (OCHR2) at address 0001Eh and the least significant byte register (OCLR2) at address 0001Fh.

This register works as the Output Compare Register 1. For a complete description, please refer to the above and substitute the appropriate index in the bit and register names.

**Software Force Compare.** The force compare capability main purpose is to facilitate fixed frequency generation.

When the Force Output Level 1 bit (FOLV1) of TCR is written to 1, OLVL1 is copied to pin OCMP1. To provide this capability, internal logic allows a single instruction to change OLVL1 and causes a forced compare with the new value of OLVL1. OCF1 is not affected and thus, no interrupt request is generated.

## 2.3.3 Register Description

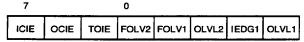

TIMER CONTROL REGISTER (0012h)

Read/Write

Reset Value: 0000 00x0 (00h or 02h)

b7 = ICIE Input Capture Interrupt Enable

If ICIE is set, a timer interrupt is enabled whenever

the ICF1 status flags of TSR are set. If the ICIE bit

is cleared, the interrupt is inhibited.

b6 = **OCIE**: Output Compare Interrupt Enable If OCIE is set, a timer interrupt is enabled whenever the OCF1 or OCF2 status flags of TSR are set. If the OCIE bit is cleared, the interrupt is inhibited.

b5 = **TOIE**: Timer Overflow Interrupt Enable If TOIE is set, a timer interrupt is enable whenever the TOF status flag of TSR is set. If the TOIE bit is cleared, the interrupt is inhibited.

b4 = **FOLV2**: Force Output Compare 2 This bit has no affect. FOLV2 is cleared by a system reset.

b3 = **FOLV1**: Force Output Compare 1 When written to 1, FOLV1 forces OLVL1 to be copied to the OCMP pin.

b2 = OVL2: Output Level 2. This bit has no affect.

b1 = IEDG1: Input Edge 1

The value of the IEDG1 determines which level transition on IC\_A input will trigger a free running counter transfer to the ICR1. When IEDG1 is high, a rising edge triggers the capture since when low, a falling edge does.

## b0 = OLVL1 Output Level 1

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs at OCR1.

## TIMER STATUS REGISTER (0013h)

Read Only

Reset Value: Undefined

| 7    |      |     | 0    |      |   |   |   |

|------|------|-----|------|------|---|---|---|

| ICF1 | OCF1 | TOF | ICF2 | OCF2 | 0 | 0 | 0 |

## b7 = ICF1 input Capture Flag 1

ICF1 is set when a proper edge has been sensed by the input capture edge detector at IC\_A. The edge is selected by the IEDG1-bit in TCR. ICF1 is cleared by a processor access to the TSR while ICF1 is set followed by an access (read or write) to the low byte of ICR1 (ICLR1).

## b6 = OCF1 Output Compare Flag 1

OCF1 is set when the content of the free running counter matches the content of OCR1. It is cleared by a processor access of TSR while OCF1 is set followed by an access (read or write) to the low byte of OCR1.

## b5 = **TOF** Timer Overflow

TOF is set by a transition of the free running counter from FFFFh to 0000h. It is cleared by a processor access to TSR while TOF is setfollowed by an access (read or write) to the low byte of the counter low register. TOF is not affected by an access to the Alternate Counter Register.

## b4 = ICF2 Input Capture Flag 2

ICF2 is set when a negative edge has been sensed by the input capture edge detector at IC\_B. ICF2 is cleared by a processor access to the TSR while ICF2 is set followed by an access (read or write) to the low byte of ICR2 (ICLR2).

## b3 = OCF2 Output Compare Flag 2

OCF2 is set when the content of the free running counter matches the content of OCR2. It is cleared by a processor access of TSR while OCF2 is set followed by an access (read or write) to the low byte of OCR2.

b2-0 = Unused, read as '0'.

30/95

SCS-THORSON

INPUT CAPTURE REGISTER 1, High Byte (0014h)

Read Only

Reset Value: Undefined

(

| IC1.15 IC1.14 IC1.13 IC1.12 IC1.11 IC1.10 IC1.9 IC1. |        |        |        |        |        |        |       |       |

|------------------------------------------------------|--------|--------|--------|--------|--------|--------|-------|-------|

|                                                      | IC1.15 | IC1.14 | IC1.13 | IC1.12 | IC1.11 | IC1.10 | IC1.9 | IC1.8 |

## INPUT CAPTURE REGISTER 1, Low byte (0015h)

Read Only

Reset Value: Undefined

7

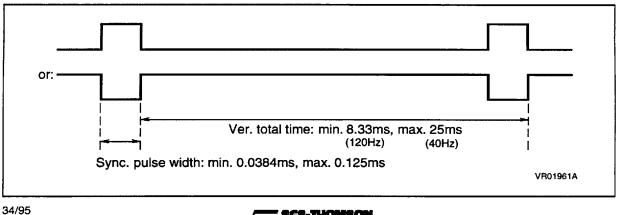

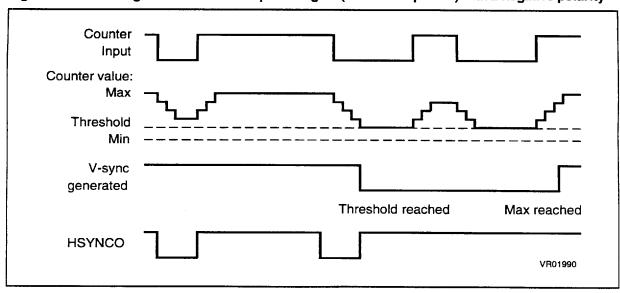

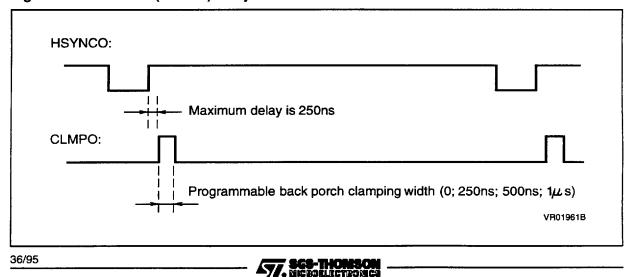

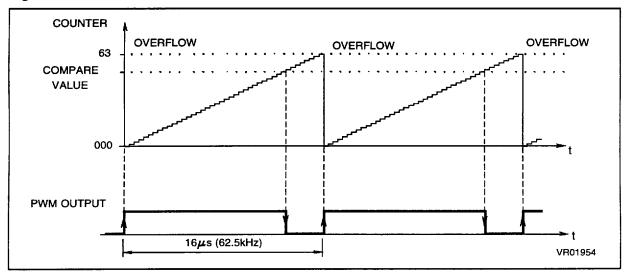

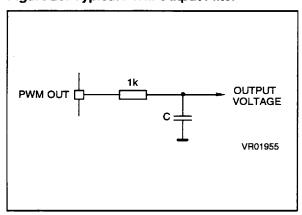

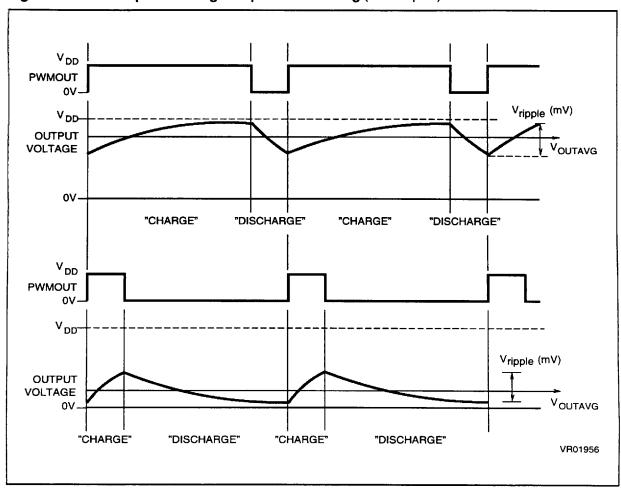

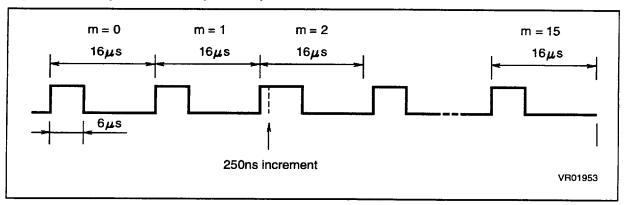

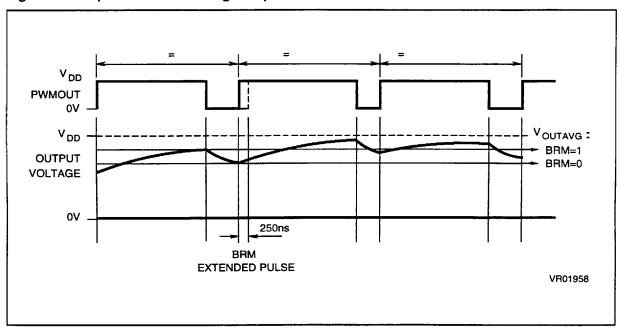

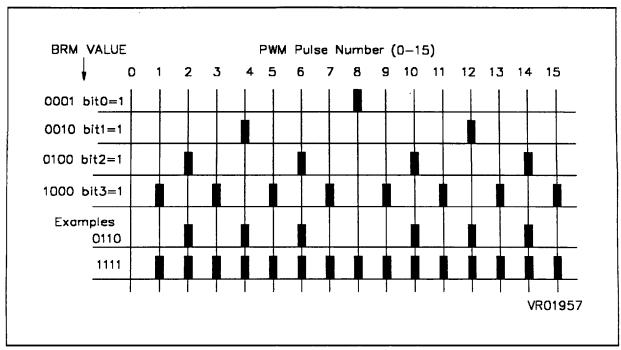

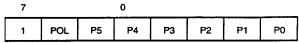

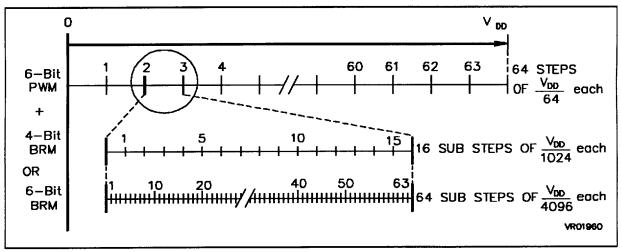

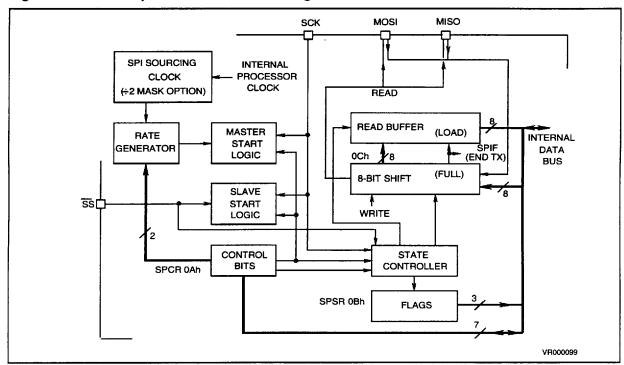

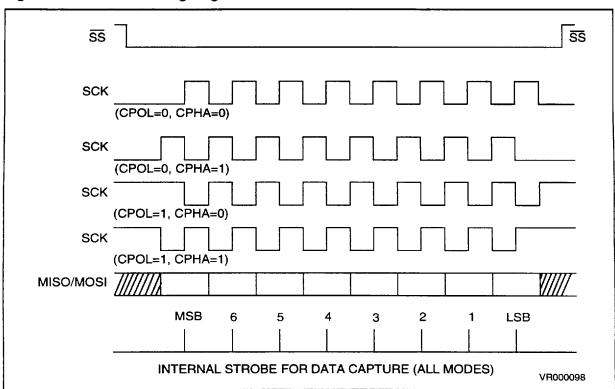

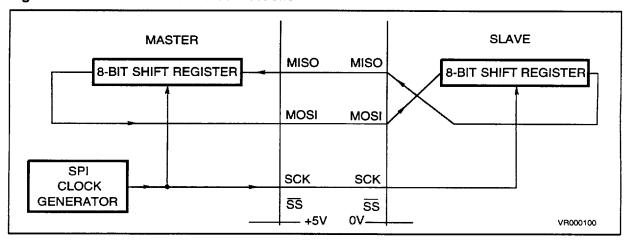

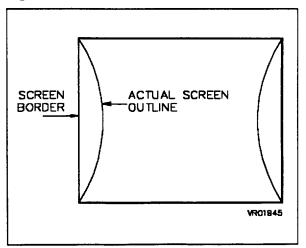

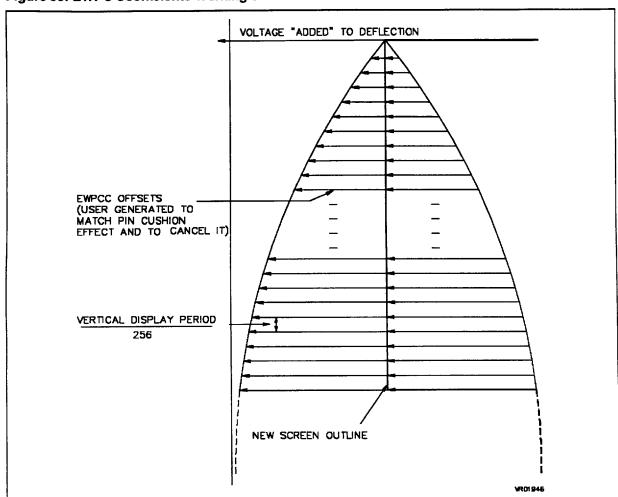

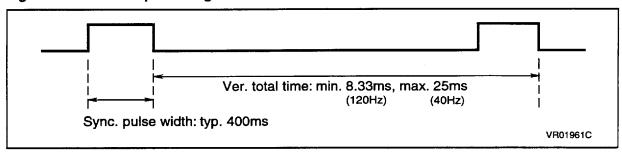

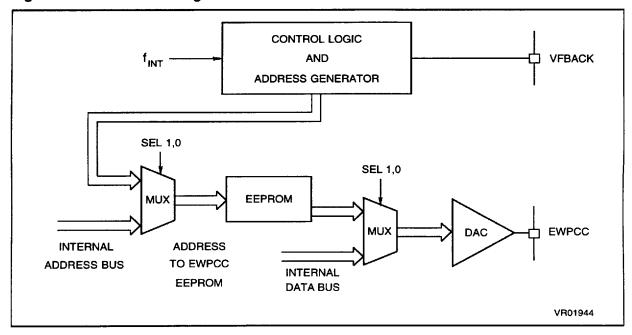

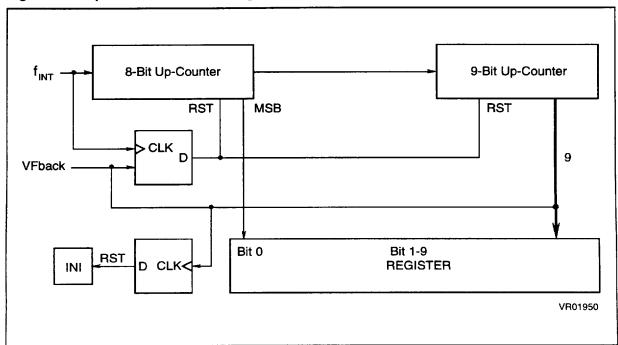

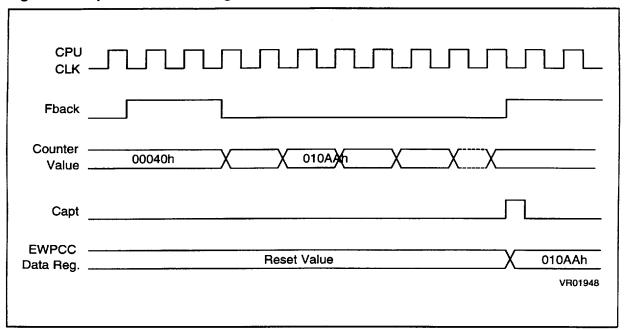

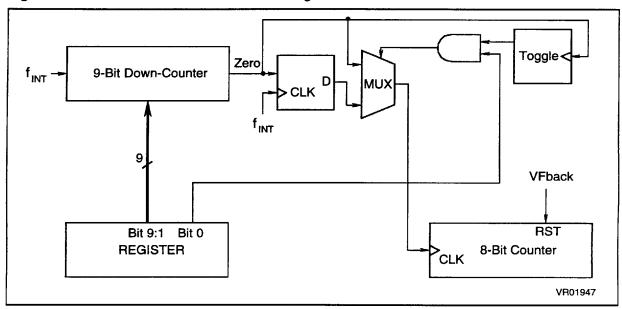

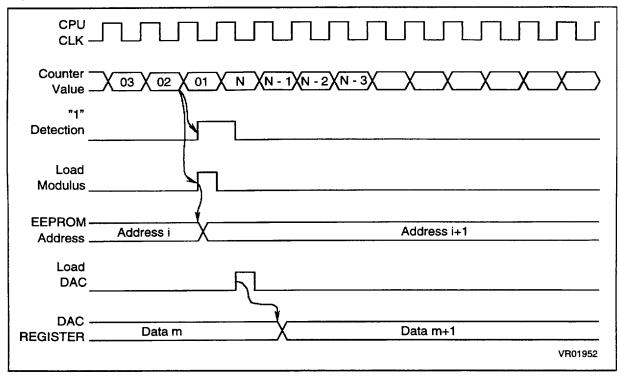

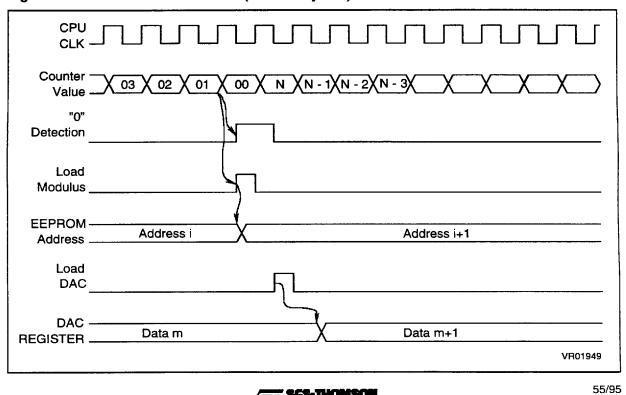

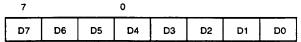

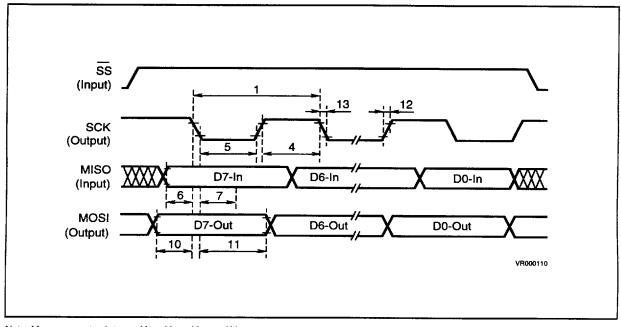

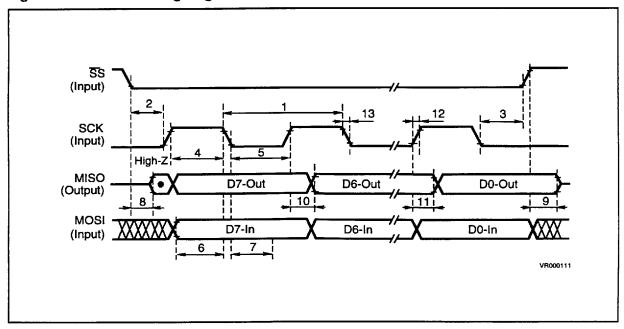

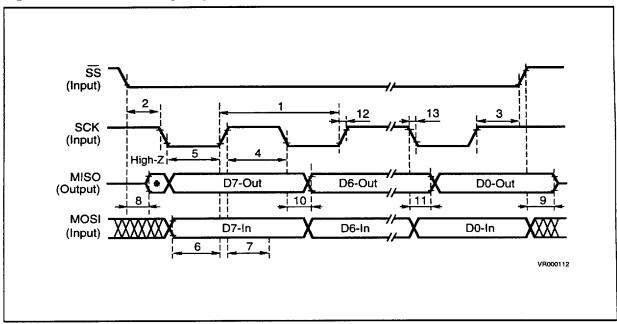

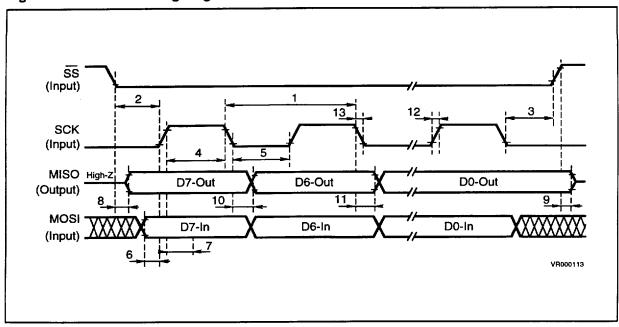

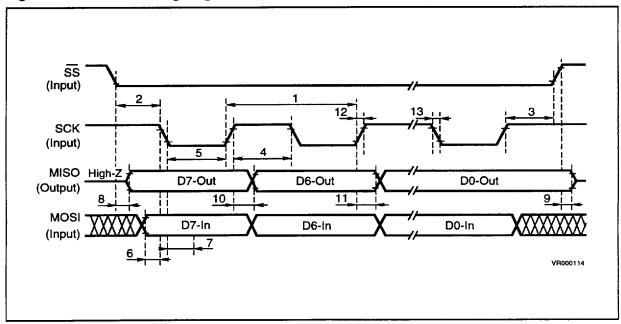

| IC1.7 IC1.6 IC1.5 IC1.4 IC1.3 IC1.2 IC1.1 IC1.6 |       |       |       |       |       |       |       |       |