# 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH

SCES352C - JUNE 2001 - REVISED SEPTEMBER 2001

- Member of the Texas Instruments

Widebus™ Family

- TI-OPC™ Circuitry Limits Ringing on Unevenly Loaded Backplanes

- OEC<sup>™</sup> Circuitry Improves Signal Integrity and Reduces Electromagnetic Interference

- Bidirectional Interface Between GTLP Signal Levels and LVTTL Logic Levels

- Split LVTTL Port Provides a Feedback Path for Control and Diagnostics Monitoring

- LVTTL Interfaces Are 5-V Tolerant

- High-Drive GTLP Open-Drain Outputs (100 mA)

- LVTTL Outputs (–24 mA/24 mA)

- Variable Edge-Rate Control (ERC) Input Selects GTLP Rise and Fall Times for Optimal Data-Transfer Rate and Signal Integrity in Distributed Loads

- I<sub>off</sub>, Power-Up 3-State, and BIAS V<sub>CC</sub> Support Live Insertion

- Distributed V<sub>CC</sub> and GND Pins Minimize

High-Speed Switching Noise

- Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

- ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 1000-V Charged-Device Model (C101)

# DGG OR DGV PACKAGE (TOP VIEW)

|                 | (101           | VIL. VV | '                    |

|-----------------|----------------|---------|----------------------|

| IMODE1          | $\int_{1}^{1}$ | J 48    | IMODE0               |

| AI1             | 12             |         | BIAS V <sub>CC</sub> |

| AO1             | 3              |         | B1                   |

| GND             | 7              |         | GND                  |

| Al2             | 9              |         | OEAB                 |

|                 | 7              |         | ] B2                 |

| AO2             | _              |         | <b>=</b>             |

| V <sub>CC</sub> |                |         | ERC                  |

|                 | 8              |         | OEAB                 |

| AO3             | <b>U</b> 9     |         | ] B3                 |

| GND             | 10             | 39      | ] GND                |

| Al4             | [] 11          | 38      | CLKAB/LEAB           |

| AO4             | 12             | 37      | ] B4                 |

| AO5             | 13             | 36      | B5                   |

| AI5             | 14             | 35      | CLKBA/LEBA           |

| GND             | 15             | 34      | ] GND                |

| AO6             | [ 16           | 33      | ] B6                 |

| Al6             | [ 17           | 32      | ] OEBA               |

| $V_{CC}$        | [] 18          | 31      | ] v <sub>cc</sub>    |

| AO7             | [] 19          | 30      | ] B7                 |

| AI7             | 20             | 29      | LOOPBACK             |

| GND             | 21             | 28      | GND                  |

| AO8             | _              |         | В8                   |

| Al8             | 23             | 26      | V <sub>REF</sub>     |

| OMODE0          | 24             | 25      | OMODE1               |

|                 |                |         |                      |

### description

The SN74GTLP2033 is a high-drive, 8-bit, three-wire registered transceiver that provides inverted LVTTL-to-GTLP and GTLP-to-LVTTL signal-level translation. The device allows for transparent, latched, and flip-flop modes of data transfer with separate LVTTL input and LVTTL output pins, which provides a feedback path for control and diagnostics monitoring, the same functionality as the SN74FB2033. The device provides a high-speed interface between cards operating at LVTTL logic levels and a backplane operating at GTLP signal levels. High-speed (about three times faster than standard LVTTL or TTL) backplane operation is a direct result of GTLP's reduced output swing (<1 V), reduced input threshold levels, improved differential input, OEC<sup>TM</sup> circuitry, and TI-OPC<sup>TM</sup> circuitry. Improved GTLP OEC and TI-OPC circuits minimize bus-settling time and have been designed and tested using several backplane models. The high drive allows incident-wave switching in heavily loaded backplanes with equivalent load impedance down to 11 Ω.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH

SCES352C - JUNE 2001 - REVISED SEPTEMBER 2001

### description (continued)

GTLP is the Texas Instruments derivative of the Gunning Transceiver Logic (GTL) JEDEC standard JESD 8-3. The ac specification of the SN74GTLP2033 is given only at the preferred higher noise-margin GTLP, but the user has the flexibility of using this device at either GTL ( $V_{TT} = 1.2 \text{ V}$  and  $V_{REF} = 0.8 \text{ V}$ ) or GTLP ( $V_{TT} = 1.5 \text{ V}$  and  $V_{REF} = 1 \text{ V}$ ) signal levels. For information on using GTLP devices in FB+/BTL applications, refer to TI application reports, *Texas Instruments GTLP Frequently Asked Questions*, literature number SCEA019, and *GTLP in BTL Applications*, literature number SCEA017.

Normally, the B port operates at GTLP signal levels. The A-port and control inputs operate at LVTTL logic levels, but are 5-V tolerant and can be directly driven by TTL or 5-V CMOS devices. V<sub>REF</sub> is the B-port differential input reference voltage.

This device is fully specified for live-insertion applications using  $l_{off}$ , power-up 3-state, and BIAS  $V_{CC}$ . The  $l_{off}$  circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down. The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down, which prevents driver conflict. The BIAS  $V_{CC}$  circuitry precharges and preconditions the B-port input/output connections, preventing disturbance of active data on the backplane during card insertion or removal, and permits true live-insertion capability.

This GTLP device features TI-OPC circuitry, which actively limits overshoot caused by improperly terminated backplanes, unevenly distributed cards, or empty slots during low-to-high signal transitions. This improves signal integrity, which allows adequate noise margin to be maintained at higher frequencies.

High-drive GTLP backplane interface devices feature adjustable edge-rate control (ERC). Changing the ERC input voltage between low and high adjusts the B-port output rise and fall times. This allows the designer to optimize system data-transfer rate and signal integrity to the backplane load.

When  $V_{CC}$  is between 0 and 1.5 V, the device is in the high-impedance state during power up or power down. However, to ensure the high-impedance state above 1.5 V, OEAB should be tied to  $V_{CC}$  through a pullup resistor and OEAB and OEBA should be tied to GND through a pulldown resistor; the minimum value of the resistor is determined by the current-sinking/current-sourcing capability of the driver.

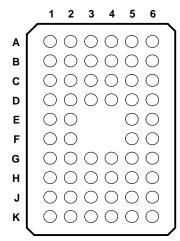

#### GQL PACKAGE (TOP VIEW)

### terminal assignments

|   | 1      | 2   | 3   | 4   | 5                    | 6      |

|---|--------|-----|-----|-----|----------------------|--------|

| Α | IMODE1 | NC  | NC  | NC  | NC                   | IMODE0 |

| В | AO1    | Al1 | GND | GND | BIAS V <sub>CC</sub> | B1     |

| С | AO2    | Al2 | Vcc | ERC | OEAB                 | B2     |

| D | AO3    | Al3 | GND | GND | OEAB                 | В3     |

| Ε | AO4    | Al4 |     |     | CLKAB/LEAB           | B4     |

| F | AO5    | AI5 |     |     | CLKBA/LEBA           | B5     |

| G | AO6    | Al6 | GND | GND | OEBA                 | B6     |

| Н | AO7    | AI7 | Vcc | Vcc | LOOPBACK             | B7     |

| J | AO8    | Al8 | GND | GND | VREF                 | B8     |

| K | OMODE0 | NC  | NC  | NC  | NC                   | OMODE1 |

|   |        |     | ·   |     |                      |        |

NC = No internal connection

# SN74GTLP2033 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH

SCES352C – JUNE 2001 – REVISED SEPTEMBER 2001

#### ORDERING INFORMATION

| TA            | PACKAGE <sup>†</sup> |               | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|---------------|----------------------|---------------|--------------------------|---------------------|

|               | TSSOP – DGG          | Tape and reel | SN74GTLP2033DGGR         | GTLP2033            |

| -40°C to 85°C | TVSOP – DGV          | Tape and reel | SN74GTLP2033DGVR         | GT2033              |

|               | VFBGA – GQL          | Tape and reel | SN74GTLP2033GQLR         | GR033               |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

### functional description

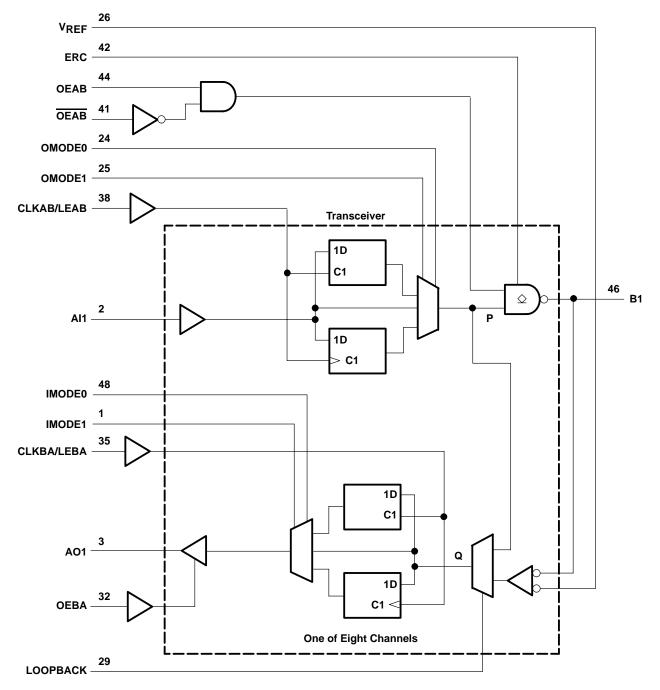

The SN74GTLP2033 is a high-drive (100 mA), 8-bit, three-wire registered transceiver containing D-type latches and D-type flip-flops for data-path operation in the transparent, latched, or flip-flop modes. Data transmission is complementary, with inverted AI data going to the B port and inverted B data going to AO. The split LVTTL AI and AO provides a feedback path for control and diagnostics monitoring.

The logic element for data flow in each direction is configured by two mode (IMODE1 and IMODE0 for B to A, OMODE1 and OMODE0 for A to B) inputs as a buffer, D-type flip-flop, or D-type latch. When configured in the buffer mode, the inverted input data appears at the output port. In the flip-flop mode, data is stored on the rising edge of the appropriate clock (CLKAB/LEAB or CLKBA/LEBA) input. In the latch mode, the clock inputs serve as active-high transparent latch enables.

Data flow in the B-to-A direction, regardless of the logic element selected, is further controlled by the LOOPBACK input. When LOOPBACK is low, B-port data is the B-to-A input. When LOOPBACK is high, the output of the selected A-to-B logic element (prior to inversion) is the B-to-A input.

The AO enable/disable control is provided by OEBA. When OEBA is low or when  $V_{CC}$  is less than 1.5 V, AO is in the high-impedance state. When OEBA is high, AO is active (high or low logic levels).

The B port is controlled by OEAB and  $\overline{OEAB}$ . If OEAB is low,  $\overline{OEAB}$  is high, or  $V_{CC}$  is less than 1.5 V, the B port is inactive. If OEAB is high and  $\overline{OEAB}$  is low, the B port is active.

The A-to-B and B-to-A logic elements are active, regardless of the state of their associated outputs. The logic elements can enter new data (in flip-flop and latch modes) or retain previously stored data while the associated outputs are in the high-impedance (AO) or inactive (B port) states.

# 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH SCES352C - JUNE 2001 - REVISED SEPTEMBER 2001

#### **Function Tables**

#### FUNCTION/MODE

|      |      |      |        | INPUTS |        |        |          | OUTPUT                                | MODE                           |

|------|------|------|--------|--------|--------|--------|----------|---------------------------------------|--------------------------------|

| OEBA | OEAB | OEAB | OMODE1 | OMODE0 | IMODE1 | IMODE0 | LOOPBACK | OUTPUT                                | MODE                           |

| L    | L    | Х    | Х      | Х      | Х      | Х      | Х        | Z                                     | Isolation                      |

| L    | Х    | Н    | Χ      | Χ      | Χ      | Χ      | X        | ۷                                     | ISOIAUOII                      |

| Х    | Н    | L    | L      | L      | Х      | Х      | Х        |                                       | Buffer                         |

| Х    | Н    | L    | L      | Н      | Χ      | Χ      | X        | Inverted AI to B                      | Flip-flop                      |

| Х    | Н    | L    | Н      | Χ      | Х      | Χ      | X        |                                       | Latch                          |

| Н    | L    | Х    | Х      | Х      | L      | L      | L        | lavorate d B to AO                    | D. "                           |

| Н    | Х    | Н    | Χ      | Χ      | L      | L      | L        | Inverted B to AO                      | Buffer                         |

| Н    | L    | Х    | Х      | Х      | L      | Н      | L        | Increased Disc AO                     | Tin floor                      |

| Н    | Χ    | Н    | Χ      | Χ      | L      | Н      | L        | Inverted B to AO                      | Flip-flop                      |

| Н    | L    | Х    | Х      | Х      | Н      | Х      | L        | Increased Disc AO                     | Latek                          |

| Н    | Х    | Н    | Χ      | Χ      | Н      | Χ      | L        | Inverted B to AO                      | Latch                          |

| Н    | L    | Х    | Х      | Χ      | L      | L      | Н        | AI to AO                              | Buffer                         |

| Н    | Х    | Н    | Х      | Х      | L      | L      | Н        | AI IU AO                              | Bullet                         |

| Н    | L    | Χ    | Χ      | Χ      | L      | Н      | Н        | AI to AO                              | Flip-flop                      |

| Н    | Χ    | Н    | Χ      | Χ      | L      | Н      | Н        | AI to AO                              | т пр-пор                       |

| Н    | L    | Х    | Х      | Χ      | Н      | Х      | Н        | AI to AO                              | Latch                          |

| Н    | Х    | Н    | Χ      | Χ      | Н      | Х      | Н        | AI IU AO                              | Later                          |

| Н    | Н    | L    | Х      | Х      | Х      | Х      | L        | Inverted AI to B,<br>Inverted B to AO | Transparent with feedback path |

### **ENABLE/DISABLE**

| INPUTS |      |      | OUTI   | PUTS   |

|--------|------|------|--------|--------|

| OEBA   | OEAB | OEAB | AO     | В      |

| L      | Х    | Х    | Z      |        |

| Н      | Χ    | Χ    | Active |        |

| Х      | L    | L    |        | Z      |

| Х      | L    | Н    |        | Z      |

| Х      | Н    | L    |        | Active |

| Х      | Н    | Н    |        | Z      |

#### **BUFFER**

| INPUT | OUTPUT |

|-------|--------|

| L     | Н      |

| Н     | L      |

#### **LATCH**

| INPU <sup>*</sup> | OUTPUT |        |

|-------------------|--------|--------|

| CLK/LE            | DATA   | OUIFUI |

| Н                 | L      | Н      |

| Н                 | Н      | L      |

| L                 | X      | $Q_0$  |

# **SN74GTLP2033** 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LYTTL PORT AND FEEDBACK PATH SCES352C – JUNE 2001 – REVISED SEPTEMBER 2001

## **Function Tables (Continued)**

### LOOPBACK

| LOOPBACK | Q†       |

|----------|----------|

| L        | B port   |

| Н        | Point P‡ |

TQ is the input to the B-to-A logic element.

#### **SELECT**

| INPUTS |       | SELECTED LOGIC |  |

|--------|-------|----------------|--|

| MODE1  | MODE0 | ELEMENT        |  |

| L      | L     | Buffer         |  |

| L      | Н     | Flip-flop      |  |

| Н      | Χ     | Latch          |  |

#### **FLIP-FLOP**

| INPU        | OUTPUT |                |

|-------------|--------|----------------|

| CLK/LE DATA |        | OUTFUT         |

| L           | Χ      | Q <sub>0</sub> |

| 1           | L      | Н              |

| 1           | Н      | L              |

### **B-PORT EDGE-RATE CONTROL (ERC)**

| INPUT<br>ERC | OUTPUT<br>B-PORT |

|--------------|------------------|

| LOGIC LEVEL  | EDGE RATE        |

| Н            | Slow             |

| L            | Fast             |

<sup>‡</sup>P is the output of the A-to-B logic element (see functional block diagram).

# 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH

SCES352C – JUNE 2001 – REVISED SEPTEMBER 2001

### functional block diagram

Pin numbers shown are for the DGG and DGV packages.

# SN74GTLP2033 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH

SCES352C – JUNE 2001 – REVISED SEPTEMBER 2001

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> and BIAS V <sub>CC</sub>                     |               |

|------------------------------------------------------------------------------------|---------------|

| Input voltage range, V <sub>I</sub> (see Note 1): Al port, ERC, and control inputs | –0.5 V to 7 V |

| B port and V <sub>REF</sub>                                                        |               |

| Voltage range applied to any output in the high-impedance or power-off state, VO   |               |

| (see Note 1): AO port                                                              | –0.5 V to 7 V |

| B port                                                                             |               |

| Current into any output in the low state, IO: AO port                              | 48 mA         |

| B port                                                                             |               |

| Current into any A-port output in the high state, IO (see Note 2)                  | 48 mA         |

| Continuous current through each V <sub>CC</sub> or GND                             | ±100 mA       |

| Input clamp current, $I_{IK}$ ( $V_I < 0$ )                                        |               |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0)                         |               |

| Package thermal impedance, θ <sub>JA</sub> (see Note 3): DGG package               |               |

| DGV package                                                                        | 58°C/W        |

| GQL package                                                                        |               |

| Storage temperature range, T <sub>Sto</sub>                                        |               |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- 2. This current flows only when the output is in the high state and  $V_O > V_{CC}$ .

- 3. The package thermal impedance is calculated in accordance with JESD 51-7.

# 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH

SCES352C - JUNE 2001 - REVISED SEPTEMBER 2001

### recommended operating conditions (see Notes 4 through 7)

|                                           |                                    |                        | MIN                    | NOM | MAX                    | UNIT |

|-------------------------------------------|------------------------------------|------------------------|------------------------|-----|------------------------|------|

| V <sub>CC</sub> ,<br>BIAS V <sub>CC</sub> | Supply voltage                     |                        | 3.15                   | 3.3 | 3.45                   | V    |

| \ <u></u>                                 | Termination voltage                | GTL                    | 1.14                   | 1.2 | 1.26                   | V    |

| VTT                                       | remination voltage                 | GTLP                   | 1.35                   | 1.5 | 1.65                   | V    |

| \/===                                     | Reference voltage                  | GTL                    | 0.74                   | 8.0 | 0.87                   | V    |

| VREF                                      | Reference voltage                  | GTLP                   | 0.87                   | 1   | 1.1                    | V    |

| \/.                                       | Input voltage                      | B port                 |                        |     | VTT                    | V    |

| VI                                        | Input voltage                      | Except B port and VREF |                        | Vcc | 5.5                    | V    |

|                                           | High level input voltage           | B port                 | V <sub>REF</sub> +0.05 |     |                        | V    |

| VIH                                       | High-level input voltage           | Except B port          | 2                      |     |                        | V    |

| \/                                        | Low lovel input voltage            | B port                 |                        |     | V <sub>REF</sub> -0.05 | V    |

| VIL                                       | Low-level input voltage            | Except B port          |                        |     | 0.8                    | V    |

| lıĸ                                       | Input clamp current                |                        |                        |     | -18                    | mA   |

| loн                                       | High-level output current          | AO                     |                        |     | -24                    | mA   |

| 1                                         | Low lovel output output            | AO                     |                        |     | 24                     | A    |

| lOL                                       | Low-level output current           | B port                 |                        |     | 100                    | mA   |

| Δt/Δν                                     | Input transition rise or fall rate | Outputs enabled        |                        |     | 10                     | ns/V |

| Δt/ΔV <sub>CC</sub>                       | Power-up ramp rate                 |                        | 20                     |     |                        | μs/V |

| T <sub>A</sub>                            | Operating free-air temperature     |                        | -40                    |     | 85                     | °C   |

- NOTES: 4. All unused control and B-port inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, *Implications of Slow or Floating CMOS Inputs*, literature number SCBA004.

- 5. Proper connection sequence for use of the B-port I/O precharge feature is GND and BIAS V<sub>CC</sub> = 3.3 V first, I/O second, and V<sub>CC</sub> = 3.3 V last, because the BIAS V<sub>CC</sub> precharge circuitry is disabled when any V<sub>CC</sub> pin is connected. The control and V<sub>REF</sub> inputs can be connected anytime, but normally are connected during the I/O stage. If B-port precharge is not required, any connection sequence is acceptable but, generally, GND is connected first.

- 6. V<sub>TT</sub> and R<sub>TT</sub> can be adjusted to accommodate backplane impedances if the dc recommended I<sub>OL</sub> ratings are not exceeded.

- 7. VREF can be adjusted to optimize noise margins, but normally is two-thirds V<sub>TT</sub>. TI-OPC circuitry is enabled in the A-to-B direction and is activated when V<sub>TT</sub> > 0.7 V above V<sub>REF</sub>. If operated in the A-to-B direction, V<sub>REF</sub> should be set to within 0.6 V of V<sub>TT</sub> to minimize current drain.

# 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH

SCES352C - JUNE 2001 - REVISED SEPTEMBER 2001

# electrical characteristics over recommended operating free-air temperature range for GTLP (unless otherwise noted)

|                  | PARAMETER             | TEST CONDITIONS                                                                                               | TEST CONDITIONS                                                   |                      |     | MAX  | UNIT |  |

|------------------|-----------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------|-----|------|------|--|

| VIK              |                       | V <sub>CC</sub> = 3.15 V,                                                                                     | I <sub>I</sub> = -18 mA                                           |                      |     | -1.2 | V    |  |

|                  |                       | $V_{CC} = 3.15 \text{ V to } 3.45 \text{ V},$                                                                 | I <sub>OH</sub> = -100 μA                                         | V <sub>CC</sub> -0.2 |     |      |      |  |

| $V_{OH}$         | AO                    | V <sub>CC</sub> = 3.15 V                                                                                      | $I_{OH} = -12 \text{ mA}$                                         | 2.4                  |     |      | V    |  |

|                  |                       | VCC = 3.13 V                                                                                                  | $I_{OH} = -24 \text{ mA}$                                         | 2                    |     |      |      |  |

|                  |                       | $V_{CC} = 3.15 \text{ V to } 3.45 \text{ V},$                                                                 | I <sub>OL</sub> = 100 μA                                          |                      |     | 0.2  |      |  |

|                  | AO                    | V <sub>CC</sub> = 3.15 V                                                                                      | I <sub>OL</sub> = 12 mA                                           |                      |     | 0.4  |      |  |

| VOL              |                       | VCC = 3.13 V                                                                                                  | $I_{OL} = 24 \text{ mA}$                                          |                      |     | 0.5  | V    |  |

| VOL              |                       |                                                                                                               | $I_{OL} = 10 \text{ mA}$                                          |                      |     | 0.2  | V    |  |

|                  | B port                | $V_{CC} = 3.15 \text{ V}$                                                                                     | 3.15 V I <sub>OL</sub> = 64 mA                                    |                      |     | 0.4  |      |  |

|                  |                       |                                                                                                               | I <sub>OL</sub> = 100 mA                                          |                      |     | 0.55 |      |  |

| I <sub>I</sub> ‡ | Al and control inputs | V <sub>CC</sub> = 3.45 V,                                                                                     | $V_{CC} = 3.45 \text{ V},$ $V_{I} = 0 \text{ or } 5.5 \text{ V}$  |                      |     | ±10  | μΑ   |  |

| . +              | AO                    | V <sub>CC</sub> = 3.45 V,                                                                                     | $V_0 = 0 \text{ to } 5.5 \text{ V}$                               |                      |     | ±10  | A    |  |

| loz‡             | B port                | $V_{CC}$ = 3.45 V, $V_{REF}$ within 0.6 V of $V_{TT}$ ,                                                       | $V_0 = 0 \text{ to } 2.3 \text{ V}$                               |                      |     | ±10  | μΑ   |  |

|                  |                       | V <sub>CC</sub> = 3.45 V, I <sub>O</sub> = 0,                                                                 | Outputs high                                                      |                      |     | 40   |      |  |

| ICC              | AO or B port          | $V_I$ (A-port or control input) = $V_{CC}$ or GND,                                                            | Outputs low                                                       |                      |     | 40   | mA   |  |

|                  |                       | $V_I$ (B port) = $V_{TT}$ or GND                                                                              | V <sub>I</sub> (B port) = V <sub>TT</sub> or GND Outputs disabled |                      |     | 40   |      |  |

| ΔICC§            |                       | $V_{CC}$ = 3.45 V, One AI or control input at $V_{CC}$ – 0.6 V, Other AI or control inputs at $V_{CC}$ or GND |                                                                   |                      |     | 1.5  | mA   |  |

| C.               | Al                    | V <sub>I</sub> = 3.15 V or 0                                                                                  |                                                                   |                      | 3.5 | 4.5  |      |  |

| Ci               | Control inputs        |                                                                                                               |                                                                   |                      | 3.5 | 5.5  | pF   |  |

| Co               | AO                    | V <sub>O</sub> = 3.15 V or 0                                                                                  |                                                                   | 5                    | 6   | pF   |      |  |

| C <sub>io</sub>  | B port                | V <sub>O</sub> = 1.5 V or 0                                                                                   |                                                                   |                      | 8.5 | 10   | pF   |  |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

### hot-insertion specifications for A port over recommended operating free-air temperature range

| PARAMETER         |                                         | TEST CONDITIONS               |                        |  |     |    |

|-------------------|-----------------------------------------|-------------------------------|------------------------|--|-----|----|

| l <sub>off</sub>  | $V_{CC} = 0$ ,                          | $V_I$ or $V_O = 0$ to 5.5 $V$ |                        |  | 10  | μΑ |

| lozpu             | $V_{CC} = 0 \text{ to } 1.5 \text{ V},$ | $V_0 = 0.5 \text{ V to 3 V},$ | OEBA = V <sub>CC</sub> |  | ±30 | μΑ |

| I <sub>OZPD</sub> | $V_{CC} = 1.5 \text{ V to } 0,$         | $V_0 = 0.5 \text{ V to 3 V},$ | OEBA = VCC             |  | ±30 | μΑ |

### live-insertion specifications for B port over recommended operating free-air temperature range

| PARAMETER               |                                                | MIN                                                                                                                                        | MAX                           | UNIT |      |    |  |

|-------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------|------|----|--|

| l <sub>off</sub>        | $V_{CC} = 0$ ,                                 | BIAS $V_{CC} = 0$ ,                                                                                                                        | $V_I$ or $V_O = 0$ to 1.5 $V$ |      | 10   | μΑ |  |

| lozpu                   | $V_{CC} = 0$ to 1.5 V, BIAS V                  | $_{CC}$ = 0 to 1.5 V, BIAS $_{CC}$ = 0, $_{O}$ = 0.5 V to 1.5 V, $\overline{OEAB}$ = 0 and $OEAB$ = $_{CC}$                                |                               |      |      |    |  |

| lozpd                   | $V_{CC} = 1.5 \text{ V to } 0, \text{ BIAS } $ | $V_{CC} = 1.5 \text{ V to } 0$ , BIAS $V_{CC} = 0$ , $V_{O} = 0.5 \text{ V to } 1.5 \text{ V}$ , $\overline{OEAB} = 0$ and $OEAB = V_{CC}$ |                               |      |      |    |  |

| Icc                     | $V_{CC} = 0 \text{ to } 3.15 \text{ V}$        | BIAS V <sub>CC</sub> = 3.15 V to 3.45 V,                                                                                                   | Vo (P. port) - 0 to 1.5 V     |      | 5    | mA |  |

| (BIAS V <sub>CC</sub> ) | V <sub>CC</sub> = 3.15 V to 3.45 V             | DIAS VCC = 3.15 V to 3.45 V,                                                                                                               | VO (В роп) = 0 to 1.5 V       |      | 10   | μΑ |  |

| Vo                      | $V_{CC} = 0$ ,                                 | BIAS $V_{CC} = 3.3 \text{ V}$ ,                                                                                                            | I <sub>O</sub> = 0            | 0.95 | 1.05 | V  |  |

| lo                      | $V_{CC} = 0$ ,                                 | BIAS $V_{CC} = 3.15 \text{ V to } 3.45 \text{ V}$ ,                                                                                        | $V_O$ (B port) = 0.6 V        | -1   |      | μΑ |  |

<sup>‡</sup> For I/O ports, the parameter IOZ includes the input leakage current.

<sup>§</sup> This is the increase in supply current for each input that is at the specified TTL voltage level rather than VCC or GND.

# **SN74GTLP2033** 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH SCES352C – JUNE 2001 – REVISED SEPTEMBER 2001

timing requirements over recommended ranges of supply voltage and operating free-air temperature,  $V_{TT}$  = 1.5 V and  $V_{REF}$  = 1 V for GTLP (unless otherwise noted)

|                        |                 |                          | MIN | MAX | UNIT |  |

|------------------------|-----------------|--------------------------|-----|-----|------|--|

| fclock                 | Clock frequency |                          |     | 175 | MHz  |  |

| t <sub>W</sub>         | Pulse duration  | CLKAB/LEAB or CLKBA/LEBA | 2.8 |     | ns   |  |

|                        |                 | Al before CLKAB↑         | 1.1 |     |      |  |

|                        |                 | Al before CLKBA↑         | 1.4 |     |      |  |

|                        | Catua tima      | B before CLKBA↑          | 1   |     |      |  |

| t <sub>su</sub>        | Setup time      | Al before LEAB↓          | 1.6 |     | ns   |  |

|                        |                 | Al before LEBA↓          | 2.1 |     |      |  |

|                        |                 | B before LEBA↓           | 2.2 |     |      |  |

|                        |                 | Al after CLKAB↑          | 0.3 |     |      |  |

|                        |                 | Al after CLKBA↑          | 0.2 |     |      |  |

| 4.                     | Hold time       | B after CLKBA↑           | 0.6 |     |      |  |

| t <sub>h</sub> Hold ti | 101d time       | Al after LEAB↓           | 0.3 |     | ns   |  |

|                        |                 | Al after LEBA↓           | 0   |     |      |  |

|                        |                 | 0                        |     |     |      |  |

# **SN74GTLP2033** 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LYTTL PORT AND FEEDBACK PATH SCES352C – JUNE 2001 – REVISED SEPTEMBER 2001

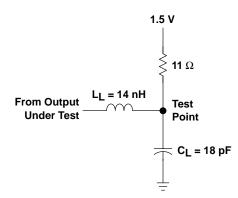

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature, $V_{TT}$ = 1.5 V and $V_{REF}$ = 1 V for GTLP (see Figure 1)

| PARAMETER        | FROM<br>(INPUT)    | TO<br>(OUTPUT) | EDGE RATE† | MIN | TYP <sup>‡</sup> MAX | UN       |   |

|------------------|--------------------|----------------|------------|-----|----------------------|----------|---|

| f <sub>max</sub> |                    |                |            | 175 |                      | MH       |   |

| <sup>t</sup> PLH | Al                 |                | - C        | 3   | 7.4                  |          |   |

| <sup>t</sup> PHL | (buffer)           | В              | Slow       | 3   | 7.1                  | ns       |   |

| <sup>t</sup> PLH | Al                 |                |            | 2   | 5.9                  |          |   |

| <sup>t</sup> PHL | HL (buffer) B Fast |                | 2          | 5.8 | ns                   |          |   |

| <sup>t</sup> PLH | В                  | AO             | _          | 1   | 5.7                  |          |   |

| <sup>t</sup> PHL | (buffer)           | AO             | _          | 1   | 5                    | n        |   |

| <sup>t</sup> PLH | LEAB               | 6              | Class      | 4.2 | 8.6                  | n        |   |

| <sup>t</sup> PHL | (latch mode)       | В              | Slow       | 3.2 | 7.7                  | "        |   |

| <sup>t</sup> PLH | LEAB               | В              | Foot       | 3.2 | 7.6                  | n        |   |

| <sup>t</sup> PHL | (latch mode)       | Ь              | Fast       | 2.8 | 6.7                  | "        |   |

| <sup>t</sup> PLH | LEAB               | 40             |            | 2   | 7                    | n        |   |

| <sup>t</sup> PHL | (latch mode)       | AO             | _          | 1.8 | 6.3                  | "        |   |

| <sup>t</sup> PLH | LEBA               | AO             |            | 1   | 5.7                  |          |   |

| <sup>t</sup> PHL | (latch mode)       | AO             | _          | 1   | 4.7                  | n        |   |

| <sup>t</sup> PLH | OEAB               | В              | Class      | 3.8 | 7.5                  | r        |   |

| <sup>t</sup> PHL | OEAB               | Ь              | Slow       | 3.1 | 7                    | '        |   |

| <sup>t</sup> PLH | OEAB               | В              | Fast       | 2.5 | 6                    | r        |   |

| <sup>t</sup> PHL | OEAB               | D              | Fasi       | 2.5 | 6                    | '        |   |

| <sup>t</sup> PLH | <del></del> OEAB   | В              | Slow       | 3.5 | 7.5                  | r        |   |

| <sup>t</sup> PHL | UEAB               | В              | Slow       | 3   | 7.2                  |          |   |

| <sup>t</sup> PLH | <del></del> OEAB   | В              | Fast       | 2.5 | 6                    | r        |   |

| <sup>t</sup> PHL | UEAB               | Ь              | Fasi       | 2.5 | 6                    | ı '      |   |

| <sup>t</sup> PZH | OEBA               | AO             | _          | 1   | 4.7                  | r        |   |

| <sup>t</sup> PZL | OLBA               | AO             | _          | 1   | 3.4                  | <u>'</u> |   |

| <sup>t</sup> PHZ | OEBA               | AO             | _          | 1   | 5.2                  | r        |   |

| <sup>t</sup> PLZ | OLBA               | AO             | _          | 1   | 4.9                  | '        |   |

| <sup>t</sup> PLH | CLKAB              | В              | Slow       | 4.4 | 8.8                  | l n      |   |

| <sup>t</sup> PHL | (flip-flop mode)   | Ь              | Slow       | 3.6 | 8.1                  |          |   |

| <sup>t</sup> PLH | CLKAB              | В              | Fast       | 3.2 | 7.2                  | l r      |   |

| <sup>t</sup> PHL | (flip-flop mode)   | Ь              | Fasi       | 3.1 | 6.9                  |          |   |

| <sup>t</sup> PLH | CLKAB              | AO             | _          | 2   | 6.9                  | l r      |   |

| <sup>t</sup> PHL | (flip-flop mode)   | 7.0            |            | 1.8 | 6.4                  |          |   |

| <sup>t</sup> PLH | CLKBA              | AO             | _          | 1   | 5.6                  | l r      |   |

| <sup>t</sup> PHL | (flip-flop mode)   | Α0             |            | 1   | 4.9                  | <u>L</u> |   |

| <sup>t</sup> PLH | OMODE              | В              | Slow       | 3.8 | 8.7                  | ,        |   |

| <sup>t</sup> PHL | O.M.ODE            | D              | Siow       | 3.2 | 8.2                  | ns       |   |

| <sup>t</sup> PLH | OMODE B            | В              | Fast       | 2.7 | 7.2                  | n        |   |

| t <sub>PHL</sub> | SSE                |                | rasi       | 2.7 | 7.2                  |          |   |

| <sup>t</sup> PLH | IMODE              | 40             | IMODE AO   | _   | 1                    | 5.6      | n |

| <sup>t</sup> PHL | INIODE             | AO             |            | 1   | 4.6                  | l ''     |   |

<sup>†</sup> Slow (ERC = H) and Fast (ERC = L)

<sup>‡</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

# 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH

SCES352C - JUNE 2001 - REVISED SEPTEMBER 2001

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature, $V_{TT} = 1.5 \text{ V}$ and $V_{REF} = 1 \text{ V}$ for GTLP (see Figure 1) (continued)

| PARAMETER        | FROM<br>(INPUT)                | TO<br>(OUTPUT)                   | EDGE RATE <sup>†</sup> | MIN | түр‡ | MAX | UNIT |

|------------------|--------------------------------|----------------------------------|------------------------|-----|------|-----|------|

| t <sub>PLH</sub> | LOOPBACK                       | AO                               |                        | 2.5 | 6.2  | 6.2 | ns   |

| <sup>t</sup> PHL | LOOPBACK                       | AO                               | _                      | 2   | 5    | 5   | 115  |

| <sup>t</sup> PLH | Al                             | AO                               |                        | 1   | 5.6  | 5.6 | ns   |

| t <sub>PHL</sub> | (loopback high)                | AO                               | _                      | 1   | 5    | 5   | 115  |

|                  | Rise time, B-port outputs (20  | 19/. to 909/.)                   | Slow                   |     | 2.8  |     |      |

| t <sub>r</sub>   | Kise time, b-port outputs (20  | e, b-port outputs (20 % to 80 %) |                        |     | 1.5  |     | ns   |

|                  | Rise time, AO (10% to 90%)     |                                  |                        |     | 3.5  |     |      |

|                  | Fall time P part outputs (909  | Slow                             |                        | 3   |      | ns  |      |

| t <sub>f</sub>   | Fall time, B-port outputs (80% | Fast                             |                        | 1.8 |      |     |      |

|                  | Fall time, AO (90% to 10%)     |                                  |                        |     | 1.5  |     |      |

<sup>†</sup> Slow (ERC = H) and Fast (ERC = L)

# skew characteristics over recommended ranges of supply voltage and operating free-air temperature (see Figure 1)§

| PARAMETER             | FROM<br>(INPUT) | TO<br>(OUTPUT) | EDGE RATET | MIN TYP‡ | MAX | UNIT |

|-----------------------|-----------------|----------------|------------|----------|-----|------|

| t <sub>sk(LH)</sub> ¶ | Al              | AI B           |            | 0.5      | 1   | ns   |

| t <sub>sk(HL)</sub> ¶ | 741             | J G            | Slow       | 0.5      | 1   | 113  |

| t <sub>sk(LH)</sub> ¶ | Al              | В              | Fast       | 0.4      | 0.9 | ns   |

| t <sub>sk(HL)</sub> ¶ | 741             | J G            | D Fast     |          | 0.9 | 113  |

| t <sub>sk(LH)</sub> ¶ | CLKAB/LEAB      | В              | Slow       | 0.5      | 1   | ns   |

| t <sub>sk(HL)</sub> ¶ | OLIVAD/LEAD     | J G            | Glow       | 0.5      | 1   | 5    |

| t <sub>sk(LH)</sub> ¶ | CLKAB/LEAB      | В              | Fast       | 0.4      | 0.9 | ns   |

| t <sub>sk(HL)</sub> ¶ | OLIVAD/LEAD     | J G            | 1 431      | 0.4      | 0.9 | 113  |

|                       | Al              | В              | Slow       | 1.4      | 2   |      |

| t <sub>sk(t)</sub> ¶  | 7.11            | 5              | Fast       | 0.6      | 1.4 | ns   |

| 'SK(t)"               | CLKAB/LEAB      | В              | Slow       | 1.8      | 2.5 | 113  |

|                       | CLIVAD/LLAD     | ט              | Fast       | 0.9      | 1.8 |      |

<sup>†</sup> Slow (ERC = L) and Fast (ERC = H)

<sup>‡</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

<sup>‡</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

<sup>§</sup> Actual skew values between the GTLP outputs could vary on the backplane due to the loading and impedance seen by the device.

$<sup>1 +</sup> t_{sk(LH)}/t_{sk(HL)}$  and  $1 + t_{sk(t)}$ . Output-to-output skew is defined as the absolute value of the difference between the actual propagation delay for all outputs with the same packaged device. The specifications are given for specific worst-case  $1 + t_{co}$  and temperature and apply to any outputs switching in the same direction either high to low  $1 + t_{co}$  or low to high  $1 + t_{co}$  or in opposite directions, both low to high and high to low  $1 + t_{co}$  or in opposite directions, both low to high and high to low  $1 + t_{co}$  or in opposite directions, both low to high and high to low  $1 + t_{co}$  or in opposite directions, both low to high and high to low  $1 + t_{co}$  or in opposite directions, both low to high and high to low  $1 + t_{co}$  or in opposite directions, both low to high and high to low  $1 + t_{co}$  or in opposite directions, both low to high and high to low  $1 + t_{co}$  or in opposite directions.

# SN74GTLP2033 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH

SCES352C – JUNE 2001 – REVISED SEPTEMBER 2001

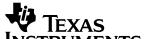

#### PARAMETER MEASUREMENT INFORMATION

- NOTES: A.  $C_L$  includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\approx$  10 MHz,  $Z_O = 50 \Omega$ ,  $t_f \approx 2$  ns,  $t_f \approx 2$  ns.

- D. The outputs are measured one at a time with one transition per measurement.

Figure 1. Load Circuits and Voltage Waveforms

# 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LVTTL PORT AND FEEDBACK PATH

SCES352C - JUNE 2001 - REVISED SEPTEMBER 2001

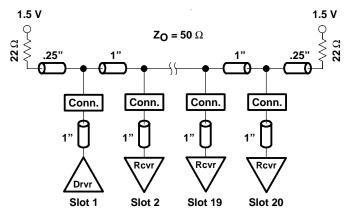

### DISTRIBUTED-LOAD BACKPLANE SWITCHING CHARACTERISTICS

The preceding switching characteristics table shows the switching characteristics of the device into a lumped load (Figure 1). However, the designer's backplane application is probably a distributed load. The physical representation is shown in Figure 2. This backplane, or distributed load, can be approximated closely to a resistor inductance capacitance (RLC) circuit, as shown in Figure 3. This device has been designed for optimum performance in this RLC circuit. The following switching characteristics table shows the switching characteristics of the device into the RLC load, to help the designer to better understand the performance of the GTLP device in this typical backplane. See www.ti.com/sc/gtlp for more information.

Figure 2. High-Drive Test Backplane

Figure 3. High-Drive RLC Network

# **SN74GTLP2033** 8-BIT LVTTL-TO-GTLP ADJUSTABLE-EDGE-RATE REGISTERED TRANSCEIVER WITH SPLIT LYTTL PORT AND FEEDBACK PATH SCES352C - JUNE 2001 - REVISED SEPTEMBER 2001

# switching characteristics over recommended operating conditions for the bus transceiver function (unless otherwise noted) (see Figure 3)

| PARAMETER        | FROM<br>(INPUT)                | TO<br>(OUTPUT) | EDGE RATE† | түр‡ | UNIT  |

|------------------|--------------------------------|----------------|------------|------|-------|

| <sup>t</sup> PLH | Al                             |                | <u> </u>   | 4.7  |       |

| <sup>t</sup> PHL | (buffer)                       | В              | Slow       | 5    | ns    |

| <sup>t</sup> PLH | Al                             |                | Face       | 3.7  | ns    |

| t <sub>PHL</sub> | (buffer)                       | В              | Fast       | 4    | 115   |

| <sup>t</sup> PLH | LEAB                           | В              | Clour      | 5.5  | ns    |

| t <sub>PHL</sub> | (latch mode)                   | В              | Slow       | 5.8  | 115   |

| <sup>t</sup> PLH | LEAB                           |                | Fast       | 4.6  | ns    |

| t <sub>PHL</sub> | (latch mode)                   | В              | Fasi       | 4.8  | 115   |

| <sup>t</sup> PLH | CLKAB                          | В              | Slow       | 5.8  | ns    |

| t <sub>PHL</sub> | (flip-flop mode)               | В              | 210W       | 6    | 113   |

| <sup>t</sup> PLH | CLKAB                          | В              | Fast       | 4.9  | ns    |

| t <sub>PHL</sub> | (flip-flop mode)               | Ь              | i asi      | 4.9  | 110   |

| <sup>t</sup> PLH | OMODE                          | В              | Slow       | 5.5  | ns    |

| t <sub>PHL</sub> | OWODE                          | Ь              | Slow       | 5.7  | 113   |

| <sup>t</sup> PLH | OMODE                          | В              | Fast       | 4.5  | ns    |

| t <sub>PHL</sub> | OMOBE                          | Ь              | i asi      | 4.7  | 110   |

| t <sub>r</sub>   | Rise time, B-port outputs (20  | % to 80%)      | Slow       | 1.8  | ns    |

| ή                |                                |                | Fast       | 1.1  | - 110 |

| tf               | Fall time, B-port outputs (80% | % to 20%)      | Slow       | 3.4  | ns    |

| ۳<br>ا           | Tan anie, B port outputs (00)  | 0 10 20 70,    | Fast       | 2.6  |       |

<sup>†</sup> Slow (ERC = H) and Fast (ERC = L)

$<sup>\</sup>ddagger$  All typical values are at V<sub>CC</sub> = 3.3 V, T<sub>A</sub> = 25°C. All values are derived from TI-SPICE models.

### PACKAGE OPTION ADDENDUM

19-May-2005

### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|-------------------------|------------------|------------------------------|

| 74GTLP2033DGGRE4 | ACTIVE                | TSSOP           | DGG                | 48   | 2000           | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-1-250C-UNLIM           |

| 74GTLP2033DGVRE4 | ACTIVE                | TVSOP           | DGV                | 48   | 2000           | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-1-250C-UNLIM           |

| SN74GTLP2033DGGR | ACTIVE                | TSSOP           | DGG                | 48   | 2000           | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-1-250C-UNLIM           |

| SN74GTLP2033DGVR | ACTIVE                | TVSOP           | DGV                | 48   | 2000           | Pb-Free<br>(RoHS)       | CU NIPDAU        | Level-1-250C-UNLIM           |

| SN74GTLP2033GQLR | ACTIVE                | VFBGA           | GQL                | 56   | 1000           | TBD                     | SNPB             | Level-1-240C-UNLIM           |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

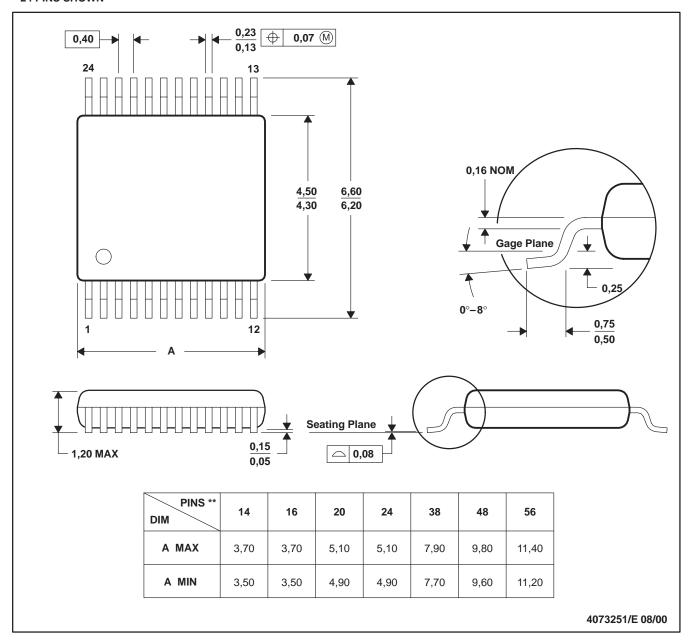

### DGV (R-PDSO-G\*\*)

### **24 PINS SHOWN**

### **PLASTIC SMALL-OUTLINE**

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0,15 per side.

- D. Falls within JEDEC: 24/48 Pins MO-153 14/16/20/56 Pins – MO-194

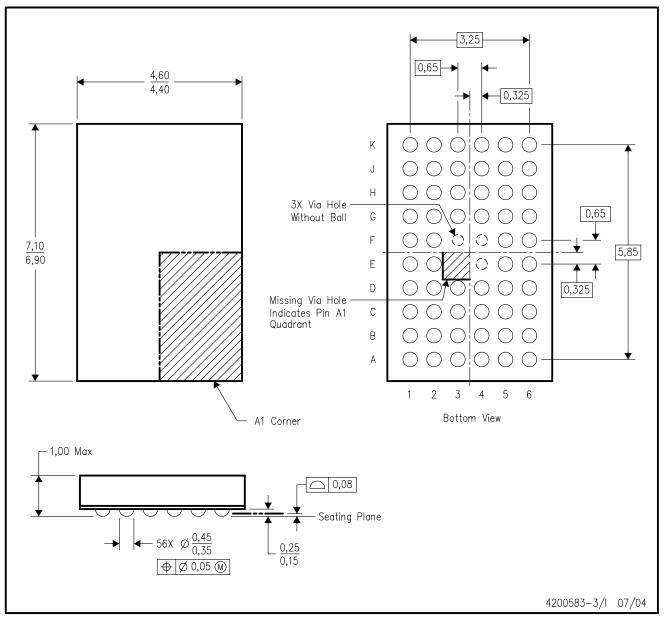

# GQL (R-PBGA-N56)

# PLASTIC BALL GRID ARRAY

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MO-225 variation BA.

- D. This package is tin-lead (SnPb). Refer to the 56 ZQL package (drawing 4204437) for lead-free.

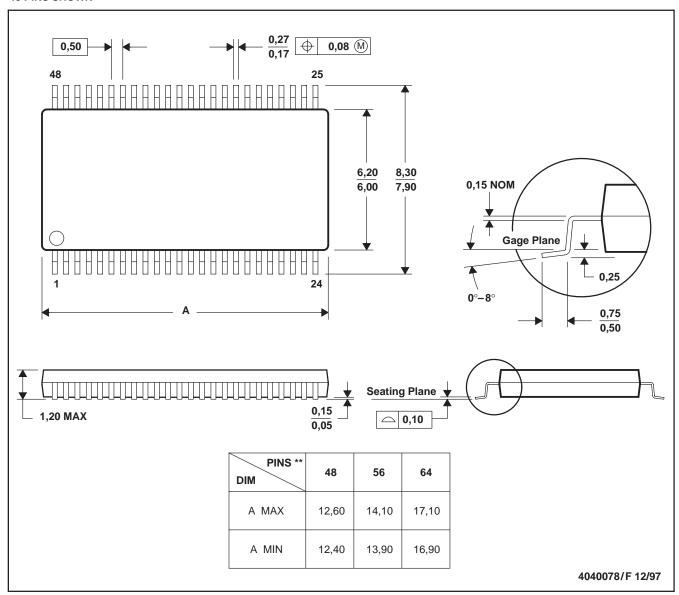

## DGG (R-PDSO-G\*\*)

### PLASTIC SMALL-OUTLINE PACKAGE

### **48 PINS SHOWN**

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold protrusion not to exceed 0,15.

- D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265