# 80960SA WWW.DZSC.COM EMBEDDED 32-BIT MICROPROCESSOR WITH 16-BIT BURST DATA BUS

- High-Performance Embedded

- Architecture

int

- 20 MIPS\* Burst Execution at 20 MHz 7.5 MIPS Sustained Execution

- at 20 MHz

- 512-Byte On-Chip Instruction Cache Direct Mapped

- Parallel Load/Decode for Uncached Instructions

- Multiple Register Sets

- Sixteen Global 32-Bit Registers

- Sixteen Local 32-Bit Registers

- Four Local Register Sets Stored

- **On-Chip**

- **Register Scoreboarding**

- Pin Compatible with 80960SB

- **Built-in Interrupt Controller**

- 4 Direct Interrupt Pins

- 31 Priority Levels, 256 Vectors

- Easy to Use, High Bandwidth 16-Bit Bus - 32 Mbytes/s Burst

- Up to 16 Bytes Transferred per Burst

- 32-Bit Address Space, 4 Gigabytes

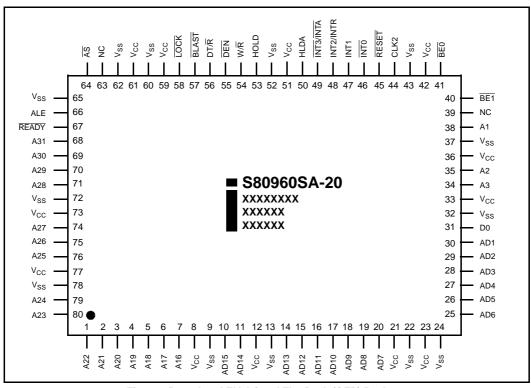

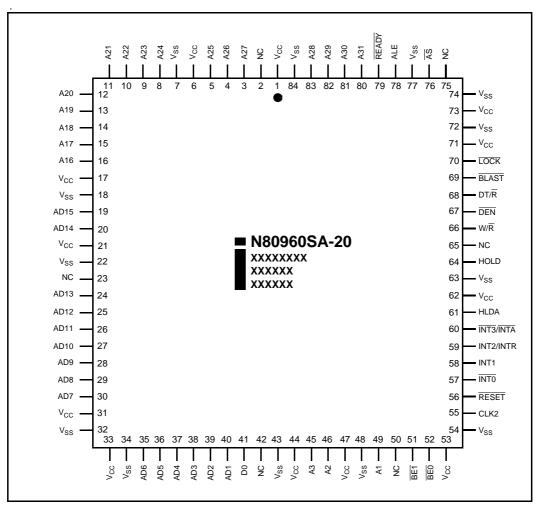

- 80-Lead Quad Flat Pack (EIAJ QFP) 84-Lead Plastic Leaded Chip Carrier (PLCC)

- Software Compatible with 80960KA/KB/CA/CF Processors

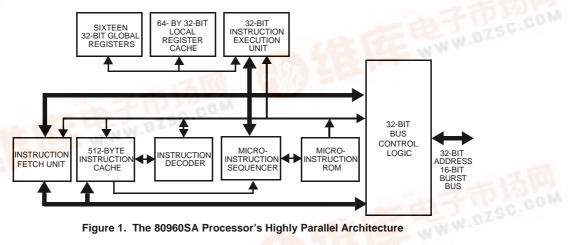

The 80960SA is a member of Intel's i960<sup>®</sup> 32-bit processor family, which is designed especially for low cost embedded applications. It includes a 512-byte instruction cache and a built-in interrupt controller. The 80960SA has a large register set, multiple parallel execution units and a 16-bit burst bus. Using advanced RISC technology, this high performance processor is capable of execution rates in excess of 7.5 million instructions per second. The 80960SA is well-suited for a wide range of cost sensitive embedded applications including non-impact printers, network adapters and I/O controllers.

Figure 1. The 80960SA Processor's Highly Parallel Architecture

Relative to Digital Equipment Corporation's VAX-11/780 at 1 MIPS (VAX-11™ is a trademark of Digital Equipment Corporation)

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied. Information contained herein supersedes previously published specifications on these devices from Intel.

© INTEL CORPORATION, 1993

Order Number: 272206-002

# 80960SA EMBEDDED 32-BIT MICROPROCESSOR WITH 16-BIT BURST DATA BUS

# CONTENTS

### PAGE

| 1.0 | THE i960 <sup>®</sup> PROCESSOR         | 1    |

|-----|-----------------------------------------|------|

|     | 1.1 Key Performance Features            | 2    |

|     | 1.1.1 Memory Space And Addressing Modes | 4    |

|     | 1.1.2 Data Types                        | 4    |

|     | 1.1.3 Large Register Set                | 4    |

|     | 1.1.4 Multiple Register Sets            | 5    |

|     | 1.1.5 Instruction Cache                 | 6    |

|     | 1.1.6 Register Scoreboarding            | 6    |

|     | 1.1.7 High Bandwidth Bus                | 6    |

|     | 1.1.8 Interrupt Handling                | 6    |

|     | 1.1.9 Debug Features                    | 6    |

|     | 1.1.10 Fault Detection                  | 7    |

|     | 1.1.11 Built-in Testability             | 7    |

|     | 1.1.12 CHMOS                            | 7    |

| 2.0 | ELECTRICAL SPECIFICATIONS               | . 11 |

|     | 2.1 Power and Grounding                 | . 11 |

|     | 2.2 Power Decoupling Recommendations    | . 11 |

|     | 2.3 Connection Recommendations          | . 11 |

|     | 2.4 Characteristic Curves               | . 11 |

|     | 2.5 Test Load Circuit                   |      |

|     | 2.6 ABSOLUTE MAXIMUM RATINGS*           | .14  |

|     | 2.7 DC Characteristics                  | .14  |

|     | 2.8 AC Specifications                   |      |

| 3.0 | MECHANICAL DATA                         | .21  |

|     | 3.1 Packaging                           |      |

|     | 3.2 Pin Assignment                      | . 21 |

|     | 3.3 Pinout                              |      |

|     | 3.4 Package Thermal Specifications      | .27  |

|     | 3.5 Stepping Register Information       | .27  |

| 4.0 | WAVEFORMS                               | . 28 |

| 5.0 | REVISION HISTORY                        | .34  |

# int<sub>el</sub>.

| LIST OF F | IGURES                                                                         | PAGE |

|-----------|--------------------------------------------------------------------------------|------|

| Figure 1  | The 80960SA Processor's Highly Parallel Architecture                           | 0    |

| Figure 2  | 80960SA Programming Environment                                                | 1    |

| Figure 3  | Instruction Formats                                                            | 4    |

| Figure 4  | Multiple Register Sets Are Stored On-Chip                                      | 5    |

| Figure 5  | Connection Recommendation for LOCK                                             | 11   |

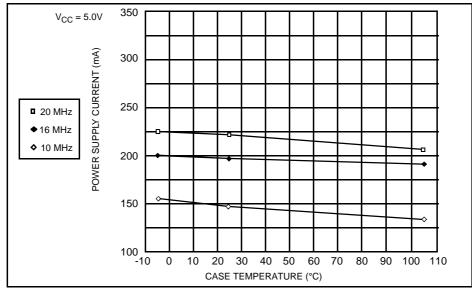

| Figure 6  | Typical Supply Current vs. Case Temperature                                    | 12   |

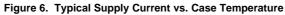

| Figure 7  | Typical Current vs. Frequency (Room Temp)                                      | 12   |

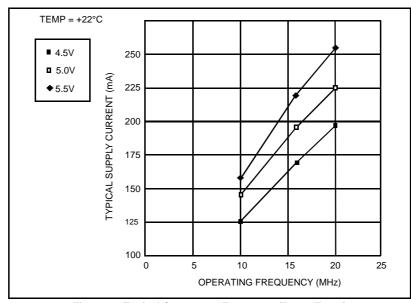

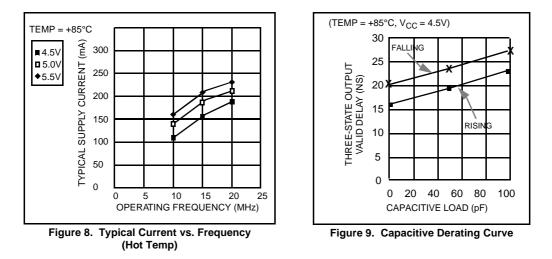

| Figure 8  | Typical Current vs. Frequency (Hot Temp)                                       | 13   |

| Figure 9  | Capacitive Derating Curve                                                      | 13   |

| Figure 10 | Test Load Circuit for Three-State Output Pins                                  | 13   |

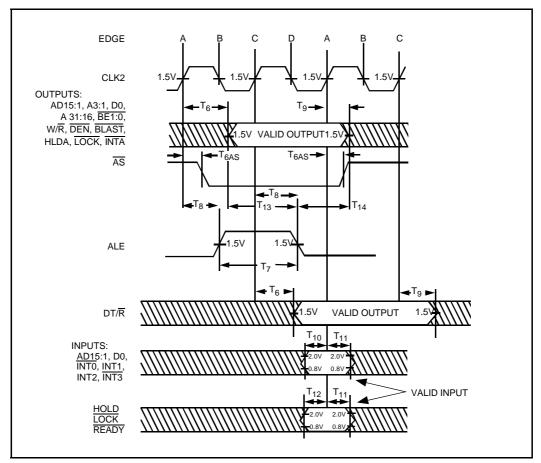

| Figure 11 | Drive Levels and Timing Relationships for 80960SA Signals                      | 15   |

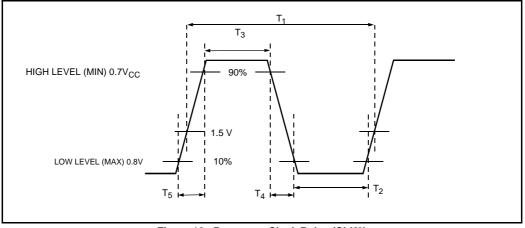

| Figure 12 | Processor Clock Pulse (CLK2)                                                   | 19   |

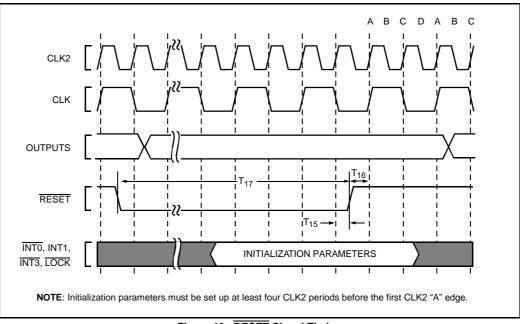

| Figure 13 | RESET Signal Timing                                                            | 19   |

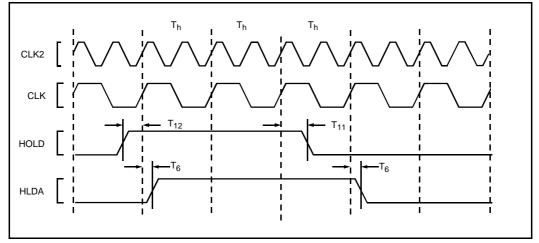

| Figure 14 | HOLD Timing                                                                    | 20   |

| Figure 15 | 80-Lead EIAJ Quad Flat Pack (QFP) Package                                      | 21   |

| Figure 16 | 84-Lead Plastic Leaded Chip Carrier (PLCC) Package                             | 22   |

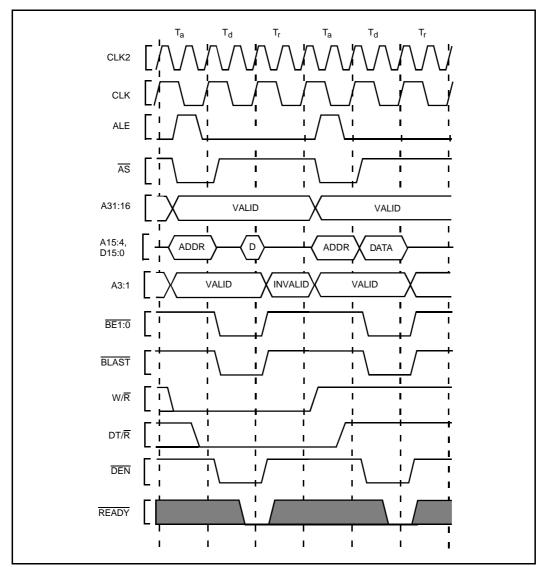

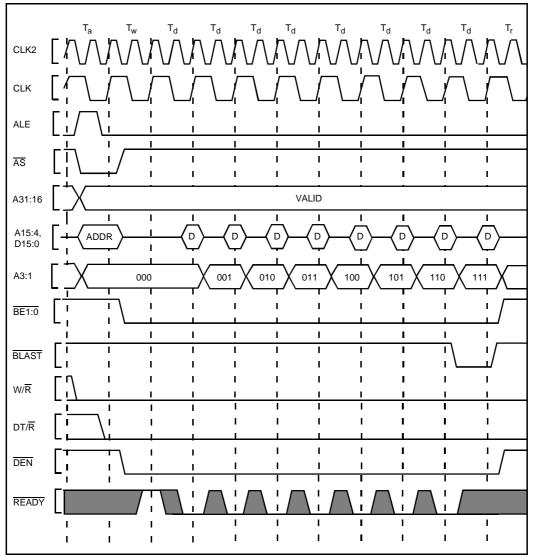

| Figure 17 | Non-Burst Read and Write Transactions Without Wait States                      | 28   |

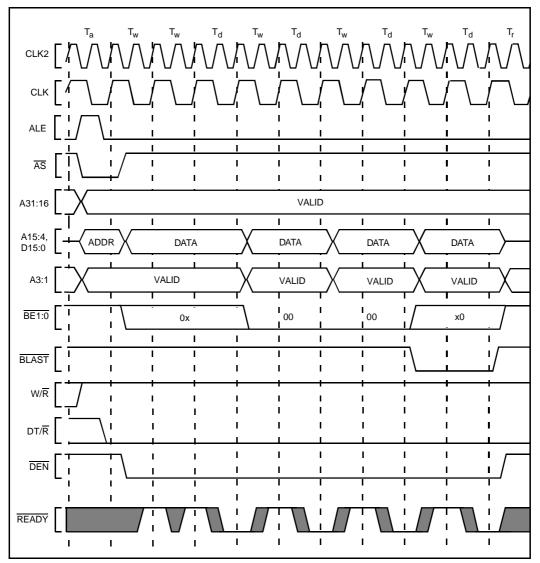

| Figure 18 | Quad Word Burst Read Transaction With 1, 0, 0, 0, 0, 0, 0, 0, 0 Wait States    | 29   |

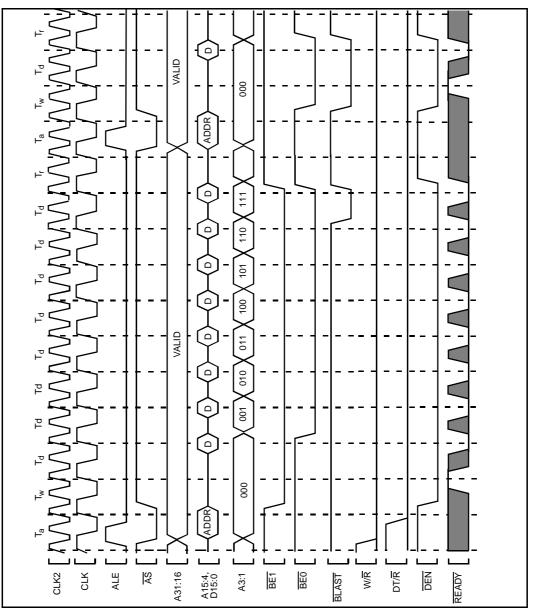

| Figure 19 | Burst Write Transaction With 2, 1, 1, 1 Wait States (6-8 Bytes Transferred)    |      |

| Figure 20 | Accesses Generated by Quad Word Read Bus Request,                              |      |

|           | Misaligned One Byte from Quad Word Boundary 1, 0, 0, 0, 0, 0, 0, 0 Wait States |      |

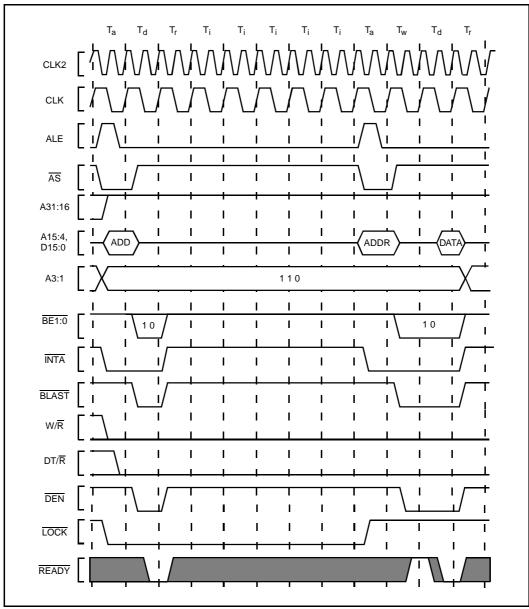

| Figure 21 | Interrupt Acknowledge Cycle                                                    |      |

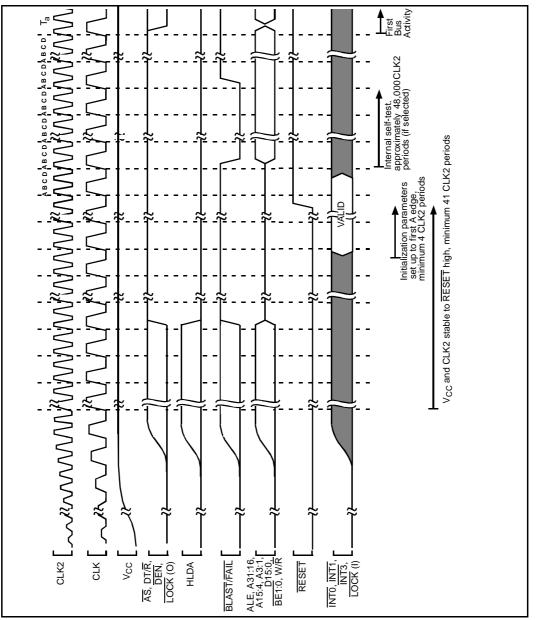

| Figure 22 | Cold Reset Waveform                                                            | 33   |

| LIST OF T | ABLES                                                                          |      |

| Table 1   | 80960SA Instruction Set                                                        | 3    |

| Table 2   | Memory Addressing Modes                                                        | 4    |

| Table 3   | 80960SA Pin Description: Bus Signals                                           | 8    |

| Table 4   | 80960SA Pin Description: Support Signals                                       | 10   |

| Table 5   | DC Characteristics                                                             | 14   |

| Table 6   | 80960SA AC Characteristics (10 MHz)                                            |      |

| Table 7   | 80960SA AC Characteristics (16 MHz)                                            | 17   |

| Table 8   | 80960SA AC Characteristics (20 MHz)                                            | 18   |

| Table 9   | 80960SA QFP Pinout — In Pin Order                                              | 23   |

| Table 10  | 80960SA QFP Pinout — In Signal Order                                           | 24   |

| Table 11  | 80960SA PLCC Pinout — In Pin Order                                             |      |

| Table 12  | 80960SA PLCC Pinout — In Signal Order                                          |      |

| Table 13  | 80960SA QFP Package Thermal Characteristics                                    |      |

| Table 14  | 80960SA PLCC Package Thermal Characteristics                                   |      |

| Table 15  | Die Stepping Cross Reference                                                   | 27   |

# 1.0 THE i960<sup>®</sup> PROCESSOR

The 80960SA is a member of the 32-bit architecture from Intel known as the i960 processor family. These microprocessors were especially designed to serve the needs of embedded applications. The embedded market includes applications as diverse as industrial automation, avionics, image processing, graphics and networking. These types of applications require high integration, low power consumption, quick interrupt response times and high performance. Since time to market is critical, embedded microprocessors need to be easy to use in both hardware and software designs.

All members of the i960 processor family share a common core architecture which utilizes RISC technology so that, except for special functions, the family members are object-code compatible. Each new processor in the family adds its own special set of functions to the core to satisfy the needs of a specific application or range of applications in the embedded market.

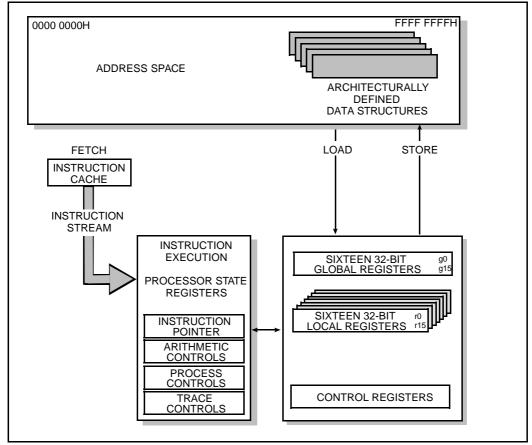

Figure 2. 80960SA Programming Environment

#### 1.1 Key Performance Features

The 80960SA architecture is based on the most recent advances in microprocessor technology and is grounded in Intel's long experience in the design and manufacture of embedded microprocessors. Many features contribute to the 80960SA's exceptional performance:

- Large Register Set. Having a large number of registers reduces the number of times that a processor needs to access memory. Modern compilers can take advantage of this feature to optimize execution speed. For maximum flexibility, the 80960SA provides thirty-two 32-bit registers. (See Figure 2.)

- Fast Instruction Execution. Simple functions make up the bulk of instructions in most programs so that execution speed can be improved by ensuring that these core instructions are executed as quickly as possible. The most frequently executed instructions — such as register-register moves, add/subtract, logical operations and shifts — execute in one to two cycles. (Table 1 contains a list of instructions.)

- 3. Load/Store Architecture. One way to improve execution speed is to reduce the number of times that the processor must access memory to perform an operation. As with other processors based on RISC technology, the 80960SA has a Load/Store architecture. As such, only the LOAD and STORE instructions reference memory; all other instructions operate on registers. This type of architecture simplifies instruction decoding and is used in combination with other techniques to increase parallelism.

- 4. Simple Instruction Formats. All instructions in the 80960SA are 32 bits long and must be aligned on word boundaries. This alignment makes it possible to eliminate the instruction alignment stage in the pipeline. To simplify the instruction decoder, there are only five instruction formats; each instruction uses only one format. (See Figure 3.)

- intel

- 5. Overlapped Instruction Execution. Load operations allow execution of subsequent instructions to continue before the data has been returned from memory, so that these instructions can overlap the load. The 80960SA manages this process transparently to software through the use of a register scoreboard. Conditional instructions also make use of a scoreboard so that subsequent unrelated instructions may be executed while the conditional instruction is pending.

- 6. Integer Execution Optimization. When the result of an arithmetic execution is used as an operand in a subsequent calculation, the value is sent immediately to its destination register. At the same time, the value is put on a bypass path to the ALU, thereby saving the time that otherwise would be required to retrieve the value for the next operation.

- 7. Bandwidth Optimizations. The 80960SA gets optimal use of its memory bus bandwidth because the bus is tuned for use with the on-chip instruction cache: instruction cache line size matches the maximum burst size for instruction fetches. The 80960SA automatically fetches four words in a burst and stores them directly in the cache. Due to the size of the cache and the fact that it is continually filled in anticipation of needed instructions in the program flow, the 80960SA is relatively insensitive to memory wait states. The benefit is that the 80960SA delivers outstanding performance even with a low cost memory system.

- 8. Cache Bypass. If a cache miss occurs, the processor fetches the needed instruction then sends it on to the instruction decoder at the same time it updates the cache. Thus, no extra time is spent to load and read the cache.

## Table 1. 80960SA Instruction Set

| Data Movement         | Arithmetic                    | Logical             | Bit and Bit Field  |

|-----------------------|-------------------------------|---------------------|--------------------|

| Load                  | Add                           | And                 | Set Bit            |

| Store                 | Subtract                      | Not And             | Clear Bit          |

| Move                  | Multiply                      | And Not             | Not Bit            |

| Load Address          | Divide                        | Or                  | Check Bit          |

|                       | Remainder                     | Exclusive Or        | Alter Bit          |

|                       | Modulo                        | Not Or              | Scan For Bit       |

|                       | Shift                         | Or Not              | Scan Over Bit      |

|                       | Extended Multiply             | Nor                 | Extract            |

|                       | Extended Divide               | Exclusive Nor       | Modify             |

|                       |                               | Not                 |                    |

|                       |                               | Nand                |                    |

|                       |                               | Rotate              |                    |

| Comparison            | Branch                        | Call/Return         | Fault              |

| Compare               | Unconditional Branch          | Call                | Conditional Fault  |

| Conditional Compare   | Conditional Branch            | Call Extended       | Synchronize Faults |

| Compare and Increment | Compare and Branch            | Call System         |                    |

| Compare and Decrement |                               | Return              |                    |

|                       |                               | Branch and Link     |                    |

| Debug                 | Miscellaneous                 | Decimal             |                    |

| Modify Trace Controls | Atomic Add                    | Move                |                    |

| Mark                  | Atomic Modify                 | Add with Carry      |                    |

| Force Mark            | Flush Local Registers         | Subtract with Carry |                    |

|                       | Modify Arithmetic<br>Controls |                     |                    |

|                       | Scan Byte for Equal           |                     |                    |

|                       | Test Condition Code           |                     |                    |

| Synchronous           |                               |                     |                    |

| -,                    |                               |                     |                    |

| Synchronous Load      |                               |                     |                    |

# 80960SA

| Control                 | Opcode | e Displacement |         |      |     |              |    |         |  |

|-------------------------|--------|----------------|---------|------|-----|--------------|----|---------|--|

| Compare and<br>Branch   | Opcode | Reg/Lit        | Reg     | М    |     | Displacement |    |         |  |

| Register to<br>Register | Opcode | Reg            | Reg/Lit | Мос  | les | s Ext'd Op   |    | Reg/Lit |  |

| Memory Access<br>Short  | Opcode | Reg            | Base    | М    | Х   | Offset       |    |         |  |

| Memory Access<br>Long   | Opcode | Reg            | Base    | Mode |     | Scale        | хх | Offset  |  |

|                         |        | Displacement   |         |      |     |              |    |         |  |

Figure 3. Instruction Formats

#### 1.1.1 Memory Space And Addressing Modes

The 80960SA offers a linear programming environment so that all programs running on the processor are contained in a single address space. Maximum address space size is 4 Gigabytes ( $2^{32}$  bytes).

For ease of use the 80960SA has a small number of addressing modes, but includes all those necessary to ensure efficient execution of high-level languages such as C. Table 2 lists the memory addressing modes.

#### Table 2. Memory Addressing Modes

- 12-Bit Offset

- 32-Bit Offset

- Register-Indirect

- Register + 12-Bit Offset

- Register + 32-Bit Offset

- Register + (Index-Register x Scale-Factor)

- Register x Scale Factor + 32-Bit Displacement

- Register + (Index-Register x Scale-Factor) + 32-Bit Displacement

Scale-Factor is 1, 2, 4, 8 or 16

#### 1.1.2 Data Types

The 80960SA recognizes the following data types:

Numeric:

- 8-, 16-, 32- and 64-bit ordinals

- 8-, 16-, 32- and 64-bit integers

### Non-Numeric:

- Bit

- Bit Field

- Triple Word (96 bits)

- Quad-Word (128 bits)

#### 1.1.3 Large Register Set

The 80960SA programming environment includes a large number of registers. In fact, 32 registers are available at any time. The availability of this many registers greatly reduces the number of memory accesses required to perform algorithms, which leads to greater instruction processing speed.

There are two types of general-purpose register: local and global. The global registers consist of sixteen 32-bit registers (g0 though g15). These registers perform the same function as the general-

purpose registers provided in other popular microprocessors. The term global refers to the fact that these registers retain their contents across procedure calls.

The local registers, on the other hand, are procedure specific. For each procedure call, the 80960SA allocates 16 local registers (r0 through r15). Each local register is 32 bits wide.

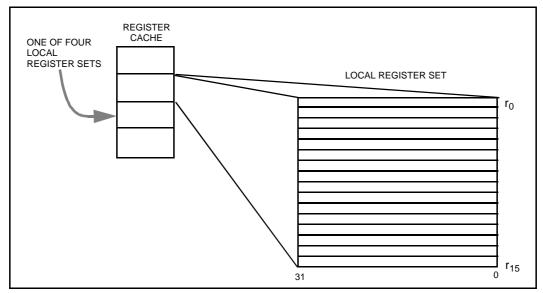

#### 1.1.4 Multiple Register Sets

To further increase the efficiency of the register set, multiple sets of local registers are stored on-chip (See Figure 4). This cache holds up to four local register frames, which means that up to three procedure calls can be made without having to access the procedure stack resident in memory. Although programs may have procedure calls nested many calls deep, a program typically oscillates back and forth between only two to three levels. As a result, with four stack frames in the cache, the probability of having a free frame available on the cache when a call is made is very high. In fact, runs of representative C-language programs show that 80% of the calls are handled without needing to access memory.

If four or more procedures are active and a new procedure is called, the 80960SA moves the oldest local register set in the stack-frame cache to a procedure stack in memory to make room for a new set of registers. Global register g15 is the frame pointer (FP) to the procedure stack.

Global registers are not exchanged on a procedure call, but retain their contents, making them available to all procedures for fast parameter passing.

Figure 4. Multiple Register Sets Are Stored On-Chip

#### 1.1.5 Instruction Cache

To further reduce memory accesses, the 80960SA includes a 512-byte on-chip instruction cache. The instruction cache is based on the concept of locality of reference; most programs are not usually executed in a steady stream but consist of many branches, loops and procedure calls that lead to jumping back and forth in the same small section of code. Thus, by maintaining a block of instructions in cache, the number of memory references required to read instructions into the processor is greatly reduced.

To load the instruction cache, instructions are fetched in 16-byte blocks; up to four instructions can be fetched at one time. An efficient prefetch algorithm increases the probability that an instruction will already be in the cache when it is needed.

Code for small loops often fits entirely within the cache, leading to a great increase in processing speed since further memory references might not be necessary until the program exits the loop. Similarly, when calling short procedures, the code for the calling procedure is likely to remain in the cache so it will be there on the procedure's return.

#### 1.1.6 Register Scoreboarding

The instruction decoder is optimized in several ways. One optimization method is the ability to overlap instructions by using register scoreboarding.

Register scoreboarding occurs when a LOAD moves a variable from memory into a register. When the instruction initiates, a scoreboard bit on the target register is set. Once the register is loaded, the bit is reset. In between, any reference to the register contents is accompanied by a test of the scoreboard bit to ensure that the load has completed before processing continues. Since the processor does not need to wait for the LOAD to complete, it can execute additional instructions placed between the LOAD and the instruction that uses the register contents, as shown in the following example:

> ld data\_2, r4 ld data\_2, r5 Unrelated instruction Unrelated instruction add r4, r5, r6

In essence, the two unrelated instructions between LOAD and ADD are executed "for free" (i.e., take no apparent time to execute) because they are executed while the register is being loaded. Up to three load instructions can be pending at one time with three corresponding scoreboard bits set. By exploiting this feature, system programmers and compiler writers have a useful tool for optimizing execution speed.

#### 1.1.7 High Bandwidth Bus

The 80960SA CPU resides on a high-bandwidth address/data bus. The bus provides a direct communication path between the processor and the memory and I/O subsystem interfaces. The processor uses the bus to fetch instructions, manipulate memory and respond to interrupts. Bus features include:

- 16-bit data path multiplexed onto the lower bits of the 32-bit address path

- Eight 16-bit half-word burst capability which allows transfers from 1 to 16 bytes at a time

- High bandwidth reads and writes with 32 Mbytes/s burst (at 20 MHz)

Table 3 defines bus signal names and functions; Table 4 defines other component-support signals such as interrupt lines.

#### 1.1.8 Interrupt Handling

The 80960SA can be interrupted in one of two ways: by the activation of one of four interrupt pins or by sending a message on the processor's data bus.

The 80960SA is unusual in that it automatically handles interrupts on a priority basis and can keep track of pending interrupts through its on-chip interrupt controller. Two of the interrupt pins can be configured to provide 8259A-style handshaking for expansion beyond four interrupt lines.

#### 1.1.9 Debug Features

The 80960SA has built-in debug capabilities. There are two types of breakpoints and six trace modes. Debug features are controlled by two internal 32-bit registers, the Process-Controls Word and the Trace-Controls Word. By setting bits in these control words, a software debug monitor can closely control how the processor responds during program execution.

# intel

The 80960SA provides two hardware breakpoint registers on-chip which, by using a special command, can be set to any value. When the instruction pointer matches either breakpoint register value, the breakpoint handling routine is automatically called.

The 80960SA also provides software breakpoints through the use of two instructions: MARK and FMARK. These can be placed at any point in a program and cause the processor to halt execution at that point and call the breakpoint handling routine. The breakpoint mechanism is easy to use and provides a powerful debugging tool.

Tracing is available for instructions (single step execution), calls and returns and branching. Each trace type may be enabled separately by a special debug instruction. In each case, the 80960SA executes the instruction first and then calls a trace handling routine (usually part of a software debug monitor). Further program execution is halted until the routine completes, at which time execution resumes at the next instruction. The 80960SA's tracing mechanisms, implemented completely in hardware, greatly simplify the task of software test and debug.

#### 1.1.10 Fault Detection

The 80960SA has an automatic mechanism to handle faults. Fault types include trace and arithmetic faults. When the processor detects a fault, it automatically calls the appropriate fault handling routine and saves the current instruction pointer and necessary state information to make efficient recovery possible. Like interrupt handling routines, fault handling routines are usually written to meet the needs of specific applications and are often included as part of the operating system or kernel. For each of the fault types, there are numerous subtypes that provide specific information about a fault. The fault handler can use this specific information to respond correctly to the fault.

#### 1.1.11 Built-in Testability

Upon reset, the 80960SA automatically conducts an exhaustive internal test of its major blocks of logic. Then, before executing its first instruction, it does a zero check sum on the first eight words in memory to ensure that the memory image was programmed correctly. If a problem is discovered at an<u>y point</u> during the self-test, the 80960SA asserts its FAIL pin and will not begin program execution. Self test takes approximately 24,000 cycles to complete.

System manufacturers can use the 80960SA's selftest feature during incoming parts inspection. No special diagnostic programs need to be written. The test is both thorough and fast. The self-test capability helps ensure that defective parts are discovered before systems are shipped and, once in the field, the self-test makes it easier to distinguish between problems caused by processor failure and problems resulting from other causes.

#### 1.1.12 CHMOS

The 80960SA is fabricated using Intel's CHMOS IV (Complementary High Speed Metal Oxide Semiconductor) process. The 80960SA is available at 10 and 16 MHz in the QFP package and at 10, 16 and 20 MHz in the PLCC package.

#### NAME TYPE DESCRIPTION CLK2 SYSTEM CLOCK provides the fundamental timing for 80960SA systems. It is I divided by two inside the 80960SA to generate the internal processor clock. A31:16 ο ADDRESS BUS carries the upper 16 bits of the 32-bit physical address to memory. T.S. It is valid throughout the burst cycle; no latch is required. AD15:1, D0 I/O ADDRESS/DATA BUS carries the low order 32-bit addresses and 16-bit data to and from memory. AD15:4 must be latched since the cycle following the address T.S. cvcle carries data on the bus. A3:1 ο ADDRESS BUS carries the word addresses of the 32-bit address to memory. T.S. These three bits are incremented during a burst access indicating the next word address of the burst access. Note that A3:1 are duplicated with AD3:1 during the address cycle. ALE ο ADDRESS LATCH ENABLE indicates the transfer of a physical address. ALE is T.S. asserted during a T<sub>a</sub> cycle and deasserted before the beginning of the T<sub>d</sub> state. It is active HIGH and floats to a high impedance state during a hold cycle (T<sub>h</sub>). **ADDRESS STATUS** indicates an address state. $\overline{AS}$ is asserted every $T_a$ state and deasserted during the following $T_d$ state. $\overline{AS}$ is driven HIGH during reset. AS ο T.S. W/R ο WRITE/READ specifies, during a Ta cycle, whether the operation is a write or read. It is latched on-chip and remains valid during T<sub>d</sub> cycles. T.S. **DATA ENABLE** is asserted during $T_d$ cycles and indicates transfer of data on the AD lines. The AD lines should not be driven by an external source unless DEN is DEN 0 T.S. asserted. When $\overline{\text{DEN}}$ is asserted, outputs from the previous cycle are guaranteed to be three-stated. In addition, DEN deasserted indicates inputs have been captured; therefore input hold times can be disregarded. DEN is driven HIGH during reset. DT/R DATA TRANSMIT / RECEIVE indicates the direction of data transfer to and from 0 T.S. the bus. It is low during $T_a$ and $T_d$ cycles for a read or interrupt acknowledgment; it is high during $\underline{T}_a$ and $\overline{T}_d$ cycles for a write. $DT/\overline{R}$ never changes state when $\overline{DEN}$ is asserted. DT/R is driven HIGH during reset. READY READY indicates that data on AD lines can be sampled or removed. If READY is Т not asserted during a $T_d$ cycle, the $T_d$ cycle is extended to the next cycle by inserting a wait state $(T_w)$ .

#### Table 3. 80960SA Pin Description: Bus Signals (Sheet 1 of 2)

Inte

I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state

# 80960SA

| NAME       | TYPE               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOCK       | <b>I/O</b><br>O.D. | BUS LOCK prevents bus masters from gaining control of the bus during<br>Read/Modify/Write (RMW) cycles. The processor or any bus agent may assert<br>LOCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            |                    | At the start of a RMW operation, the processor examines the $\overline{\text{LOCK}}$ pin. If the pin is already asserted, the processor <u>waits</u> until it is not asserted. If the pin is not asserted, the processor asserts $\overline{\text{LOCK}}$ during the T <sub>a</sub> cycle of the read transaction.                                                                                                                                                                                                                                                                                                                             |

|            |                    | The processor deasserts $\overline{\text{LOCK}}$ in the $T_a$ cycle of the write transaction. While $\overline{\text{LOCK}}$ is asserted, a bus agent can perform a normal read or write but not a RMW operation. The processor also asserts $\overline{\text{LOCK}}$ during interrupt-acknowledge transactions.                                                                                                                                                                                                                                                                                                                               |

|            |                    | Do not leave LOCK unconnected. It must be pulled high for the processor to function properly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            |                    | <b>ONCE MODE</b> : The $\overline{\text{LOCK}}$ pin is sampled during reset. If it is asserted LOW at the end of reset, all outputs will be three-stated until the part is reset again. ONCE mode is used in conjunction with an in-circuit emulator.                                                                                                                                                                                                                                                                                                                                                                                          |

| BE1:0      | <b>0</b><br>T.S.   | BYTE ENABLE LINES specify which data bytes (up to two) on the bus take part in the current bus cycle. BE1 corresponds to AD15:8; BE0 corresponds to AD7:1, D0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            |                    | The byte enable lines are asserted appropriately during each data cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            |                    | <b>INITIALIZATION FAILURE</b> indicates that the processor has failed to initialize correctly. The failure state is indicated by a combination of BLAST asserted and BE1:0 not asserted. This condition occurs after RESET is deasserted and before the first bus transaction begins. FAIL is asserted while the processor performs a self-test. If the self-test completes successfully, FAIL is deasserted. The processor then performs a zero checksum on the first eight words of memory, If it fails, FAIL is asserted for a second time and remains asserted; if it passes, system initialization continues and FAIL remains deasserted. |

| HOLD       | I                  | <b>HOLD</b> indicates a request from an external bus master to acquire the bus. When the processor receives HOLD and grants bus control to another master, it floats its three-state bus lines, then asserts HLDA and enters the $T_h$ state. When HOLD is deasserted, the processor deasserts HLDA and enters the $T_i$ or $T_a$ state.                                                                                                                                                                                                                                                                                                       |

| HLDA       | <b>0</b><br>T.S.   | HOLD ACKNOWLEDGE notifies an external bus master that the processor has relinquished control of the bus. This signal is always driven. At reset it is driven LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BLAST/FAIL | <b>0</b><br>T.S.   | <b>BURST LAST</b> indicates the last data cycle ( $T_d$ ) of a burst access. It is asserted low during the last $T_d$ and associated with $T_w$ cycles in a burst access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            |                    | <b>INITIALIZATION FAILURE</b> indicates that the processor has failed to initialize correctly. The failure state is indicated by a combination of BLAST asserted and BE1:0 not asserted. This condition occurs after RESET is deasserted and before the first bus transaction begins. FAIL is asserted while the processor performs a self-test. If the self-test completes successfully, FAIL is deasserted. The processor then performs a zero checksum on the first eight words of memory, If it fails, FAIL is asserted for a second time and remains asserted; if it passes, system initialization continues and FAIL remains deasserted. |

# Table 3. 80960SA Pin Description: Bus Signals (Sheet 2 of 2)

I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state

# 80960SA

# Table 4. 80960SA Pin Description: Support Signals

| NAME      | TYPE               |                                                                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                         |                                                                                  |                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|-----------|--------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| RESET     | I                  | RESET c                                                                                 | RESET clears the processor's internal logic and causes it to reinitialize.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                         |                                                                                  |                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|           |                    | LOCK), tl<br>for DT/R,<br>states.<br>RESET n<br>Optionally<br>should of                 | During RESET assertion, the input pins are ignored (except for INT0, INT1, INT3, LOCK), the three-state output pins are placed in a HIGH impedance state (except for DT/R, DEN, and AS) and other output pins are placed in their non-asserted states.<br>RESET must be asserted for at least 41 CLK2 cycles for a predictable reset.<br>Optionally, for a synchronous reset, the LOW and HIGH transition of RESET should occur after the rising edge of both CLK2 and the external bus CLK and before the next rising edge of CLK2. |                                                                                                         |                                                                                  |                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|           |                    | The inter                                                                               | rupt pins indic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ate the initiali                                                                                        | zation sequ                                                                      | uence executed. Typical initial-<br>a HIGH state. The reset conditions                                                                                                                                                                          |  |  |  |  |  |  |

|           |                    | INT0                                                                                    | INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | INT3                                                                                                    | LOCK                                                                             | Action Taken                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|           |                    | 1                                                                                       | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                       | 1                                                                                | Run self test (core initialization)                                                                                                                                                                                                             |  |  |  |  |  |  |

|           |                    | 0                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                       | 1                                                                                | Disable self-test                                                                                                                                                                                                                               |  |  |  |  |  |  |

|           |                    | 0                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | х                                                                                                       | х                                                                                | Reserved                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|           |                    | х                                                                                       | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                       | х                                                                                | Reserved                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|           |                    | х                                                                                       | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | х                                                                                                       | 0                                                                                | ONCE mode (see LOCK pin)                                                                                                                                                                                                                        |  |  |  |  |  |  |

| ΪΝΤΟ      | I                  | synchron<br>enabled b<br>least one<br>deasserte<br>more sys<br>an interru<br>INT0 is sa | ous system, t<br>by being deas<br>additional bu<br>ed for at least<br>tem clock cyc<br>upt vector befo<br>ampled during                                                                                                                                                                                                                                                                                                                                                                                                              | his pin — as<br>serted for at l<br>is cycle. In an<br>two system c<br>les. The intern<br>ore using this | well as the<br>least one bu<br>asynchron<br>clock cycles<br>rupt control<br>pin. | o signal an interrupt in a<br>other interrupt pins — must be<br>us cycle and then asserted for at<br>ous system, the pin must remain<br>and then asserted for at least two<br>register must be programmed with<br>e self-test sequence is to be |  |  |  |  |  |  |

|           |                    | executed                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                         |                                                                                  |                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| INT1      | 1                  |                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                         |                                                                                  | upt signaling. INT1 is sampled<br>ice is to be executed.                                                                                                                                                                                        |  |  |  |  |  |  |

| INT2/INTR | I                  | how this<br>INT1 pins                                                                   | <b>INTERRUPT2/INTERRUPT REQUEST</b> : The interrupt control register determines how this pin is interpreted. If INT2, it has the same interpretation as the INT0 and INT1 pins. If INTR, it is used to receive an interrupt request from an external interrupt controller.                                                                                                                                                                                                                                                           |                                                                                                         |                                                                                  |                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| INT3/INTA | <b>I/O</b><br>T.S. | determine<br>the INT0<br>acknowle                                                       | <b>INTERRUPT3/INTERRUPT ACKNOWLEDGE</b> : The interrupt control register determines how this pin is interpreted. If INT3, it has the same interpretation as the INT0 and INT1 pins. If INTA, it is used as an output to control interrupt acknowledge transactions. The INTA output is latched on-chip and remains valid during $T_d$ cycles; as an output, it is open-drain. INT3 must be pulled HIGH during                                                                                                                        |                                                                                                         |                                                                                  |                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| NC        | N/A                | pin marke                                                                               | ed NC; these                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | dicates pins s<br>pins may be r                                                                         | eserved for                                                                      | e connected. Never connect any<br>r factory use.                                                                                                                                                                                                |  |  |  |  |  |  |

I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state

### 2.0 ELECTRICAL SPECIFICATIONS

### 2.1 Power and Grounding

The 80960SA is implemented in CHMOS IV technology and therefore has modest power requirements. Its high clock frequency and numerous output buffers (address/data, control, error and arbitration signals) can cause power surges as multiple output buffers simultaneously drive new signal levels. For clean on-chip power distribution,  $V_{CC}$  and  $V_{SS}$  pins separately feed the device's functional units. Power and ground connections must be made to all 80960SA power and ground pins. On the circuit board, all  $V_{CC}$  pins must be strapped closely together, preferably on a power plane; all  $V_{SS}$  pins should be strapped together, preferably on a ground plane.

### 2.2 Power Decoupling Recommendations

Place a liberal amount of decoupling capacitance near the 80960SA. When driving the bus the processor can cause transient power surges, particularly when connected to a large capacitive load.

Low inductance capacitors and interconnects are recommended for best high frequency electrical performance. Inductance is reduced by shortening board traces between the processor and decoupling capacitors as much as possible.

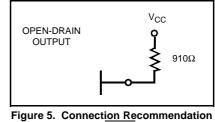

### 2.3 Connection Recommendations

For reliable operation, always connect unused inputs to an appropriate signal level. In particular, if one or more interrupt lines are not used, they should be pulled up. No inputs should ever be left floating. The LOCK open-drain pin requires a pullup resistor whether or not the pin is used as an output. Figure 5 shows the recommended resistor value.

Do not connect external logic to pins marked NC.

for LOCK

### 2.4 Characteristic Curves

Figure 6 shows typical supply current requirements over the operating temperature range of the processor at supply voltage ( $V_{CC}$ ) of 5V. Figure 7 shows the typical power supply current ( $I_{CC}$ ) that the 80960SA requires at various operating frequencies when measured at three input voltage ( $V_{CC}$ ) levels.

For a given output current ( $I_{OL}$ ) the curve in Figure 8 shows the worst case output low voltage ( $V_{OL}$ ). Figure 9 shows the typical capacitive derating curve for the 80960SA measured from 1.5V on the system clock (CLK) to 0.8V on the falling edge and 2.0V on the rising edge of the bus address/data (AD) signals.

Figure 7. Typical Current vs. Frequency (Room Temp)

#### 80960SA

### 2.5 Test Load Circuit

Figure 10 illustrates the load circuit used to test the 80960SA's output pins.

Figure 10. Test Load Circuit for Three-State Output Pins

# intel

### 2.6 ABSOLUTE MAXIMUM RATINGS\*

| Parameter                  | Maximum Rating        |

|----------------------------|-----------------------|

| Operating Temperature (PL  | CC) 0°C to +85°C Case |

| Operating Temperature (QF  | P) 0°C to +100°C Case |

| Storage Temperature        | –65°C to +150°C       |

| Voltage on Any Pin (PLCC). | 0.5V to VCC +0.5V     |

| Voltage on Any Pin (QFP)   | -0.25V to VCC +0.25V  |

| Power Dissipation          | 1.9W (20 MHz)         |

**NOTICE**: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### 2.7 DC Characteristics

80960SA (10 and 16 MHz QFP) 80960SA (10 and 16 MHz PLCC) 80960SA (20 MHz PLCC)

$$\begin{split} T_{CASE} &= 0^{\circ}C \text{ to } + 100^{\circ}C, \ V_{CC} = 5V \pm 5\% \\ T_{CASE} &= 0^{\circ}C \text{ to } + 85^{\circ}C, \ V_{CC} = 5V \pm 10\% \\ T_{CASE} &= 0^{\circ}C \text{ to } + 85^{\circ}C, \ V_{CC} = 5V \pm 5\% \end{split}$$

Table 5. DC Characteristics

| Symbol           | Parameter                                                                        | Min                 | Max                      | Units                | Notes                                                                        |

|------------------|----------------------------------------------------------------------------------|---------------------|--------------------------|----------------------|------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                                                | -0.3                | +0.8                     | V                    |                                                                              |

| V <sub>IH</sub>  | Input High Voltage                                                               | 2.0                 | V <sub>CC</sub> + 0.3    | V                    |                                                                              |

| V <sub>CL</sub>  | CLK2 Input Low Voltage                                                           | -0.3                | +0.8                     | V                    |                                                                              |

| V <sub>CH</sub>  | CLK2 Input High Voltage                                                          | 0.7 V <sub>CC</sub> | V <sub>CC</sub> + 0.3    | V                    |                                                                              |

| V <sub>OL</sub>  | Output Low Voltage                                                               |                     | 0.45                     | V                    | I <sub>OL</sub> = 4.0 mA                                                     |

|                  |                                                                                  |                     | 0.45                     | V                    | $I_{OL} = 6 \text{ mA}, \overline{\text{LOCK}} \text{ Pin}$                  |

| V <sub>OH</sub>  | Output High Voltage                                                              | 2.4                 |                          | V                    | All TS, -2.5 mA (1)                                                          |

| I <sub>CC</sub>  | Power Supply Current:<br>10 MHz-QFP<br>10 MHz-PLCC<br>16 MHz-PLCC<br>20 MHz-PLCC |                     | 240<br>240<br>300<br>340 | mA<br>mA<br>mA<br>mA | $T_{CASE} = 0°C$<br>$T_{CASE} = 0°C$<br>$T_{CASE} = 0°C$<br>$T_{CASE} = 0°C$ |

| I <sub>LI1</sub> | Input Leakage Current,<br>Except INT0, LOCK                                      |                     | ±15                      | μA                   | $0 \leq V_{IN} \leq V_{CC}$                                                  |

| I <sub>LI2</sub> | Input Leakage Current,<br>INT0, LOCK                                             |                     | -300                     | μA                   | V <sub>IN</sub> = 0.45V (2)                                                  |

| I <sub>OL</sub>  | Output Leakage Current                                                           |                     | ±15                      | μA                   |                                                                              |

| C <sub>IN</sub>  | Input Capacitance                                                                |                     | 10                       | pF                   | f <sub>C</sub> = 1 MHz (3)                                                   |

| Co               | Output Capacitance                                                               |                     | 12                       | pF                   | f <sub>C</sub> = 1 MHz (3)                                                   |

| C <sub>CLK</sub> | Clock Capacitance                                                                |                     | 10                       | pF                   | f <sub>C</sub> = 1 MHz (3)                                                   |

NOTES:

1. Not measured for open-drain output.

2.  $\overline{\text{INT0}} \text{ and } \overline{\text{LOCK}} \text{ have internal pullup devices.}$

3. Input, output and clock capacitance are not tested.

### 80960SA

# 2.8 AC Specifications

This section describes the AC specifications for the 80960SA pins. All input and output timings are specified relative to the 1.5V level of the rising edge of CLK2 and refer to the time at which the signal

crosses 1.5V (for output delay and input setup). All AC testing should be done with input voltages of 0.4V and 2.4V, except for the clock (CLK2) which should be tested with input voltages of 0.45V and 0.7 x V<sub>CC</sub>. See Figure 11 and Tables 6, 7 and 8 for timing relationships for the 80960SA signals.

Figure 11. Drive Levels and Timing Relationships for 80960SA Signals

# intel

| Symbol           | Parameter                        |                     | Max | Units | Notes                                     |

|------------------|----------------------------------|---------------------|-----|-------|-------------------------------------------|

| Input Clo        | ck                               |                     |     |       |                                           |

| T <sub>1</sub>   | Processor Clock Period (CLK2)    | 50                  | 125 | ns    | V <sub>IN</sub> = 1.5V                    |

| T <sub>2</sub>   | Processor Clock Low Time (CLK2)  | 8                   |     | ns    | V <sub>T</sub> = 10% Point                |

|                  |                                  |                     |     |       | $= V_{CL} + (V_{CH} - V_{CL}) \times 0.1$ |

| T <sub>3</sub>   | Processor Clock High Time        | 8                   |     | ns    | $V_T = 90\%$ Point                        |

|                  | (CLK2)                           |                     |     |       | $= V_{CL} + (V_{CH} - V_{CL}) \times 0.9$ |

| T <sub>4</sub>   | Processor Clock Fall Time (CLK2) |                     | 10  | ns    | $V_{T} = 90\%$ to 10% Point (1)           |

| Т <sub>5</sub>   | Processor Clock Rise Time (CLK2) |                     | 10  | ns    | $V_{T}$ = 10% to 90% Point (1)            |

| Synchron         | ous Outputs                      |                     |     |       |                                           |

| T <sub>6</sub>   | Output Valid Delay               | 2                   | 31  | ns    |                                           |

| T <sub>6AS</sub> | AS Output Valid Delay            | 2                   | 25  | ns    |                                           |

| T <sub>7</sub>   | ALE Width                        | T <sub>1</sub> - 11 |     | ns    |                                           |

| Т <sub>8</sub>   | ALE Output Valid Delay           | 4                   | 33  | ns    |                                           |

| T <sub>9</sub>   | Output Float Delay               | 2                   | 20  | ns    | (2)                                       |

| Synchron         | ious Inputs                      |                     |     |       |                                           |

| T <sub>10</sub>  | Input Setup 1                    | 10                  |     | ns    |                                           |

| T <sub>11</sub>  | Input Hold                       | 2                   |     | ns    |                                           |

| T <sub>12</sub>  | Input Setup 2                    | 13                  |     | ns    |                                           |

| T <sub>13</sub>  | Setup to ALE Inactive            | 10                  |     | ns    |                                           |

| T <sub>14</sub>  | Hold after ALE Inactive          | 8                   |     | ns    |                                           |

| T <sub>15</sub>  | RESET Hold                       | 3                   |     | ns    | (3)                                       |

| T <sub>16</sub>  | RESET Setup                      | 5                   |     | ns    | (3)                                       |

| T <sub>17</sub>  | RESET Width                      | 2050                |     | ns    | 41 CLK2 Periods Minimum                   |

### Table 6. 80960SA AC Characteristics (10 MHz)

NOTES:

1. Processor clock (CLK2) rise time and fall time are not tested.

2. A float condition occurs when the maximum output current becomes less than I<sub>LO</sub>. Float delay is not tested, but should be no longer than the valid delay.

Meeting RESET setup and hold times is an optional method of synchronizing your clocks. If you decide to use an asynchronous reset, synchronizing the clock can be accomplished by using AS.

### 80960SA

| Symbol           | Parameter                        | Min                 | Max | Units | Notes                                     |

|------------------|----------------------------------|---------------------|-----|-------|-------------------------------------------|

| Input Cloc       | :k                               |                     |     |       |                                           |

| T <sub>1</sub>   | Processor Clock Period (CLK2)    | 31.25               | 125 | ns    | V <sub>IN</sub> = 1.5V                    |

| T <sub>2</sub>   | Processor Clock Low Time (CLK2)  | 8                   |     | ns    | $V_{T} = 10\%$ Point                      |

|                  |                                  |                     |     |       | $= V_{CL} + (V_{CH} - V_{CL}) \times 0.1$ |

| T <sub>3</sub>   | Processor Clock High Time        | 8                   |     | ns    | $V_T = 90\%$ Point                        |

|                  | (CLK2)                           |                     |     |       | $= V_{CL} + (V_{CH} - V_{CL}) \times 0.9$ |

| T <sub>4</sub>   | Processor Clock Fall Time (CLK2) |                     | 10  | ns    | $V_{T} = 90\%$ to 10% Point (1)           |

| Т <sub>5</sub>   | Processor Clock Rise Time (CLK2) |                     | 10  | ns    | $V_{T} = 10\%$ to 90% Point (1)           |

| Synchron         | ous Outputs                      |                     |     |       |                                           |

| Т <sub>6</sub>   | Output Valid Delay               | 2                   | 25  | ns    |                                           |

| T <sub>6AS</sub> | AS Output Valid Delay            | 2                   | 21  | ns    |                                           |

| T <sub>7</sub>   | ALE Width                        | T <sub>1</sub> - 11 |     | ns    |                                           |

| T <sub>8</sub>   | ALE Output Valid Delay           | 2                   | 22  | ns    |                                           |

| Т <sub>9</sub>   | Output Float Delay               | 2                   | 20  | ns    | (2)                                       |

| Synchron         | ous Inputs                       |                     |     |       |                                           |

| T <sub>10</sub>  | Input Setup 1                    | 10                  |     | ns    |                                           |

| T <sub>11</sub>  | Input Hold                       | 2                   |     | ns    |                                           |

| T <sub>12</sub>  | Input Setup 2                    | 13                  |     | ns    |                                           |

| T <sub>13</sub>  | Setup to ALE Inactive            | 10                  |     | ns    |                                           |

| T <sub>14</sub>  | Hold after ALE Inactive          | 8                   |     | ns    |                                           |

| T <sub>15</sub>  | RESET Hold                       | 3                   |     | ns    | (3)                                       |

| T <sub>16</sub>  | RESET Setup                      | 5                   |     | ns    | (3)                                       |

| T <sub>17</sub>  | RESET Width                      | 1281                |     | ns    | 41 CLK2 Periods Minimum                   |

### Table 7. 80960SA AC Characteristics (16 MHz)

NOTES:

1. Processor clock (CLK2) rise time and fall time are not tested.

2. A float condition occurs when the maximum output current becomes less than I<sub>LO</sub>. Float delay is not tested, but should be no longer than the valid delay.

Meeting RESET setup and hold times is an optional method of synchronizing your clocks. If you decide to use an asynchronous reset, synchronizing the clock can be accomplished by using AS.

# intel

| Symbol           | Parameter                        | Min                 | Max | Units | Notes                                     |

|------------------|----------------------------------|---------------------|-----|-------|-------------------------------------------|

| Input Cloc       | :k                               |                     |     |       |                                           |

| T <sub>1</sub>   | Processor Clock Period (CLK2)    | 25                  | 125 | ns    | V <sub>IN</sub> = 1.5V                    |

| T <sub>2</sub>   | Processor Clock Low Time (CLK2)  | 6                   |     | ns    | $V_{T} = 10\%$ Point                      |

|                  |                                  |                     |     |       | $= V_{CL} + (V_{CH} - V_{CL}) \times 0.1$ |

| T <sub>3</sub>   | Processor Clock High Time (CLK2) | 6                   |     | ns    | $V_T = 90\%$ Point                        |

|                  |                                  |                     |     |       | $= V_{CL} + (V_{CH} - V_{CL}) \times 0.9$ |

| T <sub>4</sub>   | Processor Clock Fall Time (CLK2) |                     | 10  | ns    | $V_{T} = 90\%$ to 10% Point (1)           |

| T <sub>5</sub>   | Processor Clock Rise Time (CLK2) |                     | 10  | ns    | $V_{T}$ = 10% to 90% Point (1)            |

| Synchron         | ous Outputs                      |                     |     |       |                                           |

| T <sub>6</sub>   | Output Valid Delay               | 2                   | 20  | ns    |                                           |

| T <sub>6AS</sub> | AS Output Valid Delay            | 2                   | 20  | ns    |                                           |

| T <sub>7</sub>   | ALE Width                        | T <sub>1</sub> - 11 |     | ns    |                                           |

| T <sub>8</sub>   | ALE Output Valid Delay           | 2                   | 18  | ns    |                                           |

| T <sub>9</sub>   | Output Float Delay               | 2                   | 17  | ns    | (2)                                       |

| Synchron         | ous Inputs                       |                     |     |       |                                           |

| T <sub>10</sub>  | Input Setup 1                    | 7                   |     | ns    |                                           |

| T <sub>11</sub>  | Input Hold                       | 2                   |     | ns    |                                           |

| T <sub>12</sub>  | Input Setup 2                    | 13                  |     | ns    |                                           |

| T <sub>13</sub>  | Setup to ALE Inactive            | 10                  |     | ns    |                                           |

| T <sub>14</sub>  | Hold after ALE Inactive          | 8                   |     | ns    |                                           |

| T <sub>15</sub>  | RESET Hold                       | 3                   |     | ns    | (3)                                       |

| T <sub>16</sub>  | RESET Setup                      | 5                   |     | ns    | (3)                                       |

| T <sub>17</sub>  | RESET Width                      | 1025                |     | ns    | 41 CLK2 Periods Minimum                   |

### Table 8. 80960SA AC Characteristics (20 MHz)

NOTES:

1. Processor clock (CLK2) rise time and fall time are not tested.

2. A float condition occurs when the maximum output current becomes less than I<sub>LO</sub>. Float delay is not tested, but should be no longer than the valid delay.