#### 查询80C152JA供应商

### 捷多邦,专业PCB打样工厂,24小时加急出货

PRELIMINARY

### 8XC152JA/JB/JC/JD UNIVERSAL COMMUNICATION CONTROLLER 8-BIT MICROCONTROLLER

- 8K Factory Mask Programmable ROM Available

- Superset of 80C51 Architecture

- Multi-Protocol Serial Communication I/O Port (2.048 Mbps/2.4 Mbps Max) ODI 2 (2018 Option 2018)

- SDLC/HDLC Only

- CSMA/CD and SDLC/HDLC - User Definable Protocols

- Full Duplex/Half Duplex

- MCS®-51 Compatible UART

- 16.5 MHz Maximum Clock Frequency

- Multiple Power Conservation Modes

- 64KB Program Memory Addressing

- 64KB Data Memory Addressing

- 256 Bytes On-Chip RAM

- Dual On-Chip DMA Channels

- Hold/Hold Acknowledge

- Two General Purpose Timer/Counters

- 5 or 7 I/O Ports

- 56 Special Function Registers

- 11 Interrupt Sources

- Available in 48 Pin Dual-in-Line Package and 68 Pin Surface Mount PLCC Package

(See Packaging Spec. Order #231369)

The 80C152, which is based on the MCS®-51 CPU, is a highly integrated single-chip 8-bit microcontroller designed for cost-sensitive, high-speed, serial communications. It is well suited for implementing Integrated Services Digital Networks (ISDN), emerging Local Area Networks, and user defined serial backplane applications. In addition to the multi-protocol communication capability, the 80C152 offers traditional microcontroller features for peripheral I/O interface and control.

Silicon implementations are much more cost effective than multi-wire cables found in board level parallel-toserial and serial-to-parallel converters. The 83C152 contains, in silicon, all the features needed for the serialto-parallel conversion. Other 83C152 benefits include: 1) better noise immunity through differential signaling or fiber optic connections, 2) data integrity utilizing the standard, designed in CRC checks, and 3) better modularity of hardware and software designs. All of these—cost, network parameter and real estate improvements apply to 83C152 serial links between boards or systems and 83C152 serial links on a single board.

## intel

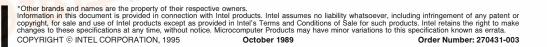

**Figure 1. Connection Diagrams**

8XC152JA/JB/JC/JD

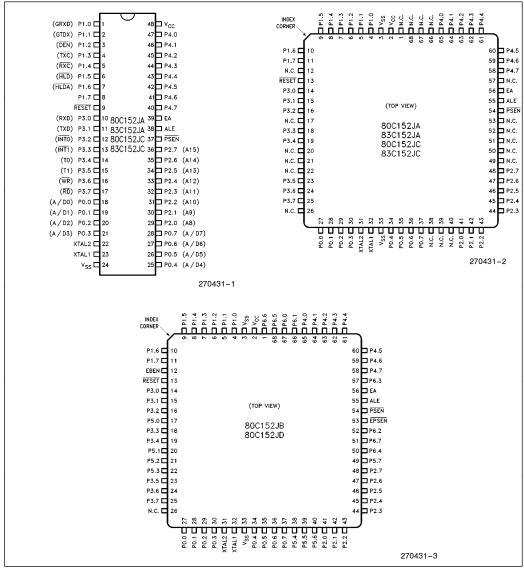

Figure 2. Block Diagram

#### 80C152JB/JD General Description

The 80C152JB/JD is a ROMless extension of the 80C152 Universal Communication controller. The 80C152JB has the same five 8-bit I/O ports of the 80C152, plus an additional two 8-bit I/O ports, Port 5 and Port 6. The 80C152JB/JD also has two additional control pins, EBEN (EPROM Bus ENable), and EPSEN (EPROM bus Program Store ENable).

EBEN selects the functionality of Port 5 and Port 6. When EBEN is low, these ports are strictly I/O, similar to Port 4. The SFR location for Port 5 is 91H and Port 6 is 0A1H. This means Port 5 and Port 6 are not bit addressable. With EBEN low, all program memory fetches take place via Port 0 and Port 2. (The 80C152 is a ROMless only product). When EBEN is high, Port 5 and Port 6 form an address/data bus called the E-Bus (EPROM-Bus) for program memory operations.

EPSEN is used in conjunction with Port 5 and Port 6 program memory operations. EPSEN functions like PSEN during program memory operation, but supports Port 5 and Port 6. EPSEN is the read strobe to external program memory for Port 5 and Port 6. EPSEN is activated twice during each machine cycle unless an external data memory operation occurs on Port(s) 0 and Port 2. When external data memory is accessed the second activation of EPSEN is skipped, which is the same as when using PSEN. Note that data memory fetches cannot be made through Ports 5 and 6.

When EBEN is high and EA is low, all program memory operations take place via Ports 5 and 6. The high byte of the address goes out on Port 6, and the low byte is output on Port 5. ALE is still used to latch the address on Port 5. Next, the op code is read on Port 5. The timing is the same as when using Ports 0 and 2 for external program memory operations.

|      | Table 1. Program Memory Fetches |                      |                    |                    |                                        |  |  |  |  |  |  |

|------|---------------------------------|----------------------|--------------------|--------------------|----------------------------------------|--|--|--|--|--|--|

| EBEN | ĒĀ                              | Program<br>Fetch via | PSEN               | EPSEN              | Comments                               |  |  |  |  |  |  |

| 0    | 0                               | P0, P2               | Active             | Inactive           | Addresses 0-0FFFFH                     |  |  |  |  |  |  |

| 0    | 1                               | N/A                  | N/A                | N/A                | Invalid Combination                    |  |  |  |  |  |  |

| 1    | 0                               | P5, P6               | Inactive           | Active             | Addresses 0-0FFFFH                     |  |  |  |  |  |  |

| 1    | 1                               | P5, P6<br>P0, P2     | Inactive<br>Active | Active<br>Inactive | Addresses 0−1FFFH<br>Addresses ≥ 2000H |  |  |  |  |  |  |

#### **F** . . . . . .

|                    | Table 2. 8XC152 Product Differences |                   |                             |                    |              |                |                |  |  |  |  |  |

|--------------------|-------------------------------------|-------------------|-----------------------------|--------------------|--------------|----------------|----------------|--|--|--|--|--|

| ROMIess<br>Version | CSMA/CD<br>and<br>HDLC/SDLC         | HDLC/SDLC<br>Only | ROM<br>Version<br>Available | PLCC<br>and<br>DIP | PLCC<br>Only | 5 I/O<br>Ports | 7 I/0<br>Ports |  |  |  |  |  |

| 80C152JA           | *                                   |                   | *(83C152JA)                 | *                  |              | *              |                |  |  |  |  |  |

| 80C152JB           | *                                   |                   |                             |                    | *            |                | *              |  |  |  |  |  |

| 80C152JC           |                                     | *                 | *(83C152JC)                 | *                  |              | *              |                |  |  |  |  |  |

| 80C152JD           |                                     | *                 |                             |                    | *            |                | *              |  |  |  |  |  |

#### NOTES:

\* = options available

0 standard frequency range 3.5 MHz to 12 MHz

0 "-1" frequency range 3.5 MHz to 16.5 MHz

## int<sub>el</sub>.

#### 8XC152JA/JB/JC/JD

| Pi              | in #                       | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|-----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DIP             | PLCC(1)                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 48              | 2                          | Vcc—Supply vol                                                                                                                                                                                                                                                                                                                                                                                                                                      | tage.                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 24              | 3,33(2)                    | V <sub>SS</sub> —Circuit grou                                                                                                                                                                                                                                                                                                                                                                                                                       | und.                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 18-21,<br>25-28 | 27-30,<br>34-37            | can sink 8 LS TT<br>state can be used<br>Port 0 is also th<br>external program<br>Memory, Port 0 a<br>data bus. In these<br>Port 0 also out                                                                                                                                                                                                                                                                                                         | L inputs. Port 0 pin<br>d as high-impedance<br>ne multiplexed low-<br>memory if EBEN is<br>lways emits the low<br>e applications it use                                                                                                     | order address and data bus during accesses to<br>s pulled low. During accesses to external Data<br>v-order address byte and serves as the multiplexed<br>es strong internal pullups when emitting 1s.<br>s during program verification. External pullups are                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 1-8             | 4-11                       | Port 1—Port 1 is an 8-bit bidirectional I/O port with internal pullups. Port 1 pins that have 1s written to them are pulled high by the internal pullups, and in that state car used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (I <sub>IL</sub> , on the data sheet) because of the internal pullups.<br>Port 1 also serves the functions of various special features of the 8XC152, as lis below: |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                 |                            | Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Name                                                                                                                                                                                                                                        | Alternate Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                 |                            | P1.0<br>P1.1<br>P1.2<br>P1.3<br>P1.4<br>P1.5<br>P1.6                                                                                                                                                                                                                                                                                                                                                                                                | GRXD<br>GTXD<br>DEN<br>TXC<br>RXC<br>HLD<br>HLDA                                                                                                                                                                                            | GSC data input pin<br>GSC data output pin<br>GSC enable signal for an external driver<br>GSC input pin for external transmit clock<br>GSC input pin for external receive clock<br>DMA hold input/output<br>DMA hold acknowledge input/output                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 29-36           | 41-48                      | have 1s written to<br>used as inputs. A<br>current (I <sub>IL</sub> , on th<br>Port 2 emits the<br>Memory if EBEN<br>bit addresses (Mu<br>address byte. In 1<br>During accesso<br>Port 2 emits the o                                                                                                                                                                                                                                                | o them are pulled h<br>s inputs, Port 2 pin<br>e data sheet) beca<br>e high-order addres<br>is pulled low. Durin<br>OVX @ DPTR and<br>these applications<br>es to external Data<br>contents of the P2 3                                     | al I/O port with internal pullups. Port 2 pins that<br>igh by the internal pullups, and in that state can be<br>s that are externally being pulled low will source<br>use of the internal pullups.<br>ss byte during fetches from external Program<br>ig accesses to external Data Memory that use 16-<br>DMA operations), Port 2 emits the high-order<br>t uses strong internal pullups when emitting 1s.<br>Memory that use 8-bit addresses (MOVX @ Ri),<br>Special Function Register.<br>er address bits during program verification. |  |  |  |  |  |

| 10- 17          | 14-16,<br>18, 19,<br>23-25 | have 1s written to<br>used as inputs. A<br>current (I <sub>IL</sub> , on th<br>Port 3 also ser<br>listed below:                                                                                                                                                                                                                                                                                                                                     | o them are pulled h<br>s inputs, Port 3 pin<br>e data sheet) beca<br>ves the functions o                                                                                                                                                    | f various special features of the MCS-51 Family, as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                 |                            | Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pin Name Alternate Function                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                 |                            | P3.0<br>P3.1<br>P3.2<br>P3.3<br>P3.4<br>P3.5<br>P3.6<br>P3.6<br>P3.7                                                                                                                                                                                                                                                                                                                                                                                | RXD Serial input line   TXD Serial output line   INT0 External Interrupt 0   INT1 External Interrupt 1   T0 Timer 0 external input   T1 Timer 1 external input   WR External Data Memory Write strobe   RD External Data Memory Read strobe |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

## intel

#### Pin Description (Continued) Pin # **Pin Description** 65-58 Port 4—Port 4 is an 8-bit bidirectional I/O port with internal pullups. Port 4 pins that 47-40 have 1s written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 4 pins that are externally being pulled low will source current (IIL, on the data sheet) because of the internal pullups. In addition, Port 4 also receives the low-order address bytes during program verification. **RST**—Reset input. A logic low on this pin for three machine cycles while the 9 13 oscillator is running resets the device. An internal pullup resistor permits a power-on reset to be generated using only an external capacitor to V<sub>SS</sub>. Although the GSC recognizes the reset after three machine cycles, data may continue to be transmitted for up to 4 machine cycles after Reset is first applied. 38 55 ALE—Address Latch Enable output signal for latching the low byte of the address during accesses to external memory. In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency, and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external Data Memory. While in Reset, ALE remains at a constant high level. **PSEN**—Program Store Enable is the Read strobe to External Program Memory. 37 54 When the 8XC152 is executing from external program memory. PSEN is active (low). When the device is executing code from External Program Memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to External Data Memory. While in Reset, PSEN remains at a constant high level. **EA**—External Access enable. EA must be externally pulled low in order to enable 39 56 the 8XC152 to fetch code from External Program Memory locations 0000H to OFFFH EA must be connected to V<sub>CC</sub> for internal program execution. 23 32 XTAL1—Input to the inverting oscillator amplifier and input to the internal clock generating circuits. 22 31 XTAL2—Output from the inverting oscillator amplifier. 17, 20 N/A Port 5—Port 5 is an 8-bit bidirectional I/O port with internal pullups. Port 5 pins that 21, 22 have 1s written to them are pulled high by the internal pullups, and in that state can 38, 39 be used as inputs. As inputs, Port 5 pins that are externally being pulled low will 40, 49 source current (IIL, on the data sheet) because of the internal pullups. Port 5 is also the multiplexed low-order address and data bus during accesses to external program memory if EBEN is pulled high. In this application it uses strong pullups when emitting 1s. N/A 67.66 Port 6—Port 6 is an 8-bit bidirectional I/O port with internal pullups. Port 6 pins that 52, 57 have 1s written to them are pulled high by the internal pullups, and in that state can 50.68 be used as inputs. As inputs, Port 6 pins that are externally pulled low will source 1, 51 current (IIL, on the data sheet) because of the internal pullups. Port 6 emits the high-order address byte during fetches from external Program Memory if EBEN is pulled high. In this application it uses strong pullups when emitting 1s. N/A 12 EBEN-E-Bus Enable input that designates whether program memory fetches take place via Ports 0 and 2 or Ports 5 and 6. Table 1 shows how the ports are used in conjunction with EBEN. N/A 53 **EPSEN**—E-bus Program Store Enable is the Read strobe to external program memory when EBEN is high. Table 2 shows when EPSEN is used relative to PSEN depending on the status of EBEN and EA.

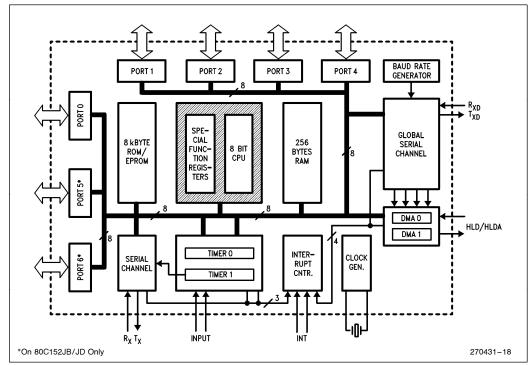

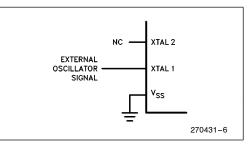

#### **OSCILLATOR CHARACTERISTICS**

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 3.

To drive the device from an external clock source, XTAL1 should be driven, while XTAL2 is left unconnected, as shown in Figure 4. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum high and low times specified on the Data Sheet must be observed.

An external oscillator may encounter as much as a 100 pF load at XTAL1 when it starts-up. This is due to interaction between the amplifier and its feedback capacitance. Once the external signal meets the V<sub>IL</sub> and V<sub>IH</sub> specifications the capacitance will not exceed 20 pF.

Figure 3. Using the On-Chip Oscillator

8XC152JA/JB/JC/JD

Figure 4. External Clock Drive

#### **IDLE MODE**

In Idle Mode, the CPU puts itself to sleep while most of the on-chip peripherals remain active. The major peripherals that do not remain active during Idle, are the DMA channels. The Idle Mode is invoked by software. The content of the on-chip RAM and all the Special Function Registers remain unchanged during this mode. The Idle Mode can be terminated by any enabled interrupt or by a hardware reset.

#### POWER DOWN MODE

In Power Down Mode, the oscillator is stopped and all on-chip functions cease except that the on-chip RAM contents are maintained. The mode Power Down is invoked by software. The Power Down Mode can be terminated only by a hardware reset.

Table 3. Status of the External Pins During Idle and Power Down Modes 80C152JA/83C152JA/80C152JC/83C152JC

| Mode       | Program<br>Memory | ALE | PSEN | Port 0 | Port 1 | Port 2  | Port 3 | Port 4 |

|------------|-------------------|-----|------|--------|--------|---------|--------|--------|

| Idle       | Internal          | 1   | 1    | Data   | Data   | Data    | Data   | Data   |

| Idle       | External          | 1   | 1    | Float  | Data   | Address | Data   | Data   |

| Power Down | Internal          | 0   | 0    | Data   | Data   | Data    | Data   | Data   |

| Power Down | External          | 0   | 0†   | Float  | Data   | Data    | Data   | Data   |

#### 80C152JB/80C152JD

| Mode       | Instruction<br>Bus | ALE | PSEN | EPSEN | Port 0 | Port 1 | Port 2  | Port 3 | Port 4 | Port 5 | Port 6  |

|------------|--------------------|-----|------|-------|--------|--------|---------|--------|--------|--------|---------|

| Idle       | P0, P2             | 1   | 1    | 1     | Float  | Data   | Address | Data   | Data   | 0FFH   | 0FFH    |

| Idle       | P5, P6             | 1   | 1    | 1     | Data   | Data   | Data    | Data   | Data   | 0FFH   | Address |

| Power Down | P0, P2             | 0   | 0    | 1     | Float  | Data   | Data    | Data   | Data   | 0FFH   | 0FFH    |

| Power Down | P5, P6             | 0   | 1†   | 0     | Data   | Data   | Data    | Data   | Data   | 0FFH   | 0FFH    |

#### NOTE:

For more detailed information on the reduced power modes refer to the Embedded Controller Handbook, and Application Note AP-252, "Designing with the 80C51BH."

\*Note difference of logic level of PSEN during Power Down for ROM JA/JC and ROM emulation mode for JC/JD.

#### ABSOLUTE MAXIMUM RATINGS\*

| Ambient Temperature Under Bias $\ldots.0^{\circ}C$ to $+70^{\circ}C$ |

|----------------------------------------------------------------------|

| Storage Temperature $\dots -65^{\circ}C$ to $+150^{\circ}C$          |

| Voltage on Any pin to V_{SS}\ldots-0.5V to (V_{CC}+0.5V)             |

| Voltage on $V_{CC}$ to VSS $\ldots \ldots \ldots -0.5V$ to $+6.5V$   |

| Power Dissipation1.0W <sup>(9)</sup>                                 |

|                                                                      |

NOTICE: This data sheet contains preliminary information on new products in production. The specifications are subject to change without notice. Verify with your local Intel Sales office that you have the latest data sheet before finalizing a design.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

| Symbol           | Parameter                                                                         | Min                     | Typ<br>(Note 3) | Max                     | Unit           | Test Conditions                                        |

|------------------|-----------------------------------------------------------------------------------|-------------------------|-----------------|-------------------------|----------------|--------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage<br>(All Except EA, EBEN)                                        | -0.5                    |                 | 0.2V <sub>CC</sub> -0.1 | V              |                                                        |

| V <sub>IL1</sub> | Input Low Voltage<br>(EA, EBEN)                                                   | -0.5                    |                 | 0.2V <sub>CC</sub> -0.3 | V              |                                                        |

| V <sub>IH</sub>  | Input High Voltage<br>(Except XTAL1, RST)                                         | 0.2V <sub>CC</sub> +0.9 |                 | V <sub>CC</sub> +0.5    | V              |                                                        |

| V <sub>IH1</sub> | Input High Voltage<br>(XTAL1, RST)                                                | 0.7V <sub>CC</sub>      |                 | V <sub>CC</sub> +0.5    | V              |                                                        |

| V <sub>OL</sub>  | Output Low Voltage<br>(Ports 1, 2, 3, 4, 5, 6)                                    |                         |                 | 0.45                    | V              | I <sub>OL</sub> = 1.6 mA<br>(Note 4)                   |

| V <sub>OL1</sub> | Output Low Voltage<br>(Port 0, ALE, PSEN, EPSEN)                                  |                         |                 | 0.45                    | V              | I <sub>OL</sub> = 3.2 mA<br>(Note 4)                   |

| V <sub>OH</sub>  | Output High Voltage<br>(Ports 1, 2, 3, 4, 5, 6 COMM9                              | 2.4                     |                 |                         | V              | $I_{OH}=-60 \ \mu A$<br>$V_{CC}=5V \pm 10\%$           |

|                  | ALE, PSEN, EPSEN)                                                                 | 0.9V <sub>CC</sub>      |                 |                         | V              | $I_{OH} = -10 \ \mu A$                                 |

| V <sub>OH1</sub> | Output High Voltage<br>(Port 0 in External                                        | 2.4                     |                 |                         | V              | $I_{OH}=-400\ \mu A$<br>$V_{CC}=5V\ \pm10\%$           |

|                  | Bus Mode)                                                                         | 0.9V <sub>CC</sub>      |                 |                         | V              | $I_{OH} = -40 \ \mu A$ (Note 5)                        |

| IIL              | Logical 0 Input<br>Current (Ports 1, 2, 3, 4, 5, 6)                               |                         |                 | -50                     | μA             | $V_{IN} = 0.45V$                                       |

| ITL              | Logical 1 to 0<br>Transition Current<br>(Ports 1, 2, 3, 4, 5, 6)                  |                         | -               | -650                    | μΑ             | $V_{IN} = 2V$                                          |

| ILI              | Input Leakage<br>(Port 0, ĒĀ)                                                     |                         |                 | ±10                     | μA             | $0.45 < V_{IN} < V_{CC}$                               |

| RRST             | Reset Pullup Resistor                                                             | 40                      |                 |                         | kΩ             |                                                        |

| I <sub>IH</sub>  | Logical 1 Input Current (EBEN)                                                    |                         |                 | + 60                    | μA             |                                                        |

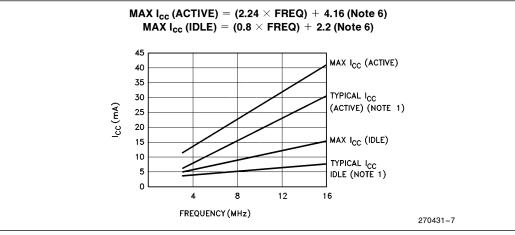

| ICC              | Power Supply Current :<br>Active (16.5 MHz)<br>Idle (16.5 MHz)<br>Power Down Mode |                         | 31<br>8<br>10   | 41.1<br>15.4            | mA<br>mA<br>μA | (Note 6)<br>(Note 6)<br>V <sub>CC</sub> = 2.0V to 5.5V |

### D.C. CHARACTERISTICS (T<sub>A</sub> = 0°C to +70°C; V<sub>CC</sub> = 5V $\pm$ 10%; V<sub>SS</sub> = 0V)

#### 8XC152JA/JB/JC/JD

Figure 5. I<sub>CC</sub> vs Frequency

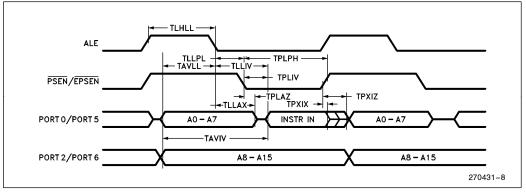

#### EXPLANATION OF THE AC SYMBOLS

Each timing symbol has 5 characters. The first character is always a 'T' (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

- A: Address.

- C: Clock

- D: Input data.

- H: Logic level HIGH.

- I: Instruction (program memory contents).

- L: Logic level LOW, or ALE.

- P: PSEN.

- Q: Output data.

- R: READ signal.

- T: Time.

- V: Valid.

- W: WRITE signal.

- X: No longer a valid logic level.

- Z: Float.

For example,

- TAVLL = Time for Address Valid to ALE Low.

- TLLPL = Time for ALE Low to  $\overline{\text{PSEN}}$  Low.

**A.C. CHARACTERISTICS** (T<sub>A</sub> = 0°C to +70°C; V<sub>CC</sub> = 5V ±10%; V<sub>SS</sub> = 0V; Load Capacitance for Port 0, ALE, and  $\overline{PSEN}$  = 100 pF; Load Capacitance for All Other Outputs = 80 pF)

| Symbol               | Parameter                                                         | 16.5 | MHz | Variable   | Unit       |     |

|----------------------|-------------------------------------------------------------------|------|-----|------------|------------|-----|

| Symbol               | Farameter                                                         | Min  | Max | Min        | Max        |     |

| 1/TCLCL              | Oscillator Frequency<br>80C152JA/JC<br>83C152JA/JC<br>80C152JB/JD |      |     | 3.5        | 12         | MHz |

|                      | 80C152JA/JC-1<br>83C152JA/JC-1<br>80C152JB/JD-1                   |      |     | 3.5        | 16.5       | MHz |

| TLHLL                | ALE Pulse Width                                                   | 81   |     | 2TCLCL-40  |            | ns  |

| TAVLL                | Address Valid to ALE Low                                          | 5    |     | TCLCL-55   |            | ns  |

| TLLAX                | Address Hold After ALE Low                                        | 25   |     | TCLCL-35   |            | ns  |

| TLLIV                | ALE Low to Valid<br>Instruction In                                |      | 142 |            | 4TCLCL-100 | ns  |

| TLLPL                | ALE Low to PSEN Low                                               | 20   |     | TCLCL-40   |            | ns  |

| TPLPH                | PSEN Pulse Width                                                  | 137  |     | 3TCLCL-45  |            | ns  |

| TPLIV                | PSEN Low to Valid<br>Instruction In                               |      | 77  |            | 3TCLCL-105 | ns  |

| ΤΡΧΙΧ                | Input Instruction<br>Hold After PSEN                              | 0    |     | 0          |            | ns  |

| TPXIZ                | Input Instruction<br>Float After PSEN                             |      | 35  |            | TCLCL-25   | ns  |

| TAVIV                | Address to Valid<br>Instruction In                                |      | 198 |            | 5TCLCL-105 | ns  |

| TPLAZ                | PSEN Low to Address<br>Float                                      |      | 10  |            | 10         | ns  |

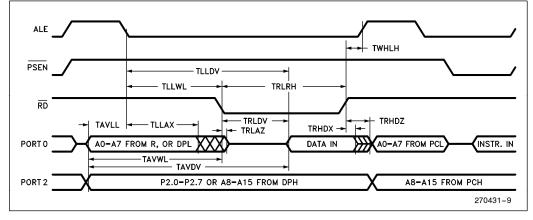

| TRLRH                | RD Pulse Width                                                    | 263  |     | 6TCLCL-100 |            | ns  |

| TWLWH                | WR Pulse Width                                                    | 263  |     | 6TCLCL-100 |            | ns  |

| TRLDV                | RD Low to Valid<br>Data In                                        |      | 138 |            | 5TCLCL-165 | ns  |

| TRHDX                | Data Hold After RD                                                | 0    |     | 0          |            | ns  |

| TRHDZ                | Data Float After RD                                               |      | 51  |            | 2TCLCL-70  | ns  |

| TLLDV                | ALE Low to Valid<br>Data In                                       |      | 335 |            | 8TCLCL-150 | ns  |

| TAVDV                | Address to Valid<br>Data In                                       |      | 380 |            | 9TCLCL-165 | ns  |

| TLLWL                | ALE Low to RD or<br>WR Low                                        | 132  | 232 | 3TCLCL-50  | 3TCLCL+50  | ns  |

| TAVWL                | Address to RD or<br>WR Low                                        | 112  |     | 4TCLCL-130 |            | ns  |

| TQVWX <sup>(8)</sup> | Data Valid to WR<br>Transition                                    | 196  |     | 6TCLCL-167 |            | ns  |

| TWHQX                | Data Hold After WR                                                | 10   |     | TCLCL-50   |            | ns  |

| TRLAZ                | RD Low to Address<br>Float                                        |      | 0   |            | 0          | ns  |

| TWHLH                | RD or WR High to<br>ALE High                                      | 20   | 100 | TCLCL-40   | TCLCL+40   | ns  |

| EXTERNAL | . PROGRAM | AND DATA | MEMORY | CH | ARACTERISTICS (Note 7, 10) |  |

|----------|-----------|----------|--------|----|----------------------------|--|

|          |           |          |        |    |                            |  |

#### 8XC152JA/JB/JC/JD

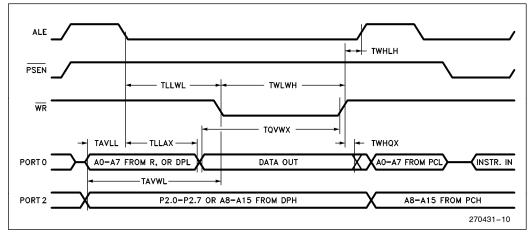

#### EXTERNAL PROGRAM MEMORY READ CYCLE

#### EXTERNAL DATA MEMORY READ CYCLE

#### EXTERNAL DATA MEMORY WRITE CYCLE

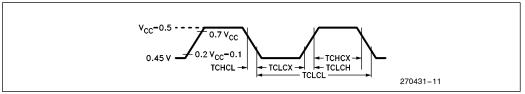

### EXTERNAL CLOCK DRIVE

| Symbol  | Parameter            | Min | Мах  | Units |

|---------|----------------------|-----|------|-------|

| 1/TCLCL | Oscillator Frequency | 3.5 | 16.5 | MHz   |

| TCHCX   | High Time            | 20  |      | ns    |

| TCLCX   | Low Time             | 20  |      | ns    |

| TCLCH   | Rise Time            |     | 20   | ns    |

| TCHCL   | Fall Time            |     | 20   | ns    |

#### EXTERNAL CLOCK DRIVE WAVEFORM

#### 8XC152JA/JB/JC/JD

| Symbol | Parameter                                   | 16.5 | MHz | Variable    | Units       |       |

|--------|---------------------------------------------|------|-----|-------------|-------------|-------|

| Cymbol | randheter                                   | Min  | Max | Min         | Мах         | onito |

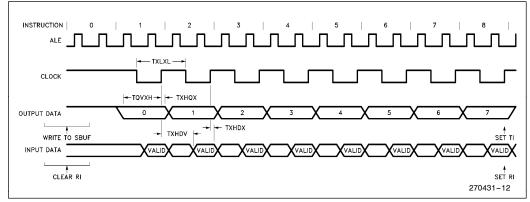

| TXLXL  | Serial Port Clock Cycle<br>Time             | 727  |     | 12TCLCL     |             | ns    |

| TQVXH  | Output Data Setup to<br>Clock Rising Edge   | 473  |     | 10TCLCL-133 |             | ns    |

| TXHQX  | Output Data Hold After<br>Clock Rising Edge | 4    |     | 2TCLCL-117  |             | ns    |

| TXHDX  | Input Data Hold After<br>Clock Rising Edge  | 0    |     | 0           |             | ns    |

| TXHDV  | Clock Rising Edge to<br>Input Data Valid    |      | 473 |             | 10TCLCL-133 | ns    |

#### LOCAL SERIAL CHANNEL TIMING—SHIFT REGISTER MODE

#### SHIFT REGISTER MODE TIMING WAVEFORMS

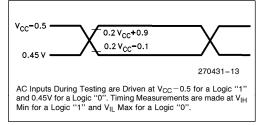

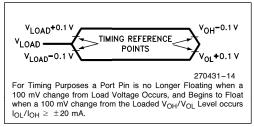

### A.C. TESTING:

#### INPUT, OUTPUT WAVEFORMS

#### FLOAT WAVEFORM

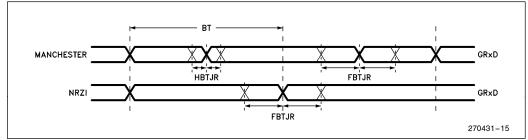

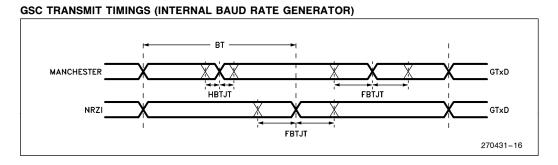

| Symbol | Parameter                                                                             | 16.5 MHz (E | BAUD = 0) | Varia | Unit                                       |    |

|--------|---------------------------------------------------------------------------------------|-------------|-----------|-------|--------------------------------------------|----|

| Gymbol | rarameter                                                                             | Min         | Мах       | Min   | Мах                                        |    |

| HBTJR  | Allowable jitter on<br>the Receiver for ½<br>bit time (Manchester<br>encoding only)   |             | 0.0375    |       | (0.125 ×<br>(BAUD+1)×<br>8TCLCL)<br>−25 ns | μs |

| FBTJR  | Allowable jitter on<br>the Receiver for one<br>full bit time (NRZI<br>and Manchester) |             | 0.10      |       | (0.25 ×<br>(BAUD+1)×<br>8TCLCL)<br>−25 ns  | μs |

| HBTJT  | Jitter of data from<br>Transmitter for ½<br>bit time (Manchester<br>encoding only)    |             | ±10       |       | ±10                                        | ns |

| FBTJT  | Jitter of data from<br>Transmitter for one<br>full bit time (NRZI<br>and Manchester)  |             | ±10       |       | ±10                                        | ns |

| DRTR   | Data rise time for<br>Receiver <sup>(11)</sup>                                        |             | 20        |       | 20                                         | ns |

| DFTR   | Data fall time for<br>Receiver <sup>(12)</sup>                                        |             | 20        |       | 20                                         | ns |

#### GLOBAL SERIAL PORT TIMINGS—Internal Baud Rate Generator

#### GSC RECEIVER TIMINGS (INTERNAL BAUD RATE GENERATOR)

#### 8XC152JA/JB/JC/JD

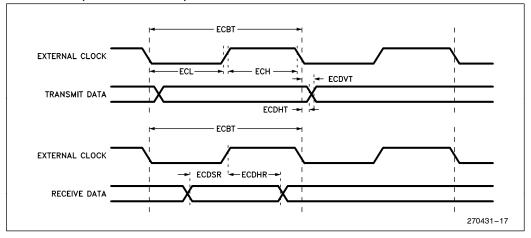

### GLOBAL SERIAL PORT TIMINGS—External Clock

| Symbol  | Parameter                                                                              | 16.5 MHz |     | Variable Oscillator |                       | Unit |

|---------|----------------------------------------------------------------------------------------|----------|-----|---------------------|-----------------------|------|

|         |                                                                                        | Min      | Max | Min                 | Max                   |      |

| 1/ECBT  | GSC Frequency with an<br>External Clock                                                |          | 2.4 | 0.009               | $F_{OSC} 	imes 0.145$ | MHz  |

| ECH     | External Clock High                                                                    | 170      |     | 2TCLCL<br>+ 45 ns   |                       | ns   |

| ECL(13) | External Clock Low                                                                     | 170      |     | 2TCLCL<br>+ 45 ns   |                       | ns   |

| ECRT    | External Clock Rise<br>Time <sup>(11)</sup>                                            |          | 20  |                     | 20                    | ns   |

| ECFT    | External Clock Fall<br>Time <sup>(12)</sup>                                            |          | 20  |                     | 20                    | ns   |

| ECDVT   | External Clock to Data<br>Valid Out - Transmit<br>(to External Clock<br>Negative Edge) |          | 150 |                     | 150                   | ns   |

| ECDHT   | External Clock Data<br>Hold - Transmit<br>(to External Clock<br>Negative Edge)         | 0        |     | 0                   |                       | ns   |

| ECDSR   | External Clock Data<br>Set-up - Receiver<br>(to External Clock<br>Positive Edge)       | 45       |     | 45                  |                       | ns   |

| ECDHR   | External Clock to Data<br>Hold - Receiver<br>(to External Clock<br>Positive Edge)      | 50       |     | 50                  |                       | ns   |

#### GSC TIMINGS (EXTERNAL CLOCK)

#### NOTES:

1. N.C. pins on PLCC package may be connected to internal die and should not be used in customer applications.

2. It is recommended that both Pin 3 and Pin 33 be grounded for PLCC devices.

3. "Typicals" are based on samples taken from early manufacturing lots and are not guaranteed. The measurements were and with  $V_{CC} = 5V$  at room temperature. 4. Capacitive loading on Ports 0 and 2 may cause spurious noise pulses to be superimposed on the V<sub>OL</sub>s of ALE and Ports

1 and 3. The noise is due to external bus capacitance discharging into the Port 0 and Port 2 pins when these pins make 1to-0 transitions during bus operations. In the worst cases (capacitive loading > 100 pF), the noise pulse on the ALE pin may exceed 0.8V. In such cases it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input.

5. Capacitive loading on Ports 0 and 2 may cause the VOH on ALE and PSEN to momentarily fall below the 0.9V<sub>CC</sub> specification when the address bits are stabilizing.

6. I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with TCLCH, TCHCL = 5 ns,  $V_{IL} = V_{SS} + 0.5V$ ,  $V_{IH} = V_{CC} - 0.5V$ ; XTAL2 N.C.; Port 0 pins connected to  $V_{CC}$ . "Operating" current is measured with EA connected to  $V_{CC}$  and RST connected to  $V_{SS}$ . "Idle" current is measured with EA connected to  $V_{SS}$ , RST connected to  $V_{CC}$  and GSC inactive. 7. The specifications relating to external data memory characteristics are also applicable to DMA operations.

8. TQVWX should not be confused with TQVWX as specified for 80C51BH. On 80C152, TQVWX is measured from data valid to rising edge of WR. On 80C51BH, TQVWX is measured from data valid to falling edge of WR. See timing diagrams. 9. This value is based on the maximum allowable die temperature and the thermal resistance of the package.

10. All specifications relating to external program memory characteristics are applicable to: EPSEN for PSEN

Port 5 for Port 0 Port 6 for Port 2

when EBEN is at a Logical 1 on the 80C152JB/JD.

11. Same as TCLCH, use External Clock Drive Waveform.

12. Same as TCHCL, use External Clock Drive Waveform.

13. When using the same external clock to drive both the receiver and transmitter, the minimum ECL spec effectively becomes 195 ns at all frequencies (assuming 0 ns propagation delay) because ECDVT (150 ns) plus ECDSR (45 ns) reguirements must also be met (150 + 45 = 195 ns). The 195 ns requirement would also increase to include the maximum propagation delay between receivers and transmitters.

#### 8XC152JA/JB/JC/JD

### **DESIGN NOTES**

Within the 8XC152 there exists a race condition that may set both the RDN and AE bits at the end of a valid reception. This will not cause a problem in the application as long as the following steps are followed:

-Never give the receive error interrupt a higher priority than the valid reception interrupt

—Do not leave the valid reception interrupt service routine when AE is set by using a RETI instruction until AE is cleared. To clear AE set the GREN bit, this enables the receiver. If the user desires that the receiver remain disabled, clear GREN after setting it before leaving the interrupt service routine.

—If the AE bit is checked by user software in response to a valid reception interrupt, the status of AE should be considered invalid.

The race condition is dependent upon both the temperature that the device is currently operating at and the processing the device received during the wafer fabrication.

When the idle mode is terminated by a hardware reset, the device normally resumes program execution, from where it left off, up to two machine cycles before the internal reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but access to the port pins is not inhibited. To eliminate the possibility of an unexpected write when Idle is terminated by reset, the instruction following the one that invokes Idle should not be one that writes to a port pin or to external memory.

#### DATA SHEET REVISION SUMMARY

The following represent the key differences between the "-003" and the "-002" version of the 80C152/83C152 data sheet. Please review this summary carefully.

- 1. Removed minimum GSC frequency spec when used with an external clock.

- 2. Change figure "External Program Memory Read Cycle" to show Port 0/Port 5 address floating after PSEN goes low.

- 3. Added design note on terminating idle with reset.

- 4. Added status of PSEN during Power Down mode to Table 3.

- 5. Moved all notes to back of data sheet.

- 6. Changed microcomputer to microcontroller.

- 7. Added External Oscillator start-up capacitance note.

The following represent the key differences between the "-002" and the "-001" version of the 80C152/ 83C152 data sheet. Please review this summary carefully.

- 1. Status of data sheet changed from "ADVANCED" to "PRELIMINARY".

- 2. 80C152JC, 83C152JC, and 80C152JD were added.

- 3. Added AE/RDN design note.

- 4. This revision summary was added.

- 5. Note #13 was added (Effective ECL spec at higher clock rates).

- 6. Table #2 changed to Table #3 (Status of pins during Idle/Power Down).

- 7. Current Table #2 was added (JA vs. JB vs. JC vs. JD matrix).

- 8. Transmit jitter spec changed from  $\pm35$  ns and  $\pm70$  ns to  $\pm10$  ns.