ADVANCE INFORMATION

# 82595FX ISA BUS HIGH INTEGRATION ETHERNET CONTROLLER

- Optimal Integration for Lowest Cost Solution

- Glueless 8-Bit/16-Bit ISA Bus Interface

- Provides Fully 802.3 Compliant AUI and TPE Serial Interface

- Local SRAM Support up to 64 Kbytes

- Integrated ISA Bus Data

Transceivers

- FLASH/EPROM Boot Support up to 1 Mbyte for Diskless Workstations

- Hardware and Software Portable between Motherboard and Adapter Card Solutions

- High Performance Networking Functions

- Advanced Concurrent Processing of Receive and Transmit Functions

- 16-Bit/32-Bit IO Accesses to Local SRAM with Zero Added Wait-States

- Ring Buffer Structure for Continuous

Frame Reception and Transmit

Chaining

- Automatic Retransmission on Collision

- Automatically Corrects TPE Polarity Switching Problems

- Auto Negotiation/Manual Full Duplex Support

- Low Power CHMOS IV Technology

- Ease of Use

- Auto-Negotiation of Full Duplex Functionality

- Fully Compatible with ISA Plug and Play Specification

- EEPROM Interface to Support Jumperless Designs

- Software Structures Optimized to Reduce Processing Steps

- Automatically Maps into Unused PC IO Locations to Help Eliminate LAN Setup Problems

- All Software Structures Contained in One 16-Byte IO Space

- JTAG Port for Reduced Board Testing Times

- Automatic or Manual Switching between TPE and AUI Ports

- Supports Eight IRQs

- Power Management

- Advanced Power Management

Support by Power Down and Sleep

Mode

- Both SL Compatible SMOUT Input and Non-SL Software Parameter for Power Down Mode

- 160-Lead QFP Package Provides Smallest Available Form Factor

- 100% Backwards Software Compatible to 82595TX

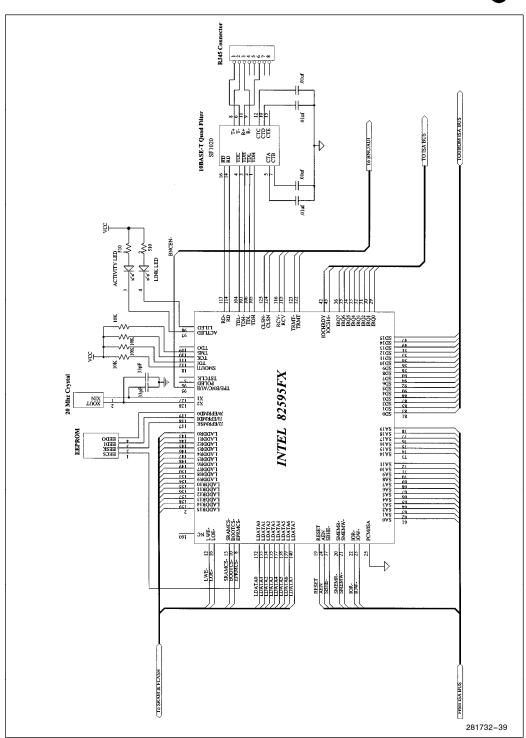

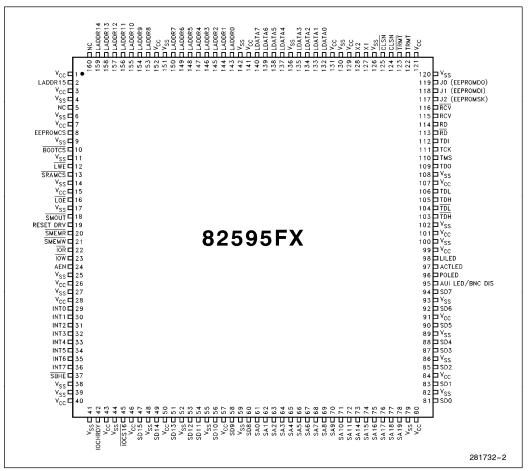

Figure 1. 82595FX Block Diagram

\*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

COPYRIGHT © INTEL CORPORATION, 1996

November 1995

Order Number: 281732-001

## 82595FX ISA Bus High Integration ETHERNET Controller

| CONTENTS                                    | PAGE | CONTENTS                                                 | PAGE              |

|---------------------------------------------|------|----------------------------------------------------------|-------------------|

| 1.0 INTRODUCTION                            | 5    | 4.4 Local SRAM Accesses .                                | 18                |

| 1.1 82595FX Overview                        |      | 4.4.1 Writing to Local Mem                               | nory 18           |

| 1.2 Power Management                        |      | 4.4.2 Reading from Local                                 | 40                |

| 1.3 Auto-Negotiation                        |      | Memory                                                   |                   |

| 1.4 Compliance to Industry                  |      | 4.5 Serial EEPROM Interface<br>4.6 Boot EPROM/FLASH Inte |                   |

| Standards                                   | 6    | 4.0 BOOLEPHOW/FLASH III.                                 | 311ace 20         |

| 1.4.1 Bus Interface—ISA IEEE P996           | 6    | 5.0 COMMAND AND STATUS INTERFACE                         | 20                |

| 1.4.2 ETHERNET/Twisted Pair                 |      | 5.1 Command OP Code Field                                | 20                |

| Ethernet Interface—IEEE 802.3 Specification | 6    | 5.2 ABORT (Bit 5)                                        |                   |

| ·                                           |      | 5.3 Pointer Field (Bits 6 and 7                          |                   |

| 2.0 82595FX PIN DEFINITIONS                 |      | 5.4 82595FX Status Interface                             | 22                |

| 2.1 ISA Bus Interface                       |      | 6.0 INITIALIZATION                                       | 22                |

| 2.3 Miscellaneous Control                   |      | 7.0 FRAME TRANSMISSION .                                 | 22                |

| 2.4 JTAG Control                            |      | 7.1 82595FX XMT Block Men                                |                   |

| 2.5 Serial Interface                        |      | Format                                                   |                   |

| 2.6 Serial Interface LEDs                   |      | 7.2 XMT Chaining                                         | 25                |

| 2.7 Power and Ground                        |      | 7.3 Automatic Retransmission                             | ı on              |

| 2.8 Reserved Pins                           |      | Collision                                                | 28                |

| 2.9 82595FX Pin Summary                     |      | 8.0 FRAME RECEPTION                                      | 28                |

| •                                           |      | 8.1 82595FX RCV Memory                                   |                   |

| 3.0 82595FX INTERNAL ARCHITECTURE OVERVIEW  | 13   | Structure                                                |                   |

| 3.1 System Interface Overview               |      | 8.2 RCV Ring Buffer Operation                            | <sub>'</sub> n 31 |

| 3.1.1 Concurrent Processing Functionality   |      | 9.0 SERIAL INTERFACE                                     | 32                |

| 3.2 Local Memory Interface                  |      | 10.0 APPLICATION NOTES                                   | 33                |

| 3.3 CSMA/CD Unit                            |      | 10.1 Bus Interface                                       |                   |

| 3.4 Serial Interface                        |      | 10.2 Local Memory Interface                              |                   |

|                                             |      | 10.3 EEPROM Interface (ISA                               | • •               |

| 4.0 ACCESSING THE 82595FX                   |      | 10.4 Serial Interface                                    |                   |

| 4.1 82595FX Register Map                    |      | 10.4.1 AUI Circuit                                       |                   |

| 4.1.1 IO Bank 0                             |      | 10.4.2 TPE Circuit                                       |                   |

| 4.1.2 IO Bank 1                             |      | 10.4.3 LED Circuit                                       | 34                |

| 4.1.3 IO Bank 2                             |      |                                                          |                   |

| 4.2 Writing to the 82595FX                  |      |                                                          |                   |

| 4.3 Reading from the 82595FX                | 18   |                                                          |                   |

| CONTENTS                              | PAGE   | CONTENTS                       | PAGE |

|---------------------------------------|--------|--------------------------------|------|

| 10.5 Layout Guidelines                | 34     | 11.2 AC Timing Characteristics | 36   |

| 10.5.1 General                        | 34     | 11.3 AC Measurement Conditions | 36   |

| 10.5.2 Crystal                        | 34     | 11.4 ISA Interface Timing      | 37   |

| 10.5.3 82595FX Analog Differ          | ential | 11.6 Local Memory Timings      | 41   |

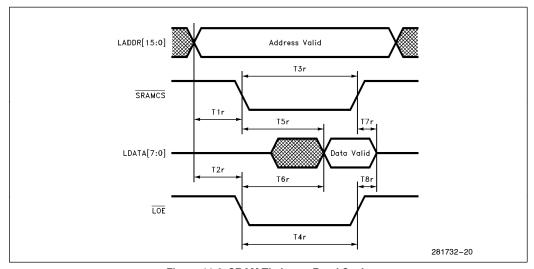

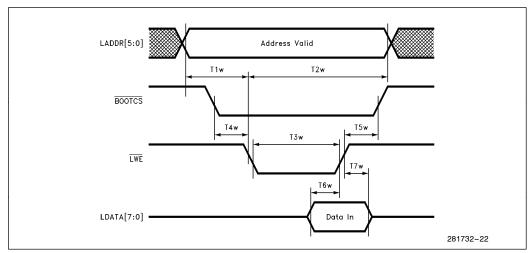

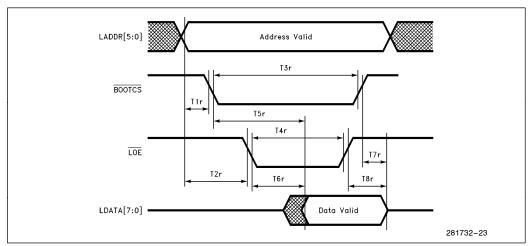

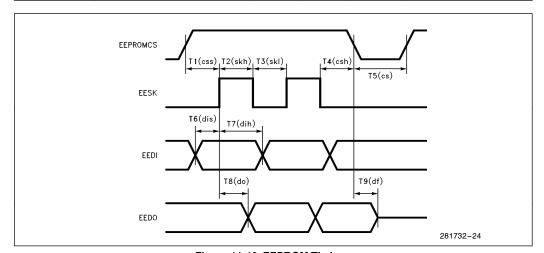

| Signals                               | 34     | 11.6.1 SRAM Timings            | 41   |

| 10.5.4 Decoupling  Considerations     | 24     | 11.6.2 FLASH/EPROM Timings     | 43   |

| Considerations                        |        | 11.7 Interrupt Timing          | 45   |

| 11.0 ELECTRICAL SPECIFICATIO          | NS     | 11.8 RESET and SMOUT Timing    | 46   |

| AND TIMINGS                           |        | 11.9 JTAG Timing               | 47   |

| 11.1 Absolute Maximum Ratings         | 35     | 11.10 Serial Timings           |      |

| 11.1.1 Package Thermal Specifications | 36     |                                |      |

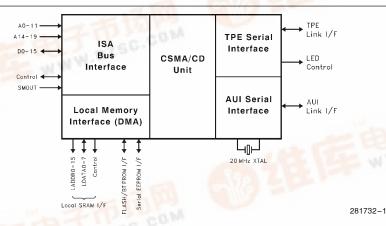

Figure 2. 82595FX Pinout

## 1.0 INTRODUCTION

## 1.1 82595FX Overview

The 82595FX is a highly integrated, high performance LAN controller which provides a cost effective LAN solution for ISA compatible Personal Computer (PC) motherboards (both desktop and portable), and add-on ISA adapter boards. The 82595FX integrates all of the major functions of a buffered LAN solution into one chip with the exception of the local buffer memory, which is implemented by adding one SRAM component to the LAN solution. The 82595FX's Concurrent Processing feature significantly enhances throughput performance. Both system bus and serial link activities occur concurrently, allowing the 82595FX to maximize network bandwidth by minimizing delays associated with transmit or receiving frames. The 82595FX's bus interface is a glueless attachment to an ISA bus. Its serial interface provides a Twisted Pair Ethernet (TPE) and an Attachment Unit Interface (AUI) connection. By integrating the majority of the LAN solution functions into one cost effective component, production cost saving can be achieved as well as significantly decreasing the design time for a solution. This level of integration also allows an 82595FX solution to be ported between different applications (PC motherboards, and adapters, while maintaining a compatible hardware and software base.

The 82595FX's software interface is optimized to reduce the number of processing steps that are required to interface to the 82595FX solution. The 82595FX's initialization and control registers are directly addressable within one 16-byte IO address block. The 82595FX can automatically resolve any conflicts to an IO block by moving its IO offset to an unused location in the case that a conflict occurs. The 82595FX's local memory is arranged in a simple ring buffer structure for efficient transfer of transmit and receive packets. The local memory, up to 64 Kbytes of SRAM, resides as either a 16-bit or 32bit IO port in the host systems IO map programmable through configuration. The 82595FX provides direct control over the local SRAM. The 82595FX performs a prefetch to the SRAM memory allowing CPU IO cycles to this data with no added wait-states. The 82595FX also provides an interface to up to 1 Mbyte of FLASH or EPROM memory. An interface to an EEPROM, which holds solution configuration values and can also contain the Node ID, allows for the implementation of a "jumperless" design. In addition, the 82595FX contains full hardware support for the implementation of the ISA Plug N' Play specification. Plug N' Play eliminates jumpers and complicated setup utilities by allowing peripheral functions to be added to a PC automatically (such as adapter cards) without the need to individually configure each parameter (e.g. Interrupt, IO Address, etc). This allows for configuration ease-of-use, which results in minimal time associated with installation.

The 82595FX's packaging and power management features are designed to consume minimal board real estate and system power. This is required for applications such as portable PC motherboard designs which require a solution with very low real estate and power consumption. The 82595FX package is a 160-lead PQFP (Plastic Quad Flat Pack). Its dimensions are 28 mm by 28 mm, and 3.5 mm in height. The 82595FX contains two power down modes; an SL compatible power down mode which utilizes the SL SMOUT input, and a POWER DOWN command for non-SL systems.

## 1.2 Power Management

Power management and low power consumption are two items that will allow any design using the 82595FX to be suitable for green PC use. Low power operation is initiated when software issues a SLEEP command to the device. After a short wait, it will shut off the system clock, some parts of the Backoff Randomizer, several input buffers and the two LED drivers. The 82595FX will subsequently wake up from sleep mode when software initiates an ISA cycle in the application, as well as when it receives a frame addressed to it. The total power consumption when in sleep mode can be as low as approximately 175 mW. Normal idle power consumption is 300 mW.

The software POWER DOWN command, along with its companion hardware implementation—the SMOUT I/O pin, provide additional power management capabilities. This feature allows the 82595FX to be powered down, and then at some time in the future be selectively reset without having lost the current configuration. See the 82595FX User's Guide for further details on these features.

## 1.3 Auto-Negotiation

Auto-negotiation functionality is a method of automatically determining the highest common operating mode (i.e., 10BaseT half duplex, 10BaseT full duplex, etc.) between two network devices. Using this functionality, two stations, each having a varying number of different operating modes, negotiate the highest possible common operating mode between them. During the power up sequence, the auto-negotiation functionality will automatically establish a link with which it can take advantage of any auto-negotiation-capable device it is connected to. An autonegotiation capable hub can detect and automatically configure its ports to take maximum advantage of

common modes of operation without any user intervention or prior knowledge by connected stations. See the 82595FX User's Guide for details on this function.

For further information on these enhancements and a description of all the differences between the 82595TX and 82595FX, please consult the 82595FX User's Manual, available through your local sales representative.

## 1.4 Compliance to Industry Standards

The 82595FX has two interfaces; the host system interface, which is an ISA bus interface, and the serial, or network interface. This interface has been standardized by the IEEE.

## 1.4.1 BUS INTERFACE— ISA IEEE P996

The 82595FX implements the full ISA bus interface. It is compatible with the IEEE spec P996.

## 1.4.2 ETHERNET/TWISTED PAIR ETHERNET INTERFACE—IEEE 802.3 SPECIFICATION

The 82595FX's serial interface provides either an AUI port interface or a Twisted Pair Ethernet (TPE) interface. The AUI port can be connected to an Ethernet Transceiver cable drop, providing a fully compliant IEEE 802.3 AUI interface. The TPE port provides a fully compliant IEEE 10BASE-T interface. The 82595FX can automatically switch to whichever port (TPE or AUI) is active.

## 2.0 82595FX PIN DEFINITIONS

## 2.1 ISA Bus Interface

| Symbol | Pin<br>No. | Туре | Name and Function                                                         |

|--------|------------|------|---------------------------------------------------------------------------|

| SA0    | 61         | I    | ADDRESS BUS: These pins provide address decoding for up to 1 Kbyte of     |

| SA1    | 62         |      | address. These pins also provide 4 Kbytes of IO addressing to support the |

| SA2    | 63         |      | Plug N' Play Standard.                                                    |

| SA3    | 64         |      |                                                                           |

| SA4    | 65         |      |                                                                           |

| SA5    | 66         |      |                                                                           |

| SA6    | 67         |      |                                                                           |

| SA7    | 68         |      |                                                                           |

| SA8    | 69         |      |                                                                           |

| SA9    | 70         |      |                                                                           |

| SA10   | 71         |      |                                                                           |

| SA11   | 72         |      |                                                                           |

| SA14   | 73         | I    | ADDRESS BUS: These pins provide address decoding between the 16 Kbyte     |

| SA15   | 74         |      | and 1 Mbyte memory space. This allows for decoding of a Boot EPROM or a   |

| SA16   | 75         |      | FLASH in 16K increments.                                                  |

| SA17   | 76         |      |                                                                           |

| SA18   | 77         |      |                                                                           |

| SA19   | 78         |      |                                                                           |

## 2.1 ISA Bus Interface (Continued)

| Symbol     | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                       |

|------------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD0        | 81         | 1/0  | DATA BUS: This is the data interface between the 82595FX and the host                                                                                                                                                                   |

| SD1        | 83         |      | system. This data is buffered by one (8-bit design) or two (16-bit design)                                                                                                                                                              |

| SD2        | 85         |      | internal transceivers.                                                                                                                                                                                                                  |

| SD3        | 87         |      |                                                                                                                                                                                                                                         |

| SD4        | 88         |      |                                                                                                                                                                                                                                         |

| SD5        | 90         |      |                                                                                                                                                                                                                                         |

| SD6<br>SD7 | 92<br>94   |      |                                                                                                                                                                                                                                         |

| SD8        | 60         |      |                                                                                                                                                                                                                                         |

| SD9        | 58         |      |                                                                                                                                                                                                                                         |

| SD10       | 56         |      |                                                                                                                                                                                                                                         |

| SD11       | 54         |      |                                                                                                                                                                                                                                         |

| SD12       | 53         |      |                                                                                                                                                                                                                                         |

| SD13       | 51         |      |                                                                                                                                                                                                                                         |

| SD14       | 49         |      |                                                                                                                                                                                                                                         |

| SD15       | 47         |      |                                                                                                                                                                                                                                         |

| AEN        | 24         | ı    | ADDRESS ENABLE: Active high signal indicates a DMA cycle is active.                                                                                                                                                                     |

| SMEMR      | 20         | I    | MEMORY READ for system memory accesses below 1 Mbyte. Active low.                                                                                                                                                                       |

| SMEMW      | 21         | I    | MEMORY WRITE for system memory accesses below 1 Mbyte. Active low.                                                                                                                                                                      |

| ĪŌR        | 22         | I    | IO READ: Active low.                                                                                                                                                                                                                    |

| ĪŌW        | 23         | I    | IO WRITE: Active low.                                                                                                                                                                                                                   |

| IOCS16     | 45         | 0    | IO CHIP SELECT 16: Active low, open drain output which indicates that an IO cycle access to the 82595FX solution is 16-bit wide. Driven for IO cycles to the local memory or to the 82595FX.                                            |

| IOCHRDY    | 42         | 0    | <b>IO CHANNEL READY:</b> Active high, open drain output. When driven low, it extends host cycles to the 82595FX solution.                                                                                                               |

| SBHE       | 37         | I    | SYSTEM BUS HIGH ENABLE: Active low input indicates a data transfer on the high-byte (D8-D15) of the system bus (a 16-bit transfer). This pin also determines if the 82595FX is operating in an 8- or 16-bit system upon initialization. |

| INT0       | 29         | 0    | 82595FX INTERRUPT 0-7: One of these 8 pins is selected to be active                                                                                                                                                                     |

| INT1       | 30         |      | one at a time (the other seven are in Hi-Z state) by configuration. These                                                                                                                                                               |

| INT2       | 31         |      | active high outputs serve as interrupts to the host system.                                                                                                                                                                             |

| INT3       | 32         |      |                                                                                                                                                                                                                                         |

| INT4       | 33         |      |                                                                                                                                                                                                                                         |

| INT5       | 34         |      |                                                                                                                                                                                                                                         |

| INT6       | 35         |      |                                                                                                                                                                                                                                         |

| INT7       | 36         |      |                                                                                                                                                                                                                                         |

| RESET DRV  | 19         | I    | RESET DRIVE: Active high reset signal.                                                                                                                                                                                                  |

## 2.2 Local Memory Interface

| Symbol           | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                            |

|------------------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LADDR0           | 143        | 0    | LOCAL MEMORY ADDRESS (LADDR0-LADDR15): These outputs                                                                                                                                                         |

| LADDR1           | 144        |      | contain the multiplexed address for the local SRAM.                                                                                                                                                          |

| LADDR2           | 145        |      | FLASH ADDRESS 14-17 (LADDR0-LADDR5): These pins control the                                                                                                                                                  |

| LADDR3           | 146        |      | FLASH addressing from 16K to 1M to allow paging of the FLASH in 16K                                                                                                                                          |

| LADDR4           | 147        |      | spaces. These addresses are under direct control of the FLASH PAGING                                                                                                                                         |

| LADDR5           | 148<br>149 |      | configuration register.                                                                                                                                                                                      |

| LADDR6<br>LADDR7 | 150        |      |                                                                                                                                                                                                              |

| LADDR7           | 153        |      |                                                                                                                                                                                                              |

| LADDR9           | 154        |      |                                                                                                                                                                                                              |

| LADDR10          | 155        |      |                                                                                                                                                                                                              |

| LADDR11          | 156        |      |                                                                                                                                                                                                              |

| LADDR12          | 157        |      |                                                                                                                                                                                                              |

| LADDR13          | 158        |      |                                                                                                                                                                                                              |

| LADDR14          | 159        |      |                                                                                                                                                                                                              |

| LADDR15          | 2          |      |                                                                                                                                                                                                              |

| LDATA0           | 132        | 1/0  | LOCAL MEMORY DATA BUS (LDATA0-LDATA7): The eight I/O                                                                                                                                                         |

| LDATA1           | 133        |      | signals, comprising the local data bus, are used to read or write data to or                                                                                                                                 |

| LDATA2           | 134        |      | from the 8-bit wide SRAM.                                                                                                                                                                                    |

| LDATA3           | 135        |      | FLASH MEMORY DATA BUS (LDATA0-LDATA7): These signals also                                                                                                                                                    |

| LDATA4           | 137        |      | provide eight bits of data for accesses to an 8-bit FLASH/EPROM if these                                                                                                                                     |

| LDATA5           | 138        |      | components are used.                                                                                                                                                                                         |

| LDATA6           | 139        |      |                                                                                                                                                                                                              |

| LDATA7           | 140        |      |                                                                                                                                                                                                              |

| SRAMCS           | 13         | 0    | <b>SRAM CHIP SELECT:</b> This active low output is the chip select to the SRAM.                                                                                                                              |

| <u>LWE</u>       | 12         | 0    | This active low output is the <b>Write Enable</b> to the SRAM.                                                                                                                                               |

|                  |            |      | This pin also provides the active low Write Enable to the FLASH.                                                                                                                                             |

| LOE              | 16         | 0    | This active low output is the <b>Output Enable</b> to the SRAM.                                                                                                                                              |

|                  |            |      | This pin also provides the active low <b>Output Enable</b> control to the <b>FLASH.</b>                                                                                                                      |

| BOOTCS           | 10         | 0    | BOOT EPROM/FLASH CHIP SELECT: Active low output.                                                                                                                                                             |

| EEPROMCS         | 8          | 1/0  | <b>EEPROM CS:</b> Active high signal. If no EEPROM is connected, this pin should be connected to $V_{\rm CC}$ . In this case it will function as an input to the 82595FX to indicate no EEPROM is connected. |

| EEPROMSK         | 117        | 0    | <b>EEPROM SHIFT CLOCK:</b> This output is used to shift data into and out of the serial EEPROM.                                                                                                              |

| EEPROMDO         | 119        | 0    | EEPROM DATA OUT                                                                                                                                                                                              |

| EEPROMDI         | 118        | 0    | EEPROM DATA IN                                                                                                                                                                                               |

## 2.4 Miscellaneous Control

| Symbol | Pin<br>No. | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                             | Name and Function                                                               |          |                     |  |  |  |

|--------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------|---------------------|--|--|--|

| SMOUT  | 18         | 1/0  | This active LOW signal, when asserted, places the 82595FX into a Power Down mode. The 82595FX will remain in power down mode until SMOUT is unasserted. If this line is unconnected to SMOUT from the system bus, it can be used as an active low output which, when a POWER DOWN command is issued to the 82595FX, can be used to power down other external components (this output function is enabled by configuration). |                                                                                 |          |                     |  |  |  |

| J0     | 119        | I    | JUMPER: Input for selecting between 7 ISA IO spaces. These pins should be                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |          |                     |  |  |  |

| J1     | 118        | I    | connected t                                                                                                                                                                                                                                                                                                                                                                                                                 | connected to either V <sub>CC</sub> or GND or the EEPROM. The 82595FX reads the |          |                     |  |  |  |

| J2     | 117        | I    | Jumper bloc                                                                                                                                                                                                                                                                                                                                                                                                                 | Jumper block during its initialization sequence.                                |          |                     |  |  |  |

|        |            |      | J0                                                                                                                                                                                                                                                                                                                                                                                                                          | J1                                                                              | J2       | IO Address          |  |  |  |

|        |            |      | Connect                                                                                                                                                                                                                                                                                                                                                                                                                     | Connected to EEPROM Configuration contained in EEPROM                           |          |                     |  |  |  |

|        |            |      | GND                                                                                                                                                                                                                                                                                                                                                                                                                         | GND                                                                             | GND      | I/O Window Disabled |  |  |  |

|        |            |      | Vcc                                                                                                                                                                                                                                                                                                                                                                                                                         | GND                                                                             | GND      | 2A0h                |  |  |  |

|        |            |      | GND                                                                                                                                                                                                                                                                                                                                                                                                                         | $V_{CC}$                                                                        | GND      | 280h                |  |  |  |

|        |            |      | Vcc                                                                                                                                                                                                                                                                                                                                                                                                                         | $V_{CC}$                                                                        | GND      | 340h                |  |  |  |

|        |            |      | GND                                                                                                                                                                                                                                                                                                                                                                                                                         | GND                                                                             | $V_{CC}$ | 300h                |  |  |  |

|        |            |      | V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                             | GND                                                                             | $V_{CC}$ | 360h                |  |  |  |

|        |            |      | GND                                                                                                                                                                                                                                                                                                                                                                                                                         | $V_{CC}$                                                                        | $V_{CC}$ | 350h                |  |  |  |

|        |            |      | V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                             | $V_{CC}$                                                                        | $V_{CC}$ | 330h                |  |  |  |

## 2.4 JTAG Control

|        | - Tracontrol |      |                       |  |  |  |  |

|--------|--------------|------|-----------------------|--|--|--|--|

| Symbol | Pin<br>No.   | Туре | Name and Function     |  |  |  |  |

| TDO    | 109          | 0    | JTAG TEST DATA OUT    |  |  |  |  |

| TMS    | 110          | ı    | JTAG TEST MODE SELECT |  |  |  |  |

| TCK    | 111          | ı    | JTAG TEST CLOCK       |  |  |  |  |

| TDI    | 112          | I    | JTAG TEST DATA IN     |  |  |  |  |

## 2.5 Serial Interface

| Symbol | Pin<br>No. | Туре | Name and Function                                                                                                                                         |

|--------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

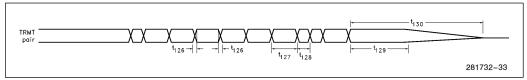

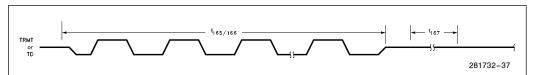

| TRMT   | 122        | 0    | Positive side of the differential output driver pair that drives 10 Mb/s Manchester Encoded data on the TRMT pair of the AUI cable (Data Out A).          |

| TRMT   | 123        | 0    | Negative side of the differential output driver pair that drives 10 Mb/s Manchester Encoded data on the TRMT pair of the AUI cable (Data Out B).          |

| RCV    | 115        | Ì    | The positive input to a differential amplifier connected to the RCV pair of the AUI cable (Data In A). It is driven with 10 Mb/s Manchester Encoded data. |

## 2.5 Serial Interface (Continued)

| Symbol | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                                                  |

|--------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCV    | 116        | I    | The negative input to a differential amplifier connected to the RCV pair of the AUI cable (Data In B). It is driven with 10 Mb/s Manchester Encoded data.                                                                                                                                          |

| CLSN   | 124        | I    | The positive input to a differential amplifier connected to the CLSN pair of the AUI cable (Collision In A).                                                                                                                                                                                       |

| CLSN   | 125        | I    | The negative input to a differential amplifier connected to the CLSN pair of the AUI cable (Collision In B).                                                                                                                                                                                       |

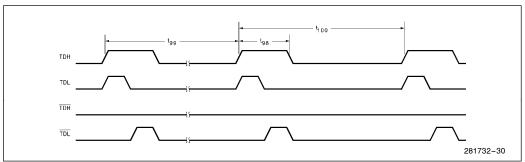

| TDH    | 105        | 0    | TRANSMIT DATA HIGH: Active high Manchester Encoded data to be transmitted onto the twisted pair. This signal is used in conjunction with TDL, TDH, and TDL to generate the pre-conditioned twisted pair output waveform.                                                                           |

| TDL    | 106        | 0    | TRANSMIT DATA LOW: Twisted Pair Output Driver. Active high Manchester Encoded data with embedded pre-distortion information to be transmitted onto the twisted pair. This signal is used in conjunction with TDH, TDH, and TDL to generate the pre-conditioned twisted pair output waveform.       |

| TDH    | 103        | 0    | <b>TRANSMIT DATA HIGH INVERT:</b> Active low Manchester Encoded data to be transmitted onto the twisted pair. This signal is used in conjunction with TDL, TDH, and TDL to generate the pre-conditioned twisted pair output waveform.                                                              |

| TDL    | 104        | 0    | TRANSMIT DATA LOW INVERT: Twisted Pair Output Driver. Active low Manchester Encoded data with embedded pre-distortion information to be transmitted onto the twisted pair. This signal is used in conjunction with TDL, TDH, and TDH to generate the pre-conditioned twisted pair output waveform. |

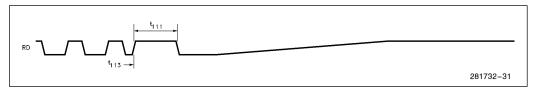

| RD     | 114        | I    | Active high Manchester Encoded data received from the twisted pair.                                                                                                                                                                                                                                |

| RD     | 113        | ı    | Active low Manchester Encoded data received from the twisted pair.                                                                                                                                                                                                                                 |

| X1     | 127        | l    | <b>20 MHz CRYSTAL INPUT:</b> This pin can be driven with an external MOS level clock when X2 is left floating. This input provides the timing for all of the 82595FX functional blocks.                                                                                                            |

| X2     | 128        | 0    | 20 MHz CRYSTAL OUTPUT: If X1 is driven with an external MOS level clock, X2 should be left floating.                                                                                                                                                                                               |

## 2.6 Serial Interface LEDs

| Symbol          | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

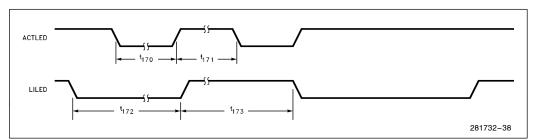

| AUI LED/BNC DIS | 95         | 0    | AUI LED INDICATOR: This output, when the 82595FX is used as a TPE/AUI solution, will turn on an LED when the 82595FX is actively interfaced to its AUI serial port. When the 82595FX is used as a BNC/AUI solution, this output becomes the BNC DIS output, which can be used to power down the BNC Transceiver section (the Transceiver and the DC to DC Converter) of the solution when the BNC port is unconnected. |

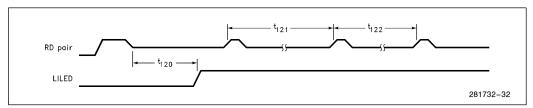

| LILED           | 98         | 0    | LINK INTEGRITY LED: Normally on (low) ouput which indicates a good link integrity status when the 82595FX is connected to an active TPE port. This output will remain on when the Link Integrity function has been disabled. It turns off (driven high) when Link Integrity fails, or when the 82595FX is actively interfaced to an AUI port. The minimum off time is 100 ms.                                          |

## 2.6 Serial Interface LEDs (Continued)

| Symbol | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                        |

|--------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACTLED | 97         | 0    | <b>LINK ACTIVITY LED:</b> Normally off (high) output turns on to indicate activity for transmission, reception, or collision. Flashes at a rate dependent on the level of activity on the link.                                                                          |

| POLED  | 96         | 0    | POLARITY LED: If the 82595FX detects that the receive TPE wires are reversed, the POLED will turn on (low) to indicate the fault. POLED remains on even if automatic polarity correction is enabled, and the 82595FX has automatically corrected for the reversed wires. |

## 2.7 Power and Ground

| Symbol | Pin<br>No.                                                                                                                                                 | Туре | Name and Function       |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------|

| Vcc    | 1, 3, 7, 15,<br>26, 28, 40,<br>43, 46, 50,<br>57, 80, 84,<br>91, 99, 101,<br>107, 121,<br>129, 131,<br>141, 152                                            | l    | <b>POWER</b> : +5V ±5%. |

| Vss    | 4, 6, 9, 11,<br>14, 17, 25,<br>27, 38, 39,<br>41, 44, 48,<br>52, 55, 59,<br>79, 82, 86,<br>89, 93, 100,<br>102, 108,<br>120, 126,<br>130, 136,<br>142, 151 | _    | GROUND: 0V.             |

## 2.8 Reserved Pins

| Symbol | Pin<br>No. | Туре | Name and Function         |

|--------|------------|------|---------------------------|

| N/C    | 5, 160     |      | Reserved. Do not connect. |

## 2.9 82595FX Pin Summary

## ISA Bus Interface

| ISA<br>Pin Name                                                                           | Pin<br>Type | P-Down<br>State                                                                          |

|-------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------|

| SA0-SA3 (In) SA4-SA11 SA14-19 (In) SD0-SD15 (I/O) SMEMR (In) SMEMW (In) IOR (In) IOW (In) | TS          | Inactive Inactive/Act(1) Inactive TS Inactive Inactive Inactive Inactive Inactive/Act(1) |

| INT0-7 (Out)                                                                              | TS          | TS                                                                                       |

| RESET DRV (In) IOCS16 (Out) IOCHRDY (Out) SBHE (In) AEN (In)                              | OD<br>OD    | Act TS TS Inactive Inactive/Act <sup>(1)</sup>                                           |

## NOTE:

1. For hardware powerdown using SMOUT, these pins will be inactive. For software powerdown, these pins remain active.

## **Local Memory Interface**

| Pin<br>Name       | MUXed<br>Name | Pin<br>Type | P-Down |

|-------------------|---------------|-------------|--------|

| LADDR[5:0] (Out)  | FADDR[14:19]  | 2S          | TS     |

| LADDR[6:15] (Out) |               | 2S          | TS     |

| LDATA[0:7] (I/O)  |               | TS          | TS     |

| LWE (Out)         |               | 2S          | TS     |

| LOE (Out)         |               | 2S          | TS     |

| BOOTCS (Out)      |               | 2S          | PU     |

| SRAMCS (Out)      |               | 2S          | PU     |

| EEPROMCS (I/O)    |               | TS          | PD     |

## **Miscellaneous Control**

| Pin Name    | MUXed<br>Pin<br>Name | Pin<br>Type | P-Down<br>State | Dual<br>Pin Name   |  |  |  |  |

|-------------|----------------------|-------------|-----------------|--------------------|--|--|--|--|

| J0(In)      |                      |             | ACT             | EEPROM2D0<br>(In)  |  |  |  |  |

| J1 (I/O)    |                      | TS          | TS              | EEPROM2DI<br>(Out) |  |  |  |  |

| J2 (I/O)    |                      | TS          | TS              | EEPROM2SK          |  |  |  |  |

| SMOUT (I/O) |                      | TS          | ACT/TS          | (Out)              |  |  |  |  |

## **JTAG Control**

| Pin Name  | MUXed<br>Pin Name | Pin<br>Type | P-Down<br>State |

|-----------|-------------------|-------------|-----------------|

| TMS (In)  |                   |             | In Act          |

| TCK (In)  |                   |             | In Act          |

| TDI (In)  |                   |             | In Act          |

| TDO (Out) |                   | TS          |                 |

## **Serial Interface**

| Pin Name     | MUXed<br>Pin Name | Pin<br>Type | P-Down<br>State |

|--------------|-------------------|-------------|-----------------|

| TRMT (Out)   |                   | Ana         | TS              |

| TRMT (Out)   |                   | Ana         | TS              |

| RCV (In)     |                   | Ana         | In Act          |

| RCV (In)     |                   | Ana         | In Act          |

| CLSN (In)    |                   | Ana         | In Act          |

| CLSN (In)    |                   | Ana         | In Act          |

| TDH (Out)    |                   | Ana         | TS              |

| TDL (Out)    |                   | Ana         | TS              |

| TDH (Out)    |                   | Ana         | TS              |

| TDL (Out)    |                   | Ana         | TS              |

| RD (In)      |                   | Ana         | In Act          |

| RD (In)      |                   | Ana         | In Act          |

| X1 (ln)      |                   |             | In Act          |

| X2 (Out)     |                   | 2S          | TS              |

| LILED (Out)  |                   | 2S          | TS*             |

| POLED (Out)  |                   | 2S          | TS*             |

| ACTLED (Out) |                   | 2S          | TS*             |

| AUILED (Out) | BNC DIS (Out)     | 2S          | TS*             |

<sup>\*</sup>Assuming auto-negotiation disabled.

Legend:

TS—TriState.

OD—Open Drain.

2S—Two State, will be found in either a 1 or 0 logic level.

Ana—Analog pin (all serial interface signals).

Act—Input buffer is active during Power Down.

In Act—Input buffer is inactive during Power Down.

PU—Output in inactive state with weak internal Pull-up during Power Down.

PD—Output in inactive state with weak internal Pull-down during Power Down.

Dual—Dual function pin.

## 3.0 82595FX INTERNAL ARCHITECTURE OVERVIEW

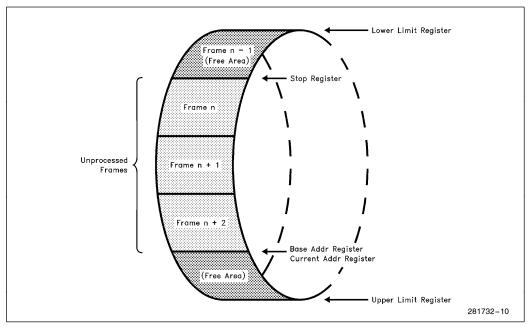

Figure 1 shows a high level block diagram of the 82595FX. The 82595FX is divided into four main subsections; a system interface, a local memory sub-system interface, a CSMA/CD unit, and a serial interface.

## 3.1 System Interface Overview

The 82595FX's system interface subsection includes a glueless ISA bus interface, and the 82595FX's IO registers (including the 82595FX's command, status, and Data In/Out registers). The system interface block also interfaces with the 82595FX's local memory interface subsystem and CSMA/CD subsystem.

The bus interface logic provides the control, address, and data interface to an ISA compatible bus. The 82595FX decodes up to 1M of total memory address space. Address decoding within 16K block increments (A14–A19) are used for Flash or Boot EPROM. IO accesses are decoded throughout the 1 Kbyte PC IO address range (A10 and A11 provide up to 4K of IO addressing and are used for Plug N' Play). The 82595FX data bus interface provides either an 8- or 16-bit interface to the host system's data bus. The control interface provides complete handshaking interface with the system bus to enable transfer of data between the 82595FX solution and the host system.

The 82595FX's IO registers provide 3 banks of directly addressable registers which are used as the control and data interface to the 82595FX. There are 16 IO registers per bank, with only one bank enabled at a time. This allows the complete 82595FX software interface to be contained in one 16-byte IO space. The base address of this IO space is selectable via either software (which can be stored in a serial EEPROM), or by strapping the 82595FX IO Jumper block (J0-J2). The 82595FX can also detect conflicts to its base IO space, and automatically resolve these conflicts either by allowing the selection of one Plug N' Play card from multiple cards (using Plug N' Play software), or by mapping itself into an un-used IO space (Automatic IO Resolution). Included in the 82595FX IO registers are the Command Register, the Status Register, and the Local Memory IO Port register, which provides the data interface to the local SRAM buffer contained in an 82595FX solution. Functions such as IO window mapping, Interrupt enable, RCV and XMT buffer initialization, etc. are also configured and controlled through the IO registers.

## 3.1.1 CONCURRENT PROCESSING FUNCTIONALITY

The 82595FX's Concurrent Processing feature significantly enchances data throughput performance by performing both system bus and serial link activities concurrently. Transmission of a frame is started by the 82595FX before that frame is completely copied into local memory. During reception, a frame is processed by the host CPU before that frame is entirely copied to local memory. Transmit Concurrent Processing feature is enabled by writing to BANK 2, Register 1, Bit 0. A 1 written to this bit enables this functionality, a 0 (default) disables it. To enable Receive Concurrent Processing, BANK 1, Register 7 must be programmed to value other than 00h (00h disables RCV Concurrent Processing, and is default). (See Section 4.1 for the format of IO BANK 1 and 2.) Improvements in concurrent processing functionality have allowed the 82595FX to include enhancements to the throughput efficiency of the 82595TX. For details, refer to the 82595FX User's Guide. Concurrent Processing is not recommended for 8-bit interfaces. For more information on Transmit and Receive Concurrent Processing, refer to Section 7.0 and Section 8.0.

## 3.2 Local Memory Interface

The 82595FX's local memory interface includes a DMA unit which controls data transfers to or from the 82595FX's local SRAM, control for access to a Boot EPROM/FLASH, and two interfaces to a serial EEPROM. The local memory interface subsection also arbitrates accesses to the local memory by the host CPU and the 82595FX.

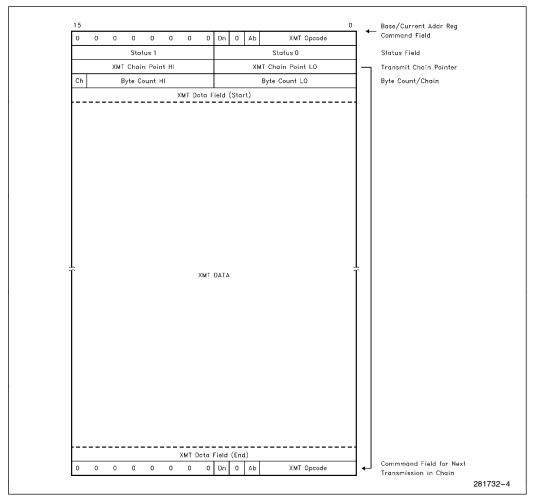

Data transfers between the 82595FX and the local SRAM are always through the 82595FX's Local Memory 16-bit/32-bit IO Port. This allows the entire SRAM memory (up to 64 Kbytes) to be mapped into one IO location in the host systems IO map. By setting a configuration bit in the 82595FX's IO Registers (32IO/HAR#), the local memory can be extended from 16 bits to a full 32 bits. During 32-bit accesses, the CPU would perform a doubleword access addressed to register 12 of BANKO. The ISA bus will break this access up into two 16-bit accesses to Registers 12/13 followed by Registers 14/15, (or 4 sequential 8-bit accesses in an 8-bit interface). The CPU always accesses the 82595FX IO Port for Receive or Transmit data transfers, while the 82595FX automatically increments the address to the SRAM after each CPU access. The SRAMs data path is an 8-bit interface (typically 64K by 8-bits wide, or 256K by 8-bits wide) to allow for the lowest possible solution cost. The 82595FX implements a

prefetch mechanism to the local SRAM so that the data is always available to the CPU as either an 8- or 16-bit word. In the case of the CPU reading from the SRAM, the 82595FX reads the next two bytes from the SRAM, the 82595FX between CPU cycles so that the data is always available as a word in the 82595FX's Local Memory IO Port register. In the case of the CPU writing to the SRAM, the data is written into the 82595FX's Local Memory IO Port then transferred to the SRAM by the 82595FX between CPU cycles. This prefetch mechanism of the 82595FX allows for IO read and writes to the local memory to be performed with no additional waitstates (3 clocks per data transfer cycle).

The DMA unit provides addressing and control to move RCV or XMT data between the 82595FX and the local SRAM. For transmission, the CPU is reguired only to copy the data to the local memory, initialize the 82595FX's DMA Current Address Register (CAR) to point to the beginning of the frame, and issue a Transmit Command to the 82595FX. The DMA unit facilitates the transfers from the local memory to the 82595FX as transmission takes place. The DMA unit will reset upon collision during a transmission, enabling automatic re-transmission of the transmit frame. During reception, the DMA unit implements a recyclable ring buffer structure which can receive continuous back to back frames without CPU intervention on a per frame basis (see Section 8.2 for details).

The 82595FX provides address decoding and control to allow access to an external Boot EPROM/FLASH if these components are utilized in an 82595FX design. The 82595FX also provides an interface to a serial EEPROM to replace jumper blocks used to contain configuration information. This port is used to store configuration information and in addition, it is used to store Plug N' Play information as defined in the Plug N' Play Specification.

The 82595FX arbitrates accesses to the local memory sub-system by the CPU and the 82595FX. The arbitration unit will hold off an 82595FX DMA cycle to the local memory if a CPU cycle is already in progress. Likewise, it will hold off the CPU if an 82595FX cycle is already in progress. The cycle which is held off will be completed on termination of the preceding cycle.

## 3.3 CSMA/CD Unit

The CSMA/CD unit implements the IEEE 802.3 CSMA/CD protocol. It performs such functions as transmission deferral to link traffic, interframe spacing, exponential backoff for collision handling, address recognition, etc. The CSMA/CD unit serves as the interface between the local memory and the serial interface. It serializes data transferred from the local memory before it is passed to the serial interface unit for transmission. During frame reception, it converts the serial data received from the serial interface to a byte format before it is transferred to local memory. The CSMA/CD unit strips framing parameters such as the Preamble and SFD fields before the frame is passes to memory for reception. For transmission, the CSMA/CD unit builds the frame format before the frame is passed to the serial interface for transmission.

## 3.4 Serial Interface

The 82595FX's serial interface provides either an AUI port interface or a Twisted Pair Ethernet (TPE) interface. The AUI port can be connected to an Ethernet Transceiver cable drop to provide a fully compliant IEEE 802.3 AUI interface. The AUI port can also interface to a transceiver device to provide a fully compliant IEEE 802.3 10BASE2 (Cheapernet) interface. The TPE port provides a fully compliant 10BASE-T interface. The 82595FX automatically enables either to the AUI or TPE interface depending on which medium is connected to the chip. Software configuration can override this automatic selection.

## 4.0 ACCESSING THE 82595FX

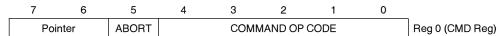

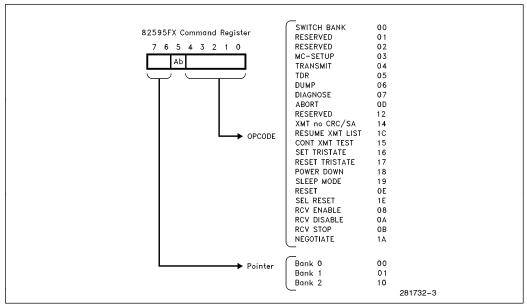

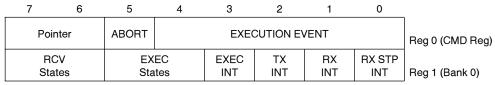

All access to the 82595FX is made through one of three banks of IO registers. Each bank contains 16 registers. Each register in a bank is directly accessible via addressing. Through the use of bank switching, the 82595FX utilizes only 16 IO locations in the host system's IO map to access each of its registers. The different banks are accessed by setting the POINTER field in the 82595FX Command Register to select each bank. The Command Register is Register for each bank.

## 4.1 82595FX Register Map

The 82595FX registers are contained in three banks of 16 IO registers per bank. These three banks are shown in the following three pages.

## 4.1.1 IO BANK 0

The format for IO Bank 0 is shown below.

| 7                                                 | 6                                                   | 5                     | 4                   | 3              | 2          | 1                     | 0              |        |

|---------------------------------------------------|-----------------------------------------------------|-----------------------|---------------------|----------------|------------|-----------------------|----------------|--------|

| POIN                                              | NTER                                                | ABORT COMMAND OP CODE |                     |                |            | Reg 0<br>(CMD<br>Reg) |                |        |

|                                                   | CV<br>ites                                          |                       | EC<br>ites          | EXEC<br>INT    | TX<br>INT  | RX<br>INT             | RX STP<br>INT  | Reg 1  |

| (Cou                                              | ınter)                                              | ID REG                | GISTER<br>(Auto En) | 0              | 1          | 0<br>RESE             | 0<br>ERVED     | Reg 2  |

| 0<br>Resvrd                                       | 0<br>Resvrd                                         | Cur/<br>Base          | 32 IO/<br>HAR       | EXEC<br>Mask   | TX<br>Mask | RX<br>Mask            | RX STP<br>Mask | Reg 3  |

|                                                   |                                                     |                       |                     | AR/BAR<br>ow)  |            | •                     | 1              | Reg 4  |

|                                                   |                                                     |                       |                     | AR/BAR<br>igh) |            |                       |                | Reg 5  |

|                                                   |                                                     |                       |                     | OP REG<br>ow)  |            |                       |                | Reg 6  |

|                                                   |                                                     |                       |                     | OP REG<br>igh) |            |                       |                | Reg 7  |

|                                                   |                                                     | I                     | RCV Copy Th         | nreshold REC   | à          |                       |                | Reg 8  |

|                                                   |                                                     | EARLY XI              | MT THRESH           | OLD REGIST     | ΓER (XTR)  |                       |                | Reg 9  |

|                                                   |                                                     |                       |                     | AR/BAR<br>ow)  |            |                       |                | Reg 10 |

|                                                   |                                                     |                       |                     | AR/BAR<br>igh) |            |                       |                | Reg 11 |

|                                                   | Host Address Reg (Low) /32-Bit I/O (Byte 0)         |                       |                     |                |            |                       |                | Reg 12 |

|                                                   | Host Address Reg (High)<br>/32-Bit I/O (Byte 1)     |                       |                     |                |            |                       |                | Reg 13 |

|                                                   | Local Memory I/O Port (Low)<br>/32-Bit I/O (Byte 2) |                       |                     |                |            |                       | Reg 14         |        |

| Local Memory I/O Port (High) /32-Bit I/O (Byte 3) |                                                     |                       |                     |                |            |                       | Reg 15         |        |

| 732-bit 170 (byte 3)                              |                                                     |                       |                     |                |            |                       |                |        |

## 4.1.2 IO BANK 1

The format for IO Bank 1 is shown below.

| 7                | 6            | 5                         | 4            | 3                    | 2               | 1              | 0           |                       |

|------------------|--------------|---------------------------|--------------|----------------------|-----------------|----------------|-------------|-----------------------|

| POIN             | ITER         | ABORT                     |              | COMMAND OP CODE      |                 |                |             | Reg 0<br>(CMD<br>Reg) |

| Tri-ST<br>INT    | 0<br>Resvrd  | 0<br>Resvrd               | 0<br>Resvrd  | 0<br>Resvrd          | 0<br>Resvrd     | Host<br>Bus Wd | 0<br>Resvrd | Reg 1                 |

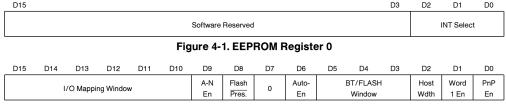

| FL/BT<br>Present |              | : EPROM/FL<br>ecode Windo |              | Bad<br>IRQ           |                 | INT Select     |             | Reg 2                 |

| 0                | 0            |                           |              |                      | apping<br>dow   |                |             | Reg 3                 |

| 0                | 0            | 0                         | 0<br>(Rese   | 0<br>erved)          | 0               | 0              | 0           | Reg 4                 |

| 0                | 0            | 0                         | 0<br>(Rese   | 0<br>erved)          | 0               | 0              | 0           | Reg 5                 |

|                  |              | BAG                       | CK TO BACK   | TRANSMIT             | IFS             |                |             | Reg 6                 |

|                  |              |                           | RCV BOF Th   | reshold REG          | ì               |                |             | Reg 7                 |

|                  |              |                           |              | R LIMIT REG<br>Byte) |                 |                |             | Reg 8                 |

|                  |              |                           |              | R LIMIT REG<br>Byte) |                 |                |             | Reg 9                 |

|                  |              |                           |              | R LIMIT REG<br>Byte) |                 |                |             | Reg 10                |

|                  |              |                           |              | R LIMIT REG<br>Byte) |                 |                |             | Reg 11                |

| FLASH<br>SELECT  | PAGE<br>HIGH |                           | WRITE<br>BLE |                      |                 | I PAGE<br>ECT  |             | Reg 12                |

| 0                | 0<br>(Rese   | 0<br>erved)               | 0            | 0                    | SMOUT<br>OUT EN | 0<br>Resvrd    | 0<br>Resvrd | Reg 13                |

| 0                | 0            | 0                         | 0<br>(Rese   | 0<br>erved)          | 0               | 0              | 0           | Reg 14                |

| 0                | 0            | 0                         | 0            | 0<br>erved)          | 0               | 0              | 0           | Reg 15                |

|                  |              |                           | ,            | •                    |                 |                |             |                       |

## 4.1.3 IO BANK 2

The format for IO Bank 2 is shown below.

| 7               | 6                            | 5                | 4                   | 3                   | 2                | 1           | 0                 |                       |

|-----------------|------------------------------|------------------|---------------------|---------------------|------------------|-------------|-------------------|-----------------------|

| POIN            | ITER                         | ABORT            |                     | COM                 | IMAND OP C       | ODE         |                   | Reg 0<br>(CMD<br>Reg) |

| Disc<br>Bad Fr  | Tx Chn<br>ErStp              | Tx Chn<br>Int Md |                     |                     |                  |             | TX Con<br>Proc En | Reg 1                 |

| Loop            | Back                         | Multi<br>IA      | No SA<br>Ins        | Length<br>Enable    | RX CRC<br>In MEM | BC<br>DIS   | PRMSC<br>Mode     | Reg 2                 |

| Test 1          | Test 2                       | BNC/<br>TPE      | APORT               | Jabber<br>Disable   | TPE/<br>AUI      | Pol<br>Corr | Link In<br>Dis    | Reg 3                 |

|                 |                              |                  | INDIVIDUAL<br>REGIS | ADDRESS<br>STER 0   |                  |             |                   | Reg 4                 |

|                 |                              |                  | INDIVIDUAL<br>REGIS | ADDRESS             |                  |             |                   | Reg 5                 |

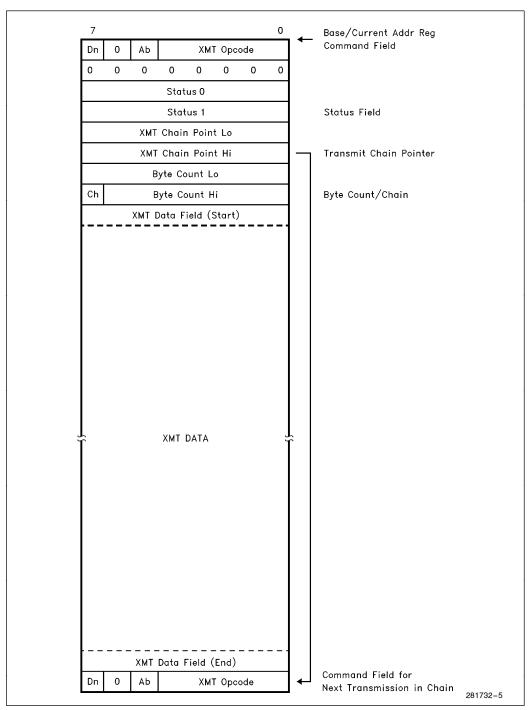

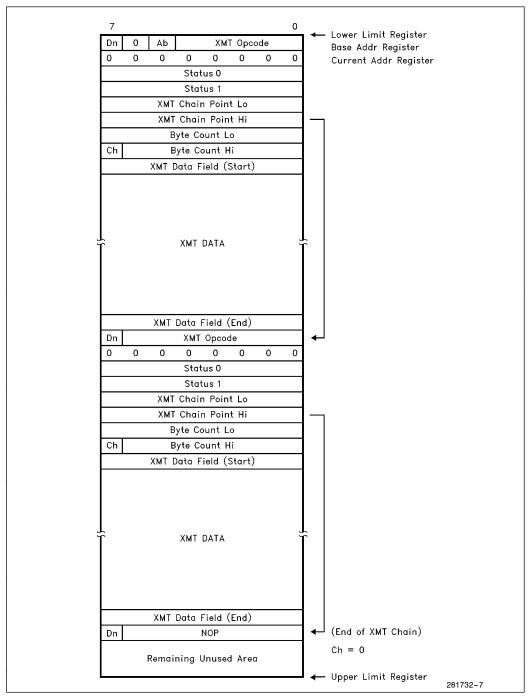

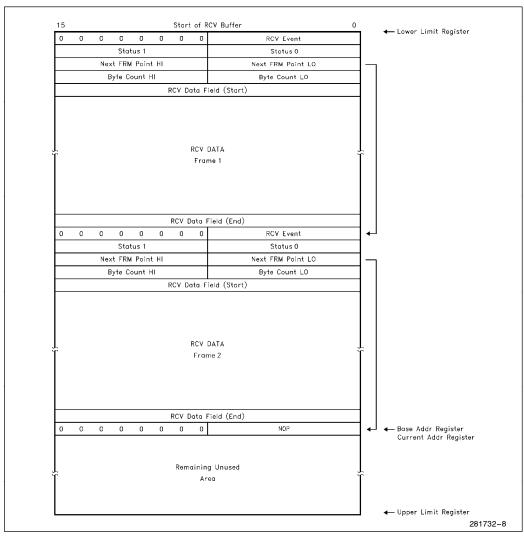

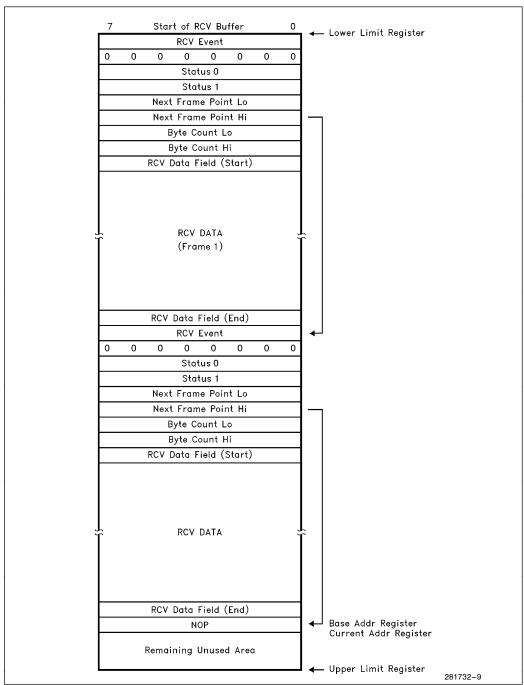

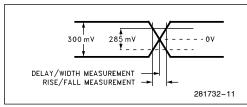

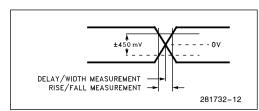

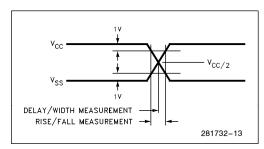

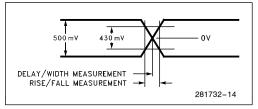

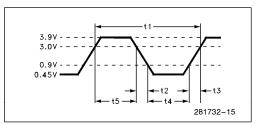

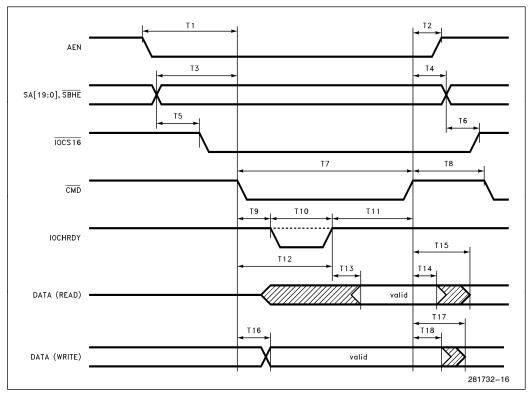

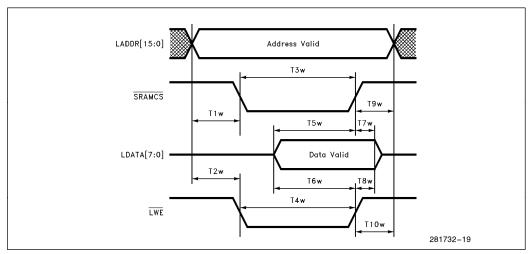

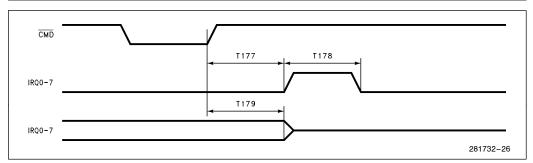

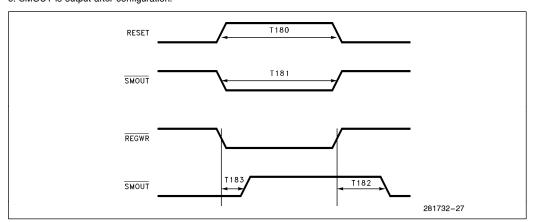

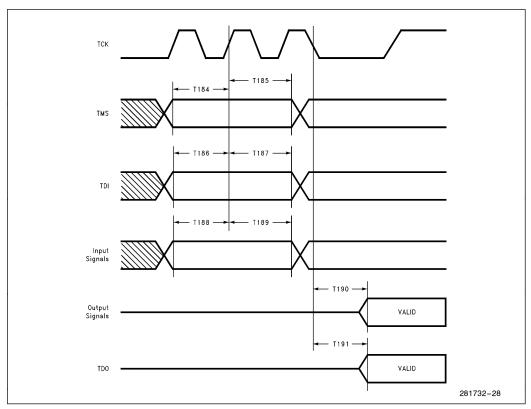

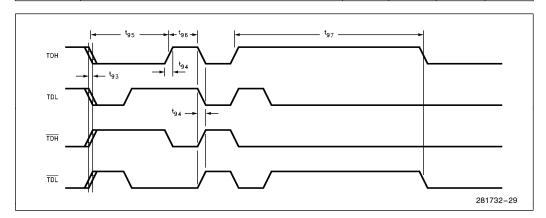

|                 |                              |                  |                     | ADDRESS<br>STER 2   |                  |             |                   | Reg 6                 |