## 82596CA HIGH-PERFORMANCE 32-BIT LOCAL AREA NETWORK COPROCESSOR

- Performs Complete CSMA/CD Medium Access Control (MAC) Functions— Independently of CPU

- IEEE 802.3 (EOC) Frame Delimiting

- Supports Industry Standard LANs

- IEEE TYPE 10BASE-T,

IEEE TYPE 10BASE5 (Ethernet\*),

IEEE TYPE 10BASE2 (Cheapernet),

IEEE TYPE 1BASE5 (StarLAN),

and the Proposed Standard

10BASE-F

- Proprietary CSMA/CD Networks Up to 20 Mb/s

- On-Chip Memory Management

- Automatic Buffer Chaining

- Buffer Reclamation after Receipt of Bad Frames; Optional Save Bad Frames

- 32-Bit Segmented or Linear (Flat) Memory Addressing Formats

- Network Management and Diagnostics

- Monitor Mode

- 32-Bit Statistical Counters

- 82586 Software Compatible

- Self-Test Diagnostics

- Optimized CPU Interface

- Optimized Bus Interface to Intel's i486TMDX, i486TMSX, i487TMSX and 80960CA Processors

- 33 MHz, 25 MHz, 20 MHz and 16 MHz Clock Frequencies

- Supports Big Endian and Little Endian Byte Ordering

- 32-Bit Bus Master Interface

- 106 MB/s Bus Bandwidth

- Burst Bus Transfers

- Bus Throttle Timers

- Transfers Data at 100% of Serial

Bandwidth

- 128-Byte Receive FIFO, 64-Byte Transmit FIFO

- Configurable Initialization Root for Data Structures

- High-Speed, 5V, CHMOS\*\* IV Technology

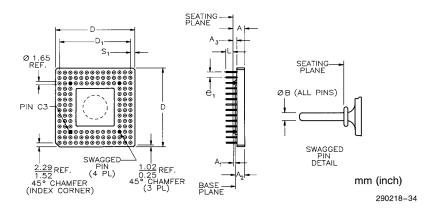

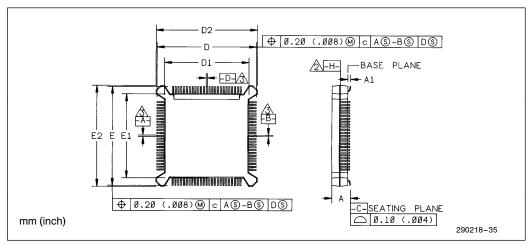

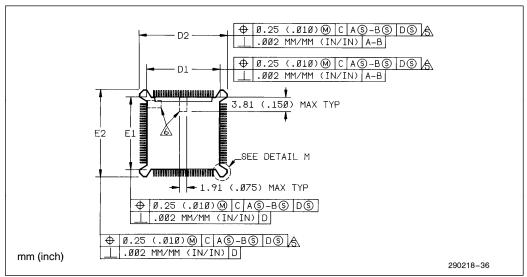

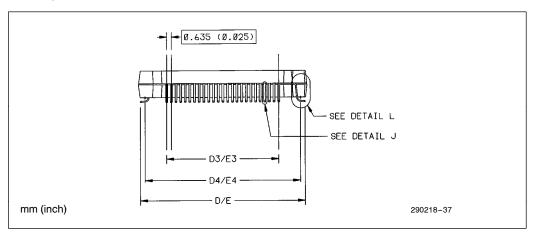

- 132-Pin Plastic Quad Flat Pack (PQFP) and PGA Package

(See Packaging Spec Order No. 240800-001, Package Type KU and A)

i486 is a trademark of Intel Corporation.

\*Ethernet is a registered trademark of Xerox Corporation.

\*\*CHMOS is a patented process of Intel Corporation.

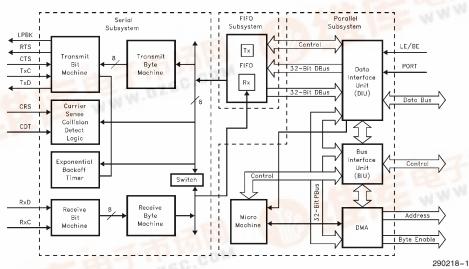

Figure 1. 82596CA Block Diagram

\*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

COPYRIGHT © INTEL CORPORATION, 1996

October 1995

Order Number: 290218-006

## 82596CA High-Performance 32-Bit Local Area Network Coprocessor

| <b>CONTENTS</b> PAGE                         | <b>CONTENTS</b> PA                                      | AGE |

|----------------------------------------------|---------------------------------------------------------|-----|

| INTRODUCTION 3                               | SYSTEM CONTROL BLOCK (SCB)                              | 27  |

| PIN DESCRIPTIONS 7                           | SCB OFFSET ADDRESSES                                    | 30  |

| 82596 AND HOST CPU<br>INTERACTION11          | CBL Offset (Address)                                    |     |

| <b>82596 BUS INTERFACE</b>                   | SCB STATISTICAL COUNTERS                                | 31  |

| <b>82596 MEMORY ADDRESSING</b> 11            | Statistical Counter Operation                           | 31  |

| 82596 SYSTEM MEMORY STRUCTURE                | ACTION COMMANDS AND OPERATING MODES                     |     |

| TRANSMIT AND RECEIVE MEMORY STRUCTURES14     | NOP                                                     | 33  |

| TRANSMITTING FRAMES 17                       | Configure                                               |     |

| RECEIVING FRAMES                             | Transmit                                                |     |

| 82596 NETWORK MANAGEMENT AND DIAGNOSTICS18   | Jamming Rules TDR                                       |     |

| NETWORK PLANNING AND MAINTENANCE             | Dump Diagnose                                           |     |

| STATION DIAGNOSTICS AND SELF-                | RECEIVE FRAME DESCRIPTOR                                | 50  |

| <b>TEST</b> 21                               | Simplified Memory Structure                             | 50  |

| 82586 SOFTWARE COMPATIBILITY 21              | Flexible Memory Structure                               |     |

| INITIALIZING THE 8259621                     | Receive Buffer Descriptor (RBD)                         | 52  |

| SYSTEM CONFIGURATION POINTER (SCP)           | PGA PACKAGE THERMAL SPECIFICATIONS                      | 57  |

| Writing the Sysbus                           | ELECTRICAL AND TIMING CHARACTERISTICS                   | 57  |

| INTERMEDIATE SYSTEM                          | Absolute Maximum Ratings                                |     |

| CONFIGURATION POINTER (ISCP)23               | DC Characteristics                                      |     |

| INITIALIZATION PROCESS                       | AC Characteristics                                      | 58  |

| CONTROLLING THE 82596CA24                    | 82596CA C-Step Input/Output System Timings              |     |

| 82596 CPU ACCESS INTERFACE<br>(PORT)24       | Transmit/Receive Clock Parameters 82596CA BUS Operation |     |

| MEMORY ADDRESSING FORMATS 24                 | System Interface AC Timing Characteristics              | 67  |

| LITTLE ENDIAN AND BIG ENDIAN BYTE ORDERING25 | Input Waveforms                                         | 68  |

| <b>COMMAND UNIT (CU)</b>                     | OUTLINE DIAGRAMS                                        |     |

| <b>RECEIVE UNIT (RU)</b>                     | REVISION HISTORY                                        |     |

#### INTRODUCTION

The 82596CA is an intelligent, high-performance 32-bit Local Area Network coprocessor. The 82596CA implements the CSMA/CD access method and can be configured to support all existing IEEE 802.3 standards—TYPEs 10BASE-T, 10BASE5, 10BASE2, 1BASE5, and 10BROAD36. It can also be used to implement the proposed standard TYPE 10BASE-F. The 82596CA performs high-level commands, command chaining, and interprocessor communications via shared memory, thus relieving the host CPU of many tasks associated with network control. All time-critical functions are performed independently of the CPU, this increases network performance and efficiency. The 82596CA bus interface is optimized for Intel's i486™SX, i486™DX, i487TMSX, 80960CA, and 80960KB processors.

The 82596CA implements all IEEE 802.3 Medium Access Control and channel interface functions, these include framing, preamble generation and stripping, source address generation, destination address checking, short-frame detection, and automatic length-field handling. Data rates up to 20 Mb/s are supported.

The 82596CA provides a powerful host system interface. It manages memory structures automatically, with command chaining and bidirectional data chaining. An on-chip DMA controller manages four channels, this allows autonomous transfer of data blocks (buffers and frames) and relieves the CPU of byte transfer overhead. Buffers containing errored or collided frames can be automatically recovered without CPU intervention. The 82596CA provides an upgrade path for existing 82586 software drivers by providing an 82586-software-compatible mode that supports the current 82586 memory structure. The 82586CA also has a Flexible memory structure and a Simplified memory structure. The 82596CA can address up to 4 gigabytes of memory. The 82596CA supports Little Endian and Big Endian byte ordering.

The 82596CA bus interface can achieve a burst transfer rate of 106 MB/s at 33 MHz. The bus interface employs bus throttle timers to regulate 82596CA bus use. Two large, independent FIFOs—128 bytes for Receive and 64 bytes for Transmit—tolerate long bus latencies and provide programmable thresholds that allow the user to optimize bus overhead for any worst-case bus latency. The high-performance bus is capable of back-to-back transmission and reception during the IEEE 802.3 9.6- $\mu$ s Interframe Spacing (IFS) period.

The 82596CA provides a wide range of diagnostics and network management functions, these include internal and external loopback, exception condition

tallies, channel activity indicators, optional capture of all frames regardless of destination address (promiscuous mode), optional capture of errored or collided frames, and time domain reflectometry for locating fault points on the network cable. The statistical counters, in 32-bit segmented and linear modes, are 32-bits each and include CRC errors, alignment errors, overrun errors, resource errors, short frames, and received collisions. The 82596CA also features a monitor mode for network analysis. In this mode the 82596CA can capture status bytes, and update statistical counters, of frames monitored on the link without transferring the contents of the frames to memory. This can be done concurrently while transmitting and receiving frames destined for that station.

The 82596CA can be used in both baseband and broadband networks. It can be configured for maximum network efficiency (minimum contention overhead) with networks of any length. Its highly flexible CSMA/CD unit supports address field lengths of zero through six bytes for IEEE 802.3/Ethernet frame delimitation. It also supports 16- or 32-bit cyclic redundancy checks. The CRC can be transferred directly to memory for receive operations, or dynamically inserted for transmit operations. The CSMA/CD unit can also be configured for full duplex operation for high throughput in point-to-point connections.

The 82596 C-step incorporates several new features not found in previous steppings. The following is a summary of the 82596 C-step's new features.

- The 82596 C-step fixes Errata found in the A1 and B steppings.

- The 82596 C-step has improved AC timings over both the A and B steppings.

- The 82596 C-step has a New Enhanced Big Endian Mode where in Linear Addressing Mode, true 32-bit Big Endian functionality is achieved. New Enhanced Big Endian Mode is enabled by setting bit 7 of the SYSBUS byte. This mode is software compatible with the big endian mode of the B-step with one exception—no 32-bit addresses need to be swapped by software in the C-step. In this new mode, the 82596 C-step treats 32-bit address pointers as true 32-bit entities and the SCB absolute address and statistical counters are still treated as two 16-bit big endian entities. Not setting this mode will configure the 82596 C-step to be 100% compatible to the A1-step big endian mode.

- The 82596 C-step is hardware and software compatible to both the A1 and B steppings allowing for easy "drop-in" to current designs. Pinout and control structures remain unchanged.

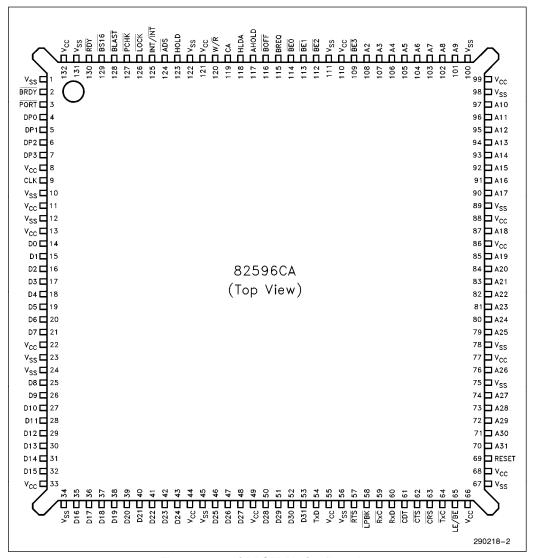

The 82596CA is fabricated with Intel's reliable, 5-V, CHMOS IV (process 648.8) technology. It is available in a 132-pin PQFP or PGA package.

Figure 2. 82596CA PQFP Pin Configuration

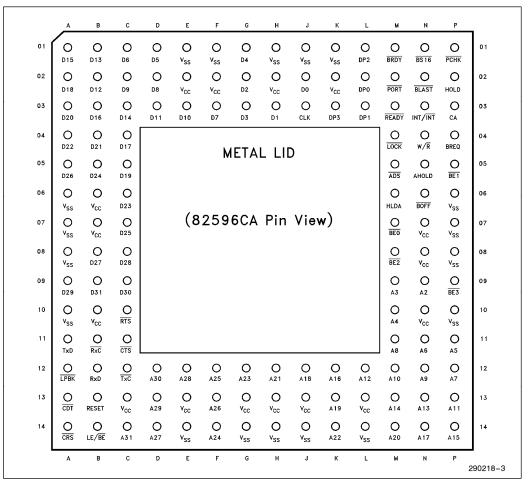

Figure 3. 82596CA PGA Pinout

## 82596CA PGA Cross Reference by Pin Name

| Add    | Iress   | D      | ata     | Con     |         | Serial<br>Interface |         | V <sub>CC</sub> | V <sub>SS</sub> |

|--------|---------|--------|---------|---------|---------|---------------------|---------|-----------------|-----------------|

| Signal | Pin No. | Signal | Pin No. | Signal  | Pin No. | Signal              | Pin No. | Pin No.         | Pin No.         |

| A2     | N9      | D0     | J2      | ADS     | M5      | CDT                 | A13     | B6              | A6              |

| A3     | M9      | D1     | H3      | AHOLD   | N5      | CRS                 | A14     | B7              | A7              |

| A4     | M10     | D2     | G2      | BE0     | M7      | CTS                 | C11     | B10             | A8              |

| A5     | P11     | D3     | G3      | BE1     | P5      | LPBK                | A12     | C13             | A10             |

| A6     | N11     | D4     | G1      | BE2     | M8      | RTS                 | C10     | E2              | E1              |

| A7     | P12     | D5     | D1      | BE3     | P9      | RxC                 | B11     | E13             | E14             |

| A8     | M11     | D6     | C1      | BLAST   | N2      | RxD                 | B12     | F2              | F1              |

| A9     | N12     | D7     | F3      | BOFF    | N6      | TxC                 | C12     | G13             | G14             |

| A10    | M12     | D8     | D2      | BRDY    | M1      | TxD                 | A11     | H2              | H1              |

| A11    | P13     | D9     | C2      | BREQ    | P4      |                     |         | H13             | H14             |

| A12    | L12     | D10    | E3      | BS16    | N1      |                     |         | J13             | J1              |

| A13    | N13     | D11    | D3      | CA      | P3      |                     |         | K2              | J14             |

| A14    | M13     | D12    | B2      | CLK     | J3      |                     |         | L13             | K1              |

| A15    | P14     | D13    | B1      | DP0     | L2      |                     |         | N7              | L14             |

| A16    | K12     | D14    | C3      | DP1     | L3      |                     |         | N8              | P6              |

| A17    | N14     | D15    | A1      | DP2     | L1      |                     |         | N10             | P7              |

| A18    | J12     | D16    | B3      | DP3     | K3      |                     |         |                 | P8              |

| A19    | K13     | D17    | C4      | HLDA    | M6      |                     |         |                 | P10             |

| A20    | M14     | D18    | A2      | HOLD    | P2      |                     |         |                 |                 |

| A21    | H12     | D19    | C5      | INT/INT | N3      |                     |         |                 |                 |

| A22    | K14     | D20    | A3      | LE/BE   | B14     |                     |         |                 |                 |

| A23    | G12     | D21    | B4      | LOCK    | M4      |                     |         |                 |                 |

| A24    | F14     | D22    | A4      | PCHK    | P1      |                     |         |                 |                 |

| A25    | F12     | D23    | C6      | PORT    | M2      |                     |         |                 |                 |

| A26    | F13     | D24    | B5      | READY   | M3      |                     |         |                 |                 |

| A27    | D14     | D25    | C7      | RESET   | B13     |                     |         |                 |                 |

| A28    | E12     | D26    | A5      | W/R     | N4      |                     |         |                 |                 |

| A29    | D13     | D27    | B8      |         |         |                     |         |                 |                 |

| A30    | D12     | D28    | C8      |         |         |                     |         |                 |                 |

| A31    | C14     | D29    | A9      |         |         |                     |         |                 |                 |

|        |         | D30    | C9      |         |         |                     |         |                 |                 |

|        |         | D31    | B9      |         |         |                     |         |                 |                 |

## PIN DESCRIPTIONS

| Symbol  | PQFP<br>Pin No. | Туре |                                               | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |                                            |                                                                    |                                                                                                                                                    |                                                       |  |  |  |

|---------|-----------------|------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

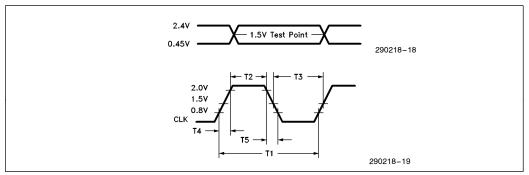

| CLK     | 9               | I    | the 8                                         | <b>CLOCK.</b> The system clock input provides the fundamental timing for the 82596. It is a 1X CLK input used to generate the 82596 clock and requires TTL levels. All external timing parameters are specified in reference to the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                                            |                                                                    |                                                                                                                                                    |                                                       |  |  |  |

| D0-D31  | 14–53           | 1/0  | proving mem is de lines floate write POR addr | DATA BUS. The 32 Data Bus lines are bidirectional, tri-state lines that provide the general purpose data path between the 82596 and memory. With the 82596 the bus can be either 16 or 32 bits wide; this is determined by the \$\overline{BS16}\$ signal. The 82596 always drives all 32 data lines during Write operations, even with a 16-bit bus. D31 – D0 are floated after a Reset or when the bus is not acquired.  These lines are inputs during a CPU Port access; in this mode the CPU writes the next address to the 82596 through the data lines. During \$\overline{PORT}\$ commands (Relocatable SCP, Self-Test, Reset and Dump) the address must be aligned to a 16-byte boundary. This frees the D3-D0 lines so they can be used to distinguish the commands. The following is a summary of the decoding data. |                                                     |                                            |                                                                    |                                                                                                                                                    |                                                       |  |  |  |

|         |                 |      | D0                                            | D1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D2                                                  | D3                                         | D31-D4                                                             | Function                                                                                                                                           |                                                       |  |  |  |

|         |                 |      | 0<br>0<br>1<br>1                              | Reset<br>Relocatable SCP<br>Self-Test<br>Dump Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |                                            |                                                                    |                                                                                                                                                    |                                                       |  |  |  |

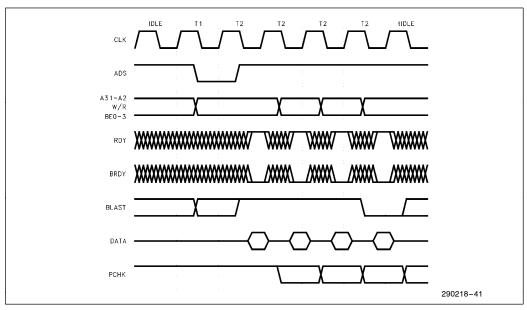

| DP0-DP3 | 4-7             | 1/0  | parity<br>even<br>as da<br>as re              | DATA PARITY. These are tri-stated data parity pins. There is one parity line for each byte of the data bus. The 82596 drives them with even-parity information during write operations having the same timing as data writes. Likewise, even-parity information, with the same timing as read information, must be driven back to the 82596 over these pins to ensure that the correct parity check status is indicated by the                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |                                            |                                                                    |                                                                                                                                                    |                                                       |  |  |  |

| PCHK    | 127             | 0    | Read<br>previous<br>data<br>bytes<br>PCH      | d operatious clo<br>has be<br>s, which<br>K is on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ations of<br>ock cyclen san<br>h are in<br>ly valid | of the policie. When pled. Indicate for on | arity status of<br>en driven low<br>It only check<br>d by the Byte | gh one clock after RE f data sampled at the v it indicates that inco s the parity status of Enable and Bus Size after data read is retu her times. | e end of the<br>prect parity<br>enabled<br>e signals. |  |  |  |

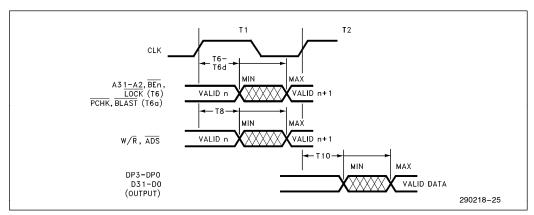

| A31-A2  | 70–108          | 0    | addr                                          | ess bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | s requir                                            | ed for                                     |                                                                    | d Address lines outpuration. These lines arcquired.                                                                                                |                                                       |  |  |  |

| BE3-BE0 | 109-114         | 0    | bytes Byte being  BE  BE  BE                  | BYTE ENABLE. These tri-stated signals are used to indicate which bytes are involved with the current memory access. The number of Byte Enable signals asserted indicates the physical size of the data being transferred (1, 2, 3, or 4 bytes).  • BEO indicates D7-D0  • BE1 indicates D15-D8  • BE2 indicates D23-D16  • BE3 indicates D31-D24 These lines are floated after a Reset or when the bus is not acquired.                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |                                            |                                                                    |                                                                                                                                                    |                                                       |  |  |  |

| W/R     | 120             | 0    | WRI                                           | TE/RE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AD. Th                                              | nis dua                                    | I function pin                                                     | is used to distinguish<br>a Reset or when the                                                                                                      | Write and                                             |  |  |  |

## PIN DESCRIPTIONS (Continued)

| Symbol | PQFP<br>Pin No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADS    | 124             | 0    | ADDRESS STATUS. The 82596 uses this tri-state pin to indicate to indicate that a valid bus cycle has begun and that A31–A2, \$\overline{BE3}\$-\$\overline{BE0}\$, and W/\$\overline{R}\$ are being driven. It is asserted during t1 bus states. This line is floated after a Reset or when the bus is not acquired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

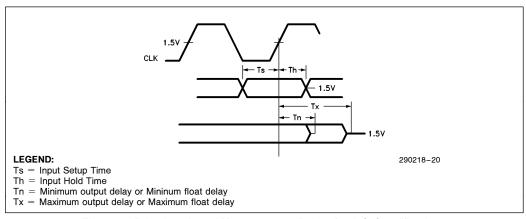

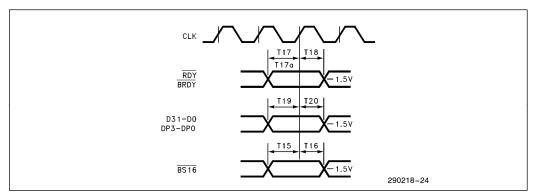

| RDY    | 130             | I    | <b>READY.</b> Active low. This signal is the acknowledgment from addressed memory that the transfer cycle can be completed. When high, it causes wait states to be inserted. It is ignored at the end of the first clock of the bus cycle's data cycle. This active-low signal does not have an internal pull-up resistor. This signal must meet the setup and hold times to operate correctly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BRDY   | 2               | I    | BURST READY. Active low. Burst Ready, like $\overline{\text{RDY}}$ , indicates that the external system has presented valid data on the data pins in response to a Read, or that the external system has accepted the 82596 data in response to a Write request. Also, like $\overline{\text{RDY}}$ , this signal is ignored at the end of the first clock in a bus cycle. If the 82596 can still receive data from the previous cycle, ADS will not be asserted in the next clock cycle; however, Address and Byte Enable will change to reflect the next data item expected by the 82596. $\overline{\text{BRDY}}$ will be sampled during each succeeding clock and if active, the data on the pins will be strobed to the 82596 or to external memory (read/write). $\overline{\text{BRDY}}$ operates exactly like READY during the last data cycle of a burst sequence and during nonburstable cycles. |

| BLAST  | 128             | 0    | BURST LAST. A signal (active low) on this tri-state pin indicates that the burst cycle is finished and when BRDY is next returned it will be treated as a normal ready; i.e., another set of addresses will be driven with ADS or the bus will go idle. BLAST is not asserted if the bus is not acquired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

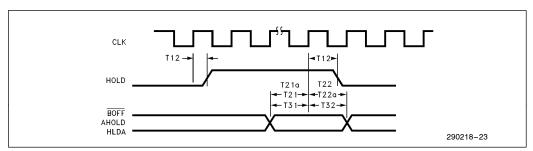

| AHOLD  | 117             | I    | ADDRESS HOLD. This hold signal is active high, it allows another bus master to access the 82596 address bus. In a system where an 82596 and an i486 processor share the local bus, AHOLD allows the cache controller to make a cache invalidation cycle while the 82596 holds the address lines. In response to a signal on this pin, the 82596 immediately (i.e. during the next clock) stops driving the entire address bus (A31–A2); the rest of the bus can remain active. For example, data can be returned for a previously specified bus cycle during Address Hold. The 82596 will not begin another bus cycle while AHOLD is active.                                                                                                                                                                                                                                                               |

| BOFF   | 116             | I    | BACKOFF. This signal is active low, it informs the 82596 that another bus master requires access to the bus before the 82596 bus cycle completes. The 82596 immediately (i.e. during the next clock) floats its bus. Any data returned to the 82596 while BOFF is asserted is ignored. BOFF has higher priority than RDY or BRDY; if two such signals are returned in the same clock period, BOFF is given preference. The 82596 remains in Hold until BOFF goes high, then the 82596 resumes its bus cycle by driving out the address and status, and asserting ADS.                                                                                                                                                                                                                                                                                                                                      |

| LOCK   | 126             | 0    | LOCK. This tri-state pin is used to distinguish locked and unlocked bus cycles. LOCK generates a semaphore handshake to the CPU. LOCK can be active for several memory cycles, it goes active during the first locked memory cycle (t1) and goes inactive at the last locked cycle (t2). This line is floated after a Reset or when the bus is not acquired. LOCK can be disabled via the sysbus byte in software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## PIN DESCRIPTIONS (Continued)

| Symbol  | PQFP<br>Pin No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BS16    | 129             | I    | BUS SIZE. This signal allows the 82596CA to work with either 16- or 32-bit bytes. Inserting BS16 low causes the 82596 to perform two 16-bit memory accesses when transferring 32-bit data. In little endian mode the D15–D0 lines are driven when BS16 is inserted, in Big Endian mode the D31–D16 lines are driven.                                                                                                                                                                                                                                                          |

| HOLD    | 123             | 0    | <b>HOLD.</b> The HOLD signal is active high, the 82596 uses it to request local bus mastership. In normal operation HOLD goes inactive before HLDA. The 82596 can be forced off the bus by deasserting HLDA or if the bus throttle timers expire.                                                                                                                                                                                                                                                                                                                             |

| HLDA    | 118             | I    | HOLD ACKNOWLEDGE. The HLDA signal is active high, it indicates that bus mastership has been given to the 82596. HLDA is internally synchronized; after HOLD is detected low, the CPU drives HLDA low.  NOTE:                                                                                                                                                                                                                                                                                                                                                                  |

|         |                 |      | Do not connect HLDA to V <sub>CC</sub> —it will cause a deadlock. A user wanting to give the 82596 permanent access to the bus should connect HLDA to HOLD. If HLDA goes inactive before HOLD, the 82596 will release the bus (by deasserting HOLD) within a maximum of within a specified number of bus cycles as specified in the 82596 User's Manual.                                                                                                                                                                                                                      |

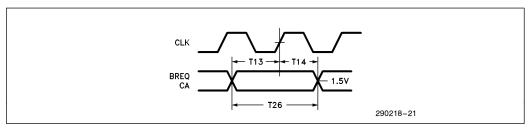

| BREQ    | 115             | I    | BUS REQUEST. This signal, when configured to an externally activated mode, is used to trigger the bus throttle timers.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

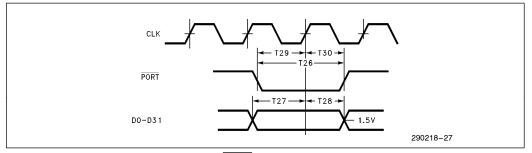

| PORT    | 3               | I    | PORT. When this signal is received, the 82596 latches the data on the data bus into an internal 32-bit register. When the CPU is asserting this signal it can write into the 82596 (via the data bus). This pin must be activated twice during all CPU Port access commands.                                                                                                                                                                                                                                                                                                  |

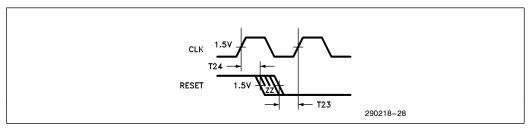

| RESET   | 69              | I    | RESET. This active high, internally synchronized signal causes the 82596 to terminate current activity. The signal must be high for at least five system clock cycles. After five system clock cycles and four TxC clock cycles the 82596 will execute a Reset when it receives a high RESET signal. When RESET returns to low the 82596 waits for the first CA signal and then begins the initialization sequence.                                                                                                                                                           |

| LE/BE   | 65              | I    | LITTLE ENDIAN/BIG ENDIAN. This dual-function pin is used to select byte ordering. When LE/BE is high, little endian byte ordering is used; when low, big endian byte ordering is used for data in frames (bytes) and for control (SCB, RFD, CBL, etc).                                                                                                                                                                                                                                                                                                                        |

| CA      | 119             | I    | CHANNEL ATTENTION. The CPU uses this pin to force the 82596 to begin executing memory resident Command blocks. The CA signal is internally synchronized. The signal must be high for at least one system clock. It is latched internally on the high to low edge and then detected by the 82596.  The first CA after a Reset forces the 82596 into the initialization sequence beginning at location 00FFFFF6h or an SCP address written to the 82596 using CPU Port access. All subsequent CA signals cause the 82596 to begin executing new command sequences from the SCB. |

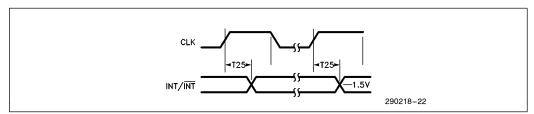

| INT/INT | 125             | 0    | INTERRUPT. A high signal on this pin notifies the CPU that the 82596 is requesting an interrupt. This signal is an edge triggered interrupt signal, and can be configured to be active high or low.                                                                                                                                                                                                                                                                                                                                                                           |

## PIN DESCRIPTIONS (Continued)

| Symbol          | PQFP<br>Pin No. | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> | 17 Pins         |      | <b>POWER.</b> +5 V ±10%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>SS</sub> | 17 Pins         |      | GROUND. 0 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TxD             | 54              | 0    | <b>TRANSMIT DATA.</b> This pin transmits data to the serial link. It is high when not transmitting.                                                                                                                                                                                                                                                                                                                                                                                                            |

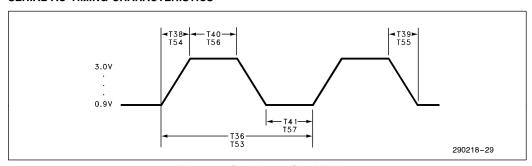

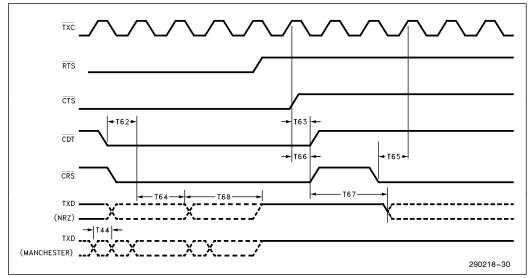

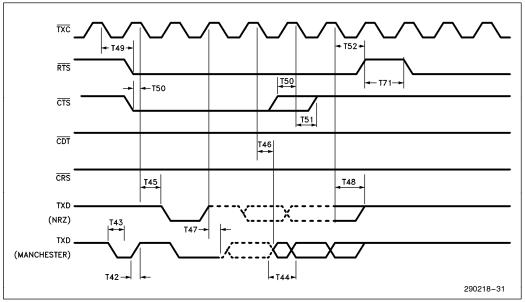

| TxC             | 64              | I    | TRANSMIT CLOCK. This signal provides the fundamental timing for the serial subsystem. The clock is also used to transmit data synchronously on the TxD pin. For NRZ encoding, data is transferred to the TxD pin on the high to low clock transition. For Manchester encoding, the transmitted bit center is aligned with the low to high transition. Transmit clock must always be running for proper device operation.                                                                                       |

| <u> </u>        | 58              | 0    | LOOPBACK. This TTL-level control signal enables the loopback mode. In this mode serial data on the TxD input is routed through the 82C501 internal circuits and back to the RxD output without driving the transceiver cable. To enable this signal, both internal and external loopback need to be set with the Configure command.                                                                                                                                                                            |

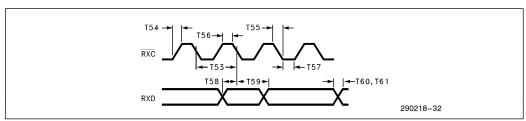

| RxD             | 60              | I    | RECEIVE DATA. This pin receives NRZ serial data only. It must be high when not receiving.                                                                                                                                                                                                                                                                                                                                                                                                                      |

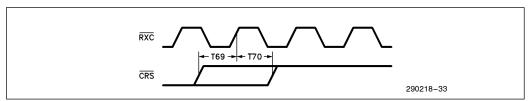

| RxC             | 59              | I    | RECEIVE CLOCK. This signal provides timing information to the internal shifting logic. For NRZ data the state of the RxD pin is sampled on the high to low transition of the clock.                                                                                                                                                                                                                                                                                                                            |

| RTS             | 57              | 0    | REQUEST TO SEND. When this signal is low the 82596 informs the external interface that it has data to transmit. It is forced high after a Reset or when transmission is stopped.                                                                                                                                                                                                                                                                                                                               |

| CTS             | 62              | I    | CLEAR TO SEND. An active-low signal that enables the 82596 to send data. It is normally used as an interface handshake to $\overline{\text{RTS}}$ . Asserting $\overline{\text{CTS}}$ high stops transmission. $\overline{\text{CTS}}$ is internally synchronized. If $\overline{\text{CTS}}$ goes inactive, meeting the setup time to the $\overline{\text{TxC}}$ negative edge, the transmission will stop and $\overline{\text{RTS}}$ will go inactive within, at most, two $\overline{\text{TxC}}$ cycles. |

| CRS             | 63              | I    | CARRIER SENSE. This signal is active low, it is used to notify the 82596 that traffic is on the serial link. It is only used if the 82596 is configured for external Carrier Sense. In this configuration external circuitry is required for detecting traffic on the serial link. CRS is internally synchronized. To be accepted, the signal must remain active for at least two serial clock cycles (for CRSF=0).                                                                                            |

| CDT             | 61              | I    | COLLISION DETECT. This active-low signal informs the 82596 that a collision has occurred. It is only used if the 82596 is configured for external Collision Detect. External circuitry is required for collision detection. CDT is internally synchronized. To be accepted, the signal must remain active for at least two serial clock cycles (for CDTF = 0).                                                                                                                                                 |

## 82596 AND HOST CPU INTERACTION

The 82596CA and the host CPU communicate through shared memory. Because of its on-chip DMA capability, the 82596 can make data block transfers (buffers and frames) independently of the CPU; this greatly reduces the CPU byte transfer overhead.

The 82596 is a multitasking coprocessor that comprises two independent logical units—the Command Unit (CU) and the Receive Unit (RU). The CU executes commands from shared memory. The RU handles all activities related to frame reception. The independence of the CU and RU enables the 82596 to engage in both activities simultaneously—the CU can fetch and execute commands from memory while the RU is storing received frames in memory. The CPU is only involved with this process after the CU has executed a sequence of commands or the RU has finished storing a sequence of frames.

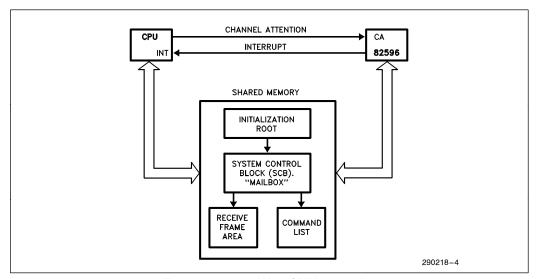

The CPU and the 82596 use the hardware signals Interrupt (INT) and Channel Attention (CA) to initiate communication with the System Control Block (SCB), see Figure 4. The 82596 uses INT to alert the CPU of a change in the contents of the SCB, the CPU uses CA to alert the 82596.

The 82596 has a CPU Port Access state that allows the CPU to execute certain functions without accessing memory. The 82596 PORT pin and data bus pins are used to enable this feature. The CPU can directly activate four operations when the 82596 is in this state.

- Write an alternative System Configuration Pointer (SCP). This can be used when the 82596 cannot use the default SCP address space.

- Write a different Dump Command Pointer and execute Dump. This can be used for troubleshooting No Response problems.

- The CPU can reset the 82596 via software without disturbing the rest of the system.

- A self-test can be used for board testing; the 82596 will execute a self-test and write the results to memory.

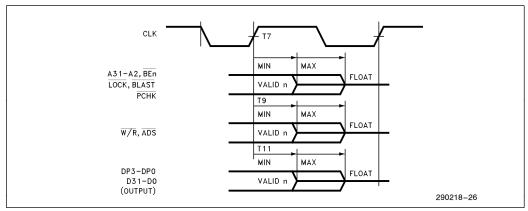

#### 82596 BUS INTERFACE

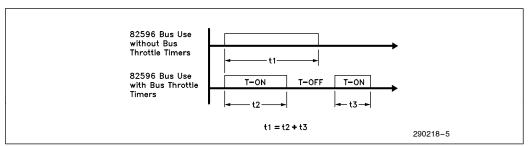

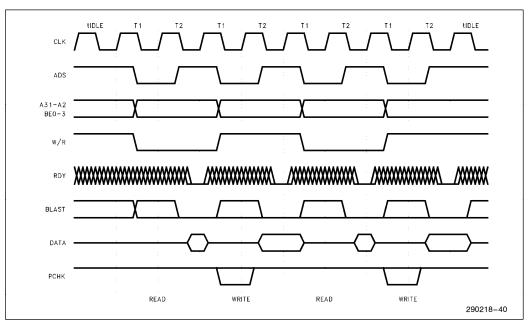

The 82596CA has bus interface timings and pin definitions that are compatible with Intel's 32-bit i486™SX and i486™DX microprocessors. This eliminates the need for additional bus interface logic. Operating at 33 MHz, the 82596's bus bandwidth can be as high as 106 MB/s. Since Ethernet only requires 1.25 MB/s, this leaves a considerable amount of bandwidth for the CPU. The 82596 also has a bus throttle to regulate its use of the bus. Two timers can be programmed through the SCB: one controls the maximum time the 82596 can remain on the bus, the other controls the time the 82596 must stay off the bus (see Figure 5). The bus throttle can be programmed to trigger internally with HLDA or externally with BREQ. These timers can restrict the 82596 HOLD activation time and improve bus utiliza-

#### 82596 MEMORY ADDRESSING

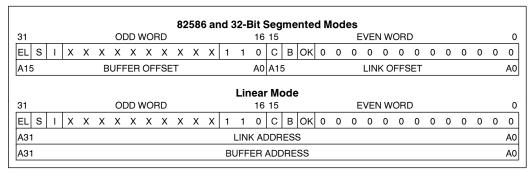

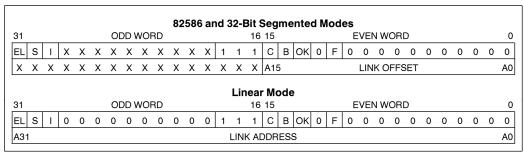

The 82596 has a 32-bit memory address range, which allows addressing up to four gigabytes of memory. The 82596 has three memory addressing modes (see Table 1).

- 82586 Mode. The 82596 has a 24-bit memory address range. The System Control Block, Command List, Receive Descriptor List, and Buffer Descriptors must reside in one 64-KB memory segment. Transmit and Receive buffers can reside in a 24-bit address space.

- 32-Bit Segmented Mode. The 82596 has a 32-bit memory address range. The System Control Block, Command List, Receive Descriptor List, and Buffer Descriptors must reside in one 64-KB memory segment. Transmit and Receive buffers can reside in a 32-bit address space.

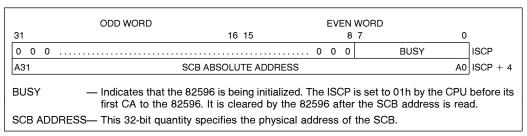

- Linear Mode. The 82596 has a 32-bit memory address range. Any memory structure can reside anywhere within the 32-bit memory address range.

Figure 4. 82596 and Host CPU Intervention

Figure 5. Bus Throttle Timers

Table 1. 82596 Memory Addressing Formats

|                        |                         | Operation Mode          |               |

|------------------------|-------------------------|-------------------------|---------------|

| Pointer or Offset      | 82586                   | 32-Bit<br>Segmented     | Linear        |

| ISCP Address           | 24-Bit Linear           | 32-Bit Linear           | 32-Bit Linear |

| SCB Address            | Base (24) + Offset (16) | Base (32) + Offset (16) | 32-Bit Linear |

| Command Block Pointers | Base (24) + Offset (16) | Base (32) + Offset (16) | 32-Bit Linear |

| Rx Frame Descriptors   | Base (24) + Offset (16) | Base (32) + Offset (16) | 32-Bit Linear |

| Tx Frame Descriptors   | Base (24) + Offset (16) | Base (32) + Offset (16) | 32-Bit Linear |

| Rx Buffer Descriptors  | Base (24) + Offset (16) | Base (32) + Offset (16) | 32-Bit Linear |

| Tx Buffer Descriptors  | Base (24) + Offset (16) | Base (32) + Offset (16) | 32-Bit Linear |

| Rx Buffers             | 24-Bit Linear           | 32-Bit Linear           | 32-Bit Linear |

| Tx Buffers             | 24-Bit Linear           | 32-Bit Linear           | 32-Bit Linear |

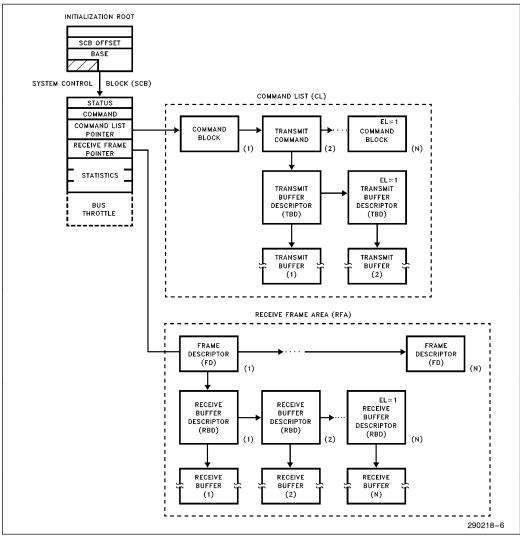

Figure 6. 82596 Shared Memory Structure

## 82596 SYSTEM MEMORY STRUCTURE

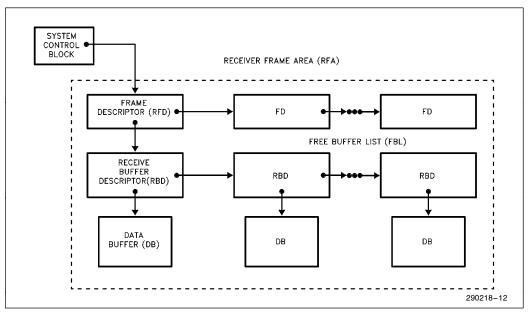

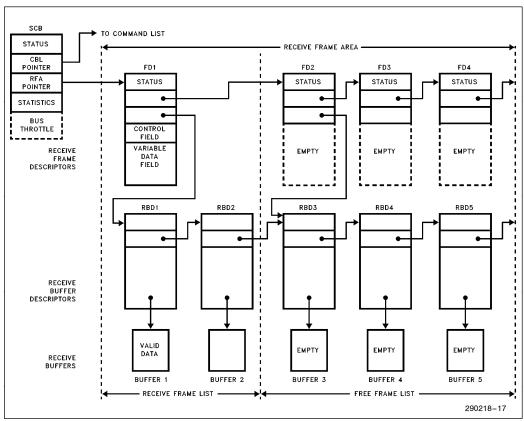

The Shared Memory structure consists of four parts: the Initialization Root, the System Control Block, the Command List, and the Receive Frame Area (see Figure 6).

The Initialization Root is in an established location known to the host CPU and the 82596 (00FFFFF6h). However, the CPU can establish the Initialization Root in another location by using the CPU Port access. This root is accessed during initialization, and points to the System Control Block.

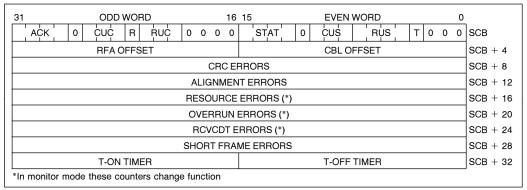

The System Control Block serves as a bidirectional mail drop for the host CPU and the 82596 CU and RU. It is the central point through which the CPU and the 82596 exchange control and status information. The SCB has two areas. The first contains instructions from the CPU to the 82596. These include: control of the CU and RU (Start, Abort, Suspend, and Resume), a pointer to the list of CU commands, a pointer to the Receive Frame Area, a set of Interrupt Acknowledge bits, and the T-ON and T-OFF timers for the bus throttle. The second area contains status information the 82596 is sending to the CPU. Such as, the CU and RU states (Idle, Active

Ready, Suspended, No Receive Resources, etc.), interrupt bits (Command Completed, Frame Received, CU Not Ready, and RU Not Ready), and statistical counters.

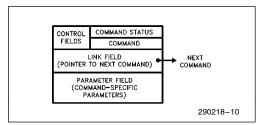

The Command List functions as a program for the CU; individual commands are placed in memory units called Command Blocks (CBs). These CBs contain the parameters and status of specific high-level commands called Action Commands; e.g., Transmit or Configure.

Transmit causes the 82596 to transmit a frame. The Transmit CB contains the destination address, the length field, and a pointer to a list of linked buffers holding the frame that is to be constructed from several buffers scattered throughout memory. The Command Unit operates without CPU intervention; the DMA for each buffer, and the prefetching of references to new buffers, is performed in parallel. The CPU is notified only after a transmission is complete.

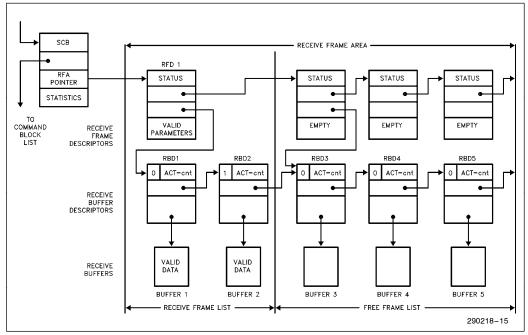

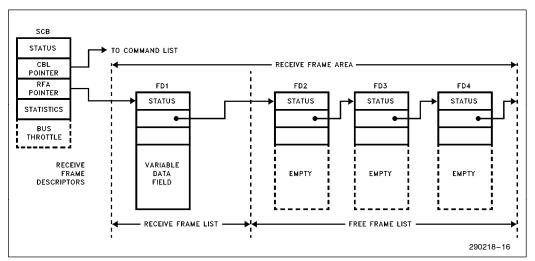

The Receive Frame Area is a list of Free Frame Descriptors (descriptors not yet used) and a list of userprepared buffers. Frames arrive at the 82596 unsolicited; the 82596 must always be ready to receive and store them in the Free Frame Area. The Receive Unit fills the buffers when it receives frames, and reformats the Free Buffer List into received-frame structures. The frame structure is, for all practical purposes, identical to the format of the frame to be transmitted. The first Frame descriptor is referenced by the SCB. Unless the 82596 is configured to Save Bad Frames, the frame descriptor, and the associated buffer descriptor, which is wasted when a bad frame is received, are automatically reclaimed and returned to the Free Buffer List.

Receive buffer chaining (storing incoming frames in a linked buffer list) significantly improves memory utilization. Without buffer chaining, the user must allocate consecutive blocks of memory, each capable of containing a maximum frame (for Ethernet, 1518 bytes). Since an average frame is about 200 bytes, this is very inefficient. With buffer chaining, the user can allocate small buffers and the 82596 will only use those that are needed.

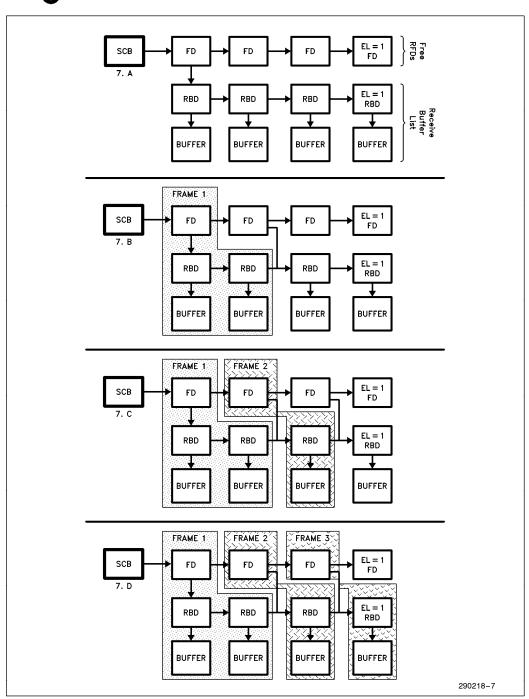

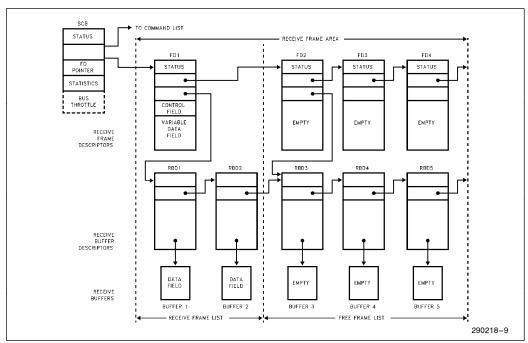

Figure 7 A-D illustrates how the 82596 uses the Receive Frame Area. Figure 7A shows an unused Receive Frame Area composed of Free Frame Descriptors and Free Receive Buffers prepared by the user. The SCB points to the first Frame Descriptor of the Frame Descriptor List. Figure 7B shows the same Receive Frame Area after receiving one frame. This first frame occupies two Receive Buffers and one Frame Descriptor—a valid received frame will only occupy one Frame Descriptor. After receiv-

ing this frame the 82596 sets the next Free Frame Descriptor RBD pointer to the next Free RBD. Figure 7C shows the RFA after receiving a second frame. In this example the second frame occupies only one Receive Buffer and one RFD. The 82596 again sets the RBD pointer. This process is repeated again in Figure 7D, showing the reception of another frame using one Receive Buffer; in this example there is an extra Frame Descriptor.

## TRANSMIT AND RECEIVE MEMORY STRUCTURES

There are three memory structures for reception and transmission. The 82586 memory structure, the Flexible memory structure, and the Simplified memory structure. The 82586 mode is selected by configuring the 82596 during initialization. In this mode all the 82596 memory structures are compatible with the 82586 memory structures.

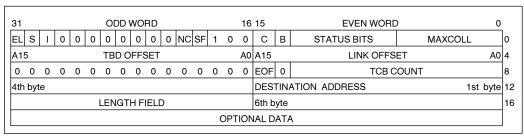

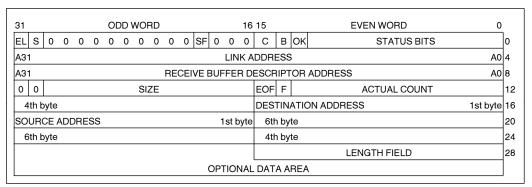

When the 82596 is not configured to the 82586 mode, the other two memory structures, Simplified and Flexible, are available for transmitting and receiving. These structures are selected by setting the S/F bit in the Transmit Command and/or the Receive Frame Descriptor (see Figures 29, 30, 41, and 42). It is recommended that any linked list of buffers be relegated to a single type—either simplified or flexible. The Simplified memory structure offers a simple structure for ease of programming (see Figure 8). All information about a frame is contained in one structure; for example, during reception the RFD and data field are contained in one structure.

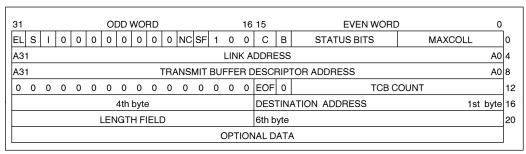

The Flexible memory structure (see Figure 9) has a control field that allows the programmer to specify the amount of receive data the RFD will contain for receive operations and the amount of transmit data the Transmit Command Block will contain for transmit operations. For example, when the control field in the RFD is set to 20 bytes during a reception, the first 20 bytes of the data field are stored in the RFD (6 bytes of destination address, 6 bytes of source address, 2 bytes of length field, and 6 bytes of data) and the remainder of the data field is stored in the Receive Data Buffers. This is useful for capturing frame headers when header information is contained in the data field. The header information can then be automatically stored in the RFD partitioned from the Receive Data Buffer.

The control field can also be used for the Transmit Command when the Flexible memory structure is used. The quantity of data field bytes to be transmitted from the Transmit Command Block is specified by the variable control field.

Figure 7. Frame Reception in the RFA

Figure 8. Simplified Memory Structure

Figure 9. Flexible Memory Structure

## TRANSMITTING FRAMES

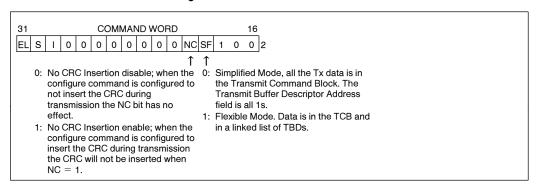

The 82596 executes high-level Action Commands from the Command List in system memory. Action Commands are fetched and executed in parallel with the host CPU operation, thereby significantly improving system performance. The format of the Action Commands is shown in Figure 10. Figure 28 shows the 82586 mode, and Figures 29 and 30 show the command formats of the Linear and 32-bit Segmented modes.

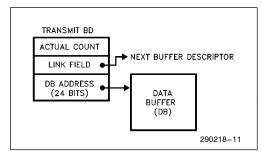

A single Transmit command contains, as part of the command-specific parameters, the destination address and length field of the transmitted frame and a pointer to buffer area in memory containing the data portion of the frame. The data field is contained in a memory data structure consisting of a buffer descriptor (BD) and a data buffer—or a linked list of buffer descriptors and buffers—as shown in Figure 11

Multiple data buffers can be chained together using the BDs. Thus, a frame with a long data field can be transmitted using several (shorter) data buffers chained together. This chaining technique allows the system designer to develop efficient buffer management

The 82596 automatically generates the preamble (alternating 1s and 0s) and start frame delimiter, fetches the destination address and length field from the Transmit command, inserts its unique address as the source address, fetches the data field specified by the Transmit command, and computes and appends the CRC to the end of the frame (see Figure 12). In the Linear and 32-bit Segmented mode the CRC can be optionally inserted on a frame-byframe basis by setting the NC bit in the Transmit Command Block (see Figures 29 and 30).

The 82596 generates the standard End Of Carrier (EOC) start and end frame delimiters. In EOC, the

start frame delimiter is 10101011 and the end frame delimiter is indicated by the lack of a signal after the last bit of the frame check sequence field has been transmitted. In EOC, the 82596 can be configured to extend short frames by adding pad bytes (7Eh) during transmission, according to the length field.

When a collision occurs, the 82596 manages the jam, random wait, and retry processes, reinitializing DMA pointers without CPU intervention. Multiple frames can be sent by linking the appropriate number of Transmit commands together. This is particularly useful when transmitting a message larger than the maximum frame size (1518 bytes for Ethernet).

Figure 10. Action Command Format

Figure 11. Data Buffer Descriptor and Data Buffer Structure

Figure 12. Frame Format

17

#### RECEIVING FRAMES

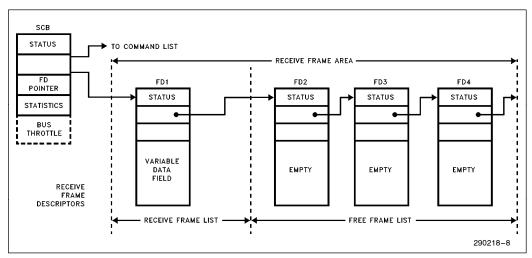

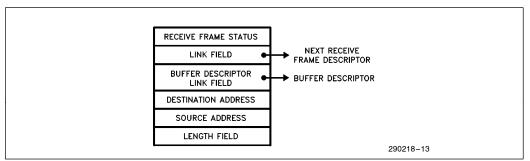

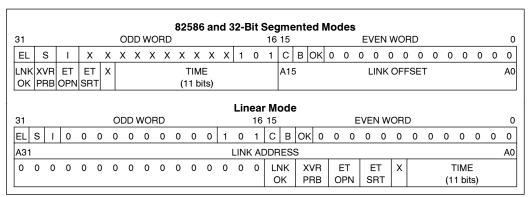

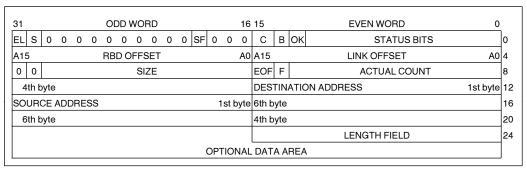

To reduce CPU overhead, the 82596 is designed to receive frames without CPU supervision. The host CPU first sets aside an adequate receive buffer space and then enables the 82596 Receive Unit. Once enabled, the RU watches for arriving frames and automatically stores them in the Receive Frame Area (RFA). The RFA contains Receive Frame Descriptors, Receive Buffer Descriptors, and Data Buffers (see Figure 13). The individual Receive Frame Descriptors make up a Receive Descriptor List (RDL) used by the 82596 to store the destination and source addresses, the length field, and the status of each frame received (see Figure 14).

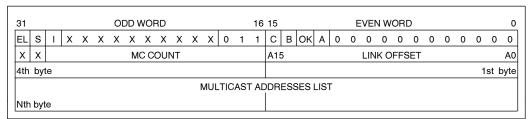

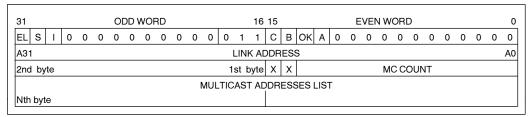

Once enabled, the 82596 checks each passing frame for an address match. The 82596 will recognize its own unique address, one or more multicast addresses, or the broadcast address. If a match is found the 82596 stores the destination and source addresses and the length field in the next available RFD. It then begins filling the next available Data Buffer on the FBL, which is pointed to by the current RFD, with the data portion of the incoming frame. As one Data Buffer is filled, the 82596 automatically fetches the next DB on the FBL until the entire frame is received. This buffer chaining technique is particularly memory efficient because it allows the system designer to set aside buffers to fit frames much shorter than the maximum allowable frame length. If AL-LOC = 1, or if the flexible memory structure is used, the addresses and length field can be placed in the Receive Buffer.

Once the entire frame is received without error, the 82596 does the following housekeeping tasks.

- The actual count field of the last Buffer Descriptor used to hold the frame just received is updated with the number of bytes stored in the associated Data Buffer.

- The next available Receive Frame Descriptor is fetched.

- The address of the next available Buffer Descriptor is written to the next available Receive Frame Descriptor.

- A frame received interrupt status bit is posted in the SCB.

- An interrupt is sent to the CPU.

If a frame error occurs, for example a CRC error, the 82596 automatically reinitializes its DMA pointers and reclaims any data buffers containing the bad frame. The 82596 will continue to receive frames without CPU help as long as Receive Frame Descriptors and Data Buffers are available.

## 82596 NETWORK MANAGEMENT AND DIAGNOSTICS

The behavior of data communication networks is normally very complex because of their distributed and asynchronous nature. It is particularly difficult to pinpoint a failure when it occurs. The 82596 has extensive diagnostic and network management functions that help improve reliability and testability. The 82596 reports on the following events after each frame is transmitted.

- · Transmission successful.

- Transmission unsuccessful. Lost Carrier Sense.

- Transmission unsuccessful. Lost Clear to Send.

- Transmission unsuccessful. A DMA underrun occurred because the system bus did not keep up with the transmission.

- Transmission unsuccessful. The number of collisions exceeded the maximum allowed.

- Number of Collisions. The number of collisions experienced during transmission of the frame.

- Heartbeat Indicator. This indicates the presence of a heartbeat during the last Interframe Spacing (IFS) after transmission.

When configured to Save Bad Frames the 82596 checks each incoming frame and reports the following errors.

- CRC error. Incorrect CRC in a properly aligned frame.

- Alignment error. Incorrect CRC in a misaligned frame.

- Frame too short. The frame is shorter than the value configured for minimum frame length.

- Overrun. Part of the frame was not placed in memory because the system bus did not keep up with incoming data.

- Out of buffer. Part of the frame was discarded because of insufficient memory storage space.

- Receive collision. A collision was detected during reception and the destination address of the incoming frame matches the 82596 individual address. Collisions in the preamble are not counted.

- Length error. A frame not matching the frame length parameter was detected.

Figure 13. Receive Frame Area Diagram

Figure 14. Receive Frame Descriptor

## NETWORK PLANNING AND MAINTENANCE

To properly plan, operate, and maintain a communication network, the network management entity must accumulate information on network behavior. The 82596 provides a rich set of network-wide diagnostics that can serve as the basis for a network management entity.

Information on network activity is provided in the status of each frame transmitted. The 82596 reports the following activity indicators after each frame.

- Number of collisions. The number of collisions the 82596 experienced while attempting to transmit the frame.

- Deferred transmission. During the first transmission attempt the 82596 had to defer to traffic on the link.

The 82596 updates its 32-bit statistical counters after each received frame that both passes address filtering and is longer than the Minimum Frame Length configuration parameter. The 82596 reports the following statistics.

- CRC errors. The number of well-aligned frames that experienced a CRC error.

- Alignment errors. The number of misaligned frames that experienced a CRC error.

- No resources. The number of frames that were discarded because of insufficient resources for reception.

- Overrun errors. The number of frames that were not completely stored in memory because the system bus did not keep up with incoming data.

- Receive Collision counter. The number of collisions detected during receive. Collisions occurring before the minimum frame length will be counted as short frames. Collisions in the preamble will not be counted at all.

- Short Frame counter. The number of frames that were discarded because they were shorter than the configured minimum frame length.

Once again, these counters are not updated until the 82596 decodes a destination address match.

The 82596 can be configured to Promiscuous mode. In this mode it captures all frames transmitted on the network without checking the Destination Address. This is useful when implementing a monitoring station to capture all frames for analysis.

A useful method of capturing frame headers is to use the Simplified memory mode, configure the 82596 to Save Bad Frames, and configure the 82596 to Promiscuous mode with space in the RFD allocated for specific number of receive data bytes.

The 82596 will receive all frames and put them in the RFD. Frames that exceed the available space in the RFD will be truncated, the status will be updated, and the 82596 will retrieve the next RFD. This allows the user to capture the initial data bytes of each frame (for instance, the header) and discard the remainder of the frame

The 82596 also has a monitor mode for network analysis. During normal operation the receive function enables the 82596 to receive frames that pass address filtering. These frames must have the Start of Frame Delimiter (SFD) field and must be longer than the absolute minimum frame length of 5 bytes (6 bytes in case of Multicast address filtering). Contents and status of the received frames are transferred to memory. The monitor function enables the 82596 to simply evaluate the incoming frames. The 82596 can monitor the frames that pass or do not pass the address filtering. It can also monitor frames which do not have the SFD fields. The 82596 can be configured to only keep statistical information about monitor frames. Three options are available in the Monitor mode. These options are selected by the two monitor mode configuration bits available in the configuration command.

When the first option is selected, the 82596 receives good frames that pass address filtering and transfers them to memory while monitoring frames that do not pass address filtering or are shorter than the minimum frame size (these frames are not transferred to memory). When this option is used the 82596 updates six counters: CRC errors, alignment errors, no resource errors, overrun errors, short frames and total good frames received.

When the second option is selected, the receive function is completely disabled. The 82596 monitors only those frames that pass address filterings and meet the minimum frame length requirement. When this option is used the 82596 updates six counters: CRC errors, alignment errors, total frames (good and bad), short frames, collisions detected and total good frames.

When the third option is selected, the receive function is completely disabled. The 82596 monitors all frames, including frames that do not have a Start Frame Delimiter. When this option is used the 82596 updates six counters: CRC errors, alignment errors, total frames (good and bad), short frames, collisions detected and total good frames.

## STATION DIAGNOSTICS AND SELF-TEST

The 82596 provides a large set of diagnostic and network management functions. These include internal and external loopback and time domain reflectometry for locating fault points in the network cable. The 82596 ensures software reliability by dumping the contents of the 82596 internal registers into system memory. The 82596 has a self-test mode that enables it to run an internal self-test and place the results in system memory.

#### 82586 SOFTWARE COMPATIBILITY

The 82596 has a software-compatible state in which all its memory structures are compatible with the 82586 memory structure. This includes all the Action Commands, the Receive Frame Area (including the RFD, Buffer Descriptors, and Data Buffers), the System Control Block, and the initialization procedures. There are two minor differences between the 82596 in the 82586-Compatible memory structure and the 82586.

- When the internal and external loopback bits in the Configure command are set to 11 the 82596 is in external loopback and the LPBK pin is activated; in the 82586 this situation would produce internal loopback.

- During a Dump command both the 82596 and 82586 dump the same number of bytes; however, the data format is different.

#### **INITIALIZING THE 82596**

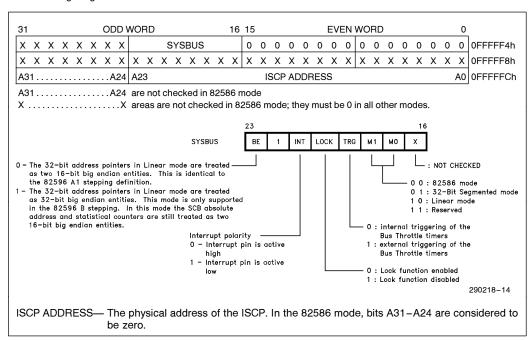

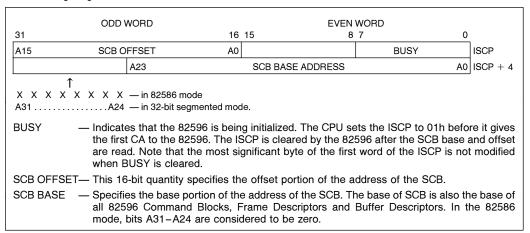

A Reset command is issued to the 82596 to prepare it for normal operation. The 82596 is initialized through two data structures that are addressed by two pointers, the System Configuration Pointer (SCP) and the Intermediate System Configuration Pointer (ISCP). The initialization procedure begins when a Channel Attention signal is asserted after RESET. The 82596 uses the address of the double word that contains the SCP as a default-00FFFFF4h. Before the CA signal is asserted this default address can be changed to any other available address by asserting the PORT pin and providing the desired address over the D<sub>31</sub>-D<sub>4</sub> pins of the address bus. Pins D3-D0 must be 0010; i.e., any alternative address must be aligned to 16-byte boundaries. All addresses sent to the 82596 must be word aligned, which means that all pointers and memory structures must start on an even address  $(A_0 = zero)$ .

# SYSTEM CONFIGURATION POINTER (SCP)

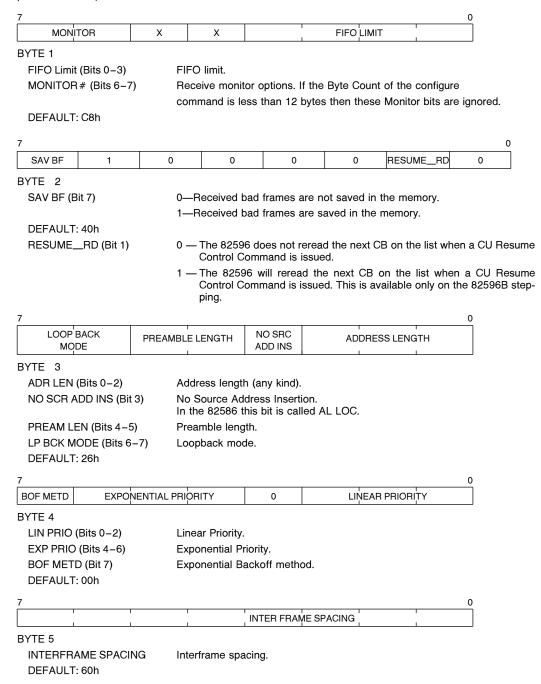

The SCP contains the sysbus byte and the location of the next structure of the initialization process, the ISCP. The following parameters are selected in the SYSBUS.

- The 82596 operation mode.

- The Bus Throttle timer triggering method.

- · Lock enabled.

- · Interrupt polarity.

- Big Endian 32-bit entity mode.

Byte ordering is determined by the LE/ $\overline{BE}$  pin. LE/ $\overline{BE}$ =1 selects Little Endian byte ordering and LE/ $\overline{BE}$ =0 selects Big Endian byte ordering.

#### NOTE:

In the following, X indicates a bit not checked 82586 mode. This bit must be set to 0 in all other modes.

The following diagram illustrates the format of the SCP.

Figure 15. The System Configuration Pointer

## **Writing the Sysbus**

When writing the sysbus byte it is important to pay attention to the byte order.

- When a Little Endian processor is used, the sysbus byte is located at byte address 00FFFF6h (or address n+2 if an alternative SCP address n was programmed).

- When a processor using Big Endian byte ordering is used, the sysbus, alternative SCP, and ISCP addresses will be different.

- The sysbus byte is located at 00FFFFF5h.

- ullet If an alternative SCP address is programmed, the sysbus byte should be at byte address n+1.

## INTERMEDIATE SYSTEM CONFIGURATION POINTER (ISCP)