# **OKI** Semiconductor

This version: Jan. 1998 Previous version: Nov. 1996

WWW.DZSC

## MSM6882-3/6882-5

2400/1200 bps Single Chip MSK Modem

#### **GENERAL DESCRIPTION**

The MSM6882-3/6882-5 is a single chip MSK (Minimum Shift Keying) modem which is fabricated by Oki's low power consumption CMOS silicon gate technology.

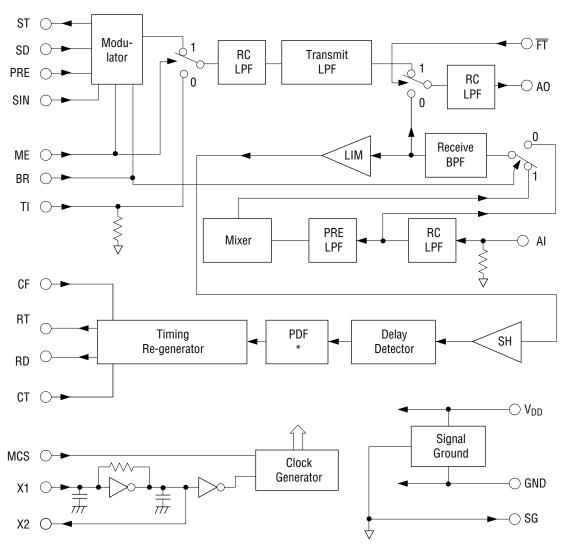

The demodulator receives the data to be transmitted (SD) synchronized with the transmit timing clock (ST) generated by the on-chip clock generator. The signal, which is modulated by MSK method, is output.

The demodulator converts the received MSK signal to the received data (RD) by means of a delay detection technique after limiting the band of the received MSK signal. This signal is input to the digital PLL and the re-generated timing clock (RT) is output from the demodulator, synchronized with the RD.

#### **FEATURES**

- Signal power supply: +3.6 V (MSM6882-3)

- +5 V (MSM6882-5)

- On-chip SCF (Switched Capacitor Filter)

- The transmit filter can be also used as voice splatter filter.

- The receive timing re-generator has two different lock-in time performance options to be chosen from

- Bit rate 2400/1200 bps

- CCIR Rec. 623

- The modulation method can be selected from COS-FFSK and SIN-FFSK.

- Built-in crystal oscillation circuit.

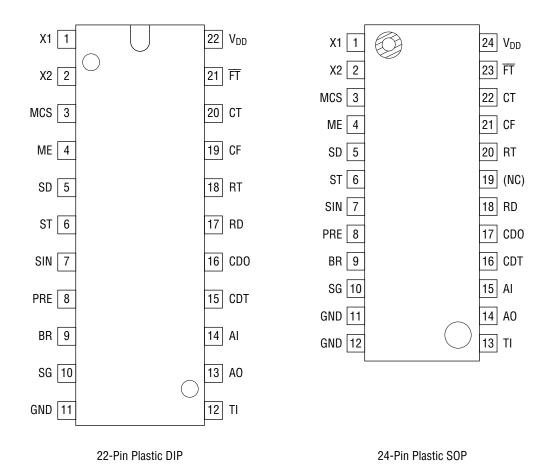

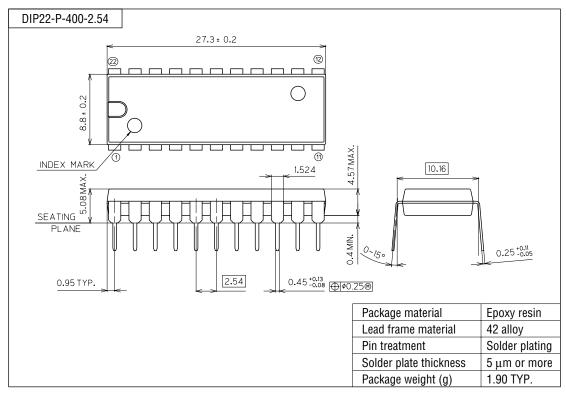

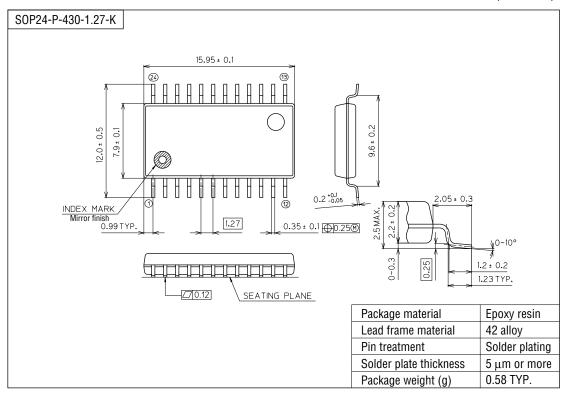

- Package options:

22-pin plastic DIP (DIP22-P-400-2.54) (Product name: MSM6882-3RS)

(Product name: MSM6882-5RS)

24-pin plastic SOP (SOP24-P-430-1.27-K) (Product name: MSM6882-3GS-K)

(Product name: MSM6882-5GS-K)

## **BLOCK DIAGRAM**

<sup>\*</sup> Post Detection Filter

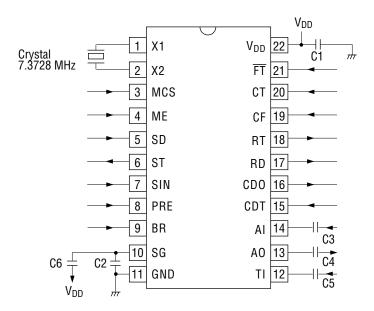

## **PIN CONFIGURATION (TOP VIEW)**

NC: No connect pin

## **PIN DESCRIPTION**

| Name | Description                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| X1   | Crystal connection pins. A 3.6864 MHz or 7.3728 MHz crystal shall be connected.                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| X2   | When an external clock is applied for MSM6882's oscillation source, it has to be input to X2. In this case, X2 has to be AC-coupled by the capacitor of 200 pF. X1 shall be left open.                                                                                                                                                         |  |  |  |  |  |  |  |  |

| MCS  | Master clock selection.  MCS Crystal or External Clock  0 3.6864 MHz  1 7.3728 MHz                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| ME   | Modulator enable.  When a "high" is input on this pin, MSK modulator output is connected to the input of transmit LPF.  When a "low" is input on this pin, TI is connected to the input of transmit LPF.                                                                                                                                       |  |  |  |  |  |  |  |  |

|      | Send data input. The data on this pin is synchronized with the rising edge of ST and input to MSK modulator as an actual transmit data.                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| SD   | SD ST                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| ST   | This timing signal is used to latch serial input data on the SD pin. The frequency of ST coincides with the transmission bit rate.                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|      | Modulation method selection.  Data put on this pin selects either SINE FAST FSK or COSINE FAST FSK.                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| SIN  | Data (2400 bps) 0 1 0 0 1 1 Sine Fast FSK Cosine Fast FSK                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| PRE  | Preamble or data transmission selection.  When a "low" is input on this pin, the data put on the SD pin is output on the AO pin.  When a "high" is input on this pin, the data put on the SD pin is neglected and preamble data is output.  Data put on PRE is latched on the rising edge of ST.  Preamble means to modulate as 010101pattern. |  |  |  |  |  |  |  |  |

| Name      | Description                                                                                 |                                    |                                 |                               |                                |                                     |              |  |  |  |

|-----------|---------------------------------------------------------------------------------------------|------------------------------------|---------------------------------|-------------------------------|--------------------------------|-------------------------------------|--------------|--|--|--|

|           | Baud rate selection.                                                                        | Baud rate selection.               |                                 |                               |                                |                                     |              |  |  |  |

|           | Master Clock                                                                                | MCS                                | BR                              | Bit Rate                      | Carrier                        | Freq. (Hz)                          |              |  |  |  |

|           | (MHz)                                                                                       | IVIUS                              | DN                              | (bps)                         | Mark                           | Space                               |              |  |  |  |

|           | 7.3728                                                                                      | 1                                  | 1                               | 2400                          | 1200                           | 2400                                |              |  |  |  |

| BR        | 1.3120                                                                                      | 1                                  | 0                               | 1200                          | 1200                           | 1800                                |              |  |  |  |

|           | 3.6864                                                                                      | 0                                  | 0                               | 1200                          | 1200                           | 1800                                |              |  |  |  |

|           | 3.6864                                                                                      | 1                                  | 1                               | 1200                          | 600                            | 1200                                |              |  |  |  |

|           | 0.0004                                                                                      | 1                                  | 0                               | 600                           | 600                            | 900                                 |              |  |  |  |

|           | Built-in analog signa                                                                       |                                    |                                 |                               |                                |                                     |              |  |  |  |

| SG        | The DC voltage is ap<br>with peripheral circu<br>source impedance lo<br>bypass capacitors s | oproxima<br>uits whicl<br>ower and | tely half<br>n must b<br>ensure | e implemente<br>the device pe | ed by AČ-coup<br>erformance of | oling. To make t<br>this device, mo | this voltage |  |  |  |

| SG<br>GND | The DC voltage is ap<br>with peripheral circu<br>source impedance l                         | oproxima<br>uits whicl<br>ower and | tely half<br>n must b<br>ensure | e implemente<br>the device pe | ed by AČ-coup<br>erformance of | oling. To make t<br>this device, mo | this voltage |  |  |  |

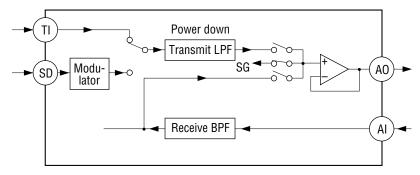

Transmit analog signal output.

The data put on ME and FT can set the status of AO as follows.

|   | FT  | ME  | Transmit LPF | State of AO               |  |  |  |  |

|---|-----|-----|--------------|---------------------------|--|--|--|--|

| Ī | "1" | "1" | Dower On     | MSK Signal                |  |  |  |  |

|   | "1" | "0" | Power On     | Voice Signal              |  |  |  |  |

|   | "0" | "1" | Power Down   | The Output of Receive BPF |  |  |  |  |

|   | "0" | "0" | Power Down   | No-signal (SG level)      |  |  |  |  |

The state when  $\overline{FT}$  and ME = "0" is shown above. When the input digital data on  $\overline{FT}$  changes to "1" from "0", AO remains to be connected to SG during about 2 ms and after that, and AO is switched to transmit LPF.

This delay time prevents AO from outputting meaningless signal during transient time from power down to on of LPF.

A0

| Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Al              | Receive analog signal input. All is biased internally to SG with about 100 k $\Omega$ same as TI.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| CDT             | Device test. This pin should be connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| CDO             | Device test. This pin should be opened.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| RD              | Demodulated serial data output. This data is synchronized with the re-generated timing clock RT.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|                 | Receive data timing clock output. This signal is re-generated by internal digital PLL. Synchronizing to negative edge of RT, RD is output.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| RT              | RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| CF              | Receive data timing clock is re-generated by digital PLL of which phase correcting speed can be selected with CF.  When a digital "1" is put on CF and phase difference between receive data timing and RT is more than 22.5 degree, phase correcting speed is high. In this case, as the phase difference enters within 22.5 degrees, that speed changes to low immediately.  When digital "0" is input to CF, phase correcting speed of PLL remains low regardless of the phase difference.  Usually, CF is connected to digital "1". |  |  |  |  |  |  |  |

| СТ              | PLL's lock-in characteristics can be selected with CT.  When digital "1" is put on CT, PLL requires max. 50 bit alternative data pattern. On the other hand, when digital "0" is input to CT, PLL can be locked in below 18-bit data.  CF CT MIN TYP MAX UNIT  1 0 — 18  1 1 0 — 50                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| FT              | Control signal for the internal connection of AO. Refer to column AO. When digital "0" is input to this pin, transmit LPF enters in power down mode, but the output buffer operational amplifier remains active. In this case, AO is at SG level.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| V <sub>DD</sub> | Power supply. MSM6882-3: 3.6 V MSM6882-5: $5 \text{ V}$ This device is sensitive to supply noise as switched capacitor techniques are utilized. A bypass capacitor of more than 2.2 $\mu\text{F}$ between V <sub>DD</sub> and GND is indispensable to ensure the performance.                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter             | Symbol           | Condition           | Rating                        | Unit  |  |

|-----------------------|------------------|---------------------|-------------------------------|-------|--|

| Power Supply Voltage  | V <sub>DD</sub>  | Ta = 25°C           | -0.3 to 7.0                   | V     |  |

| Input Voltage *1      | VI               | With respect to GND | -0.3 to V <sub>DD</sub> + 0.3 | \ \ \ |  |

| Operating Temperature | Top              | _                   | -25 to 70                     | °C    |  |

| Storage Temperature   | T <sub>STG</sub> | _                   | -55 to 150                    |       |  |

<sup>\*1</sup> MCS, ME, SD, SIN, PRE, BR, TI, AI, CDT, CF, CT, FT

#### **RECOMMENDED OPERATING CONDITIONS**

|                             | Parameter                       | Symbol              | Condition               |                        | Min.   | Тур.   | Max.   | Unit    |  |

|-----------------------------|---------------------------------|---------------------|-------------------------|------------------------|--------|--------|--------|---------|--|

|                             |                                 | V                   | With respect to CND     | *1                     | 3.0    | 3.6    | 4.0    |         |  |

| Pow                         | er Supply Voltage               | $V_{DD}$            | With respect to GND *2  |                        | 4.5    | 5      | 5.5    | V       |  |

|                             |                                 | GND                 | _                       |                        | _      | 0      | _      |         |  |

| Oper                        | ating Temperature               | T <sub>op</sub>     | _                       |                        | -25    | 25     | 70     | °C      |  |

| Cryot                       | al Daganant Fraguency           | f                   | MCS = "1"               |                        | 7.3721 | 7.3728 | 7.3735 | MHz     |  |

| Crystal Resonant Frequency  |                                 | f <sub>X' TAL</sub> | MCS = "0"               |                        | 3.6860 | 3.6864 | 3.6868 | IVITZ   |  |

| Data                        | Chand                           | т.                  | MCS = "1", BR = "1"     |                        | _      | 2400   | _      | hit/ooo |  |

| Data                        | Speed                           | T <sub>S</sub>      | BR = "0"                |                        | _      | 1200   | _      | bit/sec |  |

| C1                          |                                 | _                   | _                       |                        | _      | 2.2    | _      |         |  |

| C2                          |                                 | _                   | _                       |                        | _      | 0.1    | _      |         |  |

| C3                          |                                 | _                   | _                       |                        | _      | 0.047  | _      |         |  |

| C4                          |                                 | _                   | R <sub>LX</sub> ≥ 40 kΩ |                        | _      | 0.047  | _      | μF      |  |

| C5                          |                                 | _                   | _                       |                        | _      | 0.047  | _      |         |  |

| C6                          |                                 | _                   | _                       | _                      | 0.1    | _      |        |         |  |

|                             | Oscillation Frequency           | _                   | _                       |                        | _      | 7.3728 | _      | MHz     |  |

|                             | Frequency Deviation             | _                   | 25 ±5°C                 |                        | -100   | _      | +100   |         |  |

| Crystal                     | Temperature<br>Characteristics  | _                   | At -30°C to +70°C       | At -30°C to +70°C      |        | _      | +100   | ppm     |  |

| ō                           | Equivalent Series<br>Resistance | _                   | _                       |                        | _      | _      | 50     | Ω       |  |

|                             | Load Capacitance                | _                   | _                       |                        | _      | 16     | _      | pF      |  |

|                             | Oscillation Frequency           | _                   | _                       |                        | _      | 3.6864 | _      | MHz     |  |

|                             | Frequency Deviation             | _                   | 25 ±5°C                 |                        | -100   | _      | +100   |         |  |

| Temperature Characteristics |                                 | _                   | At -30°C to +70°C       | At -30°C to +70°C -100 |        | _      | +100   | ppm     |  |

| Equivalent Series           |                                 | _                   | _                       | _                      | 100    | Ω      |        |         |  |

|                             | Load Capacitance                | _                   | _                       |                        | _      | 16     | _      | pF      |  |

<sup>\*1</sup> MSM6882-3

<sup>\*2</sup> MSM6882-5

#### **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

(MSM6882-3:  $V_{DD}$  = 3 V to 4 V, Ta = -25°C to 70°C) (MSM6882-5:  $V_{DD}$  = 5 V ±0.5 V, Ta = -25°C to 70°C)

| Parameter               | Symbol             | Condition                      | Min.               | Тур. | Max.            | Unit |

|-------------------------|--------------------|--------------------------------|--------------------|------|-----------------|------|

|                         | 1                  | Normal Operating Mode          | _                  | 4    | 8               |      |

| Power Supply Current ** | l I <sub>DD</sub>  | <del>FT</del> = "1"            | _                  | 5.5  | 11              | mΛ   |

|                         |                    | Power Down Mode —              | _                  | 3.5  | 7               | mA   |

|                         | I <sub>DDS</sub>   | <del>FT</del> = "0"            | _                  | 5.0  | 10              |      |

| Input Leakage Current * | I <sub>IL</sub>    | $V_{IN} = 0 V$                 | -10                | 1    | 10              | μA   |

|                         | liH                | $V_{IN} = V_{DD}$              | -10                | _    | 10 μπ           | μΛ   |

|                         | V <sub>IL</sub> *1 | 0                              |                    | 0.6  |                 |      |

| Input Voltage *2        |                    | "1 0                           |                    |      | 0.8             |      |

| iliput voltage          |                    | *1                             | 1.8                |      | V               |      |

|                         | V <sub>IH</sub>    | , I                            | 2.2                | _    | $V_{DD}$        | V    |

|                         | V                  | I <sub>OL</sub> = 10 μA/1.6 mA | 0                  |      | 0.3             |      |

| Output Voltage *1 *3    | V <sub>OL1</sub>   | 10L = 10 μΑ/1.0 ΠΙΑ            | 0                  | _    | 0.4             |      |

|                         | V <sub>OH1</sub>   | Ι <sub>ΟΗ</sub> = 10 μΑ/400 μΑ | 0.8V <sub>DD</sub> | _    | V <sub>DD</sub> |      |

<sup>\*1</sup> Upper is specified for the MSM6882-3, lower for the MSM6882-5

#### **Digital Interface Characteristics**

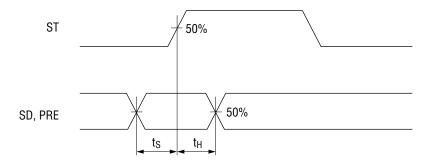

| Parameter              | Symbol         | Condition | Min. | Тур. | Max. | Unit |

|------------------------|----------------|-----------|------|------|------|------|

| Input Data Set-up Time | ts             | Coo Fig 1 | 300  | _    | _    | ns   |

| Input Data Hold Time   | t <sub>H</sub> | See Fig.1 | 300  | _    | _    | ns   |

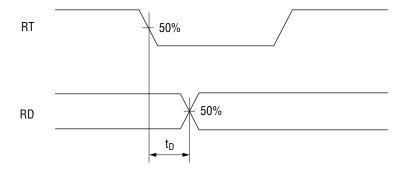

| Output Data Delay Time | t <sub>D</sub> | See Fig.2 | -300 | _    | 300  | ns   |

<sup>\*2</sup> MCS, ME, SD, SIN, PRE, BR, CF, CT, FT

<sup>\*3</sup> ST, RD, RT

## **Analog Interface Characteristics**

Transmit signal output (AO)

(MSM6882-3:  $V_{DD}$  = 3 V to 4 V, Ta = -25°C to 70°C) (MSM6882-5:  $V_{DD}$  = 5 V ±0.5 V, Ta = -25°C to 70°C)

| Paramete          | r       | Symbol           |                              | Condition | l        | Min.                | Тур.                | Max.                | Unit             |

|-------------------|---------|------------------|------------------------------|-----------|----------|---------------------|---------------------|---------------------|------------------|

|                   | 1200    | f <sub>M1</sub>  | <del></del>                  | FT - "1"  | SD = "1" | 1199                | 1200                | 1201                |                  |

| Carrier Frequency | bps     | f <sub>S1</sub>  | FI = I                       |           | SD = "0" | 1799                | 1800                | 1801                | Hz               |

|                   | 2400    | f <sub>M2</sub>  | ME = "1"                     | DD _ "1"  | SD = "1" | 1199                | 1200                | 1201                | 112              |

|                   | bps     | f <sub>S2</sub>  | ME = "1"                     | BR = "1"  | SD = "0" | 2399                | 2400                | 2401                |                  |

| Carrier Level *1  |         | V <sub>OX</sub>  | <b>R</b> . > /               | IU KO     | FT = "1" | -7                  | -3                  | -1                  | dBm              |

| Gairiei Levei     | 1       | VOX              | $R_L \ge 40 \text{ k}\Omega$ |           | ME = "1" | -3                  | 0                   | 2                   | *2               |

| Output Amplitude  | *1      | V <sub>OPP</sub> | C1 < 1                       | 10 nF     | FT = "1" | 1.4                 | 2.0                 | _                   | V                |

| Output Amplitude  | ·       | V 0PP            | C <sub>L</sub> ≤ 40 pF       |           | ME = "0" | 2.2                 | 3.0                 | _                   | V <sub>p-p</sub> |

| Output Resistance |         | R <sub>OX</sub>  |                              | _         |          | _                   | 50                  | _                   | Ω                |

| Output Load Resis | tance   | R <sub>LX</sub>  | _                            |           |          | 40                  | _                   | _                   | kΩ               |

| Output Load Capac | citance | C <sub>LX</sub>  | _                            |           |          | _                   | _                   | 40                  | pF               |

| Output DC Voltage |         | V <sub>OSX</sub> |                              | _         |          | 0.48V <sub>DD</sub> | 0.50V <sub>DD</sub> | 0.52V <sub>DD</sub> | V                |

## Voice signal input (TI)

| Parameter          |    | Symbol            | Con                     | Min.                | Тур. | Max. | Unit |     |

|--------------------|----|-------------------|-------------------------|---------------------|------|------|------|-----|

| Voltage Gain       |    | GT                | $V_{AO}/V_{TI}$         |                     | -2   | 0    | +2   | dB  |

| Input Cianal Laval | *1 | V <sub>TI</sub> — |                         | <del>FT</del> = "1" |      |      | -4   | dBm |

| Input Signal Level | 1  |                   | ME = "0"                | _                   | _    | 0    | *2   |     |

| Input Resistance   |    | R <sub>TI</sub>   | f <sub>TI</sub> ≤ 4 kHz |                     | 40   | 100  | 300  | kΩ  |

## Built-in signal ground (SG)

| Parameter  | Symbol          | Condition       | Min.                | Тур.                | Max.                | Unit |

|------------|-----------------|-----------------|---------------------|---------------------|---------------------|------|

| DC Voltage | V <sub>SG</sub> | Without DC Load | 0.48V <sub>DD</sub> | 0.50V <sub>DD</sub> | 0.52V <sub>DD</sub> | V    |

### Receive signal input (AI)

| Parameter            |          | Symbol           | C         | ondit  | tion      | Min.   | Тур.                 | Max.               | Unit               |   |  |

|----------------------|----------|------------------|-----------|--------|-----------|--------|----------------------|--------------------|--------------------|---|--|

| Input Resistance     |          | R <sub>AI</sub>  | f         | AI ≤ 4 | kHz       | 40     | 100                  | 300                | kΩ                 |   |  |

| Receive Signal Level |          | V <sub>IR1</sub> |           |        | BR = "0"  | -30    | _                    | 0                  | dBm                |   |  |

|                      |          | V <sub>IR2</sub> | _         |        | BR = "1"  | -24    | _                    | 0                  | *2                 |   |  |

|                      | 1200 bps | 1000 hns         |           |        |           | 7 dB   | _                    | $2 \times 10^{-3}$ | _                  |   |  |

| Bit Error Rate       |          | BER              | S/N at AI | S/N    | 11 dB     | _      | $2 \times 10^{-5}$   | _                  |                    |   |  |

| Dit Litti hate       | 0400 hma | 0400 hms         | 0400 bno  | DLI    | SIN = "1" | J 5/ N | 10 dB                | _                  | $2 \times 10^{-3}$ | _ |  |

|                      | 2400 bps |                  |           |        | 14 dB     | _      | 2 × 10 <sup>-5</sup> | _                  |                    |   |  |

$<sup>^{*1}</sup>$  Upper is specified for the MSM6882-3, lower for the MSM6882-5

<sup>\*2</sup> 0 dBm = 0.775 Vrms

## Re-generated receive data timing clock output (RT)

| Parameter                | Symbol            | Condition |         |    | Min. | Тур. | Max. | Unit |

|--------------------------|-------------------|-----------|---------|----|------|------|------|------|

| Data Bit Number for PLL' | N <sub>PLL1</sub> | CF = "1"  | CT= "0" | *3 |      |      | 18   | bit  |

| Lock-in                  | N <sub>PLL2</sub> |           | CT= "1" |    | _    | _    | 50   |      |

<sup>\*3</sup> Data bit number to lock-in within 22.5 degree

## **TIMING DIAGRAM**

Figure 1 Input Data Timing

Figure 2 Output Data Timing

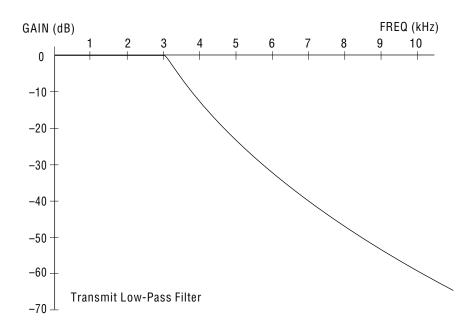

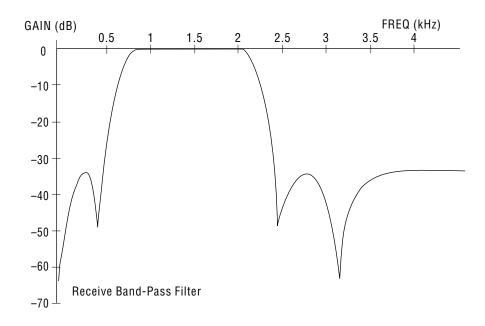

#### **BUILT-IN FILTER FREQUENCY CHARACTERISTICS**

Note: When BR = "1", frequency converter circuit (MIXER) is prepared before the receive BPF. Therefore, 1200 Hz input signal is converted to 3600 Hz at BPF output for example.

## **APPLICATION CIRCUIT**

#### **PACKAGE DIMENSIONS**

(Unit: mm)

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).