## 查询AM2950ADCB供应商 AM2950-50A/AM2951-50LA

Eight-Bit Bidirectional I/O Ports with Handshake

## DISTINCTIVE CHARACTERISTICS

- Eight-Bit, Bidirectional I/O Port with Handshake— Two eight-bit, back-to-back registers store data moving in both directions between two bidirectional busses.

- Register Full/Empty Flags— On-chip flag flip-flops provide data transfer handshaking signals.

- 24mA Output Current Sink Capability.

- Separate Clock, Clock Enable and Three-State Output Enable for Each Register.

- Separate, Edge-Sensitive Clear Control for Each Flag Flip-Flop.

- Fast -

The Am2950A and Am2951A will be 25-30% faster than the Am2950 and Am2951.

## GENERAL DESCRIPTION

The Am2950 and Am2951, members of Advanced Micro Devices' Am2900 Family, are designed for use as parallel data I/O ports. Two eight-bit, back-to-back registers store data moving in both directions between two bidirectional, 3-state busses. On chip flag flip-flops, set automatically when a register is loaded, provide the handshaking signals required for demand-response data transfer.

Considerable flexibility is designed into the Am2950/ Am2951. Separate clock, Clock Enable and Three-State Output Enable signals are provided for each register, and edge-sensitive clear inputs are provided for each flag flipflop. A number of these circuits can be used for wider I/O ports. Both inverting and non-inverting versions are available.

24mA output current sink capability, sufficient for most three-state busses, is provided by the Am2950/Am2951.

The Am2950A and Am2951A feature AMD's ion-implanted micro-oxide (IMOX<sup>TM</sup>) processing. They are plug-in replacements for the Am2950 and Am2951 respectively but will be approximately 30% faster.

## **BLOCK DIAGRAM**

Note: The Am2951 provides inverting data outputs (B<sub>0-7</sub>).

03581B

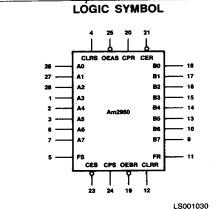

#### CONNECTION DIAGRAM Top View Chip-Pak<sup>TM</sup> F-28 D-28 L-28 \_ ^^ BS C CLR CPS 7 45 T OES B3 [ **□** 44 **□ A3** 82 \_\_ CEn **⊐** A1 ōEBR □ ⊐ A0 - OFAS CPR [ CD004660 CD004640 CD004650 Note: Pin 1 is marked for orientation Bi is inverted on Am2951.

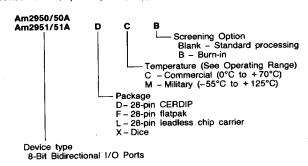

## ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

| Valid Combinations       |                                           |  |  |  |

|--------------------------|-------------------------------------------|--|--|--|

| Am2950/50A<br>Am2951/51A | DC, DCB, DMB<br>FMB<br>LC, LMB,<br>XC, XM |  |  |  |

#### Valid Combinations

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

#### PIN DESCRIPTION 1/0 Description Pin No. Name A0-7 1/0 Eight bidirectional lines carrying the R Register inputs or S Register outputs. Eight bidirectional lines carrying the S Register inputs or B Register outputs. B0-7 1/0 The clock for the R Register and FR Flip-Flop. When CER is LOW, data is entered into the R Register and the FR 20 CPR Flip-Flop is set on the LOW-to-HIGH transition of the CPR signal. The Clock Enable for the R Register and FR Flip-Flop. When CER is LOW, data is entered into the R Register and the FR Flip-Flop is set on the LOW-to-HIGH transition of the CPR signal. When CER is HIGH, The R Register and 21 CER FR Flip-Flop hold their contents, regardless of CPR signal transitions. The Output Enable for the R Register. When $\overline{\text{OEBR}}$ is LOW, the R Register three-state outputs are enabled onto the B0-7 lines. When $\overline{\text{OEBR}}$ is HIGH, the R Register outputs are in the high-impedance state. **Ö**EBR 19 0 The FR Flip-Flop output. 11 The clear control for the FR Flip-Flop. The FR Flip-Flop is cleared on the LOW-to-HIGH transition of CLRR signal. CLRR ī 12 The clock for the S Register and FS Flip-Flop. When CES is LOW, data is entered into the S Register and the FS CPS 1 24 Flip-Flop is set on the LOW-to-HIGH transition of the CPS signal. The clock enable for the S Register and FS Flip-Flop. When $\overline{\text{CES}}$ is LOW, data is entered into the S Register and the FS Flip-Flop is set on the LOW-to-HIGH transition of the CPS signal. When $\overline{\text{CES}}$ is HIGH, the S Register and FS Flip-Flop hold their contents, regardless of CPS signal transitions. CES 23 The output enable for the S Register. When OEAS is LOW, the S Register three-state outputs are enabled onto the A0-7 lines. When OEAS is HIGH, the S Register outputs are in the high-impedance state. **OEAS** The FS Flip-Flop output. FS 0 5 The clear control for the FS Flip-Flop. The FS Flip-Flop is cleared on the LOW-to-HIGH transition of CLRS signal. CLAS

## REGISTER FUNCTION TABLE (Applies to R or S Register)

|   | Inputs |    | Internal |           |

|---|--------|----|----------|-----------|

| D | СР     | CE | Q        | Function  |

| × | ×      | н  | NC       | Hold Data |

| L | 1      | Ł  | L        | Load Data |

| Н | 1      | L  | н        |           |

#### **OUTPUT CONTROL**

|        | Internal | Y-Outputs |        | <b>5</b>        |

|--------|----------|-----------|--------|-----------------|

| ŌĒ     | Q        | Am2950    | Am2951 | Function        |

| Н      | X        | Z         | Z      | Disable Outputs |

| L<br>L | L<br>H   | L<br>H    | H<br>L | Enable Outputs  |

# FLAG FLIP-FLOP FUNCTION TABLE (Applies to R or S Flag Flip-Flop)

| (Applies to 11 of 5 flag flip 1 lop) |        |          |          |            |  |

|--------------------------------------|--------|----------|----------|------------|--|

| CE                                   | Inputs | CLR      | F-Output | Function   |  |

| н                                    | ×      | <b>‡</b> | NC       | Hold Flag  |  |

| X                                    | Х      | 1        | L        | Clear Flag |  |

| L                                    | 1      | <b></b>  | Н        | Set Flag   |  |

H = HIGH

L = LOW

X = Don't Care

Z = High Impedance

NC = NO CHANGE

↑ = LOW-to-HIGH Transition

#### **APPLICATIONS**

The Am2950/Am2951 provides data transfer handshaking signals as well as eight-bit, bidirectional data storage. Its flexibility allows it to be used in any type of computer system, including Am2900, 8080, 8085, 8086, Z80, and Z8000 systems.

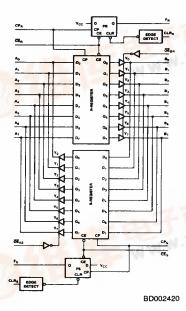

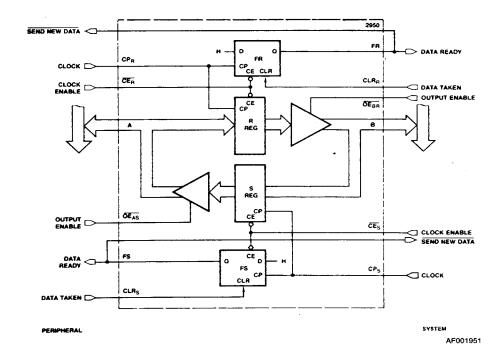

Figure 1 shows an Am2950 used to store data moving in both directions between a bidirectional system data bus and a

bidirectional peripheral data bus. The on-chip Flag flip-flops provide the data in, data out handshaking signals required for data transfer and interrupt request generation.

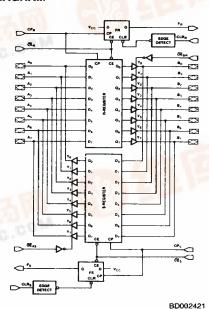

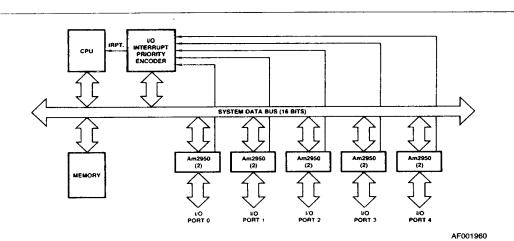

Figure 2 shows a multiple I/O port system using Am2950's. Two Am2950's are used at each port to interface the 16-bit system data bus. The Am2950 flags are used to generate I/O interrupt requests.

Figure 1. A Bidirectional I/O Port with Handshaking Using the Am2950.

as paragram

Figure 2. Multiple I/O Port System.

ma Pen

#### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature65°C to +150°C              |

|------------------------------------------------|

| (Ambient) Temperature Under Bias55°C to +125°C |

| Supply Voltage to Ground Potential             |

| Continuous0.5V to +7.0V                        |

| DC Voltage Applied to Outputs For              |

| High Output State0.5V to +V <sub>CC</sub> max  |

| DC Input Voltage0.5V to +5.5V                  |

| DC Output Current, Into Outputs                |

| DC Input Current30mA to +5.0mA                 |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

| Commercial (C) Devices               |                            |

|--------------------------------------|----------------------------|

| Temperature                          | 0°C to +70°C               |

| Supply Voltage                       | + 4.75V to + 5.25V         |

| Military (M) Devices                 |                            |

| Temperature                          | 55°C to +125°C             |

| Supply Voltage                       | + 4.5V to + 5.5V           |

| Operating ranges define those limits | s over which the function- |

| ality of the device is guaranteed.   |                            |

DC CHARACTERISTICS over operating range unless otherwise specified Am2950/Am2951

| Parameters      | Description                           | Tes                                     | t Conditio                                          | ns (Note 1)                                     | Min  | Typ<br>(Note 2) | Max   | Units |

|-----------------|---------------------------------------|-----------------------------------------|-----------------------------------------------------|-------------------------------------------------|------|-----------------|-------|-------|

|                 | 1                                     |                                         | FR, FS                                              | I <sub>OH</sub> = - 1mA                         | 2.4  | 3.4             |       |       |

| VoH             | Output HIGH Voltage                   | V <sub>CC</sub> = MIN                   | A <sub>0-7</sub> , B <sub>0-7</sub>                 | MIL, 1 <sub>OH</sub> = -2mA                     | 2.4  | 3.4             |       | Volts |

| <b>▼</b> OH     | Suipar (mair tomage                   | VIN * VIH OF VIL                        |                                                     | COM'L, I <sub>OH</sub> = -2mA                   | 2.4  | 3.4             |       |       |

|                 |                                       |                                         | FR,FS                                               | I <sub>OL</sub> = 12mA                          |      |                 | 0.5   |       |

| Vol             | Output LOW Voltage                    | V <sub>CC</sub> = MIN                   | _                                                   | MIL IOL = 16mA                                  |      |                 | 0.5   | Volts |

| FOL             | VOL Compar East Vollage               | VIN = VIH or VIL                        | A <sub>0-7</sub> , B <sub>0-7</sub>                 | COM'L, IOL = 2.4mA                              |      |                 | 0.5   |       |

| V <sub>IH</sub> | Input HIGH Level                      | Guaranteed input<br>voltage for all in  |                                                     | H                                               | 2.0  |                 |       | Volts |

| VIL             | Input LOW Level                       |                                         | Guaranteed input logical LOW voltage for all inputs |                                                 |      |                 | 8.0   | Volts |

| VI              | Input Clamp Voltage                   | V <sub>CC</sub> = MIN, I <sub>IN</sub>  | V <sub>CC</sub> = MIN, i <sub>IN</sub> = -18mA      |                                                 |      |                 | ~ 1.5 | Volts |

|                 |                                       |                                         | A <sub>0-7</sub> , B <sub>0-7</sub>                 |                                                 |      |                 | - 250 | μΑ    |

| li <u>L</u>     | Input LOW Current                     | V <sub>CC</sub> = MAX,V <sub>IN</sub> = | = 0.5V                                              | CLRR,CLRS                                       |      |                 | - 2.0 | mA    |

| - TE            | ·                                     | Others                                  |                                                     |                                                 |      | - 360           | μΑ    |       |

|                 |                                       |                                         |                                                     | A <sub>0-7</sub> , B <sub>0-7</sub>             |      |                 | 70    |       |

| I <sub>IH</sub> | Input HIGH Current                    | V <sub>CC</sub> = MAX, V <sub>IN</sub>  | = 2.7V                                              | CLRR, CLRS                                      |      |                 | 100   | μΑ    |

| 101             |                                       |                                         |                                                     | Others                                          |      |                 | 20    |       |

| l <sub>i</sub>  | Input HIGH Current                    | V <sub>CC</sub> = MAX, V <sub>IN</sub>  | = 5.5V                                              |                                                 |      |                 | 1.0   | mA    |

|                 | Output Off-state                      |                                         |                                                     | $V_0 = 2.4V$                                    |      |                 | 70    |       |

| Ю               | Leakage Current                       | V <sub>CC</sub> = MAX                   | A <sub>0-7</sub> , B <sub>0-7</sub>                 | $V_0 = 0.4V$                                    |      |                 | - 250 | μΑ    |

| Isc             | Output Short Circuit Current (Note 3) | V <sub>CC</sub> = MAX                   | V <sub>CC</sub> = MAX                               |                                                 | - 30 |                 | - 85  | mA    |

|                 |                                       |                                         |                                                     | $T_A = 0$ °C to + 70°C                          |      |                 | 275   | ]     |

|                 | Power Supply Current                  |                                         | COM, F                                              | T <sub>A</sub> = + 70°C                         |      |                 | 228   | mA    |

| Icc             | (Notes 4,5)                           | V <sub>CC</sub> = MAX                   |                                                     | $T_C = -55^{\circ}C \text{ to } + 125^{\circ}C$ |      | I               | 309   |       |

|                 |                                       |                                         | MIL                                                 | $T_C = + 125$ °C                                |      |                 | 202   |       |

Notes: 1. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

2. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

4. I<sub>CC</sub> is measured with all inputs at 4.5V and all outputs open.

5. Worst case I<sub>CC</sub> is at minimum temperature.

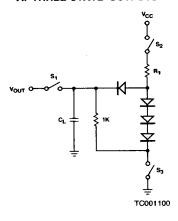

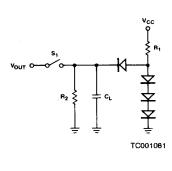

## SWITCHING TEST CIRCUIT

## A. THREE-STATE OUTPUTS

## **B. NORMAL OUTPUTS**

$$\frac{5.0 - V_{BE} - V_{OL}}{I_{OL} + V_{OL}}$$

$$R_1 = \frac{5.0 - V_{BE} - V_{OL}}{I_{OL} + V_{OL}}$$

- Notes: 1. CL = 50pF includes scope probe, wiring and stray capacitances without device in test fixture.

- 2.  $S_1$ ,  $S_2$ ,  $S_3$  are closed during function tests and all AC tests except output enable tests.

- 3.  $S_1$  and  $S_3$  are closed while  $S_2$  is open for  $t_{\mbox{\scriptsize PZH}}$  test.

- S<sub>1</sub> and S<sub>2</sub> are closed while S<sub>3</sub> is open for tpZL test.

- 4. CL = 5.0pF for output disable tests.

## TEST OUTPUT LOADS FOR Am2950/2951 (DIP)

| Pin#<br>(DIP) | Pin Labei        | Test<br>Circuit | R <sub>1</sub> | R <sub>2</sub> |

|---------------|------------------|-----------------|----------------|----------------|

| _             | A <sub>0-7</sub> | Α               | 220            | 1K             |

| _             | B <sub>0-7</sub> | Α               | 220            | 1K             |

| 5             | FS               | В               | 300            | 2.4K           |

| 11            | FR               | В               | 300            | 2.4K           |

#### **Notes on Testing**

ma Pen age

Incoming test procedures on this device should be carefully planned, taking into account the high complexity and power levels of the part. The following notes may be useful:

- Insure the part is adequately decoupled at the test head.

Large changes in V<sub>CC</sub> current when the device switches may cause erroneous function failures due to V<sub>CC</sub> changes.

- Do not leave inputs floating during any tests, as they may start to oscillate at high frequency.

- Do not attempt to perform threshold tests at high speed.

Following an input transition, ground current may change by as much as 400mA in 5-8ns. Inductance in the ground

- cable may allow the ground pin at the device to rise by 100s of millivolts momentarily.

- 4. Use extreme care in defining input levels for AC tests. Many inputs may be changed at once, so there will be significant noise at the device pins and they may not actually reach V<sub>IL</sub> or V<sub>IH</sub> until the noise has settled. AMD recommends using V<sub>IL</sub> ≤ 0V and V<sub>IH</sub> ≥ 3.0V for AC tests.

- To simplify failure analysis, programs should be designed to perform DC, Function and AC tests as three distinct groups of tests.

- 6. To assist in testing, AMD offers complete documentation on our test procedures and, in most cases, can provide Fairchild Sentry programs, under license.

## Am2950A/Am2951A SWITCHING CHARACTERISTICS

The tables below define the Am2950A/Am2951A switching characteristics. Tables A are setup and hold times relative to a clock LOW-to-HIGH transition. Tables B are propagational delays. Tables C are recovery times. Tables D are pulse-width requirements. Tables E are enable/disable times. All measurements are made at 1.5V with input levels at 0V or 3V. All values are in ns with RL on Ai and Bi =  $220\Omega$  and RL on FS and FR =  $300\Omega$ . CL = 50pF except output disable times which are specified at CL = 5pF.

## GUARANTEED CHARACTERISTICS OVER COMMERCIAL OPERATING RANGE

$(T_A = 0 \text{ to } + 70^{\circ}\text{C}, V_{CC} = 4.75 \text{ to } 5.25\text{V}, C_L = 50\text{pF})$

## A. Set-up and Hold Times.

| Input | With<br>Respect | ,  | ts | th |

|-------|-----------------|----|----|----|

| A0-7  | CPR             | 5  |    |    |

| B0-7  | CPS             | 5  |    |    |

| CES   | CPS             | -5 |    |    |

| ČĒR   | CPR             | 5  |    |    |

## B. Propagation Delays

| Input  | A0-7 | B0-7 | FS | FR |

|--------|------|------|----|----|

| CPS _  |      |      |    |    |

| CPR _  |      |      |    |    |

| CLRS _ |      |      |    |    |

| CLRR   |      |      |    |    |

#### C. Recovery Times

| From   | То    | tREC |

|--------|-------|------|

| CLRS _ | CPS   |      |

| CLRR   | CPR _ |      |

## D. Pulse-Width Requirements

| Input | Min LOW<br>Pulse Width | Min HIGH<br>Pulse Width |

|-------|------------------------|-------------------------|

| CPS   |                        |                         |

| CPR   |                        |                         |

| CLRS  |                        |                         |

| CLRR  |                        |                         |

#### E. Enable/Disable Times

| From | То   | Disable | Enable |

|------|------|---------|--------|

| ŌĒAS | A0-7 |         |        |

| ŌĒBR | B0-7 |         |        |

## GUARANTEED CHARACTERISTICS OVER MILITARY OPERATING RANGE

$(T_C = -55 \text{ to } + 125^{\circ}\text{C}, \ V_{CC} = 4.5 \text{ to } 5.5\text{V}, \ C_L = 50\text{pF})$

## A. Set-up and Hold Times.

| Input | With<br>Respec | ts   | th |

|-------|----------------|------|----|

| A0-7  | CPR            |      |    |

| B0-7  | CPS            | <br> |    |

| CĒS   | CPS            |      |    |

| CER   | CPR            | <br> |    |

#### **B. Propagation Delays**

| Input  | A0-7 | B0-7 | FS | FR |

|--------|------|------|----|----|

| CPS _F |      |      |    |    |

| CPR _  |      |      |    |    |

| CLRS _ |      |      |    |    |

| CLRR   |      |      |    |    |

#### C. Recovery Times

| From   | То    | tREC |

|--------|-------|------|

| CLRS   | CPS _ |      |

| CLRR _ | CPR   | _    |

#### D. Pulse-Width Requirements

| Input | Min LOW<br>Pulse Width | Min HIGH<br>Pulse Width |

|-------|------------------------|-------------------------|

| CPS   |                        |                         |

| CPR   |                        |                         |

| CLRS  |                        |                         |

| CLRR  |                        |                         |

#### E. Enable/Disable Times

| From | То   | Disable | Enable |

|------|------|---------|--------|

| ŌĒAS | A0-7 |         |        |

| ŌĒBR | B0-7 |         |        |

## Am2950/Am2951 SWITCHING CHARACTERISTICS

The tables below define the Am2950/Am2951 switching characteristics. Tables A are set-up and hold times relative to a clock LOW-to-HIGH transition. Tables B are propagational delays. Tables C are recovery times. Tables D are pulse-width requirements. Tables E are enable/disable times. All measurements are made at 1.5V with input levels at 0V or 3V. All values are in ns with RL on Ai and Bi =  $220\Omega$  and RL on FS and FR =  $300\Omega$ . CL = 50pF except output disable times which are specified at CL = 5pF.

## GUARANTEED CHARACTERISTICS OVER COMMERCIAL OPERATING RANGE

$(T_A = 0 \text{ to } + 70^{\circ}\text{C}, \ V_{CC} = 4.75 \text{ to } 5.25\text{V}, \ C_L = 50\text{pF})$

#### A. Set-up and Hold Times.

| Input | With<br>Respect To |    | ts     | th |

|-------|--------------------|----|--------|----|

| A0-7  | CPR                |    | 7      | 5  |

| B0-7  | CPS                |    | 7      | 5  |

| CES   | CPS                |    | *19/15 | 4  |

| CEA   | CPR                | _5 | *19/15 | 4  |

## B. Propagation Delays

| Input  | A0-7   | B0-7   | FS | FR      |

|--------|--------|--------|----|---------|

|        |        | 50-7   |    | • • • • |

| CPS _  | *30/26 |        | 20 | _       |

| CPR _  | _      | *30/26 | -  | 20      |

| CLRS   | _      | -      | 22 | _       |

| CLRR _ | _      | _      |    | 22      |

## C. Recovery Times

| From   | То     | tREC |

|--------|--------|------|

| CLRS _ | CPS _F | 31   |

| CLRR J | CPR _  | 31   |

#### D. Pulse-Width Requirements

| Input | Min LOW<br>Pulse Width | Min HiGH<br>Pulse Width |

|-------|------------------------|-------------------------|

| CPS   | 20                     | 20                      |

| CPR   | 20                     | 20                      |

| CLRS  | 20                     | 20                      |

| CLRR  | 20                     | 20                      |

## E. Enable/Disable Times

| From | То   | Disable | Enable |

|------|------|---------|--------|

| ŌĒAS | A0-7 | 22      | 27     |

| ŌĒBR | B0-7 | 22      | 27     |

\*Where two numbers appear, the first is the Am2950 spec, the second is the Am2951 spec.

## GUARANTEED CHARACTERISTICS OVER MILITARY OPERATING RANGE

$(T_C = -55 \text{ to } + 125^{\circ}\text{C}, \ V_{CC} = 4.5 \text{ to } 5.5\text{V}, \ C_L = 50\text{pF})$

## A. Set-up and Hold Times.

| Input | Wi  |     | ts     | th |

|-------|-----|-----|--------|----|

| A0-7  | CPR | _5_ | 11     | 8  |

| B0-7  | CPS |     | 11     | 8  |

| CES   | CPS |     | *20/15 | 4  |

| CER   | CPR |     | *20/15 | 4  |

## **B. Propagation Delays**

| Input | A0-7   | B0-7   | FS | FR |

|-------|--------|--------|----|----|

| CPS   | *35/28 | -      | 20 |    |

| CPR   | _      | *35/28 | -  | 20 |

| CLRS  | _      | -      | 22 | _  |

| CLRR  | _      | -      | -  | 22 |

## C. Recovery Times

| From   | То    | tREC |

|--------|-------|------|

| CLRS _ | CPS   | 34   |

| CLRR   | CPR _ | 34   |

## D. Pulse-Width Requirements

| Min LOW<br>Input Pulse Width |    | Min HIGH<br>Pulse Width |

|------------------------------|----|-------------------------|

| CPS                          | 20 | 20                      |

| CPR                          | 20 | 20                      |

| CLRS                         | 20 | 20                      |

| CLRR                         | 20 | 20                      |

#### E. Enable/Disable Times

| From | То   | Disable | Enable |

|------|------|---------|--------|

| ŌĒAS | A0-7 | 24      | 28     |

| ŌĒBR | B0-7 | 24      | 28     |

\*Where two numbers appear, the first is the Am2950 spec, the second is the Am2951 spec.