,24小时加急出货

TDA8204

# NICAM DECODER

- HIGHLY INTEGRATED TWO-CHIP SOLU-TION FOR NICAM DEMODULATION (using TDA8205 QSPK)

- DATA AND SOUND RECOVERY ACCORD-ING TO EBU SPB 424 SPECIFICATIONS

- I<sup>2</sup>S INTERFACE FOR DIGITAL AUDIO PUR-POSES (14-bit samples, 32kHz word select clock, 896kHz serial clock)

- 4 TIMES UP SAMPLING DIGITAL FILTER AND NOISE SHAPER

- I<sup>2</sup>C INTERFACE FOR MICROCONTROLLER SOFTWARE DRIVE

- PAY TV APPLICATION CAPABILITIES

- AUTOMATIC ERROR MONITORING (programmable error rate limit)

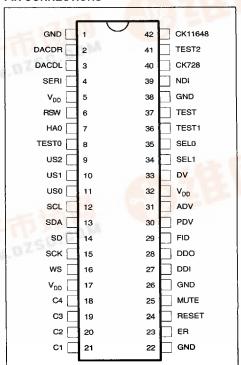

#### PIN CONNECTIONS

#### DESCRIPTION

The TDA8204 performs two main functions, first one is NICAM decoding, second one is audio signal recovery (DAC) combined with audio signal switching (Matrix). An I2S output is provided for digital audio when required and all functions of both the TDA8204 and the TDA8205 are accessed via an on-chip I<sup>2</sup>C bus interface. The I<sup>2</sup>S interface can be used as an input for converting to analog the D2MAC sound decoded by STV3830.

october 1993

7929237 0059093

1/11

991

# 204-01 TBL

# PIN ASSIGMENT

| Pin N° | Pin Name        | Function                                  | Pin N° | Pin Name        | Function                          |

|--------|-----------------|-------------------------------------------|--------|-----------------|-----------------------------------|

| 1      | GND             | Ground                                    | 22     | GND             | Ground                            |

| 2      | DACDR           | PWM Data Output Right                     | 23     | ER              | Error Monitor Flag Output         |

| 3      | DACDL           | PWM Data Output Left                      | 24     | RESET           | Reset                             |

| 4      | SERI            | Inter Chip Serial Bus Output              | 25     | MUTE            | NICAM Mute                        |

| 5      | $V_{DD}$        | +5V Supply                                | 26     | GND             | Ground                            |

| 6      | RSW             | Reserve Sound Switch Status/Control       | 27     | DDI             | Descrambled Data Input            |

| 7      | HA0             | Hardware Address Selection                | 28     | DDO             | Descrambled Data Output           |

| 8      | TEST0           | To be connected to V <sub>DD</sub> or GND | 29     | FID             | Frame Identification Flag Output  |

| 9      | US2             | User bit 2 (input)                        | 30     | PDV             | Parity Data Valid Flag Output     |

| 10     | US1             | User bit 1 (output)                       | 31     | ADV             | Additional Data Valid Flag Output |

| 11     | US0             | User bit 0 (output)                       | 32     | V <sub>DD</sub> | +5V Supply                        |

| 12     | SCL             | I <sup>2</sup> C Bus Clock                | 33     | DV              | Data Valid Flag Output            |

| 13     | SDA             | I <sup>2</sup> C Bus Data                 | 34     | SEL1            | Language Selection 1 Input        |

| 14     | SD              | I <sup>2</sup> S Bus Data                 | 35     | SEL0            | Language Selection 0 Input        |

| 15     | SCK             | I <sup>2</sup> S Bus Clock                | 36     | TEST1           | Not to be connected               |

| 16     | ws              | I <sup>2</sup> S Bus Word Select          | 37     | TEST            | To be connected to GND            |

| 17     | V <sub>DD</sub> | +5V Supply                                | 38     | GND             | Ground                            |

| 18     | C4              | Application Control Bit 4 Flag            | 39     | NDI             | NICAM Data Input                  |

| 19     | СЗ              | Application Control Bit 3 Flag            | 40     | CK728           | 728kHz bit Clock Output           |

| 20     | C2              | Application Control Bit 2 Flag            | 41     | TEST2           | Not to be connected               |

| 21     | C1              | Application Control Bit 1 Flag            | 42     | CK11648         | 11.648MHz bit Clock Input         |

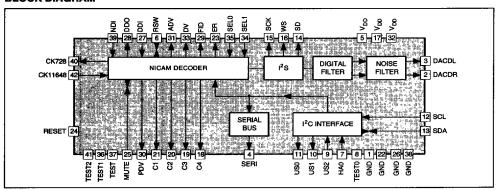

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                   | Value       | Unit |

|------------------|-----------------------------|-------------|------|

| V <sub>DD</sub>  | Supply Voltage              | 7           | V    |

| Ptot             | Total Power Dissipation     | 1.2         | W    |

| Toper            | Operating Temperature Range | 0, + 70     | °C   |

| T <sub>stg</sub> | Storage Temperature Range   | - 20, + 150 | °C   |

#### THERMAL DATA

|                       |                                         |       |      | ر |

|-----------------------|-----------------------------------------|-------|------|---|

| Symbol                | Parameter                               | Value | Unit | 8 |

| R <sub>th (r-a)</sub> | Thermal Resistance Juntion-ambient Max. | 67    | °C/W | ž |

2/11

7929237 0059094 030 🚥

992

# **ELECTRICAL CHARACTERISTICS** (T<sub>amb</sub> = 25°C, V<sub>DD</sub> = 5V, unless otherwise specified)

| Symbol          | Parameter            | Min. | Тур. | Max. | Unit |

|-----------------|----------------------|------|------|------|------|

| UPPLY           |                      |      |      |      |      |

| V <sub>DD</sub> | Supply Voltage Range | 4.75 | 5    | 5.25 | ٧    |

| IDD             | Supply Current       | 30   | 60   | 92   | mA   |

#### OUTPUTS

| DACDR, D        | DACDL, SERI, US1, SCK, WS, C4, ER, DDO, FID, PDV, | ADV, DV, CK728      |     |    |

|-----------------|---------------------------------------------------|---------------------|-----|----|

| VoL             | Low Output Voltage (IoL = -4mA)                   |                     | 0.4 | V  |

| V <sub>OH</sub> | High Output Voltage (I <sub>OH</sub> = 4mA)       | 0.7 V <sub>DD</sub> |     | V  |

| US0 (oper       | n drain)                                          |                     |     |    |

| Vol             | Low Output Voltage (I <sub>OL</sub> = -4mA)       |                     | 0.4 | V  |

| I <sub>LK</sub> | High Output Current (leakage)                     |                     | ±2  | μΑ |

| CONSTAN         | NT CURRENT LED DRIVERS C1, C2, C3                 |                     |     |    |

| loL             | Low Output Current (V <sub>OL</sub> = 0.4V)       | - 10                |     | mA |

# **INPUTS**

| HA0, US2 | , RESET, DDI, SEL1, SEL0, TEST, NDI, CK11 |                     |     |    |

|----------|-------------------------------------------|---------------------|-----|----|

| VIL      | Low Input Voltage                         |                     | 0.8 | ٧  |

| ViH      | High Input Voltage                        | 0.6 V <sub>DD</sub> |     | V  |

| ILK      | Input Leakage Current                     |                     | ± 2 | μA |

#### **BI-DIRECTIONAL**

|                 | RSW, MUTE                                     |                     |     |    |

|-----------------|-----------------------------------------------|---------------------|-----|----|

| Vol             | Low Output Voltage (I <sub>OL</sub> = -4mA)   |                     | 0.4 | V  |

| Vон             | High OUtput Voltage (I <sub>OH</sub> = 100μA) | 0.7 V <sub>DD</sub> |     | ٧  |

| VIL             | Low Input Voltage                             |                     | 0.8 | ٧  |

|                 | SD                                            |                     |     |    |

| Vol             | Low Output Voltage (I <sub>OL</sub> = -4mA)   |                     | 0.4 | ٧  |

| V <sub>OH</sub> | High Output Voltage (I <sub>OH</sub> = 4mA)   | 0.7 V <sub>DD</sub> |     | ٧  |

| VIL             | Low Input Voltage                             |                     | 0.8 | ٧  |

| VIH             | High Input Voltage                            | 0.6 V <sub>DD</sub> |     | V  |

| ILK             | Input Leakage Current                         |                     | ± 2 | μА |

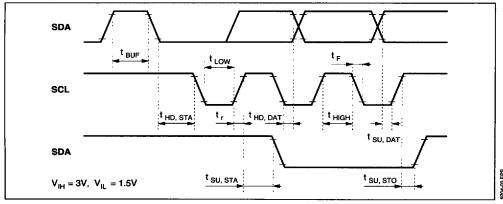

# I<sup>2</sup>C INTERFACE

|        | SCL                                                           |   |                 |     |

|--------|---------------------------------------------------------------|---|-----------------|-----|

| VIL    | Low Input Voltage                                             | 0 | 1.5             | ٧   |

| VIH    | High Input Voltage                                            | 3 | V <sub>DD</sub> | ٧   |

| fscL   | SCL Clock Frequency                                           |   | 100             | kHz |

| tr, tf | Input Rise and Fall Times                                     |   | 2               | μs  |

| քըլ    | Input Leakage Current (V <sub>I</sub> = 5.5V)                 |   | 10              | μΑ  |

| Ci     | Input Capacitance                                             |   | 7               | pF  |

|        | SDA                                                           |   |                 |     |

| VIL    | Input Low Voltage                                             | 0 | 1.5             | V   |

| VIH    | Input High Voltage                                            | 3 | V <sub>DD</sub> | V   |

| tr, tr | Input Rise / Fall Times                                       |   | 2               | μs  |

| իլ     | Input Leakage Current (V <sub>I</sub> = 5.5V with output off) | , | 10              | μΑ  |

| Cı     | Input Capacitance                                             |   | 7               | pF  |

| Vol    | Low Output Voltage (I <sub>OL</sub> = 3mA)                    | 0 | 0.5             | V   |

| tf     | Output Fall Time between 3.0V and 1.0V                        |   | 200             | ns  |

| Cı     | Load Capacitance                                              |   | 400             | pF  |

3/11

# **ELECTRICAL CHARACTERISTICS** (continued)

| Symbol                            | Parameter                                                             | Min. | Тур. | Max. | Unit     |

|-----------------------------------|-----------------------------------------------------------------------|------|------|------|----------|

| I <sup>2</sup> C BUS TIM          | ING                                                                   |      |      |      |          |

|                                   | SERIAL BUS (referred to V <sub>IH</sub> = 3V, V <sub>IL</sub> = 1.5V) |      |      |      |          |

| tLOW<br>thigh                     | Low Period Clock<br>High Period Clock                                 | 4 4  |      |      | μs<br>μs |

| tsu, dat                          | Data Set-up Time                                                      | 250  |      |      | ns       |

| t <sub>HD</sub> , d <sub>AT</sub> | Data Hold Time                                                        | 170  |      |      | ns       |

| tsu, Sto                          | Stop Set-up Time from Clock High                                      | 4    |      |      | μs       |

| t <sub>BUF</sub>                  | Start Set-up Time following a Stop                                    | 4    |      |      | μs       |

| t <sub>HD</sub> , S <sub>TA</sub> | Start Hold Time                                                       | 4    |      |      | μs       |

| tsu, Sta                          | Start Set-up Time following Clock Low to High Transition              | 4    |      |      | μs       |

Figure 1: I<sup>2</sup>C Serial Bus Timing

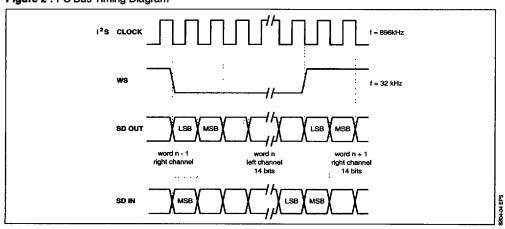

Figure 2: I<sup>2</sup>S Bus Timing Diagram

4/11 994

7929237 0059096 903

#### **FUNCTION DESCRIPTION**

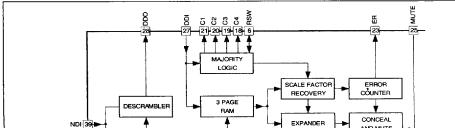

The TDA8204 is partitioned into 6 major parts shown in the block diagram.

The NICAM Decoder performs data and sound recovery from the signals specified in EBU SPB 424. The expanded digital audio signals (14-bit) are made available at the digital audio interface (I2S) in a serial multiplex of left and right channels. They are also processed by a 4 times upsampling digital filter and noise shaper which results in a high speed digital data stream at the output pins DACDL/DACDR. This data stream can be applied to the 1-bit D-A convertors contained in the TDA8205.

The TDA8204 is I<sup>2</sup>C bus controlled and provides control over the functions of the TDA8205 by means of a serial inter-chip bus.

#### 1 - NICAM Decoder

#### 1.1 - BLOCK DIAGRAM (see Figure 3)

#### 1.2 - DESCRIPTION

NICAM frame alignment requires searching out a frame alignment word (FAW) and a 16 frame seguence conveyed by C0 bit. Because of noise, interferences, errors in the incoming NICAM Data, aliases of the FAW, a robust scheme is implemented. It ensures the decoder will align, and stay aligned, to signals beyond the limit of maximum useable error rate. Thanks to a 511 bit PRBS synchronized by the recovered clock and a modulo 2 adder, original data are recovered. This data stream can be processed externaly for de-encryption in Pay TV applications using descrambled data Pins DDO. DDI.

To allow simultaneous reading and writing of mono/stereo samples, de-interleaved data frames are stored in a 3 page RAM.

The 10-bit input audio samples are expanded to 14-bit using scale factor bits according to NICAM decoding rules. Samples in error by the parity check are replaced by interpolated one or repeated.

Mute is set according to an error counter when the error rate exceeds error rate limit (ERL) and reset when the error rate is below ERL/4.

Application control information (bit C1, C2, C3, C4) is recovered by majority decision logic over 16 frames, the C1, C2, C3, C4 bits can be read in SR0 register and are set on the C1, C2, C3, C4 pins according to the state of bit 0 (BEA) of the CR2 register.

#### 2 - Digital Filter and Noise Shaper

A digital filter performs 4X upsampling in two stages. The main FIR 2x upsampler is followed by a smaller 2x FIR upsampler. Digital upsampling means a much simpler post-DAC reconstruction filter can be used thus saving on external component count and cost.

A noise shaper converts the samples from the digital filter into two high speed serial bitstreams which can be applied to the DACs in the TDA8205.

#### 3 - I<sup>2</sup>S Bus

A standard three-wire interface, conforming to the I<sup>2</sup>S bus protocol, is provided, allowing connection of an external DAC or DAT interface. Audio samples contain 14-bit, so 16-bit DACs will pad the two LSBs with 0. The word select clock operates at 32kHz and the serial clock at 896kHz.

By setting SDI bit of CR2 to 1, the I<sup>2</sup>S interface can receive the D2MAC sound decoded by the STV3840. This prevents duplicating the dual D/A converter.

AND MUTE

TO FILTER

ADDRESS

GENERATOR

Figure 3: NICAM Decoder Block Diagram

PDV 30◀

DV 33◀

FID 29-◀ ADV 31 ◀

5/11

FRAME

CONTROL

#### 4 - Interchip Bus

A one-line serial bus provides interchip communications allowing control of all functions through the single I<sup>2</sup>C bus interface.

#### 5 - I<sup>2</sup>C Bus

An I<sup>2</sup>C bus interface provides access to control and status registers within the two chips to allow control of their functions and monitoring of status. A digital filter is included to improve noise immunity.

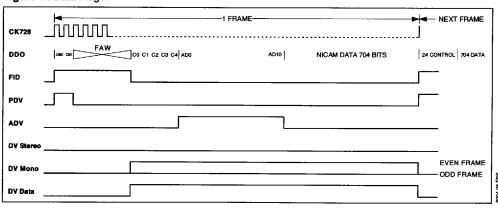

#### 5.1 - DATA FLAGS (see Figure 4)

These indicate the status of the descrambled data on the DDO pin. They are inhibited if the decoder is out of alignement.

- FID : Frame alignment word (scrambled)

- PDV : Parity Data Valid, CIB0 and CIB1 overwrite the first 2 bits of FAW

- ADV: 11 additional data bits

- DV : Data valid (mode dependant)

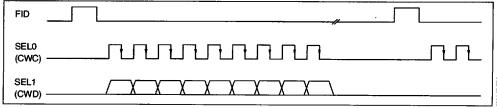

# 5.2 - DECRYPTION (see Figure 5)

The PRBS generator (used for descrambling) is normally preset to all ones at the start of each frame. However, it is possible to preset it to any value on each frame by means of a code word clock

(CWC) and serial code word data (CWD) interface on pins SEL0 and SEL1.

CWD, which is clocked in on the negative going edges of the CWC clock, can be sent anywhere during the frame except when FID = 1. The CWC is asynchronous with respect to the Nicam clock and the CWD will be used on the following frame. During the time FID = 1, the levels on the SELO, SEL1 pins are read for language selection. Code words for descrambler presetting may be sent in either an 8-bit or 9-bit formats. There are four possibilities:

- if 7 or less clock cycles are counted on CW-clock during a frame, the PRBS generator is preset to all ones:

- if 8 clock cycles are counted, 8 bits of CW-data are clocked into the shift register, the first bit of the previous transfer now moving to bit 9 position in the shift register. The resulting value is used to preset the PRBS generator on the next frame.

- if 9 clock cycles are counted, the CW-data (which has been clocked into a 9-bit shift register) is used to preset the PRBS generator on the next frame.

- if 10 or more clock cycles are counted, only the first 9 bits of the CW-data are used and loaded into the PRBS generator on the next frame.

Figure 4: Data Flags

Figure 5: PRBS Presetter

6/11

7929237 0059098 786

996

#### 5.3 - SOFTWARE SPECIFICATION

Software control of IC's is given by programming four registers, one read only status register (SR0) and three read and write control registers (CR1, CR2, CR3).

Transmit format : S = Start, A = Acknowledge P = stop

| s  | CHIP<br>ADDRESS | 0 | Α | REG SUB<br>ADDRESS | Α | DATA | Α | Р |

|----|-----------------|---|---|--------------------|---|------|---|---|

| L. | 7.001.1200      |   |   | 710011200          |   |      |   |   |

#### Receive format:

| s | CHIP<br>ADDRESS | 1 | Α | SR0<br>DATA | Α | CR1<br>DATA | Α | Р |

|---|-----------------|---|---|-------------|---|-------------|---|---|

|---|-----------------|---|---|-------------|---|-------------|---|---|

Note: All registers are read sequentially; device status and the contents of all registers may be read. The sequence may be terminated by not acknowledging (NOACK) the slave

#### Chip address

|   | 1  | 0 | 1 | 1 | 0 | 1 | HAO | R/W |

|---|----|---|---|---|---|---|-----|-----|

| М | SB |   |   |   |   |   |     | LSB |

# HAO: Hardware address selection pin

#### Register addresses

| _            | <u> </u>   |   |   |   |   |          |   |   |                  |

|--------------|------------|---|---|---|---|----------|---|---|------------------|

| Reg.<br>Name | Sub Adress |   |   |   |   | Function |   |   |                  |

| SR0          | 0          | 0 | 0 | 0 | 0 | 0        | 0 | 0 | NICAM status     |

| CR1          | 0          | 0 | 0 | 0 | 0 | 0        | 0 | 1 | Matrix and mutes |

| CR2          | 0          | 0 | 0 | 0 | 0 | 0        | 1 | 0 | NICAM control    |

| CR3          | 0          | 0 | 0 | 0 | 0 | 0        | 1 | 1 | Switches         |

#### Register contents

#### SR0: NICAM status (read only)

|     |    |    | •  |    |     |     |     |

|-----|----|----|----|----|-----|-----|-----|

| US2 | C1 | C2 | СЗ | C4 | MUT | LA2 | L/S |

| US2 | 0  | 0  | 0  | 1  | 1   | 1   | 1   |

MSB

US2 :

LSB

L/S : • If FN1 bit of CR2 is 0, LS bit is loss of frame alignment status LS =1, FAW is lost

LS = 0 FAW is identified

If FN1 bit of CR2 is 1. LS bit is selected system status

LS = 1, B/G standard LS = 0, I standard

LA2: Loss of sub-frame alignment (1 = loss of alignment)

MUT: NICAM mute  $(\bar{1} = DAC \text{ outputs muted})$

C4 Reserve sound flag (1 = FM backup)

C3 Application control bit 3 C2 Application control bit 2 C1 Application control bit 1

User bit 2 (input) US2 bit indicates the state of US2 input Pin

#### CR1: Matrix and mutes (read and write register)

|     |    |    |    |    |    | _   |     |

|-----|----|----|----|----|----|-----|-----|

| Q1  | QO | 12 | 11 | 10 | G0 | AUM | FRE |

| 0   | 0  | 0  | 0  | 0  | 0  | 0   | 0   |

| MSB |    |    |    | •  | •  |     | LSB |

Qn Output select (see tables) Input select (see tables) In

G0 Auxiliary output gain, 0 = 0dB, 1 = 6dB

AUM: Auxiliary output mute, 0 = no-mute,

1 = mutéd

FRE : Free run clock VCXO for set up, 0 = normal, 1 = free run

To set crystal series capacitor

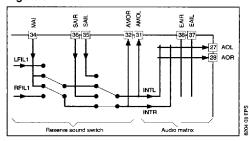

## Switches and Matrix Description

#### Figure 6

#### Output selection

| Q1 | QO | Output |

|----|----|--------|

| 0  | 0  | AOL    |

| 0  | 1  | AOR    |

#### Mute and gain selection

| Q0 | 12 | Mute | Gain   |

|----|----|------|--------|

| 0  | 0  | OFF* | -      |

| 0  | 1  | ON*  | -      |

| 1  | 0  | -    | 0dB**  |

| 1  | 1  |      | +6dB** |

<sup>\*</sup> Mute is activated by left channel selection

\*\* Gain is activated by right channel selection

#### Input selection

| l1 | 10 | Input |

|----|----|-------|

| 0  | 0  | INTL  |

| 0  | 1  | INTR  |

| 1  | 0  | EAIL  |

| 1  | 1  | EAIR  |

#### Example of programming

First 00100X X X

step INTL connected to AOL, mute ON on

AOL/AOR

Second: 01011X X X step

EAIR connected to AOR, gain 0dB on

AOL/AOR

Thrird 00000XXX step INTL connected to AOL, mute OFF on

AOL/AOR

The power up default configuration is 0dB and unmute for both channels AOL/R, and INTL connected to AOL, and INTR connected to AOR.

#### CR2: NICAM control (read and write register)

| SDI | ECT | MAE | FN1 | UMT | LA1 | LA0 | BEA |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| MSB |     |     | •   |     |     |     | LSB |

SDI: I<sup>2</sup>S direction

0 = Output, 1 = Input ECT: Bit error rate counting time

0 = 128 ms, 1 = 64 msMAE: Max allowed errors

0 = 511.1 = 255FN1: Set function of bit 0 in SR0, 0 = loss of

alignment (status), 1 = system status (I or

UMT: Un-mute NICAM, 1 = un-mute, 0 = mute LA1 : Language select 1 (LA1 ⊕ SEL1)

LA0 : Language select 0 (LA0 ⊕ SEL0)

BEA: Set C1-C3 function

| ECT | MAE | BER MUTE                          |

|-----|-----|-----------------------------------|

| 0   | 0   | 8.9 x 10 <sup>-3</sup> (1 in 112) |

| 0   | 1   | 4.4 x 10 <sup>-3</sup> (1 in 225) |

| 1   | 0   | 1.8 x 10 <sup>-2</sup> (1 in 56)  |

| 1   | 1   | 8.9 x 10 <sup>-3</sup> (1 in 112) |

#### Un-mute at BER/4.

| TDA8204      | BEA |                  |  |  |  |

|--------------|-----|------------------|--|--|--|

| Output (Pin) | 0   | 1                |  |  |  |

| C1 (21)      | C1* | Single mono mode |  |  |  |

| C2 (20)      | C2* | Dual mono mode   |  |  |  |

| C3 (19)      | C3* | Stereo mode      |  |  |  |

\* Application control bit of NICAM signal

Note: C4 pin remains unchanged. The function of C1-C4 in SR0 remains unchanged.

#### CR3: Switches (read and write register)

| US | 31 I | SO | AUT | IBG | FS1 | FS0 | Х | SYN |

|----|------|----|-----|-----|-----|-----|---|-----|

| 0  |      | 0  | 1   | 0   | 0   | 0   | 0 | 1   |

| MS | B    |    |     |     |     |     |   | LSB |

US1 : User bit 1 (output)

USO : User bit 0 (output)

AUT: Automatic selection, 1 = enable IBG Select system I or B/G, 1 = B/G

FSn Force switch (see table)

SYN: 1 = synthesiser, 0 = dual VCXO

(carrier loop)

| FS1 | FS0 | Selection  |

|-----|-----|------------|

| 0   | 0   | Auto NICAM |

| 0   | 1   | FM-Mono    |

| 1   | 0   | FM-Stereo  |

| 1   | 1   | NICAM      |

#### NICAM STAND-ALONE APPLICATION

The NICAM kit has been designed to be monitored by the I<sup>2</sup>C bus; nevertheless stand-alone working capability is offered to the designer for low cost applications.

In order to know the status of the kit in stand-alone mode, consider the contents of the four I2C registers at power-ON (4 registers : SR0 - CR1 - CR2 -CR3). Hardware configurable pins will be described

#### 1 - Power-ON Configuration

#### SR0 (status)

| US2 | C1 | C2 | СЗ | C4 | MUT | LA2 | L/S |

|-----|----|----|----|----|-----|-----|-----|

| US2 | 0  | 0  | 0  | 1  | 1   | 1   | 1   |

| MSB |    |    |    |    |     |     | LSB |

US<sub>2</sub> Not used in stand-alone

C1 Application control bit status for C2

NICAM signal СЗ

C4 Reserve Sound Flag

MUT DAC outputs muted (demuted as soon

as NICAM appears) LA2 the subframe alignment is been lost

L/S FAW status (FN1 of CR2 = 0)

# CR1 (RW)

| (-  |    |    |    |    |    |     |     |

|-----|----|----|----|----|----|-----|-----|

| Q1  | QO | 12 | 11 | 10 | G0 | AUM | FRE |

| 0   | 0  | 0  | 0  | 0  | 0  | 0   | 0   |

| MSB |    |    |    |    |    |     | LSB |

Q1

Q0 NICAM sound is sent on all matrix 12

outputs and on AMOx pins

11 G0 Gain = 0dB on AMOx AUM AMOx pins un-muted FRE VCXO in normal mode

# CR2 (R/W)

| SDA | ECT | MAE | FN1 | UMT | LA1 | LA0 | BEA |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| MSB |     |     |     |     |     |     | LSB |

SDA Normal mode ECT & BER = 1/112

MAE

Bit L/S of SR0 set to alignment loss FN1

status

**UMT** TDA8204 mute pin 25 to 0 LA1 Result depending of SEL1 LA<sub>0</sub> Result depending of SEL0

BEA Beacon decoding mode but all diodes

are OFF until a NICAM signal has been

found

## CR3 (R/W)

| US1 | US0 | AUT | IBG | FS1 | FS0 | X | SYN |

|-----|-----|-----|-----|-----|-----|---|-----|

| 0   | 0   | 1   | 0   | 0   | 0   | 0 | 1   |

| MSB |     |     |     | -   |     |   | LSB |

US<sub>1</sub> Not used in stand-by mode

Not used in stand-by mode US0

AUT Automatic standard

8/11

7929237 0059100 164

IBG Standard I (don't care)

FSn Set to Auto NICAM (if NICAM fails, FM

mono is selected)

FN2 Not used

SYN Synthesizer selected

#### 2 - Hardware Configurable Pins

2.1 - TDA8204 - PIN 6 - (RSW)

- as an output :

status of the RSW switch

- 0 = FM mono

- 1 = NICAM

- as an input :

- 0 = FM mono (forced)

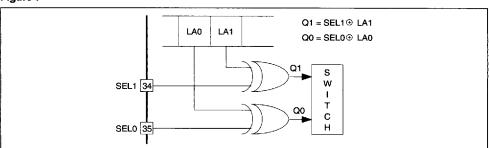

2.2 - TDA8204 - PINS 34/35 - (SEL0/SEL1)

(see Figure 7)

- to select the language in case of bilingual operation

- selected value is related to LA0 and LA1

As the  $I^2C$  bus is not used LA0 and LA1 = 0 (power-ON condition) / SEL0 = Q0, SEL1 = Q1 The 4 choices are summarized in the table below.

|      | <del>-</del> |       |  |

|------|--------------|-------|--|

| SEIN | CEI1         | DACDI |  |

| SEL0 | SEL1 | DACDL | DACDR |

|------|------|-------|-------|

| 0    | 0    | M1    | M2    |

| 0    | 1    | M1    | M1    |

| 1    | 0    | M2    | M2    |

| 1    | 1    | M2    | M1    |

M1 = Mono 1

M2 = Mono 2

VII - 2.3. TDA8204 - PIN 25 - (MUTE)

- as an output :

status of the DAC

- 0 = unmuted

- 1 = muted

- as an input :

- 0 = unmute DAC (forced)

Figure 7

#### **APPLICATION DIAGRAMS**

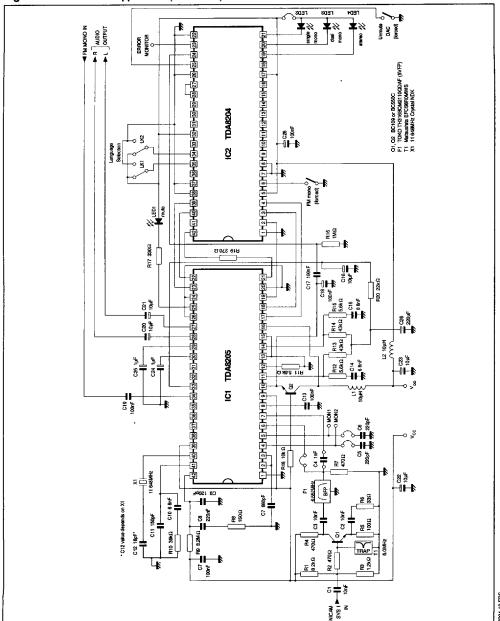

Figure 8 : Stand Alone Application (I standard)

10/11

7929237 0059102 T37

ma Pe

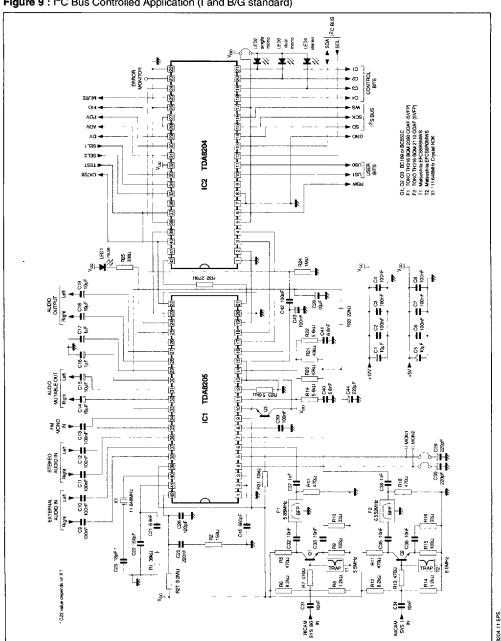

Figure 9: I<sup>2</sup>C Bus Controlled Application (I and B/G standard)