## 查询10938P供应商

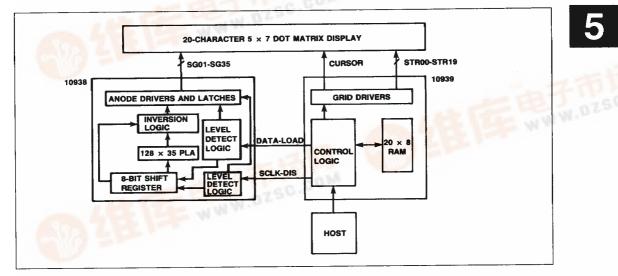

# 10938 and 10939 Dot Matrix Display Controller

### DESCRIPTION

The Rockwell 10938 and 10939 Dot Matrix Display Controller is a two-chip MOS/LSI general purpose display controller system designed to interface to dot matrix displays (vacuum-fluorescent or LED).

The two-chip set will drive displays with up to 35 anodes (dots) and up to 20 grids (characters) plus a cursor. The chips can be cascaded to drive larger displays of as many as 80 characters. An internal PLA-type decoder provides character decoding and dot pattern generation for the full 96-character ASCII set and an additional 32 special characters.

### ORDERING INFORMATION

| Part    | Package | Temperature |

|---------|---------|-------------|

| Number  | Type    | Range (°C)  |

| 10938P  | Plastic | 0 to +70    |

| 10938PE | Plastic | -40 to +85  |

| 10939P  | Plastic | 0 to +70    |

| 10939PE | Plastic | -40 to +85  |

### FEATURES

- 20-character display driver cascadable to 80

- Standard 5 × 7 character font.

- Separate cursor driver output

- Direct drive capability for vacuum-fluorescent displays

- 128 × 35 PLA provides segment decoding for full 96-character ASCII set, plus 32 special characters

WW.DZ

- Serial or parallel data input for 8-bit display and control characters

- Brightness, refresh rate, and display mode controls

- 40-pin DIP

Block Diagram of 10938 and 10939

Order No. D96 Rev. 4, June 1987

## **INTERFACE DESCRIPTION**

### **10938 Pin Functions**

| Signal Name     | Pin No.     | Function                         |

|-----------------|-------------|----------------------------------|

| V <sub>SS</sub> | 2           | Power and signal reference       |

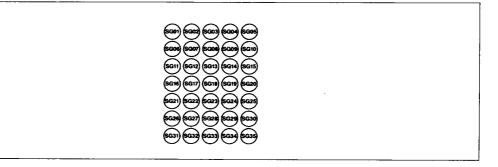

| SG01-SG35       | 3-25, 27-38 | Anode driver outputs             |

| SCLK-DIS        | 39          | Serial data shift clock          |

| DATA-LOAD       | 40          | Serial data output/latch control |

| Vop             | 1           | DC Power                         |

| V <sub>GG</sub> | 26          | Display voltage                  |

| V₀₀ □ 1             | 40 DATA-LOAD         |

|---------------------|----------------------|

| V <sub>ss</sub> □ 2 | 39 뉟 SCLK-DIS        |

| SG35 C 3            | 38 🏳 SG01            |

| SG34 📥 4            | 37 🗅 SG02            |

| SG33 🖬 5            | 36 🗗 SG03            |

| SG32 🖸 6            | 35 🗅 SG04            |

| SG31 []7            | 34 🗅 SG05            |

| SG30 🛛 8            | 33 🗅 SG06            |

| SG29 [] 9           | 32 🗅 SG07            |

| SG28 C 10           | 31 🗅 SG08            |

| SG27 d 11           | 30 🗅 SG09            |

| SG26 [ 12           | 29 🗅 SG10            |

| SG25 📥 13           | 28 🖯 SG11            |

| SG24 d 14           | 27 👌 SG12            |

| SG23 [ 15           | 26 🖸 V <sub>GG</sub> |

| SG22 16             | 25 SG13              |

| SG21 17             | 24 SG14              |

| SG20 18             | 23 SG15              |

| SG19 d 19           | 22 G16               |

| SG18 d 20           | 21 占 SG17            |

10938 Pin Configuration

### SPECIFICATIONS

### **ABSOLUTE MAXIMUM RATINGS\***

Voltages are referenced to V<sub>SS</sub>

| Parameter                                                                | Symbol          | Value                                 | Unit           |

|--------------------------------------------------------------------------|-----------------|---------------------------------------|----------------|

| Operating Temperature<br>Commercial<br>Industrial<br>Storage Temperature | Tc<br>Ti        | 0 to +70<br>-40 to +85<br>-55 to +125 | င့်<br>သိုင်္ခ |

| Operating Voltage                                                        | V <sub>DD</sub> | -22 to -18                            | Vdc            |

| Operating Display Voltage                                                | V <sub>GG</sub> | - 50                                  | Vdc            |

# **Dot Matrix Display Controller**

#### 10939 Pin Functions

| Signal Name     | Pin No. | Function                         |  |

|-----------------|---------|----------------------------------|--|

| V <sub>SS</sub> | 36      | Power and signal reference       |  |

| Vpp             | 37      | DC Power                         |  |

| CLOCK           | 38      | Synchronization Clock            |  |

| CURSOR          | 14      | Cursor drive output              |  |

| MASTER          | 39      | Master/Slave Mode control        |  |

| SIP             | 3       | Sync Input                       |  |

| SOP             | 2       | Sync Output                      |  |

| D0-D7           | 6-13    | Serial or parallel data input    |  |

| LD              | 5       | Input data strobe                |  |

| POR             | 4       | Power-on reset                   |  |

| SCLK-DIS        | 1       | Serial data shift clock          |  |

| DATA-LOAD       | 40      | Serial data output/latch control |  |

| STR00-STR19     | 15-34   | Grid Driver Outputs              |  |

| V <sub>GG</sub> | 35      | Display voltage                  |  |

| SCLK-DIS | 1 40  | DATA-LOAD       |

|----------|-------|-----------------|

| SOP C    | 2 39  | D MASTER        |

| SIP 🗂    | 3 38  | D CLOCK         |

| POR C    | 4 37  |                 |

| ւթվ      | 5 36  | D Vss           |

| D0 C     | 6 35  | V <sub>GG</sub> |

| D1 C     | 7 34  | D STROO         |

| D2 C     | 8 33  | STR01           |

| D3 🖸     | 9 32  | D STR02         |

| D4 🗆     | 10 31 | D STR03         |

| D5 🗅     | 11 30 |                 |

| D6 C     | 12 29 |                 |

| D7 🗖     | 13 28 |                 |

| CURSOR [ | 14 27 |                 |

| STR19    | 15 26 |                 |

| STR18    | 16 25 |                 |

| STR17 [  | 17 24 |                 |

| STR16    | 18 23 | B STR11         |

| STR15    | 19 22 | D STR12         |

| STR14    | 20 21 | D STR13         |

| L        |       |                 |

|          |       |                 |

#### **10939 Pin Configuration**

\*NOTE: Stresses above those listed under ABSOLUTE MAXI-MUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in other sections of this document is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Dot Matrix Display Controller**

### DC CHARACTERISTICS

#### All voltages referenced to V<sub>SS</sub>

| Parameter                                                                                                                               | Notes | Symbol                                 | Min                      | Тур | Max                                       | Unit   |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------|--------------------------|-----|-------------------------------------------|--------|

| Input D0-D7, LD, SIP<br>Logic ''1''<br>Logic ''0''                                                                                      | 2     | V <sub>IH</sub><br>V <sub>IL</sub>     | – 1.2<br>V <sub>DD</sub> |     | +0.3<br>-4.2                              | v<br>v |

| Input POR<br>Logic ''1''<br>Logic ''0''                                                                                                 | 2     | V <sub>IHPO</sub><br>V <sub>ILPO</sub> | 3.0<br>V <sub>DD</sub>   |     | + 0.3<br>- 10.0                           | v      |

| Output SOP<br>Logic ''1''<br>Logic ''0''                                                                                                | 2     | V <sub>OHSY</sub><br>V <sub>OLSY</sub> | - 1.2<br>V <sub>DD</sub> |     | V <sub>SS</sub><br>- 4.2                  | v<br>v |

| Output Grids, Cursor, and Anodes<br>Logic ''1'' (I <sub>load</sub> = 10 mA 10939, 2 mA 10938)<br>Logic ''0'' (I <sub>load</sub> = 0 mA) | 1     | V <sub>OH</sub><br>V <sub>OL</sub>     | - 1.5<br>V <sub>GG</sub> |     | V <sub>SS</sub><br>0.95 × V <sub>GG</sub> | v      |

### **OPERATING CURRENTS**

|                             | Maxi                                                                                                                               | mum                                                                | Typical                                       | Unit  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------|-------|

| Parameter                   | $ \begin{array}{r} \mbox{Industrial} \\ TA = -40^{\circ}\mbox{C} \\ V_{0D} = -22\mbox{Vdc} \\ V_{GG} = -50\mbox{Vdc} \end{array} $ | Commercial<br>TA = 0°C<br>$V_{DD} = -22$ Vdc<br>$V_{GG} = -50$ Vdc | $TA = 25^{\circ}C$ $V_{DD} = -20 \text{ Vdc}$ |       |

| 10938 <sup>1</sup>          |                                                                                                                                    |                                                                    |                                               |       |

| 1 <sub>DD</sub>             | 4.5                                                                                                                                | 3.6                                                                | 3.2                                           | mA    |

| IGG                         | 11.2                                                                                                                               | 9.0                                                                | 8.0                                           | mA    |

| 10939 (master) <sup>2</sup> |                                                                                                                                    |                                                                    |                                               |       |

| loo                         | 13.6                                                                                                                               | 10.9                                                               | 6.0                                           | mA mA |

| IGG                         | 1.0                                                                                                                                | 0.8                                                                | 0.5                                           | mA    |

| 10939 (slave) <sup>2</sup>  |                                                                                                                                    |                                                                    |                                               |       |

| loo                         | 9.1                                                                                                                                | 7.3                                                                | 4.0                                           | mA    |

| IGG                         | 1.0                                                                                                                                | 0.8                                                                | 0.5                                           | mA    |

Notes:

The 10938 has 35 internal drivers which are brought out. I<sub>GG</sub> is proportional to the number of drivers on. The values given are for all 35 drivers on. Divide I<sub>GG</sub> shown by 35 to determine I<sub>GG</sub> for one driver.

The 10939 will never have more than two drivers on at any one time; one grid driver and the cursor. The values shown are for two drivers on with 100% duty cycle.

# **Dot Matrix Display Controller**

7

# AC CHARACTERISTICS

| Parameter                 | Symbol             | Min  | Тур | Max  | Unit |

|---------------------------|--------------------|------|-----|------|------|

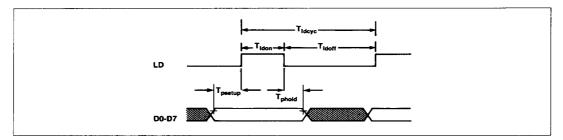

| GENERAL INTERFACE TIMING  |                    |      |     |      |      |

| Data Load (LD)            |                    |      |     |      |      |

| On Time                   | Tidon              | 1.0  |     |      | μs   |

| Off time                  | Tidoff             |      |     |      |      |

| Commercial                |                    | 40.0 |     |      | μS   |

| Industrial                |                    | 44.5 |     |      | μS   |

| Cycle Time                | Tidcyc             |      |     |      |      |

| Commerical                |                    | 60.0 |     |      | μS   |

| Industrial                |                    | 66.7 |     |      | μS   |

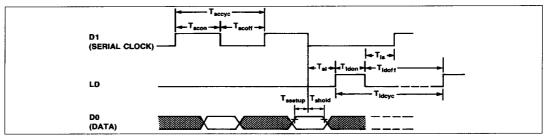

| SERIAL INTERFACE TIMING   |                    |      |     |      |      |

| Serial Clock (D1)         |                    |      | ,   |      |      |

| On Time                   | T <sub>scon</sub>  | 1.0  |     | 20.0 | μS   |

| Off Time                  | T <sub>scoff</sub> | 1.0  |     |      | μS   |

| Cycle Time                | T <sub>sccyc</sub> | 2.0  |     |      | μS   |

| Serial Clock (D0)         |                    |      |     |      |      |

| Set-up Time               | Tssetup            | 400  |     |      | ns   |

| Hold Time                 | Tshold             | 400  |     |      | ns   |

| Serial Clock to LD Time   | T <sub>sl</sub>    | 1.0  |     |      | μS   |

| LD to Serial Clock        | T <sub>Is</sub>    | 1.0  |     |      | μS   |

| PARALLEL INTERFACE TIMING |                    |      |     |      |      |

| Parallel Data (D0-D7)     |                    |      |     |      |      |

| Set-up Time               | Tpsetup            | 0    |     |      | ns   |

| Hold Time                 | Tphoid             | 200  |     |      | ns   |

# TIMING WAVEFORMS

#### Serial Interface Timing Waveforms

### Parallel Interface Timing Waveforms

## FUNCTIONAL DESCRIPTION

Once the display buffer has been loaded from the host processor, the 10938/10939 system generates all timing signals required to control the display.

Input data is loaded into the Display Data Buffer as a series of 8-bit words via the Serial or Parallel Data Input channel on the 10939. Internal timing and control logic synchronize the digit output signals with the Serial Data and Load signals to the 10938 to provide the proper timing for the multiplexing operation. A 128 x 35 bit PLA is provided for decoding the full 96 character ASCII set, plus 32 special characters.

The parallel data input mode is implemented by toggling any of data lines D2-D7 after PCR has gone low. Once the parallel data load mode has been implemented, a power-on reset procedure must be performed to return to serial data load mode. Parallel data transfer is accomplished by putting the command or display data on the data lines, then pulsing the LD line. The load cycle time must be at least 60  $\mu$ s with the LD line set high for at least one  $\mu$ s and held low for at least 40  $\mu$ s.

The serial data input mode is implemented during the poweron reset procedure. In those systems using serial mode, ports D2–D7 should be tied low to prevent the inadvertent implementation of the parallel load mode. Serial data bytes are shifted into a data buffer MSB first on line D0 using line D1 as the serial clock. The last eight bits clocked in are latched into the display controller by a pulse on the LD line. The cycle time for each data bit is 2  $\mu$ s and the load time for each byte is 60  $\mu$ s.

Input data may be Control or Display data. The following paragraphs describe the format and functions of these control and display data words.

### CONTROL DATA WORDS

Control data words are used to select the operating parameters of the display controller. They must be preceded by a Control Prefix word (0000 0001, hexadecimal 01) to be distinguished from Display Data words.

#### **Buffer Pointer Control**

The Buffer Pointer Control code sets the Display Data Buffer pointer. The lower 5 bits of the code are loaded into the buffer pointer (see Table 2).

| Table 1 | 1. | Control | Word | Assignments |

|---------|----|---------|------|-------------|

|---------|----|---------|------|-------------|

| Hex Value | Function                                           |

|-----------|----------------------------------------------------|

| 00        | Not used                                           |

| 01        | Load 01 into Data Buffer                           |

| 02        | Not used                                           |

| 03        | Not used                                           |

| 04        | Not used                                           |

| 05        | Set digit time to 16 cycles per grid               |

| 06        | Set digit time to 32 cycles per grid               |

| 07        | Set digit time to 64 cycles per grid               |

| 08        | Enable Normal Display Mode (MSB in data words      |

|           | is used for cursor control only)                   |

| 09        | Enable Blank Mode (data words with MSB = 1 will    |

|           | be blanked and cursor will be on)                  |

| 0A        | Enable Inverse Mode (data words with MSB = 1       |

|           | will be "inversed" and cursor will be on)          |

| 08        | Not used                                           |

| 0C        | Not used                                           |

| 0D        | Not used                                           |

| 0E        | Start Display Refresh Cycle (use only once after   |

|           | reset)                                             |

| 0F        | Not used                                           |

| 103F      | Not used                                           |

| 40–7F     | Load Duty Cycle Register with lower 6 bits (0-63)  |

| 80-9F     | Load Digit Counter (80 = 32, 81 = 1, 82 = 2, etc.) |

| A0-BF     | Not used                                           |

| C0-D3     | Load Buffer Pointer Register with lower 5 bits     |

| E0-FF     | Not used                                           |

Table 2. Buffer Pointer Control Codes

| Code<br>Value                 | Pointer<br>Value | Character<br>Position |

|-------------------------------|------------------|-----------------------|

| CO                            | 00               | 0                     |

| C1                            | 01               | 1                     |

| C2                            | 02               | 2                     |

| C3                            | 03               | 3                     |

| C4                            | 04               | 4                     |

| C5                            | 05               | 5                     |

| C6                            | 06               | 6                     |

| C7                            | 07               | 7                     |

| C8                            | 08               | 8                     |

| C9                            | 09               | 9                     |

| CA                            | 0A               | 10                    |

| СВ                            | 08               | 11                    |

| CC                            | OC               | 12                    |

| CD                            | 0D               | 13                    |

| CE                            | 0E               | 14                    |

| CF                            | OF               | 15                    |

| D0                            | 10               | 16                    |

| D1                            | 11               | 17                    |

| D2                            | 12               | 18                    |

| D3                            | 13               | 19                    |

| Note:<br>DO NOT U<br>(CODES D | SE CHARACTER POS | SITIONS 20-31         |

#### **Digit Counter Control**

The Digit Counter Control code defines the number of character positions (grids) to be controlled. This code is normally used only during initialization routines, but it may also be used in conjunction with the Duty Cycle Control code to extend the range of brightness control (see Table 3).

#### **Duty Cycle Control**

The Duty Cycle Control code turns the display on and off, adjusts display brightness, and modifies display timing. The time slot for each character is 16, 32, or 64 cycles as selected by the Digit Time Control codes (see Table 1). The anode and grid drivers for each character are on for a maximum of 13, 29, or 61 cycles with a 3 cycle inter-digit off-time. The lower 6 bits of the Duty Cycle Control code are loaded into the Duty Cycle Register. Resultant duty cycles are shown in Table 4.

| Code | Digit<br>Counter Value | No. of Grids<br>Controlled |

|------|------------------------|----------------------------|

| 80   | 00                     | 32                         |

| 81   | 01                     | 1                          |

| 82   | 02                     | 2                          |

| 83   | 03                     | 3                          |

| 84   | 04                     | 4                          |

| 85   | 05                     | 5                          |

| 86   | 06                     | 6                          |

| 87   | 07                     | 7                          |

| 88   | 08                     | 8                          |

| 89   | 09                     | 9                          |

| 8A   | 0A                     | 10                         |

| 8B   | 08                     | 11                         |

| 8C   | oC                     | 12                         |

| 8D   | 0D                     | 13                         |

| 8E   | 0E                     | 14                         |

| 8F   | OF                     | 15                         |

| 90   | 10                     | 16                         |

| 91   | 11                     | 17                         |

| 92   | 12                     | 18                         |

| 93   | 13                     | 19                         |

| 94   | 14                     | 20                         |

| 95   | 15                     | 21                         |

| 96   | 16                     | 22                         |

| 97   | 17                     | 23                         |

| 98   | 18                     | 24                         |

| 99   | 19                     | 25                         |

| 9A   | 1A                     | 26                         |

| 9B   | 1 <b>B</b>             | 27                         |

| 9C   | 1C                     | 28                         |

| 9D   | 1D                     | 29                         |

| 9E   | 1E                     | 30                         |

| 9F   | 1F                     | 31                         |

#### **Table 3. Digit Counter Control Codes**

### **Digit Time Select**

The Digit Time Select code sets the total time for each character during the refresh cycle. Three values can be set using the three codes shown in Table 1. The default value set at power-on is 64 cycles per grid. For displays with 40 or more characters, or under conditions where the display can be subjected to quick movements during viewing (e.g. portable or vehicle-mounted applications), it may be necessary to increase the refresh rate by selecting 16 or 32 cycles per grid with the appropriate control code.

## **Dot Matrix Display Controller**

#### Table 4. Duty Cycle Control Codes

| Digit Time = 16 Digit Time = 32 Digit Time = 64 |          |         |             |                  |          |           |  |  |  |  |  |  |  |

|-------------------------------------------------|----------|---------|-------------|------------------|----------|-----------|--|--|--|--|--|--|--|

|                                                 | Digit Ti | me = 16 | Digit Ti    | ime = 32         | Digit Ti | Time = 64 |  |  |  |  |  |  |  |

| Code                                            | On       | Off     | On          | Off              | On       | Off       |  |  |  |  |  |  |  |

| 40                                              |          | 16      | _           | 32               | -        | 64        |  |  |  |  |  |  |  |

| 41                                              | -        | 16      | -           | 32               | -        | 64        |  |  |  |  |  |  |  |

| 42                                              | - 1      | 16      |             | 32               | _        | 64        |  |  |  |  |  |  |  |

| 43                                              | 1        | 15      | 1           | 31               | 1        | 63        |  |  |  |  |  |  |  |

| 44                                              | 2        | 14      | 2<br>3<br>4 | 30               | 23       | 62        |  |  |  |  |  |  |  |

| 45                                              | 3        | 13      | 3           | 29               | 3        | 61        |  |  |  |  |  |  |  |

| 46                                              | 4        | 12      | 4           | 28               | 4        | 60        |  |  |  |  |  |  |  |

| 47                                              | 5        | 11      | 5           | 27               | 5        | 59        |  |  |  |  |  |  |  |

| 48                                              | 6        | 10      | 6           | 26               | 6        | 58        |  |  |  |  |  |  |  |

| 49                                              | 7        | 9       | 7           | 25               | 7        | 57        |  |  |  |  |  |  |  |

| 4A                                              | 8        | 8       | 8           | 24               | 8        | 56        |  |  |  |  |  |  |  |

| 4B                                              | 9        | 7       | 9           | 23               | 9        | 55        |  |  |  |  |  |  |  |

| 4C                                              | 10       | 6       | 10          | 22               | 10       | 54        |  |  |  |  |  |  |  |

| 4D                                              | 11       | 5       | 11          | 21               | 11       | 53        |  |  |  |  |  |  |  |

| 4E                                              | 12       | 4       | 12          | 20               | 12       | 52        |  |  |  |  |  |  |  |

| 4F                                              | 13       | 3       | 13          | 19               | 13       | 51        |  |  |  |  |  |  |  |

| 50                                              | 13       | 3       | 14          | 18               | 14       | 50        |  |  |  |  |  |  |  |

| 51                                              | 13       | 3       | 15          | 17               | 15       | 49        |  |  |  |  |  |  |  |

| 52                                              | 13       | 3       | 16          | 16               | 16       | 48        |  |  |  |  |  |  |  |

| 53                                              | 13       | 3       | 17          | 15               | 17       | 47        |  |  |  |  |  |  |  |

| •                                               | •        | •       | •           | · ·              | •        | •         |  |  |  |  |  |  |  |

| •                                               | •        | •       | •           | •                | •        | •         |  |  |  |  |  |  |  |

| •                                               | •        | •       | •           | •                | •        | •         |  |  |  |  |  |  |  |

| 5B                                              | 13       | 3       | 25          | 7                | 25       | 39        |  |  |  |  |  |  |  |

| 5C                                              | 13       | 3       | 26          | 6                | 26       | 38        |  |  |  |  |  |  |  |

| 5D                                              | 13       | 3       | 27          | 6<br>5<br>4<br>3 | 27       | 37        |  |  |  |  |  |  |  |

| 5E                                              | 13       | 3       | 28          | 4                | 28       | 36        |  |  |  |  |  |  |  |

| 5F                                              | 13       | 3       | 29          | 3                | 29       | 35        |  |  |  |  |  |  |  |

| 60                                              | 13       | 3       | 29          | 3                | 30       | 34        |  |  |  |  |  |  |  |

| 61                                              | 13       | 3       | 29          | 3<br>3<br>3      | 31       | 33        |  |  |  |  |  |  |  |

| 62                                              | 13       | 3       | 29          | 3                | 32       | 32        |  |  |  |  |  |  |  |

| •                                               | •        | •       | •           | •                | •        | •         |  |  |  |  |  |  |  |

| •                                               | •        | •       | •           | •                | •        | •         |  |  |  |  |  |  |  |

| •                                               | •        | •       | •           | •                | •        | •         |  |  |  |  |  |  |  |

| 7C                                              | 13       | 3       | 29          | 3                | 58       | 6         |  |  |  |  |  |  |  |

| 7D                                              | 13       | 3       | 29          | 3                | 59       | 5         |  |  |  |  |  |  |  |

| 7E                                              | 13       | 3       | 29          | 3                | 60       | 4         |  |  |  |  |  |  |  |

| 7F                                              | 13       | 3       | 29          | 3                | 61       | 3         |  |  |  |  |  |  |  |

#### **Display Mode Select**

Each ASCII character is represented by the lower seven bits of the 8-bit value loaded into the 10939. The eighth (most significant) bit controls the cursor (see Cursor Control). This bit is known as the data byte control bit. If either Blank or Inverse mode is selected, a "0" in this bit causes a normal character display, while "1" selects either Blank or Inverse mode, depending on which mode is enabled. Three control codes are provided (see Table 1) to enable Blank Mode, Inverse Mode, or Normal Display Mode.

In the Blank mode, any character with the MSB = "1" will be blanked. In the Inverse mode, it will be displayed with all segment driver outputs inverted. On video displays, this is referred to as "Inverse Video" format. These controls allow individual characters or groups of characters to be blinked or blanked by simply changing the mode without changing the data in the Display Buffer.

#### **Cursor Control**

The data byte control bit (MSB 8), besides selecting Blank, Inverse, or Normal mode, also controls the cursor output which is enabled on all characters with the MSB equal to one. Therefore, when the Normal mode is enabled and the MSB of the data byte is set to a one, the normal character is displayed with the cursor on. When the Blank mode is enabled and the MSB is set to a one, the character is blanked but the cursor is on. If Inverse mode is enabled and the MSB is set to a one, the inverse character is displayed and the cursor is on but not inversed.

#### Start Refresh

At power on, the 10939 is held in an internal halt mode. The normal display refresh sequence starts upon receipt of a Start Refresh control code. This is particularly useful for synchronizing systems using more than one 10939. Only the Master 10939 in a multi-chip system will recognize the Start Refresh code. The Master starts the Slave(s) at the appropriate time, using the SOP signal.

### INPUT DISPLAY DATA WORDS

Display data words are loaded as 8-bit codes. The eighth (most significant) bit specifies normal (0) or blank/inverse (1) display mode, depending on the blank/inverse mode selection (see Control data words 09 and 0A in Table 1). This bit also controls the cursor.

Twenty display data words must be entered to completely load the Display Data Buffer. The Buffer Pointer automatically increments after each data word is stored in the buffer. To select a character position to be loaded out of sequence, use the Buffer Pointer control code. The Buffer Pointer will automatically reset to character position 0 when its value is equal to the programmed Digit Count.

### **POWER-ON RESET**

The Power-On Reset (POR) initializes the internal circuits of the 10939. This is normally accomplished when power ( $V_{DD}$ ) is applied. The following conditions are established by application of POR:

a. The Grid Drivers (STR00-STR19) on the 10939 are in the off state.

# **Dot Matrix Display Controller**

- b. The Anode Drivers (SG01–SG35) on the 10938 are in the off state.

- c. The Duty Cycle is set to 0.

- d. The Digit Counter is set to 32.

- e. The Buffer Pointer is set to 0.

- f. The Digit time is set to 64.

- g. The Normal display mode is set.

- h. DATA-LOAD is set to high impedance state.

- SCLK-DIS is set to V<sub>OL</sub> to disable the anode drivers in the 10938.

- j. SOP is set to VOL to disable the sync pulse.

#### NOTE:

- 1. When the POR signal is removed, SCLK-DIS is set to the high impedance state.

- 2. During the initial rise time of V\_{DD} at power turn-on, the magnitude of V\_{GG} should not exceed the magnitude of V\_{DD}.

### GRID (DIGIT) DRIVERS (STR00-STR19) PLUS CURSOR

The 20 Digit Drivers select each of the display character positions sequentially during a refresh scan. Display dots will be illuminated when both the Digit Drivers and Dot Drivers for a particular character are energized simultaneously. The cursor segment is generated by the 10939, but its timing characteristics are identical to the anode timing generated by the 10938.

### ANODE (DOT) DRIVERS (SG01-SG35)

35 Dot Drivers are provided in the 10938. The output states for each character pattern are internally decoded from the 8-bit characters received from the 10939 by means of a 128 × 35-bit PLA. Data codes and the corresponding patterns are shown in Figure 1. Figure 2 shows the Dot Driver (SG01–SG35) assignments as they relate to the 5 × 7 dot matrix patterns.

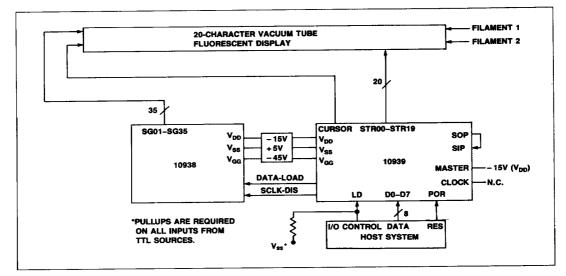

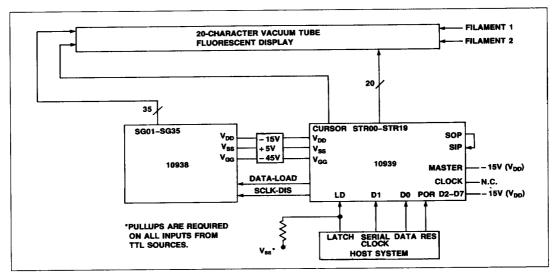

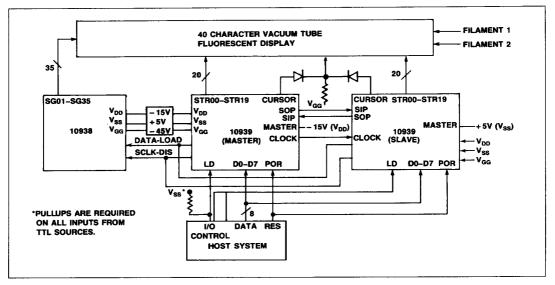

# TYPICAL SYSTEM HOOKUPS

Figure 3 shows a 10938 and 10939 in a parallel interface with the host system driving a 20 character display. Figure 4 shows a 10938 and a 10939 in a serial interface with the host system driving a 20 character display. Figure 5 shows a 10938 and two 10939's in a parallel interface with the host system driving a 40 character display.

| $00$ $01$ $\cdots$ $02$ $\cdots$ $03$ $\cdots$ $04$ $\cdots$ $05$ $\cdots$ $06$ $\cdots$ $07$ $\cdots$ $08$ $\cdots$ $08$ $\cdots$ $06$ $\cdots$ $0C$ $\cdots$ $0D$ $\cdots$ $0E$ $\cdots$ $07$ $\cdots$ $10$ $\cdots$ $11$ $\cdots$ $12$ $\cdots$ $13$ $\cdots$ $14$ $\cdots$ $15$ $\cdots$ $16$ $\cdots$ $17$ $\cdots$ $10$ $\cdots$ $19$ $\cdots$ $1A$ $\cdots$ $16$ $\cdots$ $25$ $\cdots$ $26$ $\cdots$ $17$ $\cdots$ $20$ $21$ $22$ $21$ $22$ $23$ $24$ $\cdots$ $25$ $26$ $\cdots$ $27$ $\cdots$ $27$ $\cdots$ $28$ $\cdots$ $28$ $\cdots$ $28$ $\cdots$ $28$ $\cdots$ $33$ $32$ $\cdots$ $33$ $33$ $34$ $10$ $36$ $\cdots$ $37$ $\cdots$ $17$ $\cdots$ $17$ $\cdots$ $17$ $\cdots$ |    |          |               |    |         |    |               |    |    |    |          |    |           |    |          |    |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------|---------------|----|---------|----|---------------|----|----|----|----------|----|-----------|----|----------|----|------|

| 10 $\vdots$ 11 $\vdots$ 12 $\vdots$ 13 $\vdots$ 14 $\vdots$ 15 $\vdots$ 16 $\vdots$ 17 $\vdots$ 18 $\vdots$ 19 $\vdots$ 1A $\vdots$ 18 $\vdots$ 10 $\vdots$ 11 $i$ 17 $i$ 20       21 $i$ 22 $i$ 23 $i$ $i$ 24 $i$ 25 $i$ 26 $i$ 27 $i$ 28 $i$ 29 $i$ 24 $i$ 35 $i$ 36 $i$ 37 $i$ 30 $i$ 31 $i$ 32 $i$ 33 $i$ 34 $i$                                                                                                                                                                                                                       | 00 | 0        |               | 01 |         | 02 |               | 03 |    | 04 | <b>.</b> | 05 |           | 06 |          | 07 |      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 08 |          |               | 09 |         | 04 |               | 08 | :  | ос | :        | oD | :::       | 0E | :::      | 0F | 4    |

| 20       21 $\vdots$ 22 $\vdots$ 23 $\vdots$ 24 $\vdots$ 25 $\vdots$ 26 $\vdots$ 27 $\vdots$ 28 $\vdots$ 29 $\vdots$ 2A $\vdots$ 2B $\vdots$ 2C $\vdots$ 2D $\ldots$ 2E $\vdots$ 2F $$ 37 $\vdots$ 30 $\vdots$ 31 $\vdots$ 32 $$ 33 $$ 34 $$ 35 $\ldots$ 36 $\vdots$ $$ 37 $\vdots$ 38 $$ 39 $\ldots$ 3A $\ldots$ 36 $$ 3D $\ldots$ 36 $\vdots$ $$ 37 $\vdots$ 40 $$ 41 $$ 42 $$ 43 $$ 44 $$ 45 $$ 46 $$ 47 $$ $$ 50 $$ 51 $$ 52 $$ 53 $$ 54 $$ 55 $$ 56 $$ 57 $$ 57 $$ 58 <t< td=""><td>10</td><td>•</td><td></td><td></td><td>÷</td><td>12</td><td>:</td><td>13</td><td>::</td><td>14</td><td>·</td><td>15</td><td></td><td>16</td><td></td><td>17</td><td></td></t<>                    | 10 | •        |               |    | ÷       | 12 | :             | 13 | :: | 14 | ·        | 15 |           | 16 |          | 17 |      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18 | 8<br>:   | ::::<br>::::: | 19 |         | 1A |               | 18 | ·: | 1C |          | 1D |           | 1E |          | 1F |      |

| 30 $\vdots$ 31 $\vdots$ 32 $\vdots$ 33 $\vdots$ 34 $\vdots$ 35 $\vdots$ 36 $\vdots$ 37 $\vdots$ 38 $\vdots$ 39 $\vdots$ 34 $\vdots$ 35 $\vdots$ 36 $\vdots$ 37 $\vdots$ 40 $\vdots$ 39 $\vdots$ 34 $\vdots$ 36 $\vdots$ 37 $\vdots$ 40 $\vdots$ 41 $\vdots$ 42 $\vdots$ 43 $\vdots$ 44 $\vdots$ 45 $\vdots$ 46 $i$ 47 $\vdots$ 48 $\vdots$ 49 $\vdots$ 44 $\vdots$ 40 $i$ 46 $i$ 47 $\vdots$ 50 $\vdots$ 52 $\vdots$ 53 $\vdots$ 54 $\vdots$ 55 $\vdots$ 56 $i$                                                                                                                        | 20 | 0        |               | 21 | 1       | 22 | ::            | 23 |    | 24 | :::::    | 25 |           | 26 |          | 27 | .:   |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28 | 8        |               | 29 |         | 2A | :::           | 28 |    | 2C | .:       | 2D |           | 2E |          | 2F | ···· |

| $40$ $\cdots$ $41$ $\cdots$ $42$ $\cdots$ $43$ $\cdots$ $44$ $\cdots$ $45$ $\cdots$ $46$ $\cdots$ $47$ $\cdots$ $48$ $\cdots$ $49$ $\cdots$ $4A$ $\cdots$ $4C$ $\cdots$ $40$ $\cdots$ $4F$ $\cdots$ $50$ $\cdots$ $51$ $\cdots$ $52$ $\cdots$ $53$ $\cdots$ $55$ $\cdots$ $56$ $\cdots$ $4F$ $\cdots$ $58$ $\cdots$ $59$ $\cdots$ $54$ $\cdots$ $55$ $\cdots$ $56$ $\cdots$ $57$ $\cdots$ $58$ $\cdots$ $59$ $\cdots$ $54$ $\cdots$ $55$ $\cdots$ $56$ $\cdots$ $57$ $\cdots$ $60$ $\cdots$ $61$ $\cdots$ $62$ $\cdots$ $63$ $\cdots$ $64$ $\cdots$ $66$ $\cdots$ $67$ $\cdots$ $60$ $\cdots$ $0$ $\cdots$ $0$ $\cdots$ $0$ $\cdots$ $0$ $\cdots$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ <        | 30 | •        |               | 31 | 1       | 32 | •***•<br>•••• | 33 |    | 34 |          | 35 | :         | 36 | <u>.</u> | 37 | :    |

| 48        49        48        4C        4D        4E        4F          50        51        52        53        54        55        56        57          58        59        5A        5B        5C        50        5F          60        61        62        63        66        67                                                                                                                                                                                                                                                                                                                                                                                                     | 38 | в :<br>: |               | 39 |         | 3А |               | 38 |    | зс |          | 3D |           | зе |          | ЗF |      |

| 50 $\cdots$ 51 $\cdots$ 52 $\cdots$ 53 $\cdots$ 54 $\cdots$ 55 $\cdots$ 56 $\cdots$ 57 $\cdots$ 58 $\cdots$ 59 $\cdots$ 5A $\cdots$ 5B $\cdots$ 50 $\cdots$ 5F $\cdots$ 66 $\cdots$ 67 $\cdots$ 57 $\cdots$ <                  | 40 | •        |               | 41 |         | 42 |               | 43 |    | 44 |          | 45 |           | 46 |          | 47 | ···· |

| 58       :       59       :       5A       :       5B       :       5C       :       5D        5F          60        61        62        63       :       65       :       66        67       :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48 | 8        |               | 49 |         |    |               | 48 |    | 4C |          |    |           | 4E | ŀ··      | 4F |      |

| 58        59        5A        5B        5C        5D        5E        5F          60        61        62        63        64        65        66        67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50 |          |               | 51 |         | 52 | R             | 53 | :  | 54 |          | 55 | l!        | 56 | l.,!     | 57 |      |

| 60 · · 61 62 63 64 65 66 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58 | ,<br>,   |               | 59 | ·       | 5  | ·····         | 5B |    | 5C | ·•.      |    |           |    |          | 5F | ··   |

| 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60 |          | ·.            | 61 |         | 62 | <u> </u> :    | 63 | :  | 64 | ::::     | 65 |           | 66 |          | 67 |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68 | ,        |               | 69 |         | 64 |               | 68 | Ŀ: | 6C | 1        | 6D | ΪΠ        | 6E |          | 6F | :::: |

| 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70 |          |               | 71 |         | 72 | ·             |    |    | 74 | ÷:       |    |           |    | ۰        | Π  | ii   |

| 78 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 78 |          | :::]          | 79 | ::<br>: | 7A |               | 7B |    | 7C | ·        | 70 | :-::<br>: | 7E |          | 7F |      |

Figure 1. 5 × 7 Dot Matrix PLA Patterns

Figure 2. Anode (Dot) Driver Assignments

Figure 3. Typical Display System with Parallel Interface to Host System

Figure 4. Typical Display System with Serial Interface to Host System

Figure 5. Typical Display System with Parallel Interface to Host and Two 10939 Devices