# Smart Dual Port RAM (S-DPRAM)

### Description

Driven by the declining costs of VLSI CPUs, new multiprocessing and parallel-processing architectures are being explored to break the performance barrier of single CPU designs. A critical factor for multiprocessor performance is the choice of the communication mechanism between CPUs. A poorly designed communication scheme can destroy the potential for a multiprocessor design since message passing overhead can quickly offset the performance advantage of multiple CPUs.

An HD63310R S-DPRAM acts as a communication link between two CPUs. Thus, it replaces older, less flexible communication schemes such as parallel ports and FIFO ICs.

Programmable operating mode and bus interface tailor the S-DPRAM for a wide variety of multiprocessor system designs using industry standard MPUs.

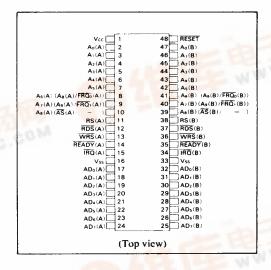

#### Pin Arrangement

#### **Features**

- 1024-byte data buffer with dual ports -Configurable as a RAM (DPRAM mode) or two FIFOs (FIFO mode)

- Asynchronous bus operation on each port

- Programmable bus interface

- Each bus configurable as a multiplexed or non-multiplexed address and data bus.

- Built-in programmable registers

- -8 semaphore registers for multiprocessing applications, 32 user-definable registers

- Programmable outputs

- --Interrupt outputs

- —FIFO status (full/empty, etc) outputs

- High speed operation and low power dissipation 2-µm CMOS circuit

- Single + 5V power supply

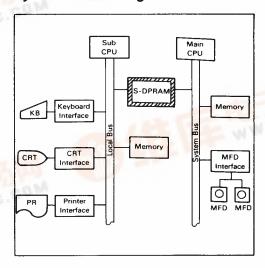

### System Block Diagram

# HD63310R

## Pin Description

| Symbol                                                                       | Pin Number     | Name                                                              | I/O |  |  |

|------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------|-----|--|--|

| V <sub>CC</sub>                                                              | 1              | Power supply                                                      |     |  |  |

| V <sub>SS</sub>                                                              | 16, 33         | Ground                                                            |     |  |  |

| RESET                                                                        | 48             | Reset                                                             | I   |  |  |

| A <sub>0</sub> -A <sub>5</sub> (A)<br>A <sub>0</sub> -A <sub>5</sub> (B)     | 2-7<br>47-42   | Address bus                                                       | ı   |  |  |

| AD <sub>0</sub> -AD <sub>7</sub> (A)<br>AD <sub>0</sub> -AD <sub>7</sub> (B) | 17-24<br>32-25 | Address/data bus                                                  | 1/0 |  |  |

| $ A_6/A_8/\overline{FRQ_0}(A)  A_6/A_8/\overline{FRQ_0}(B) $                 | 8<br>41        | Multipurpose line (1):<br>Address bit 6/8,<br>FIFO data request 0 | 1/0 |  |  |

| $A_7/A_9/\overline{FRQ_1}(A)$<br>$A_7/A_9/\overline{FRQ_1}(B)$               | 9<br>40        | Multipurpose line (2):<br>Address bit 7/9,<br>FIFO data request 1 | 1/0 |  |  |

| A <sub>8</sub> / <del>AS</del> (A)<br>A <sub>8</sub> / <del>AS</del> (B)     | 10<br>39       | Multipurpose line (3): I Address bit 8, Address strobe            |     |  |  |

| RS (A/B)                                                                     | 11, 38         | Register select                                                   | ı   |  |  |

| RDS (A/B)                                                                    | 12, 37         | Read strobe                                                       |     |  |  |

| WRS (A/B)                                                                    | 13, 36         | Write strobe                                                      |     |  |  |

| READY (A/B)                                                                  | 14, 35         | Ready                                                             |     |  |  |

| ĪRQ(A/B)                                                                     | 15, 34         | Interrupt request O                                               |     |  |  |

|                                                                              |                |                                                                   |     |  |  |

#### HITACHI

ma Pa

#### **Absolute Maximum Ratings**

| Item                           | Symbol                   | Value                        | Unit |

|--------------------------------|--------------------------|------------------------------|------|

| Supply Voltage                 | V <sub>CC</sub> (Note 2) | -0.3 to +7.0                 | ٧    |

| Input Voltage                  | Vin (Note 2)             | -0.3 to V <sub>CC</sub> +0.3 | ٧    |

| Allowable Output Current       | lo (Note 3)              | 5                            | mA   |

| Total Allowable Output Current | Σ lo  (Note 4)           | 60                           | mA   |

| Operating Temperature          | Topr                     | 0 to +70                     | °C   |

| Storage Temperature            | Tstg                     | -55 to +150                  | °C   |

- Notes: 1. Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under recommended operating conditions. If these conditions are exceeded, it could affect the reliability of the LSI.

- 2. With respect to VSS (system GND)

- The allowable output current is the maximum current that may be drawn from, or flow out to, one output terminal or one input/ output common terminal.

- 4. The total allowable output current is the total sum of currents that may be drawn from, or flow out to, output terminals or input/output common terminals.

#### **Recommended Operating Conditions**

| Item                  | Symbol                 | Min  | Тур          | Max  | Unit |

|-----------------------|------------------------|------|--------------|------|------|

| Supply Voltage        | V <sub>CC</sub> (Note) | 4.75 | 5.0          | 5.25 | V    |

| Input Voltage         | V <sub>IH</sub> (Note) | 2.2  | <del>-</del> | Vcc  | ٧    |

|                       | V <sub>IL</sub> (Note) | 0    | _            | 0.8  | V    |

| Operating Temperature | Topr                   | 0    | 25           | 70   | *C   |

Note: With respect to VSS (system GND)

ma Plane

#### HITACHI

## HD63310R

#### **Electrical Charcteristics**

# DC Characteristics (Vcc = 5 V $\pm$ 5%, Vss = 0 V, Ta = 0°C to +70°C, unless otherwise noted)

| Item                                          |                                                                                                                                                                                                                                                                   | Sym.            | Min                   | Max             | Unit   | Test<br>Condition                                                                          |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-----------------|--------|--------------------------------------------------------------------------------------------|

| Input High Voltage Input Low Voltage          |                                                                                                                                                                                                                                                                   | V <sub>IH</sub> | 2.2<br>Vss<br>-0.3    | V <sub>CC</sub> | v<br>v |                                                                                            |

|                                               |                                                                                                                                                                                                                                                                   |                 |                       |                 |        |                                                                                            |

| Three-State<br>(Off State)<br>Leakage Current | $\begin{split} & AD_{0}(A) - AD_{7}(A), AD_{0}(B) - AD_{7}(B), \\ & A_{6}(A)/A_{8}(A)\overline{FRQ_{0}}(A), \\ & A_{6}(B)/A_{8}(B)/\overline{FRQ_{0}}(B), \\ & A_{7}(A)/A_{9}(A)/\overline{FRQ_{1}}(A), \\ & A_{7}(B)/A_{9}(B)/\overline{FRQ_{1}}(B) \end{split}$ | ITSI            | -10                   | 10              | μА     | Vin = 0 to V <sub>CC</sub>                                                                 |

| Output Leakage<br>Current                     | ĪRQ(A), ĪRQ(B)                                                                                                                                                                                                                                                    | Ісон            | -10                   | 10              | μΑ     | V <sub>OH</sub> = V <sub>CC</sub>                                                          |

| Output High<br>Voltage                        |                                                                                                                                                                                                                                                                   | VoH             | V <sub>CC</sub> - 1.0 | _               | ٧      | I <sub>OH</sub> = -400 μA                                                                  |

| voitage                                       |                                                                                                                                                                                                                                                                   |                 | V <sub>CC</sub> - 0.1 | _               | ٧      | I <sub>OH</sub> ≦ −10 μA                                                                   |

| Output Low<br>Voltage                         | $\begin{array}{l} AD_{0}(A)-AD_{7}(A),AD_{0}(B)-AD_{7}(B),\\ A_{8}(A)/A_{8}(A)/FRQ_{0}(A),\\ A_{6}(B)/A_{8}(B)/FRQ_{0}(B),\\ A_{7}(A)/A_{9}(A)/FRQ_{1}(A),\\ A_{7}(B)/A_{9}(B)/FRQ_{1}(B),\\ READY(A),\ READY(B) \end{array}$                                     | VoL             | -                     | 0.5             | V      | I <sub>OL</sub> = 2 mA                                                                     |

|                                               | ĪRQ(A), ĪRQ(B)                                                                                                                                                                                                                                                    |                 | -                     | 0.5             | V      | I <sub>OL</sub> = 3.2 mA                                                                   |

| Input Capacitance                             |                                                                                                                                                                                                                                                                   | Cin             | _                     | 20              | рF     | Vin = 0 V<br>Ta = 25°C                                                                     |

| Output Capacitance                            |                                                                                                                                                                                                                                                                   | Cout            | _                     | 20              | _      | f = 1.0 MHz                                                                                |

| Current<br>Dissipation                        | Operating Mode                                                                                                                                                                                                                                                    | Icc             | _                     | 30              | mA     | V <sub>CC</sub> = 5.25 V<br>V <sub>IH</sub> = 2.2 V<br>V <sub>IL</sub> = 0.8 V             |

|                                               | Standby Mode<br>(RDS, WRS = High)                                                                                                                                                                                                                                 |                 | _                     | 1               | mA     | $V_{CC} = 5.25 \text{ V}$<br>$V_{IH} = V_{CC} - 0.2 \text{ V}$<br>$V_{IL} = 0.2 \text{ V}$ |

# **Packaging Information**

ma Pen

| Part No. | Package |  |  |

|----------|---------|--|--|

| HD63310R | DP-48   |  |  |

#### **HITACHI**