## **MC68HC58** DATA LINK CONTROLLER

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MCUinit, MCUasm, MCUdebug, and RTEK are trademarks of Motorola, Inc. Motorola and the Motorola logo are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. 1-800-441-2447 or 602/303-5454 MFAX: RMFAX0@email.sps.mot.com - TOUCHTONE (602) 244-6609

INTERNET: http://Design-NET.com

JAPAN: Nippon Motorola Ltd.; Tatsumi-SPD-JLDC,

6F Seibu-Butsuryu-Center, 3-14-2 Tatsumi Koto-Ku, Tokyo 135, Japan. 81-3-3521-8315

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park,

51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298

## **TABLE OF CONTENTS**

Paragraph Title Page

### **SECTION 1INTRODUCTION**

## **SECTION 2SIGNAL AND PIN DESCRIPTIONS**

| MC68HC58 DLC Parallel Mode                     | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DLC Parallel Mode Pin Function                 | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ADDR0 — Address Bit                            | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BUS — SAE J1850 Multiplex Bus                  | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CS — DLC Chip-Select                           | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DATA[7:0] — DLC Data Bus                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ECLK — 6800 Bus Clock                          | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INT — DLC Interrupt Request                    | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LITO — Logic In Transceiver Out                | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LOAD — External Bus Load                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LOTI — Logic Out Transceiver In                | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OSC1, OSC2 — External Oscillator               | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PRLMD — Parallel Mode                          | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PSEN — Power Supply Enable                     | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| REXT — External Bias Resistor                  | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| R/W — Read/Write Strobe                        | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>BATT</sub> — Battery Voltage            | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDD — Digital Power Supply Voltage             | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VSSA — Analog Power Ground                     | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>3</b> ··· · · · · · · · · · · · · · · · · · |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MC68HC58 DLC Serial Mode                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DLC Serial Mode Pin Function                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BUS — SAE J1850 Multiplex Bus                  | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CS — DLC Chip-Select                           | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INT — DLC Interrupt Request                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LITO — Logic In Transceiver Out                | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LOAD — External Bus Load                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SIMO — Slave In Master Out                     | 2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                | DLC Parallel Mode Pin Function  ADDR0 — Address Bit  BUS — SAE J1850 Multiplex Bus  CS — DLC Chip-Select  DATA[7:0] — DLC Data Bus  ECLK — 6800 Bus Clock  INT — DLC Interrupt Request  LITO — Logic In Transceiver Out  LOAD — External Bus Load  LOTI — Logic Out Transceiver In  OSC1, OSC2 — External Oscillator  PRLMD — Parallel Mode  PSEN — Power Supply Enable  RST — DLC Reset  REXT — External Bias Resistor  R/W — Read/Write Strobe  V <sub>BATT</sub> — Battery Voltage  V <sub>CC</sub> — Analog Power Supply Voltage  VSSA — Analog Power Ground  VSSD — Digital Power Ground  Example DLC Parallel Mode System  MC68HC58 DLC Serial Mode  DLC Serial Mode Pin Function  BUS — SAE J1850 Multiplex Bus  CS — DLC Chip-Select  INT — DLC Interrupt Request  LITO — Logic In Transceiver Out  LOAD — External Bus Load  LOTI — Logic Out Transceiver In  OSC1, OSC2 — External Oscillator  PRLMD —Parallel Mode  PSEN — Power Supply Enable  RST — DLC Reset |

ma Plant

MC68HC58

| Paragra                        | nph Title                                       | Page |  |

|--------------------------------|-------------------------------------------------|------|--|

|                                |                                                 |      |  |

| 2.2.1.14                       | SOMI — Slave Out Master In                      | 2-9  |  |

| 2.2.1.15                       | VBATT — Battery Voltage                         | 2-9  |  |

| 2.2.1.16                       | VCC — Analog Power Supply Voltage               | 2-9  |  |

| 2.2.1.17                       | VDD — Digital Power Supply Voltage              | 2-9  |  |

| 2.2.1.18                       | VSSA — Analog Power Ground                      | 2-9  |  |

| 2.2.1.19                       | VSSD — Digital Power Ground                     | 2-9  |  |

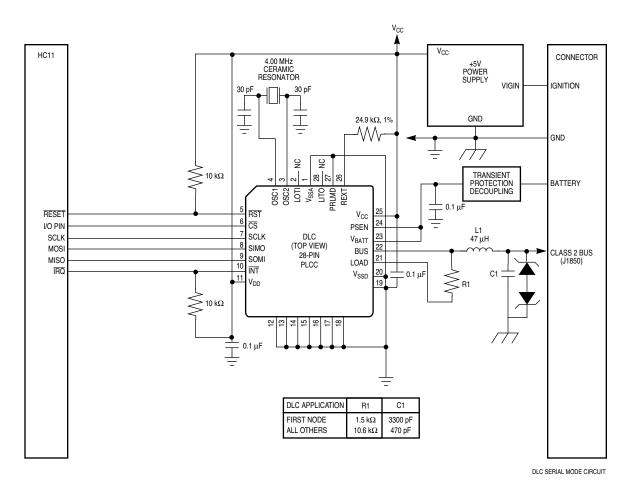

| 2.2.2                          | Example DLC Serial Mode System                  | 2-10 |  |

| 2.3                            | Bus Loading                                     |      |  |

| 2.4                            | DLC Clock Sources                               | 2-12 |  |

| 2.4.1                          | Logic Clock                                     | 2-12 |  |

| 2.4.2                          | Host Interface Clock                            |      |  |

| 2.5                            | Power Supply Connections                        |      |  |

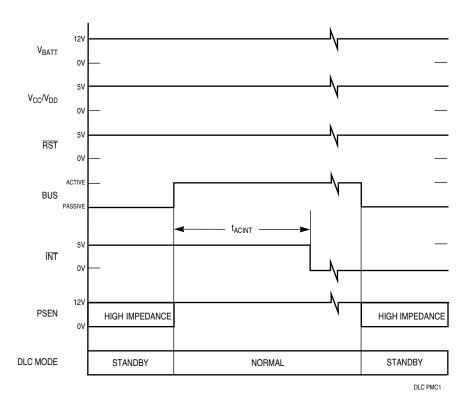

| 2.5.1                          | Method 1 — All Supplies Applied                 | 2-14 |  |

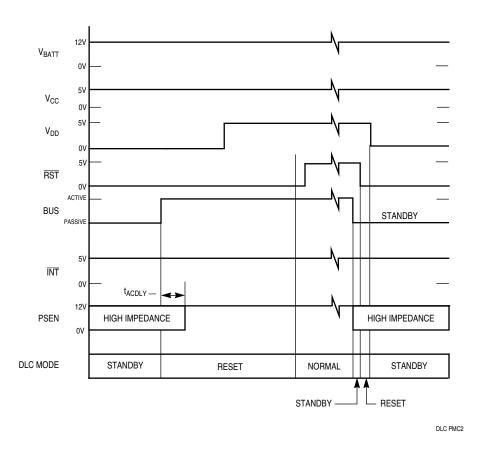

| 2.5.2                          | Method 2 — Switching VDD With PSEN              |      |  |

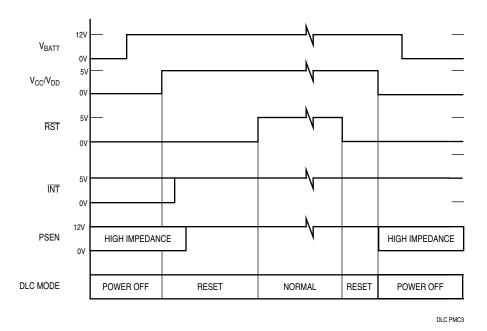

| 2.5.3                          | Method 3 — Switching VDD and VCC Simultaneously | 2-16 |  |

| 2.6                            | Reset                                           | 2-17 |  |

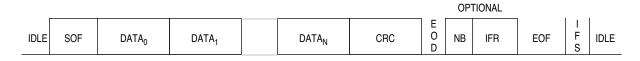

|                                | SECTION 3 J1850 FRAME FORMAT                    |      |  |

|                                |                                                 |      |  |

| 3.1                            | J1850 Frame Format                              |      |  |

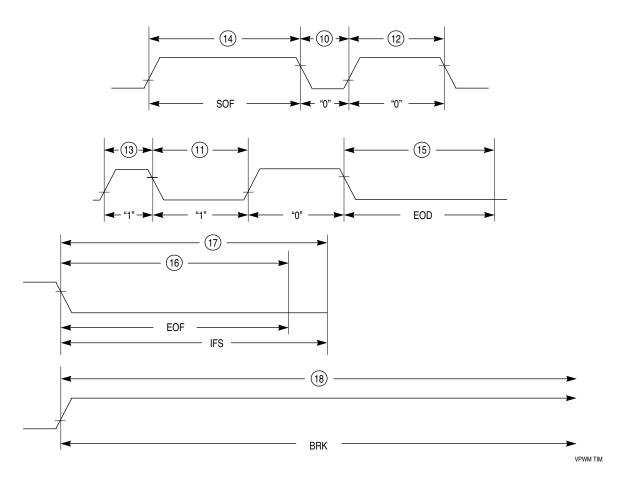

| 3.1.1                          | SOF — Start of Frame Symbol                     |      |  |

| 3.1.2                          | Data — In Frame Data Bytes                      |      |  |

| 3.1.2.1                        | Logic Zero                                      |      |  |

| 3.1.2.2                        | Logic One                                       |      |  |

| 3.1.3                          | CRC — Cyclical Redundancy Check Byte            |      |  |

| 3.1.4 EOD — End of Data Symbol |                                                 |      |  |

|                                | 3.1.5 NB — Normalization Bit                    |      |  |

| 3.1.6                          | IFR — In-Frame Response Bytes                   |      |  |

| 3.1.7                          | EOF — End of Frame Symbol                       |      |  |

| 3.1.8                          | IFS — Inter-Frame Separation Symbol             |      |  |

| 3.1.9                          | BREAK — Break                                   |      |  |

| 3.1.10                         | Idle Bus                                        |      |  |

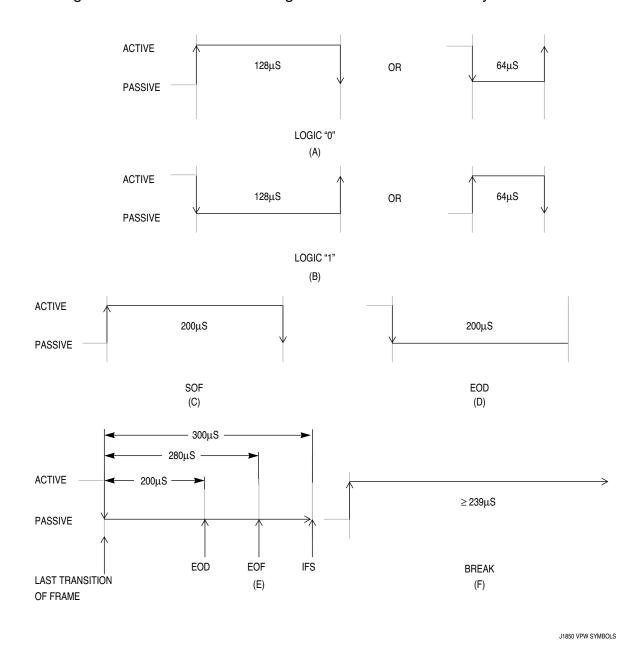

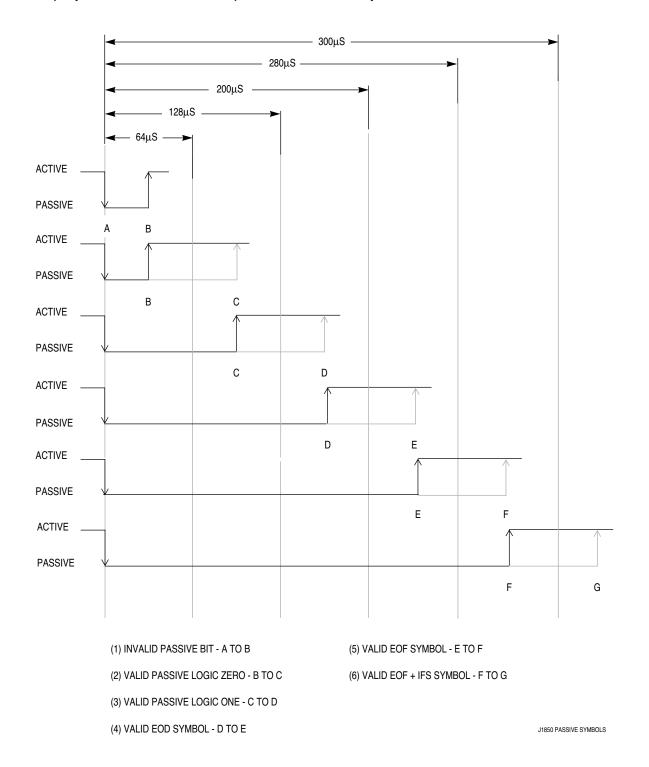

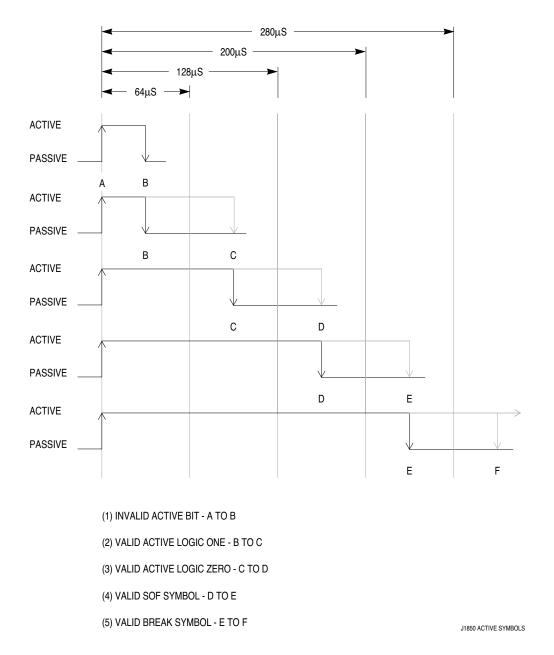

| 3.2                            | J1850 VPW Valid/Invalid Bits and Symbols        |      |  |

| 3.2.1                          | Invalid Passive Bit                             |      |  |

| 3.2.2                          | Valid Passive Logic Zero                        |      |  |

| 3.2.3                          | Valid Passive Logic One                         |      |  |

| 3.2.4                          | Valid EOD Symbol                                |      |  |

| 3.2.5                          | Valid EOF and IFS Symbol                        |      |  |

| 3.2.6                          |                                                 |      |  |

| 3.2.7                          |                                                 |      |  |

| 3.2.8                          |                                                 |      |  |

| 3.2.9                          | 3.2.9 Valid Active Logic Zero                   |      |  |

MOTOROLA

| Paragra | aph Title                                     | Page |  |

|---------|-----------------------------------------------|------|--|

| 3.2.10  | Valid SOF Symbol                              | 3-9  |  |

| 3.2.11  | Valid BREAK Symbol                            |      |  |

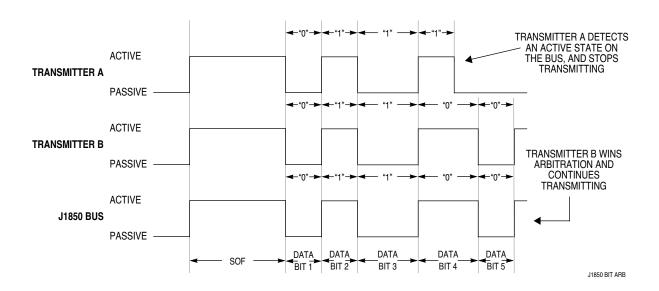

| 3.3     | Frame Arbitration                             |      |  |

|         | SECTION 4 DATA LINK CONTROLLER OPERATION      |      |  |

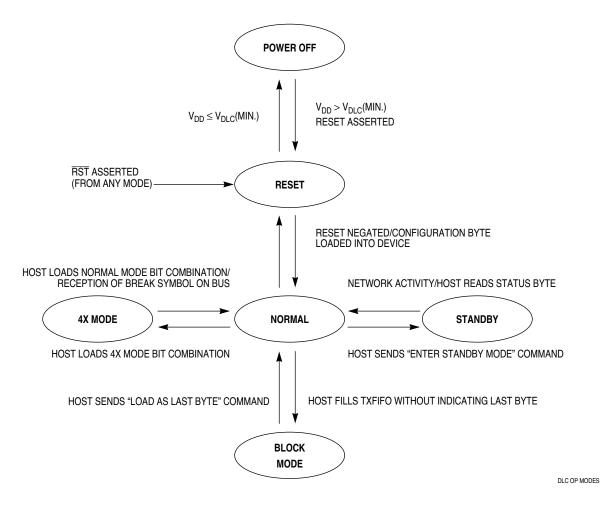

| 4.1     | Operating Modes                               | 4-1  |  |

| 4.1.1   | Power-Off Mode                                | 4-2  |  |

| 4.1.2   | Reset Mode                                    | 4-2  |  |

| 4.1.3   | Normal Mode                                   | 4-2  |  |

| 4.1.4   | Standby Mode                                  | 4-2  |  |

| 4.1.5   | 4X Mode                                       | 4-2  |  |

| 4.1.6   | Block Mode                                    | 4-3  |  |

| 4.2     | Host Interface                                |      |  |

| 4.2.1   | MC68HC58 DLC Parallel Mode Host MCU Interface | 4-5  |  |

| 4.2.1.1 | Parallel Mode Data Transfer                   | 4-5  |  |

| 4.2.1.2 | Servicing Sequence                            | 4-6  |  |

| 4.2.1.3 | Minimum Time Requirements                     | 4-7  |  |

| 4.2.1.4 | Motorola Microcontroller Data Transfers       | 4-7  |  |

| 4.2.2   | MC68HC58 DLC Serial Mode Host MCU Interface   | 4-8  |  |

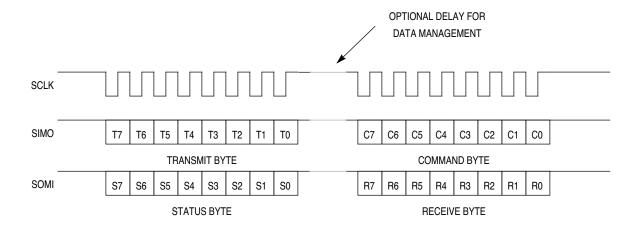

| 4.2.2.1 | Serial Mode Data Transfer                     | 4-8  |  |

| 4.2.2.2 | Servicing Sequence                            | 4-9  |  |

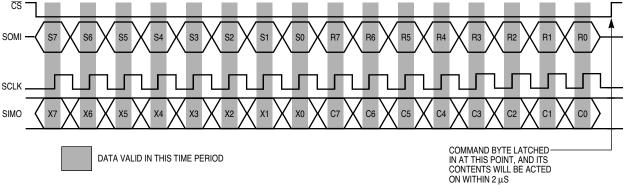

| 4.2.2.3 | SPI Exchange                                  | 4-9  |  |

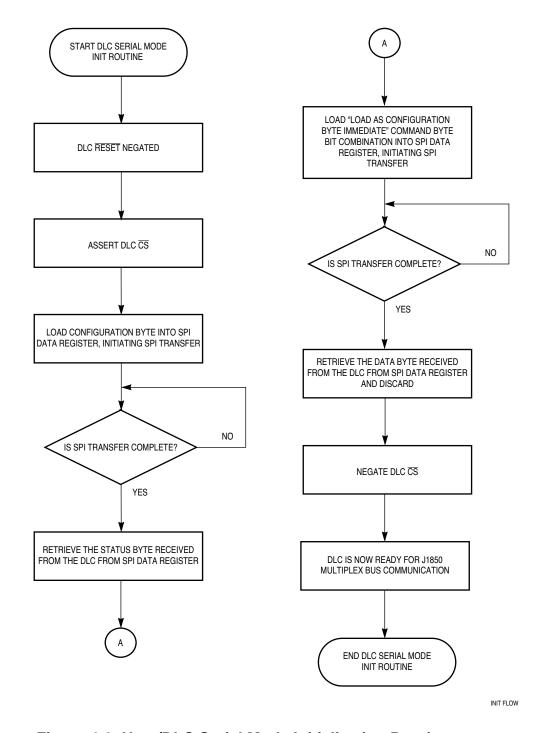

| 4.2.2.4 | Initialization                                | 4-10 |  |

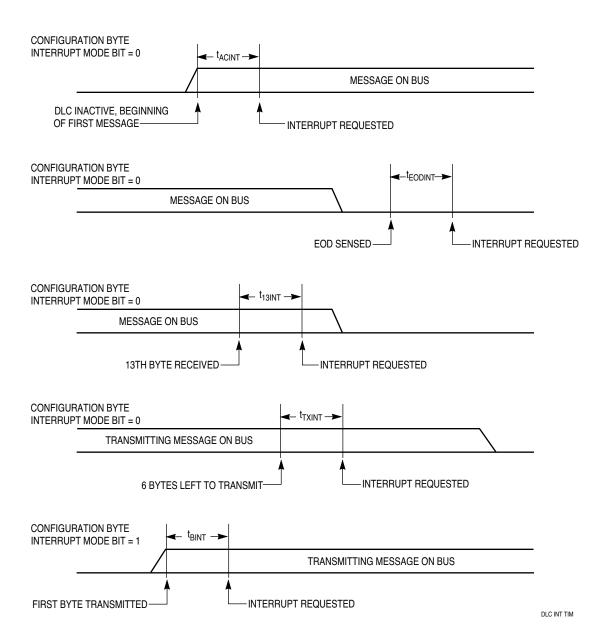

| 4.2.3   | Interrupt Requests                            | 4-11 |  |

| 4.3     | Transmitter Operation                         | 4-12 |  |

| 4.4     | Receiver Operation                            | 4-16 |  |

| 4.5     | Block Mode Operation                          | 4-20 |  |

| 4.6     | BREAK Operation                               | 4-21 |  |

| 4.7     | In-Frame Response (IFR)                       | 4-21 |  |

|         | SECTION 5 CONTROL AND STATUS CODES            |      |  |

| 5.1     | Command Byte                                  | 5-1  |  |

| 5.1.1   | GCOM[7:5] — General Command Field             | 5-1  |  |

| 5.1.1.1 | Do Nothing                                    |      |  |

| 5.1.1.2 | Enter Standby Mode                            |      |  |

| 5.1.1.3 | Send BREAK Symbol                             |      |  |

| 5.1.1.4 | Send IFR on EOD with CRC                      | 5-2  |  |

| 5.1.1.5 | Terminate Auto Retry                          |      |  |

| 5.1.1.6 | Send IFR on EOD without CRC                   | 5-3  |  |

| 5.1.1.7 | Abort Transmission                            |      |  |

| Paragra | aph Title                                               | Page |

|---------|---------------------------------------------------------|------|

|         |                                                         |      |

| 5.1.2   | BTAD[4:2] — Byte Type and Destination Field             |      |

| 5.1.2.1 | Do Not Load                                             |      |

| 5.1.2.2 | Load as Transmit Data                                   |      |

| 5.1.2.3 | Load as Last Byte of Transmit Data                      |      |

| 5.1.2.4 | Load as Configuration Byte                              |      |

| 5.1.2.5 | Load as First Byte of Transmit Data                     | 5-5  |

| 5.1.2.6 | Load as Configuration Byte – Immediate                  |      |

| 5.1.2.7 | Load as First and Last Byte of Frame                    |      |

| 5.1.3   | RFC[1:0] — Receive FIFO Command Field                   | 5-6  |

| 5.1.3.1 | Do Nothing                                              | 5-6  |

| 5.1.3.2 | Flush Byte                                              | 5-6  |

| 5.1.3.3 | Flush Frame                                             | 5-6  |

| 5.2     | Configuration Byte                                      | 5-7  |

| 5.2.1   | TM — Test Mode Control Bit                              | 5-7  |

| 5.2.2   | TC[6:5] — Test Configuration Field                      | 5-7  |

| 5.2.3   | IMSK — Interrupt Mask Bit                               | 5-7  |

| 5.2.4   | IMOD — Interrupt Mode Bit                               | 5-8  |

| 5.2.5   | OSCD[2:1] — Oscillator Divisor Field                    |      |

| 5.2.6   | 4X — High-Speed Control Bit                             |      |

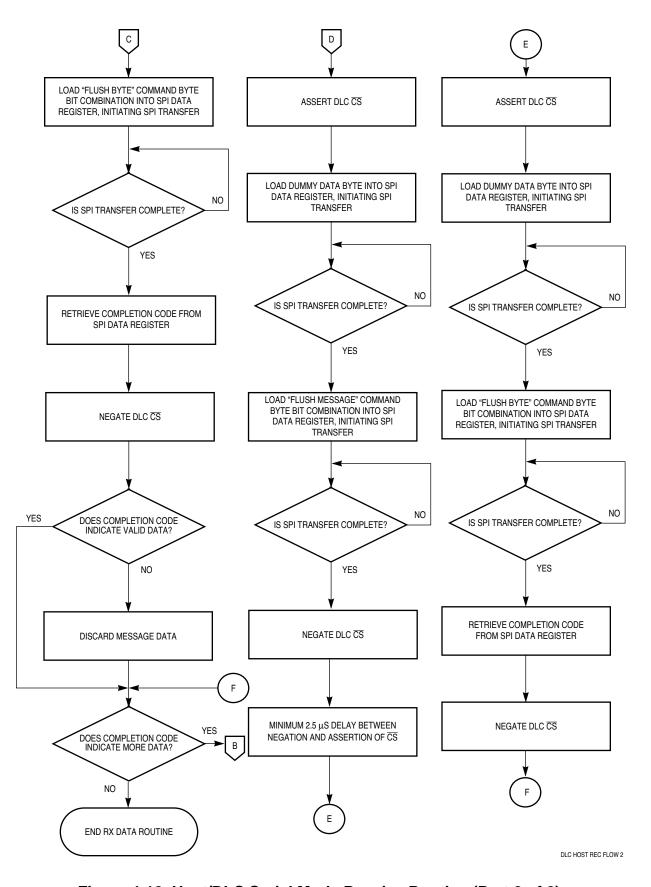

| 5.3     | Status Byte                                             |      |

| 5.3.1   | RFS[7:5] — Receive FIFO Status Field                    |      |

| 5.3.1.1 | Buffer Invalid or Empty                                 |      |

| 5.3.1.2 | Buffer Contains More Than One Byte                      |      |

| 5.3.1.3 | Buffer Contains a Completion Code                       |      |

| 5.3.1.4 | Thirteenth Byte Received                                |      |

| 5.3.1.5 | One Byte in Buffer                                      |      |

| 5.3.1.6 | Completion Code at Head of Buffer, More Bytes Available | 5-10 |

| 5.3.1.7 | Completion Code at Head of Buffer, Frame Available      |      |

| 5.3.1.8 | Completion Code Only at Head of Buffer                  |      |

| 5.3.2   | DLI — Data Link Idle Bit                                |      |

| 5.3.3   | NETF — Network Fault Bit                                | 5-10 |

| 5.3.4   | 4XMD — 4X Mode Bit                                      |      |

| 5.3.5   | TMFS[1:0] — TxFIFO Status Field                         |      |

| 5.3.5.1 | Buffer Empty                                            |      |

| 5.3.5.2 | Buffer Contains Data                                    | 5-11 |

| 5.3.5.3 | Buffer Almost Full                                      |      |

| 5.3.5.4 | Buffer Full                                             |      |

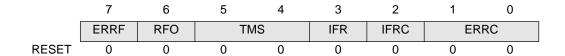

| 5.4     | Completion Code Byte                                    |      |

| 5.4.1   | ERRF — Error Bit                                        |      |

| 5.4.2   | RFO — Receive FIFO Overrun Bit                          |      |

| 5.4.3   | TMS[5:4] — Transmitter Status Field                     |      |

| Paragra                                                             | aph Title                                                                                                                                              | Page                         |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 5.4.3.1<br>5.4.3.2<br>5.4.3.3<br>5.4.3.4                            | Transmitter Not Involved                                                                                                                               | 5-12<br>5-13<br>5-13         |

| 5.4.4<br>5.4.5<br>5.4.6<br>5.4.6.1<br>5.4.6.2<br>5.4.6.3<br>5.4.6.4 | IFR — In-Frame Response Bit IFRC — In-Frame Response CRC Bit ERRC[1:0] — Error Code Field CRC Error Incomplete Byte Error Bit Timing Error BREAK Error | 5-13<br>5-13<br>5-13<br>5-14 |

|                                                                     | APPENDIX A ELECTRICAL CHARACTERISTICS                                                                                                                  |                              |

|                                                                     | APPENDIX B MECHANICAL DATA AND ORDERING INFORM                                                                                                         | IATION                       |

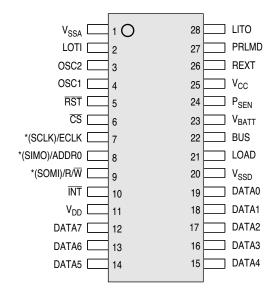

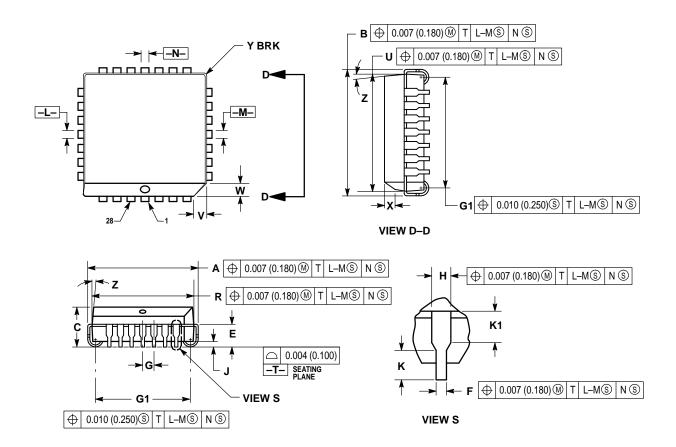

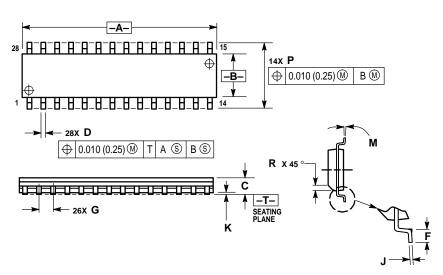

| B.1<br>5.5<br>B.2<br>B.3                                            | Pin Assignments Package Dimensions Obtaining Updated MC68HC58 Mechanical Information Ordering Information                                              | B-3<br>B-4                   |

|                                                                     | APPENDIX C DLC REGISTERS                                                                                                                               |                              |

| C.1<br>C.2<br>C.3<br>C.4                                            | Command Byte Register Configuration Byte Register Status Byte Register Completion Code Byte Register                                                   | C-2<br>C-3                   |

Paragraph Title Page

## LIST OF ILLUSTRATIONS

| Figure | Title                                                | Page |  |

|--------|------------------------------------------------------|------|--|

| 1-1    | MC68HC58 DLC Parallel Mode Block Diagram             | 1-3  |  |

| 1-2    | MC68HC58 DLC Serial Mode Block Diagram               |      |  |

| 2-1    | MC68HC58 DLC Pin Assignments                         |      |  |

| 2-2    | DLC Parallel Mode Circuit                            |      |  |

| 2-3    | DLC Serial Mode Circuit                              |      |  |

| 2-4    | Method 1 — Standby Mode Supplies Applied             | 2-14 |  |

| 2-5    | Method 2 — Switching VDD with PSEN                   |      |  |

| 2-6    | Method 3 — Switching VDD and VCC in Standby Mode     |      |  |

| 3-1    | J1850 Bus Message Components                         |      |  |

| 3-2    | J1850 Bus Frame Format (VPW)                         |      |  |

| 3-3    | J1850 VPW Symbols                                    |      |  |

| 3-4    | J1850 VPW Passive Symbols                            |      |  |

| 3-5    | J1850 VPW Active Symbols                             |      |  |

| 3-6    | J1850 VPW Bitwise Arbitration                        | 3-9  |  |

| 4-1    | DLC Operating Modes                                  | 4-1  |  |

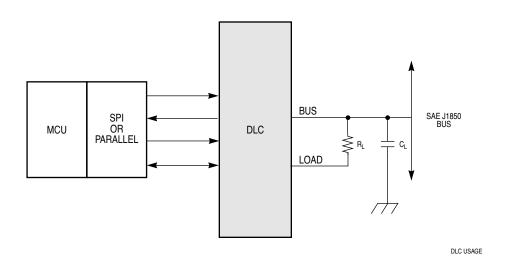

| 4-2    | DLC Usage                                            |      |  |

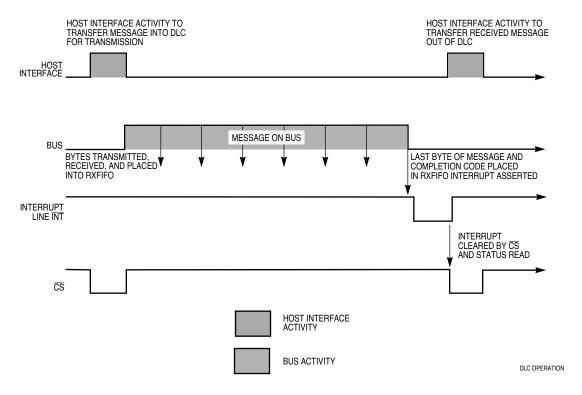

| 4-3    | DLC Operation                                        | 4-5  |  |

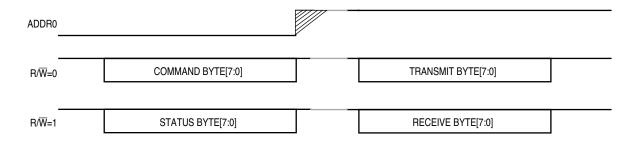

| 4-4    | Parallel Mode Byte Format                            | 4-6  |  |

| 4-5    | DLC Serial Mode Byte Format                          |      |  |

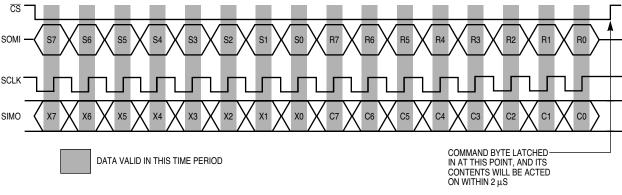

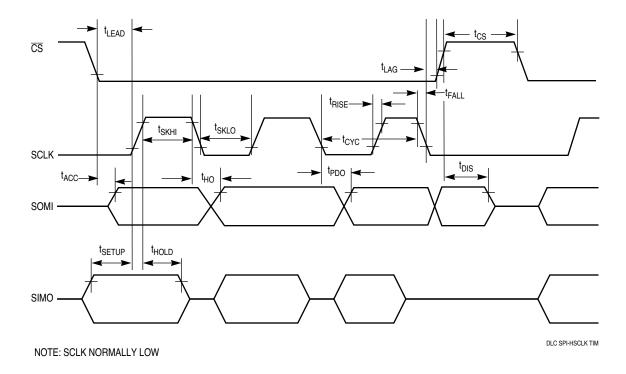

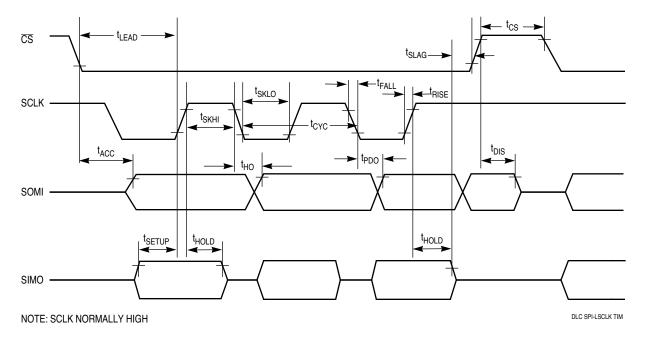

| 4-6    | SPI Transfer — Clock Polarity Low                    | 4-10 |  |

| 4-7    | SPI Transfer — Clock Polarity High                   | 4-10 |  |

| 4-8    | Host/DLC Serial Mode Initialization Routine          | 4-11 |  |

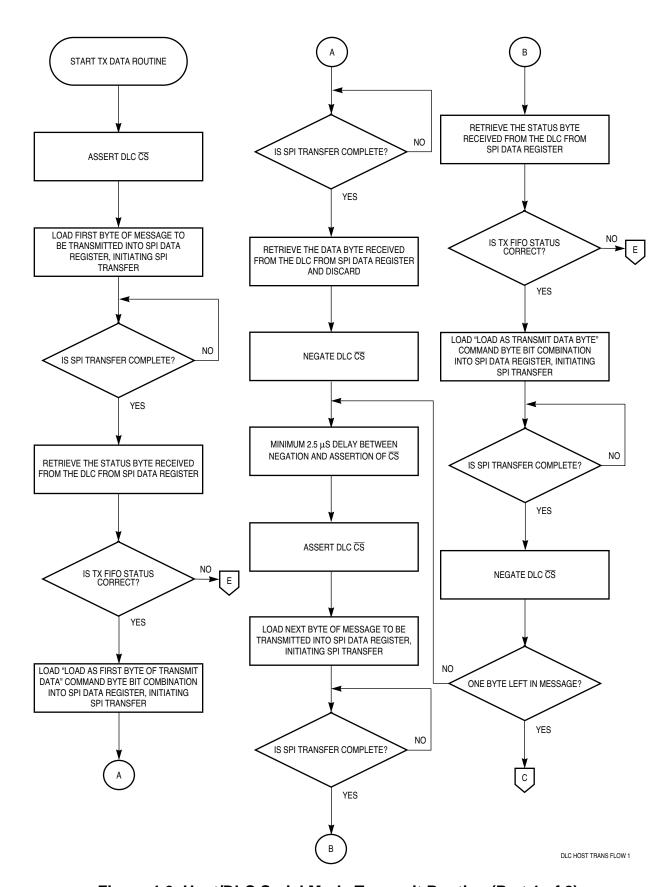

| 4-9    | Host/DLC Serial Mode Transmit Routine (Part 1 of 2)  | 4-14 |  |

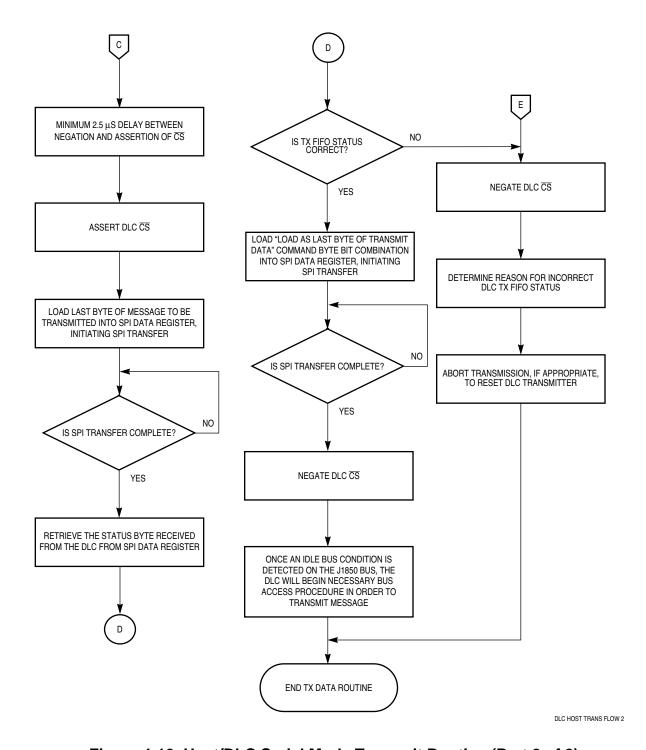

| 4-10   | Host/DLC Serial Mode Transmit Routine (Part 2 of 2)  | 4-15 |  |

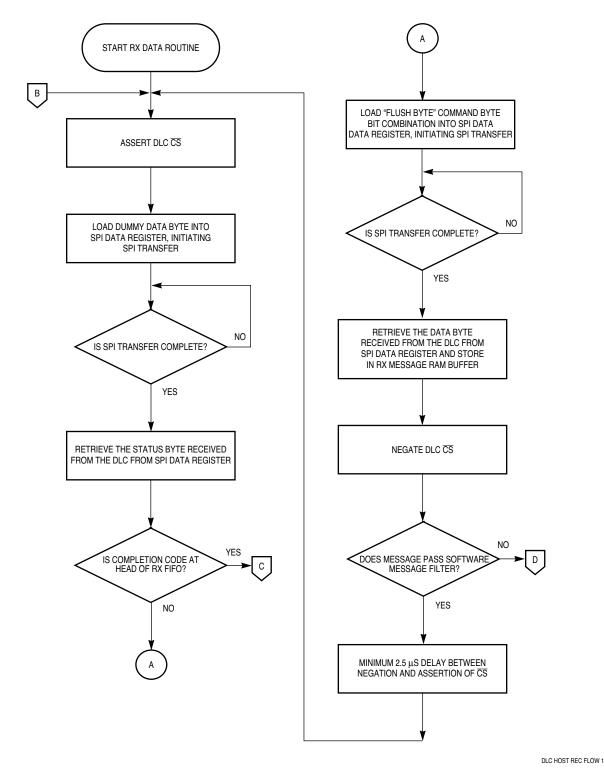

| 4-11   | Host/DLC Serial Mode Receive Routine (Part 1 of 2)   | 4-18 |  |

| 4-12   | Host/DLC Serial Mode Receive Routine (Part 2 of 2)   | 4-19 |  |

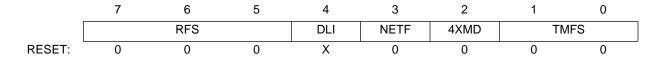

| A-1    | Parallel Interface Timing                            | A-3  |  |

| A-2    | SPI Timing — Active High SCLK                        | A-5  |  |

| A-3    | SPI Timing — Active Low SCLK                         |      |  |

| A-4    | DLC Interrupt Timing                                 | A-7  |  |

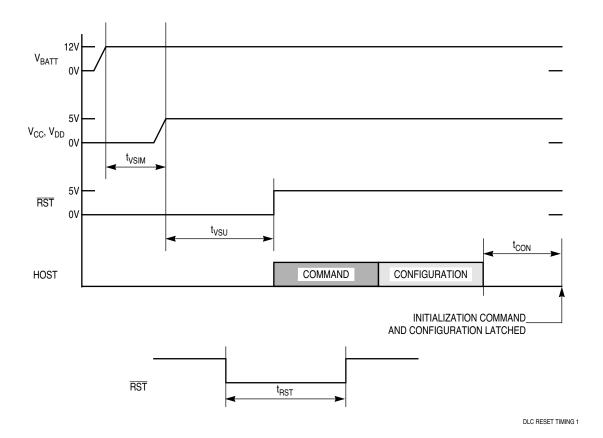

| A-5    | Reset Timing                                         | A-8  |  |

| A-6    | Variable Pulse-Width Modulation (VPW) Symbol Timings |      |  |

| B-1    | MC68HC58 28-Pin PLCC                                 |      |  |

| B-2    | MC68HC58 28-Pin SOIC                                 |      |  |

| B-3    | Case Outline #776-02                                 | B-3  |  |

| B-4    | Case Outline #751F-04                                | B-4  |  |

# LIST OF ILLUSTRATIONS (Continued) Title

Figure Title Page

MOTOROLA MC68HC58

TECHNICAL DATA

## LIST OF TABLES

| Tab  | le Title                                                         | Page |

|------|------------------------------------------------------------------|------|

|      | MC68HC58 DLC Parallel Mode Pin Function                          |      |

| 2-2  | MC68HC58 DLC Serial Mode Pin Functions                           | 2-7  |

|      | Parallel Transfers                                               |      |

| 4-2  | Minimum Time Between Operations                                  | 4-7  |

|      | Serial Transfers                                                 |      |

|      | IFR Error Conditions                                             |      |

|      | General Command Summary                                          |      |

|      | Byte Type and Destination Summary                                |      |

|      | RFC Field Encoding                                               |      |

|      | Internal Clock Frequency Derivations                             |      |

|      | RFS Field Encoding                                               |      |

|      | TMFS Field Encoding                                              |      |

|      | TMS Field Encoding                                               |      |

|      | ERRC Field Encoding                                              |      |

|      | Operating Conditions                                             |      |

|      | Electrical Characteristics                                       |      |

|      | Absolute Maximum Ratings                                         |      |

|      | Parallel Interface Parameters                                    |      |

|      | Serial Interface Parameters                                      |      |

|      | Standby and Interrupt Timing                                     |      |

|      | Reset Timing                                                     |      |

|      | Transceiver Requirements (DC)                                    |      |

|      | Transmitter VPW Symbol Timings                                   |      |

|      | O Receiver VPW Symbol Timings                                    |      |

|      | MC68HC58 Ordering Information                                    |      |

|      | General Command Summary (GCOM)                                   |      |

|      | Byte Type and Destination Summary (BTAD)RFC Field Encoding (RFC) |      |

|      | Test Mode Control Bit (TM)                                       |      |

|      | Test Configuration Field (TC)                                    |      |

|      | Interrupt Mask Bit (IMSK)                                        |      |

|      | Interrupt Mode Bit (IMOD)                                        |      |

| C-8  | Internal Clock Frequency Field (OSCD)                            | C-2  |

|      | High-Speed Control Bit (4X)                                      |      |

|      | 0 Receive FIFO Status Field Encoding (RFS)                       |      |

|      | 1 Data Link Idle Bit (DLI)                                       |      |

| C-12 | 2 Network Fault Bit (NETF)                                       |      |

|      | 3 4X Mode Bit (4XMD)                                             |      |

| C-14 | 4 Transmit FIFO Status Field Encoding (TMFS)                     |      |

|      | 5 Error Bit (ERRF)                                               |      |

|      | 6 Receive FIFO Overrun Bit (RFO)                                 |      |

|      |                                                                  |      |

## LIST OF TABLES (Continued)

| Table | e Title                                 | Page |

|-------|-----------------------------------------|------|

| C-17  | Transmitter Status Field Encoding (TMS) |      |

|       | In-Frame Response Bit (IFR)             |      |

|       | In-Frame Response CRC Bit (IFRC)        |      |

| C-20  | Error Code Field Encoding               |      |

### **SECTION 1INTRODUCTION**

The MC68HC58 DLC (data link controller) handles microcontroller unit (MCU) to Society of Automotive Engineers (SAE) J1850 bus interface duties. The MC68HC58 DLC is the successor to the MC68HC56 DLCP (data link controller parallel) and the MC68HC57 DLCS (data link controller serial). The MC68HC58 is pin configurable to communicate with a host MCU via an 8-bit non-multiplexed parallel data bus or a Motorola serial peripheral interface.

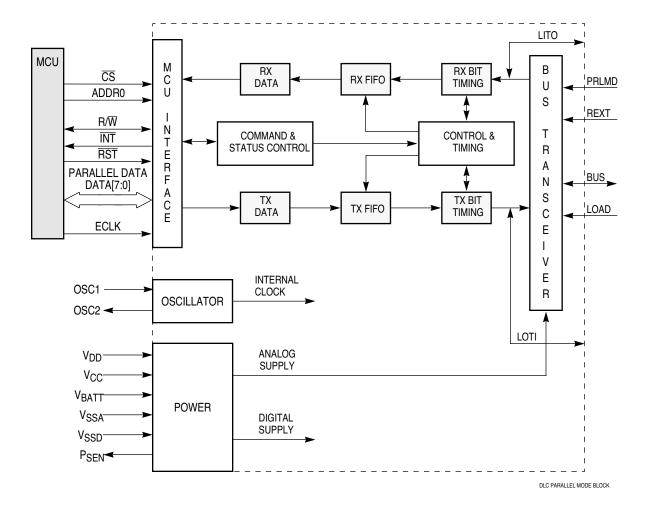

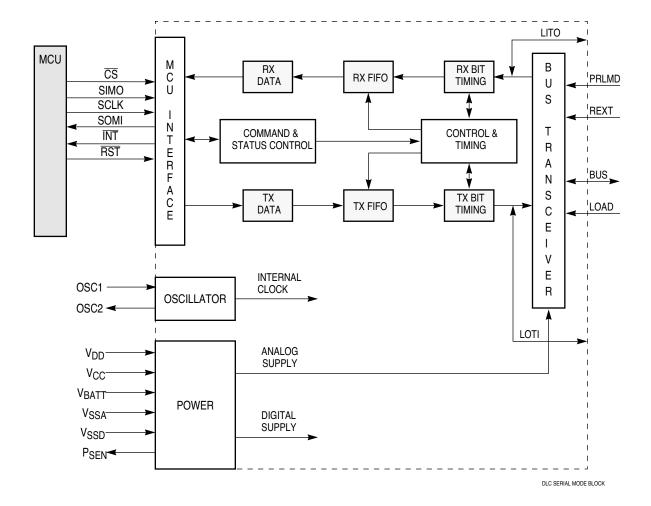

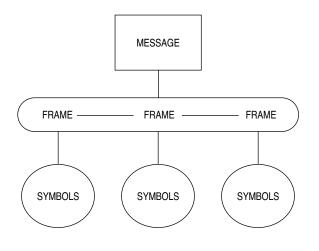

The DLC consists of control logic and bus transceiver circuits. **Figure 1-1** shows the internal structure of a DLC configured for parallel mode. **Figure 1-2** shows the internal structure of a DLC configured for serial mode. The built-in bus transceiver allows the DLC to be directly connected to the J1850 bus, thus providing a complete link between the central processing unit (CPU) host application and the J1850 bus. The J1850 bus protocol is a method of information transfer via messages (frames) between nodes. A node is any location on the J1850 bus that sends and receives messages.

The following are primary features of the DLC:

- SAE J1850 compatible

- Class 2 (vehicle bus communication protocol) compatible

- Handles all network protocol functions (access, arbitration, error detection)

- Supports polled or interrupt host DLC servicing

- Message buffering on transmit and receive

- On-board transceiver with waveshaping

- Operates with up to a 2-volt ground offset between network nodes

- Pin configurable SPI or parallel host interface

- Digitally filtered receiver

- Host configurable oscillator divisor

- Power conserving sleep feature with fast wakeup on bus or host activity

- High voltage CMOS (40 volt HVCMOS) process

- Built-in transient and ESD protection

The DLC handles SAE J1850 frames with minimal MCU servicing. Each DLC can be operated in either interrupt mode or polled mode. Internal first in/first out (FIFO) buffers, 20 bytes for receiver data and 11 bytes for transmitter data, allow full frame length operations. The MCU typically transfers complete frames to the DLC for transmission on the SAE J1850 bus, and is interrupted only when a complete frame is received from the SAE J1850 bus. The DLC handles all arbitration, error detection, and optional in-frame response duties internally.

Changes to the operating configuration can be made at any time. Depending upon the command, the changes can be made immediately or following the current J1850 bus transaction.

The logic section of the DLC consists of the MCU interface, transmit and receive bit timing logic, transmit and receive FIFO buffer logic, the control and timing block (framing, error detection and bus arbitration), and command and status control logic.

The bus transceiver allows the DLC to be directly connected to the J1850 bus, thus providing a complete link between the MCU application and the J1850 bus.

Transceiver operation is constrained by available power and the need to function reliably in the presence of conducted and induced noise. The main source of conducted noise is the ground offset between nodes. The DLC operates correctly under any combination of offsets up to a maximum differential of two volts at any frequency. Induced noise tends to be composed of short-duration pulses. The receive bit timing section includes a digital filter to remove these pulses.

The transceiver provides a waveshaped seven volt serial analog signal in response to a timed signal from the bit timing logic. The transceiver also receives J1850 bus waveforms, and provides the control logic with unfiltered inputs.

To achieve the 7-volt signal level necessary for the J1850 bus, the transceiver has a separate 9- to 16-volt power supply input ( $V_{BATT}$ ). The transceiver actively drives the J1850 bus high, and passively allows an RC load to pull the J1850 bus down. If ground is lost, the transceiver releases the J1850 bus. The transceiver also protects the MCU interface by not passing on any disruptive signals that may be on the J1850 bus.

Figure 1-1 MC68HC58 DLC Parallel Mode Block Diagram

Figure 1-2 MC68HC58 DLC Serial Mode Block Diagram

#### SECTION 2SIGNAL AND PIN DESCRIPTIONS

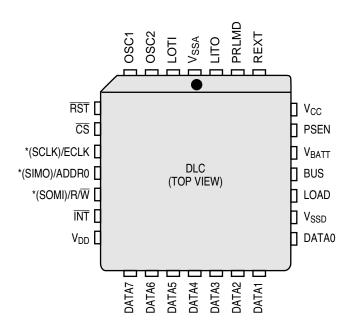

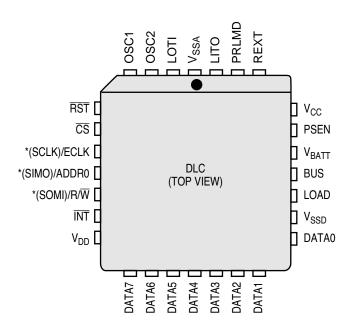

The MC68HC58 DLC is available in a 28-pin plastic leaded chip carrier (PLCC) package and a 28-pin small outline integrated circuit (SOIC) package. The MC68HC58 is pin configurable to communicate with a host MCU via a serial or parallel interface. Serial or parallel mode is selected by connecting the PRLMD pin to ground or V<sub>DD</sub> respectively. Pin function and recommended interconnections are discussed in the following paragraphs. Refer to **APPENDIX B MECHANICAL DATA AND ORDERING INFORMATION** for information on package dimensions and ordering information.

#### 2.1 MC68HC58 DLC Parallel Mode

When the PRLMD pin is tied to  $V_{DD}$ , the MC68HC58 DLC communicates with the host MCU via a parallel interface. Interface timing is based on the M6800 external bus clock signal (ECLK). Motorola M68HC11, M68HC16, and M68300 series MCUs have ECLK outputs, but any host MCU that meets the timing specification can be used.

Figure 2-1 is a pinout of the MC68HC58 (PLCC).

\* () INDICATES PIN ASSIGNMENTS FOR SERIAL MODE OPERATION

DLC PIN ASSIGNMENT

Figure 2-1 MC68HC58 DLC Pin Assignments

#### 2.1.1 DLC Parallel Mode Pin Function

**Table 2-1** summarizes DLC pin functions when operating in parallel mode. Detailed discussion of each function follows. Refer to **APPENDIX A ELECTRICAL CHARAC-TERISTICS** for more information on electrical specifications.

Table 2-1 MC68HC58 DLC Parallel Mode Pin Function

| Name              | Туре         | Function                           |

|-------------------|--------------|------------------------------------|

| ADDR0             | Input        | Address select signal              |

| BUS               | Input/Output | Serial data signal                 |

| CS                | Input        | DLC chip-select signal             |

| DATA[7:0]         | Input/Output | Bidirectional three-state data bus |

| ECLK              | Input        | 6800 bus clock                     |

| ĪNT               | Output       | DLC interrupt request              |

| LITO              | Input/Output | Logic in transceiver out           |

| LOAD              | Input        | External bus load connection       |

| LOTI              | Input/Output | Logic out transceiver in           |

| OSC1              | Input        | External clock connection          |

| OSC2              | Output       | External reference connection      |

| PSEN              | Output       | Power supply status signal         |

| PRLMD             | Input        | Parallel/serial mode select signal |

| REXT              | Input        | Transceiver biasing resistor       |

| RST               | Input        | DLC reset signal                   |

| R/W               | Input        | DLC data transfer control          |

| V <sub>BATT</sub> | Power supply | Transceiver power connection       |

| V <sub>cc</sub>   | Power supply | Analog power connection            |

| V <sub>DD</sub>   | Power supply | Digital power connection           |

| V <sub>SSA</sub>  | Power supply | Analog ground                      |

| V <sub>SSD</sub>  | Power supply | Digital ground                     |

#### 2.1.1.1 ADDR0 — Address Bit

This pin is used in conjunction with the R/W signal to address the DLC in the MCU memory map. Although the name ADDR0 implies that the pin should be connected to address line 0, it can in fact be connected to any address line to place it at a desired location in memory.

#### 2.1.1.2 BUS — SAE J1850 Multiplex Bus

This pin connects the DLC to the SAE J1850 multiplex bus. The bus signal is driven to a nominal 7 Vdc with respect to the bus load when in an active level; it is grounded through the bus load when in a passive level.

## 2.1.1.3 <del>CS</del> — DLC Chip-Select

This pin is used to input the DLC parallel data exchange enable signal. It has a nominal 15  $k\Omega$  internal pull-up resistor.

#### 2.1.1.4 DATA[7:0] — DLC Data Bus

These pins are the bidirectional data lines used to transfer parallel bytes to and from the DLC. The data lines are in high-impedance state unless  $\overline{CS}$  is asserted.

#### 2.1.1.5 ECLK — 6800 Bus Clock

This pin is used to input a 6800 peripheral bus clock. Clock timing controls parallel data exchange with the MCU. M68HC11, M68HC16, and M68300 MCUs all provide clock outputs to facilitate connection of 6800-timed peripherals.

### 2.1.1.6 INT — DLC Interrupt Request

This pin is used to output an open drain active-low interrupt request signal to the MCU. The signal is fully compatible with M68HC11, M68HC16, and M68300 interrupt request inputs. INT must have an external pull-up resistor.

#### 2.1.1.7 LITO — Logic In Transceiver Out

This pin is an external tap on the internal receive signal sent from the transceiver to the control logic. It is used for testing only, and must be left unconnected for normal operation.

#### 2.1.1.8 LOAD — External Bus Load

This pin provides an internal ground connection for the SAE J1850 multiplex bus load resistor. If DLC analog ground is lost, LOAD goes to a high-impedance state.

#### 2.1.1.9 LOTI — Logic Out Transceiver In

This pin is an external tap on the internal transmit signal sent from the control logic to the transceiver. It is used for testing only, and must be left unconnected for normal operation.

#### 2.1.1.10 OSC1, OSC2 — External Oscillator

The DLC can operate with either an external clock signal or an external ceramic resonator. These pins support connection of both types of clock. If an external clock source is used, the signal is input via OSC1, and OSC2 is left floating. If a resonator is used, it is connected between OSC1 and OSC2.

#### 2.1.1.11 PRLMD — Parallel Mode

This pin is used to select the desired MCU interface mode. When this pin is pulled up to  $V_{DD}$ , the parallel mode is selected.

#### 2.1.1.12 PSEN — Power Supply Enable

This pin provides an external  $V_{BATT}$  source when the DLC is active. It assumes high-impedance state when the DLC is in standby mode.

#### 2.1.1.13 RST — DLC Reset

This pin is used to input an active-low system reset signal. RST must have an external pull-up resistor.

#### 2.1.1.14 REXT — External Bias Resistor

This pin connects an external bias resistor to the transceiver. The resistor value determines the waveform of the transmitted bus signal.

#### 2.1.1.15 R/W — Read/Write Strobe

This pin is used to input a data direction control signal to the DLC. This signal is used in conjunction with the ADDR0 signal to select the DLC at a specific address in the MCU memory map.

## 2.1.1.16 V<sub>BATT</sub> — Battery Voltage

This pin connects a separate switched or unswitched 12 Vdc power supply to the DLC bus transceiver. This supply should be well regulated and protected against switching transients.

## 2.1.1.17 V<sub>CC</sub> — Analog Power Supply Voltage

This pin connects a nominal 5 Vdc power supply to the analog transceiver circuitry in the DLC. For maximum noise immunity,  $V_{CC}$  supply path should be separate from  $V_{DD}$  supply path.

## 2.1.1.18 V<sub>DD</sub> — Digital Power Supply Voltage

This pin connects a nominal 5 Vdc power supply to the digital control circuitry in the DLC. For maximum noise immunity, the  $V_{DD}$  supply path should be separate from  $V_{CC}$  supply path.

## 2.1.1.19 V<sub>SSA</sub> — Analog Power Ground

This pin provides the analog power ground connection to the DLC. Loss of analog ground directly affects operation of the LOAD pin. For best noise immunity in operation, the  $V_{\rm SSA}$  ground path should be separate from the  $V_{\rm SSD}$  ground path.

## 2.1.1.20 $V_{SSD}$ — Digital Power Ground

This pin provides the digital power ground connection to the DLC. For best noise immunity in operation, the  $V_{\rm SSD}$  ground path should be separate from the  $V_{\rm SSA}$  ground path.

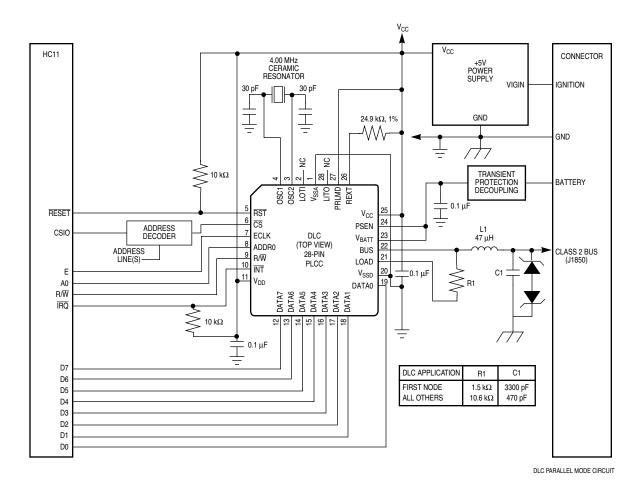

#### 2.1.2 Example DLC Parallel Mode System

**Figure 2-2** shows a typical DLC circuit (PLCC). The component values displayed are recommended, although adjustment may be required in actual operation. The example is shown wired for low-power standby mode. Typical M68HC11 MCU connections are shown, but any host MCU that has appropriate inputs and outputs compatible with DLC signals can be used.

Figure 2-2 DLC Parallel Mode Circuit

The following additional guidelines apply to Figure 2-2:

- 1. Pull-up resistor values depend on electrical characteristics of the host MCU.

- Exact values for the external components are a function of printed circuit board (PCB) capacitance and inductance, socket capacitance, operating voltage and crystal technology.

- 3. The example ceramic resonator is a Murata CSA4.00MGA with typical load capacitance. The DLC contains an internal 1 M $\Omega$  resistor across OSC1 and OSC2. No external resistor is required.

- 4. L1 is a surface mount inductor which should have characteristics similar to TDK NL322522T-470J-3.

- 5. The external bias resistor (REXT) determines the waveshape of J1850 bus signals transmitted by the DLC.

- For maximum noise immunity, V<sub>CC</sub> and V<sub>DD</sub> should be supplied by separate lines; V<sub>SSA</sub> and V<sub>SSD</sub> should also be separate. The V<sub>BATT</sub> pin is shown attached to the permanent "unswitched" battery supply to take advantage of the better transient protection found on this circuit rather than the "switched" battery, or ignition.

- 7. Applications whose requirements for electro-static discharge (ESD) protection exceed the level provided by the bus pin internal circuitry and the bus loading components may require additional transient protection. The example in Figure 2-2 illustrates this by including two 16 volt zener diodes placed between the bus and ground. These diodes (part # P4SMA16AT3) should be located as close to the module connector as possible. Refer to APPENDIX A ELECTRICAL CHARACTERISTICS for information on maximum voltage ratings.

- 8. One J1850 node in the vehicle typically has a heavier BUS to LOAD pin loading. This allows a smaller differential between the total network load of two nodes versus 32 nodes. If 26 nodes or more are used, the heavier loading should not be present as this may violate the maximum capacitance and minimum resistance allowed by the J1850. A network of 26 or more nodes should all have the lower load values.

- Figure 2-2 reflects a configuration for no wake-up upon the detection of J1850 bus activity. If system wake-up upon the detection of J1850 bus activity is desired, perform the following:

- Tie the V<sub>DD</sub> pin to a 5 Vdc power supply. This 5 Vdc power supply is powered down when the DLC is placed in the standby mode.

- Tie the PSEN pin on the DLC through a 33 k $\Omega$  resistor to the ignition input of the power supply/regulator. This limits the current sourced by the DLC. This resistor value should be determined by the individual application. A 10 k $\Omega$  pull-down resistor should be included from the PSEN line to ground. A 100 k $\Omega$  resistor from the  $\overline{\text{RST}}$  pin to ground should also be added.

- Tie the V<sub>CC</sub> pin and the pull-up points for the external bias resistor (REXT) on the DLC to a separate 5 Vdc power supply. This 5 Vdc power supply remains powered up when the rest of the node is powered down.

#### 2.2 MC68HC58 DLC Serial Mode