FUJITSU SEMICONDUCTOR

DATA SHEET

DS04-13501-2E

### LINEAR IC

# R-2R TYPE 8-BIT D/A CONVERTER WITH OPERATIONAL AMPLIFIER OUTPUT BUFFERS

### MB88346B

#### DESCRIPTION

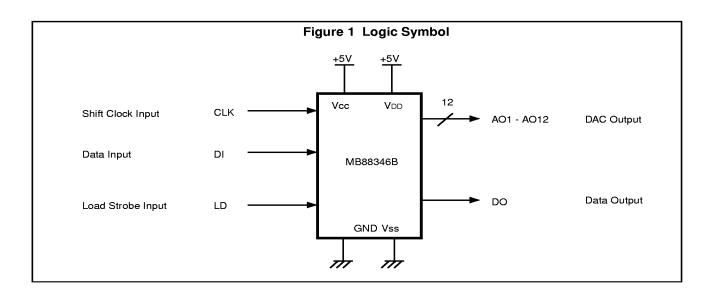

The Fujitsu MB88346B is an R-2R type 8-bit resolution digital-to-analog converter (DAC), designed for interface with a wide range of general 4-bit and 8-bit microcontrollers including Fujitsu's MB88200 family, MB8850 family, and MB88500 family 4-bit single-chip microcontrollers.

The MB88346B has an 8-bit x 12-channel D/A converter with operational amplifier output buffers. Digital data are input serially by individual channel units. The loaded digital data are converted into analog DC voltages by the D/A converter in 20  $\mu s$  settling time. Also, the MB88346B has operational amplifier output buffers. These operational amplifier output buffers are connected to each channel of the D/A converter, and provide high current drive capability. The MB88346B is suitable for electronic volumes and replacement for potentiometers for adjustment, in addition to normal D/A converter applications.

#### **■ FEATURES**

- Conversion method : R-2R resistor ladder

- 8-bit x 12-channel D/A converter with operational amplifier output buffers

- · Max. 2.5MHz Serial data input

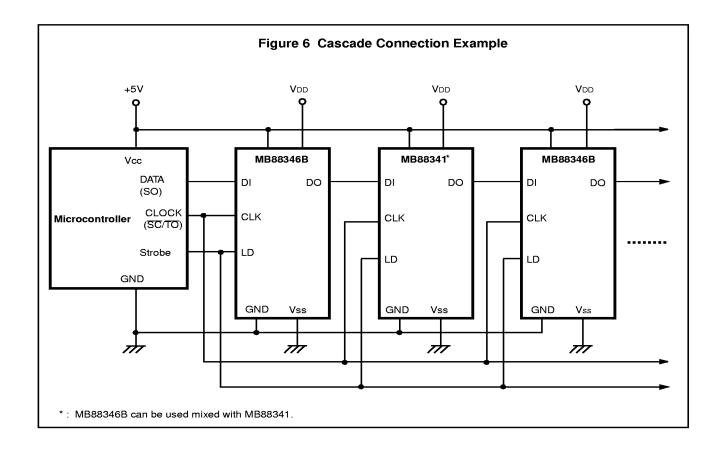

- Serial data output for cascade connection

- Max. 20 µs DAC output settling time

- Max. +1.0/-1.0 mA analog output sink/source current

- Two separate power supply/ground lines for MCU interface block/ operational amplifier output buffer block and D/A converter block

- Pin compatible with MB88341

- Single +5V power supply

- Wide operating temperature range: -20°C to +85°C

- Silicon-gate CMOS process

- Three package options:

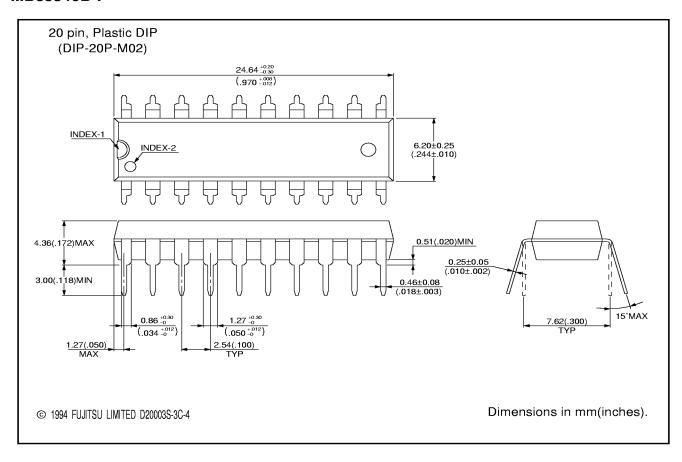

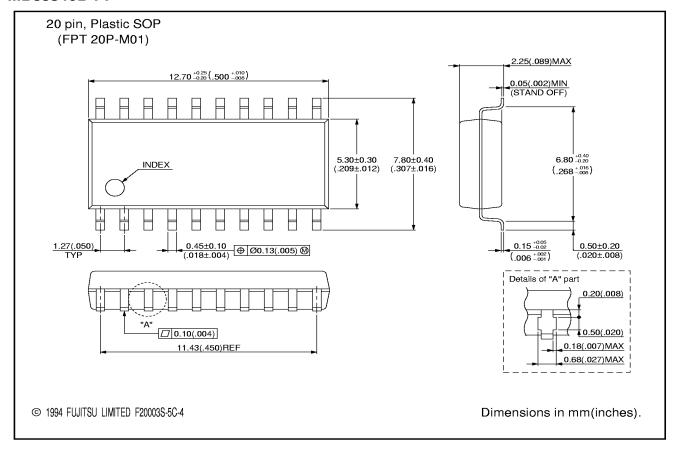

20-pin plastic DIP (Suffix : -P), 20-pin plastic SOP (Suffix : -PF), 20-pin plastic SSOP(Suffix : -PFV)

PLASTIC DIP (DIP-20P-M02)

MB88346B-PF

PLASTIC SOP (FPT-20P-M01)

MB88346B-PFV

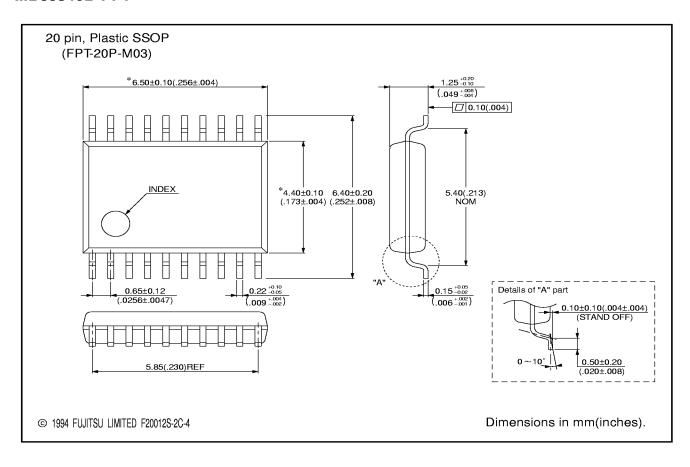

PLASTIC SSOP (FPT-20P-M03)

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

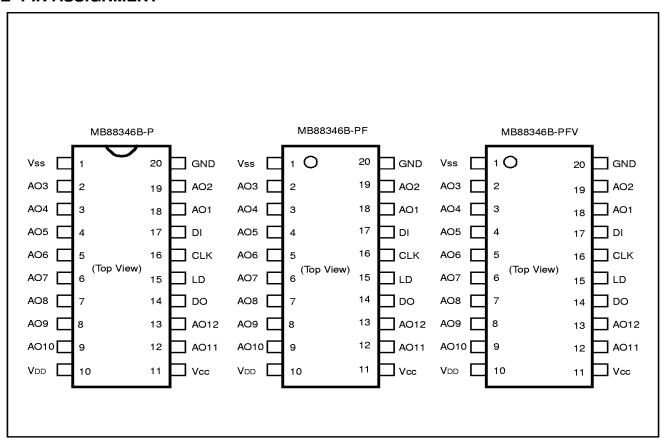

#### **■ PIN ASSIGNMENT**

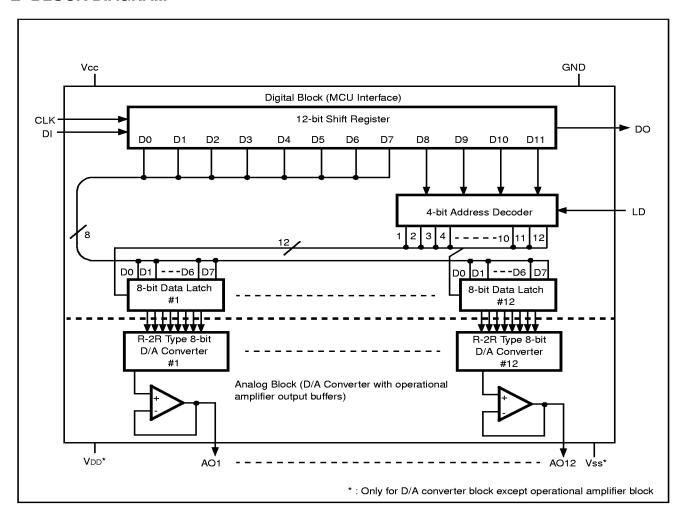

#### **■ BLOCK DIAGRAM**

#### **■ PIN DESCRIPTION**

PIN ASSIGNMENT and Tableshow the pin assignment and pin description of the MB88346B.

**Table 1 Pin Description**

| Symbol                                                                              | Pin No.                                                      | Туре | Name & Function                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Su                                                                            | pply                                                         | •    | •                                                                                                                                                                                                                                                                                                                                    |

| Vcc                                                                                 | 11                                                           | -    | +5V DC power supply pin for the digital block (MCU interface) and operational amplifier output buffers.                                                                                                                                                                                                                              |

| GND                                                                                 | 20                                                           | -    | Ground pin for the digital block (MCU interface) and operational amplifier output buffers.                                                                                                                                                                                                                                           |

| VDD                                                                                 | 10                                                           | -    | DC power supply pin for the analog block (D/A converter) except operational amplifier output buffers.                                                                                                                                                                                                                                |

| Vss                                                                                 | 1                                                            | -    | Ground pin for the analog block (D/A converter) except operational amplifier output buffers.                                                                                                                                                                                                                                         |

| Control Ir                                                                          | put                                                          | •    |                                                                                                                                                                                                                                                                                                                                      |

| CLK                                                                                 | 16                                                           | I    | Shift clock input to the internal 12-bit shift register: At the rising edge of CLK data on the DI pin is shifted into the LSB of the shift register and contents of the shift register are shifted right (to the MSB).                                                                                                               |

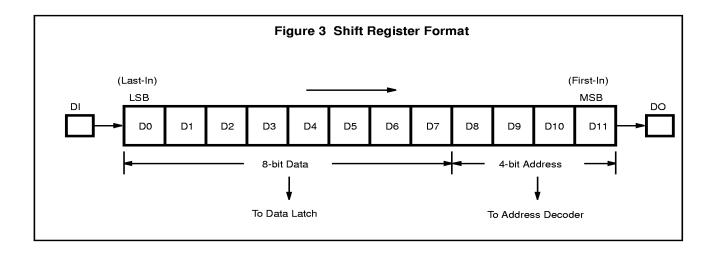

| LD                                                                                  | 15                                                           | I    | Load strobe input for a 12-bit address/data: A high level on the LD pin latches a 4-bit address (upper 4 bits: D11 to D8) of the internal 12-bit shift register into the internal address decoder, and writes 8-bit data (lower 8 bits: D7 to D0) of the shift register into an internal data latch selected by the latched address. |

| Data Inpu                                                                           | t/Output                                                     |      |                                                                                                                                                                                                                                                                                                                                      |

| Di                                                                                  | 17                                                           | ı    | Serial address/data input to the internal 12-bit shift register: The address/data format is that upper 4 bits (D11 to D8) indicate an address and lower 8 bits (D7 to D0) indicate data. The D11 (MSB) is the first-in bit and D0 (LSB) is the last-in bit.                                                                          |

| Do                                                                                  | 14                                                           | 0    | Serial address/data output from the internal 12-bit shift register: This is an output pin of the MSB bit data of the 12-bit shift register. This pin allows a cascade connection of the device.                                                                                                                                      |

| DAC Outp                                                                            | out                                                          | •    |                                                                                                                                                                                                                                                                                                                                      |

| AO1<br>AO2<br>AO3<br>AO4<br>AO5<br>AO6<br>AO7<br>AO8<br>AO9<br>AO10<br>AO11<br>AO12 | 18<br>19<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>12<br>13 | 0    | 8-bit resolution D/A converter outputs: 12 channels of DAC outputs (AO1 to AO12) are provided.  Each output channel has an operational amplifier output buffer for analog output data.                                                                                                                                               |

#### **■ FUNCTIONAL DESCRIPTION**

#### **OVERVIEW**

The MB88346B is an R-2R resistor ladder type, 8-bit resolution digital-to-analog converter (DAC) device. The MB88346B has 12 channels of D/A converters with operational amplifier output buffers. 8-bit digital data are loaded into internal data latches by individual DAC channel units. The loaded digital data are converted into analog DC voltages through the internal D/A converter in max. 20 µs settling time. And the analog DC voltages source/sink the output current through the operational amplifier output buffers. For cascade connection, a serial data output is provided.

#### **DEVICE CONFIGURATION**

As illustrated in BLOCK DIAGRAM, the MB88346B device is composed by the digital block (MCU interface) and analog block (D/A converter with operational amplifier output buffers). The digital block consists of a 12-bit shift register, a 4-bit address decoder, and 12-channels of 8-bit data latches. The analog block includes 12 channels of 8-bit D/A converters with operational amplifier output buffers connecting to the data latches. For electrically stable operation the power supply and ground lines are separate between the digital block (MCU interface) and operational amplifier output buffers, and analog block except operational amplifier output buffers.

#### **DEVICE OPERATION**

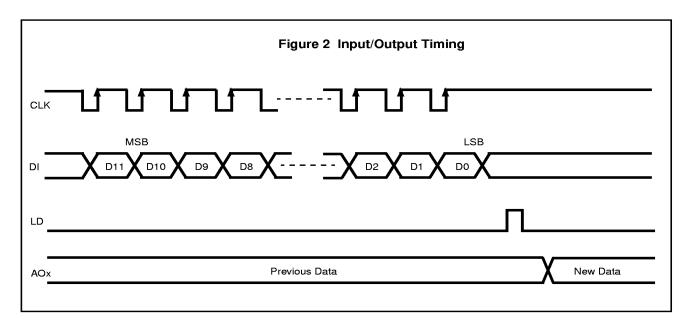

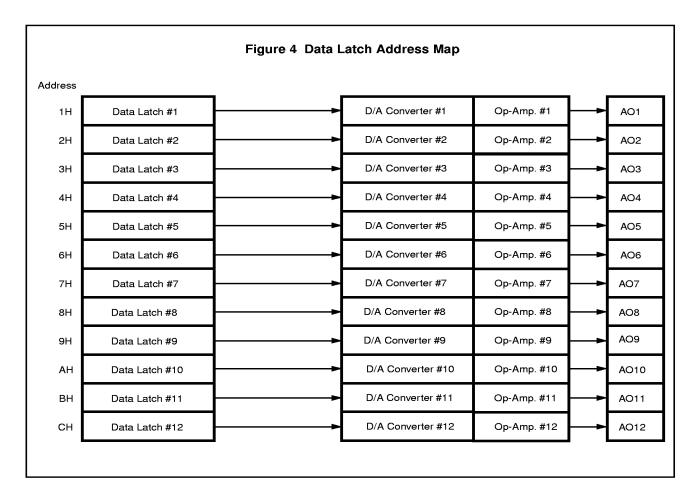

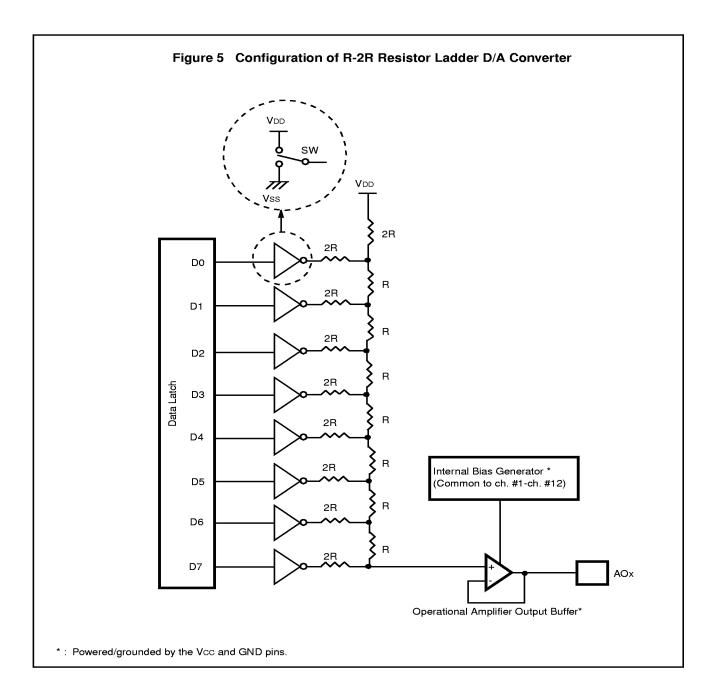

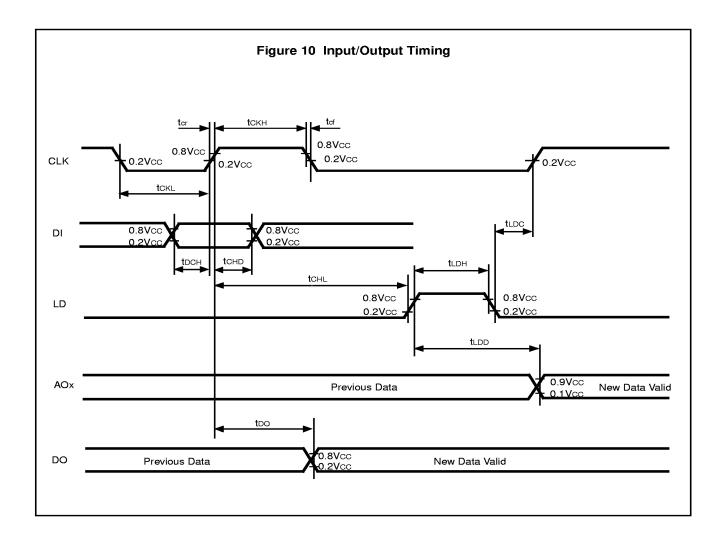

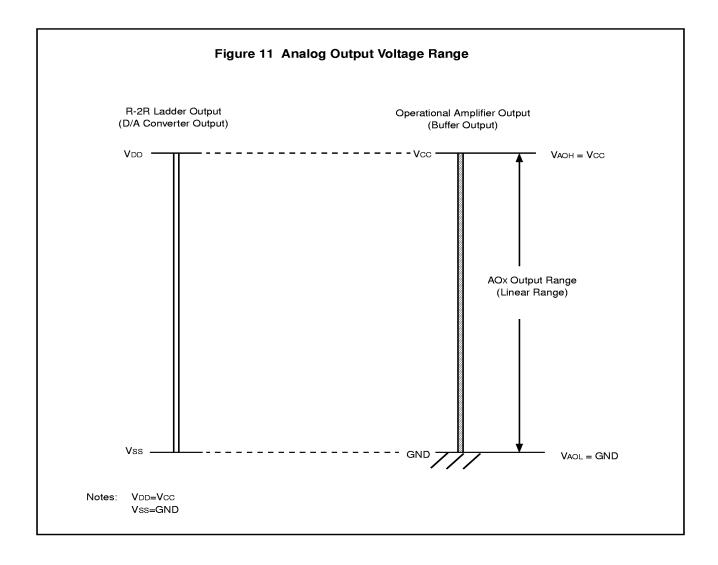

Figure 2 shows the input/output timing. A 12-bit address/data is serially input into the shift register through the DI pin synchronously with the rising edge of CLK. The format of the shift register is shown in Figure 3. The lower 8 bits (D7 to D0) are data bits to be converted, and the upper 4 bits are address bits (D11 to D8) to select a data latch to be written. A high level on the LD pin loads the address decoder with the 4-bit address to select a data latch, and writes the 8-bit data into a selected data latch. Figure 4 shows the data latch address map, and Table, address decoding. 8-bit data written into individual data latches are converted into analog DC voltages, dividing the supply voltage |VDD-Vss| through R-2R resistor ladders of D/A converters. The operational amplifier output buffers at individual D/A converter outputs can source up to 1.0 mA of the output current. Figure 5 shows a configuration of the R-2R resistor ladder D/A converter with operational amplifier, and Table 3analog DC voltages corresponding to each digital data.

Table 2 Address Decoding

|    | Add | ress | Data Latch Selected |                |

|----|-----|------|---------------------|----------------|

| D8 | D9  | D10  | D11                 | MB88346B       |

| 0  | 0   | 0    | 0                   | Deselected     |

| 0  | 0   | 0    | 1                   | Data Latch #1  |

| 0  | 0   | 1    | 0                   | Data Latch #2  |

| 0  | 0   | 1    | 1                   | Data Latch #3  |

| 0  | 1   | 0    | 0                   | Data Latch #4  |

| 0  | 1   | 0    | 1                   | Data Latch #5  |

| 0  | 1   | 1    | 0                   | Data Latch #6  |

| 0  | 1   | 1    | 1                   | Data Latch #7  |

| 1  | 0   | 0    | 0                   | Data Latch #8  |

| 1  | 0   | 0    | 1                   | Data Latch #9  |

| 1  | 0   | 1    | 0                   | Data Latch #10 |

| 1  | 0   | 1    | 1                   | Data Latch #11 |

| 1  | 1   | 0    | 0                   | Data Latch #12 |

| 1  | 1   | 0    | 1                   | Deselected     |

| 1  | 1   | 1    | 0                   | Deselected     |

| 1  | 1   | 1    | 1                   | Deselected     |

**Table 3 Data Conversion**

|    |    |    | Da | DAC Output Level |    |    |    |                             |

|----|----|----|----|------------------|----|----|----|-----------------------------|

| D7 | D6 | D5 | D4 | D3               | D2 | D1 | D0 | AOx                         |

| 0  | 0  | 0  | 0  | 0                | 0  | 0  | 0  | ≈ Vss                       |

| 0  | 0  | 0  | 0  | 0                | 0  | 0  | 1  | ≈ (VDD-VSS) x 1/255 + VSS   |

| 0  | 0  | 0  | 0  | 0                | 0  | 1  | 0  | ≈ (VDD-Vss) x 2/255 + Vss   |

| 0  | 0  | 0  | 0  | 0                | 0  | 1  | 1  | ≈ (VDD-VSS) x 3/255 + VSS   |

|    |    | :  | i  |                  | i  | i  |    |                             |

| 1  | 1  | 1  | 1  | 1                | 1  | 1  | 0  | ≈ (VDD-VSS) x 254/255 + VSS |

| 1  | 1  | 1  | 1  | 1                | 1  | 1  | 1  | ≈ VDD                       |

#### **■ APPLICATION DESCRIPTION**

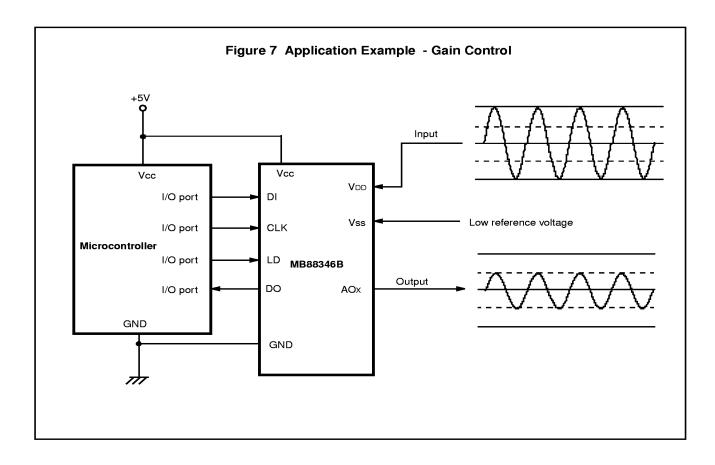

The MB88346B is suitable for electronic volumes and replacement for adjustment potentiometers, in addition to normal D/A converter applications. Figure 7 illustrates application example for a gain control.

# ■ ELECTRICAL CHARACTERISTICS ABSOLUTE MAXIMUM RATINGS (See NOTE)

| Parameter                     | Symbol |      | Rating |         | Unit       | Condition                |  |

|-------------------------------|--------|------|--------|---------|------------|--------------------------|--|

| Parameter                     | Symbol | Min  | Тур    | Max     | Offic      | Condition                |  |

| Supply Voltage                | Vcc    | -0.3 | -      | 7.0     | ٧          | Ta = +25°C               |  |

| Supply Voltage                | VDD    | -0.3 | -      | 7.0     | ٧          | $GND = 0 V VDD \le Vcc,$ |  |

| Input Voltage                 | VIN    | -0.3 | -      | Vcc+0.3 | ٧          | Ta = +25°C               |  |

| Output Voltage                | Vout   | -0.3 | -      | Vcc+0.3 | ٧          | GND = 0 V                |  |

| Power Dissipation             | PD     | -    | -      | 250     | m <b>W</b> |                          |  |

| Operating Ambient Temperature | Та     | -20  | -      | +85     | °C         |                          |  |

| Storage Temperature           | Tstg   | -55  | -      | +150    | °C         |                          |  |

NOTE: Permanent device damage may occur if the above ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                            | Cymphal |     | Value | Unit    | Condition |              |  |

|------------------------------------------------------|---------|-----|-------|---------|-----------|--------------|--|

| Parameter                                            | Symbol  | Min | Тур   | Max     | Offic     | Condition    |  |

| Supply Voltage                                       | Vcc     | 4.5 | 5.0   | 5.5     | V         | \/\/         |  |

| (for MCU Interface/OpAmp. Block)                     | GND     | -   | 0     | -       | ٧         | Vcc≥Vdd      |  |

| Supply Voltage                                       | Vcc     | 2.0 | -     | Vcc     | ٧         | VDD-Vss≥2.0V |  |

| (for Analog Block*)                                  | Vss     | GND | -     | Vcc-2.0 | ٧         |              |  |

| Analog Output Source<br>Current                      | IAL     | -   | -     | +1.0    | mA        |              |  |

| Analog Output Sink<br>Current                        | Іан     | -   | -     | +1.0    | mA        |              |  |

| Analog Output Load Capacitance for oscillation limit | Cal     | -   | -     | 1.0     | μF        |              |  |

| Operating Ambient<br>Temperature                     | Та      | -20 | -     | +85     | °C        |              |  |

<sup>\*:</sup> Except operational amplifier output buffer block

#### **■ DC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

#### Digital Block (MCU Interface)

| Parameter                               | Symbol   |                  | Value   | Unit    | Condition |                            |

|-----------------------------------------|----------|------------------|---------|---------|-----------|----------------------------|

| Farameter                               | Syllibol | Min              | Min Typ |         |           |                            |

| Active Supply Current (Vcc) *           | Icc      | -                | 2.5     | 4.5     | mA        | CLK = 1MHz, Unloaded       |

| Input Leakage Current (CLK, DI, and LD) | lilk     | -10              | -       | +10     | μΑ        | V <sub>IN</sub> = 0 to Vcc |

| Input Low Voltage (CLK, DI, and LD)     | VIL      | -                | -       | 0.2•Vcc | ٧         |                            |

| Input High Voltage<br>(CLK, DI, and LD) | ViH      | 0.5 <b>•</b> Vcc | -       | -       | ٧         |                            |

| Output Low Voltage (DO)                 | Vol      | -                | -       | 0.4     | ٧         | IOL = 2.5 mA               |

| Output High Voltage (DO)                | Vон      | Vcc-0.4          | -       | -       | ٧         | Іон = -400 μΑ              |

<sup>\*:</sup> Including the supply current to the operational amplifier block

#### Analog Block (D/A Converters with Operational Amplifier Output Buffers)

| Parameter                             | Cymbol | Value   |     |         | Unit | O a madiki a m                                                        |  |

|---------------------------------------|--------|---------|-----|---------|------|-----------------------------------------------------------------------|--|

| Parameter                             | Symbol | Min     | Тур | Max     | Unit | Condition                                                             |  |

| Supply Current (VDD) **               | IDD    | -       | 0.2 | 0.5     | mA   | Unloaded                                                              |  |

| Min. Analog Output<br>Voltage 1 (AOx) | VAOL1  | Vss     | -   | Vss+0.1 | ٧    | VDD=VCC, VSS=GND=0V<br>Unloaded, Didital Data=#00                     |  |

| Min. Analog Output<br>Voltage 2 (AOx) | VAOL2  | Vss-0.2 | Vss | Vss+0.2 | ٧    | VDD=VCC=5.0V, VSS=GND=0V<br>IAL=+500μA, Digital Data=#00              |  |

| Min. Analog Output<br>Voltage 3 (AOx) | VAOL3  | Vss     | -   | Vss+0.2 | ٧    | VDD=VCC=5.0V, VSS=GND=0V<br>IAH=+500μA, Digital Data=#00              |  |

| Min. Analog Output<br>Voltage 4 (AOx) | VAOL4  | Vss-0.3 | Vss | Vss+0.3 | ٧    | VDD=VCC=5.0V, VSS=GND=0V<br>IAL=+1.0mA, Digital Data=#00              |  |

| Min. Analog Output<br>Voltage 5 (AOx) | VAOL5  | Vss     | -   | Vss+0.3 | ٧    | VDD=VCC=5.0V, VSS=GND=0V<br>IAH=+1.0mA, Digital Data=#00              |  |

| Max. Analog Output<br>Voltage 1 (AOx) | Vaoh1  | VDD-0.1 | -   | VDD     | ٧    | VDD=VCC, VSS=GND=0V<br>Unloaded, Digital Data=#FF                     |  |

| Max. Analog Output<br>Voltage 2 (AOx) | VAOH2  | VDD-0.2 | -   | VDD     | ٧    | VDD=VCC=5.0V, VSS=GND=0V<br>IAL=+500μA, Digital Data=#FF              |  |

| Max. Analog Output<br>Voltage 3 (AOx) | Vаонз  | VDD-0.2 | VDD | VDD+0.2 | ٧    | V <sub>DD</sub> =VCC=5.0V, Vss=GND=0V<br>IAH=+500μA, Digital Data=#FF |  |

<sup>\*\*:</sup> Excluding the supply current to the operational amplifier block

Analog Block (D/A Converters with Operational Amplifier Output Buffers) - Continued

| Parameter                             | Symbol   |         | Value |         | Unit | Condition                                               |  |

|---------------------------------------|----------|---------|-------|---------|------|---------------------------------------------------------|--|

| Parameter                             | Syllibol | Min     | Тур   | Max     | Oill | Condition                                               |  |

| Max. Analog Output<br>Voltage 4 (AOx) | Va0н4    | VDD-0.3 | -     | VDD     | ٧    | VDD=VCC=5V, VSS=GND=0V,<br>IAL=+1.0mA, Digital Data=#FF |  |

| Max. Analog Output<br>Voltage 5 (AOx) | Vaoh5    | VDD-0.3 | VDD   | VDD+0.3 | ٧    | VDD=VCC=5V, Vss=GND=0V,<br>IAH=+1.0mA, Digital Data=#FF |  |

| Resolution (AOx)                      | Res      | -       | 8     | -       | bit  | Monotonicity                                            |  |

| Differential Error*<br>(AOx)          | DE       | -1.0    | 0     | +1.0    | LSB  | Unloaded, VDD≤Vcc-0.1V, Vss≥0.1V                        |  |

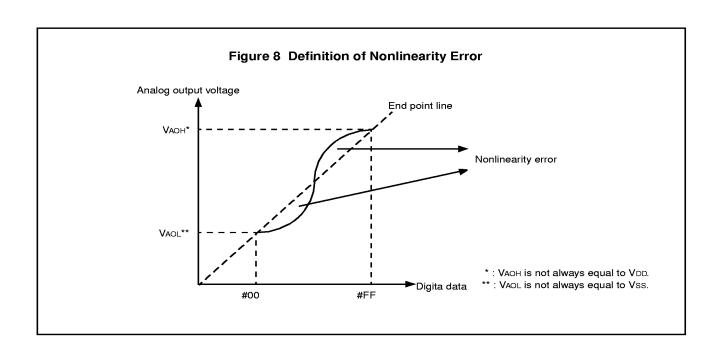

| Nonlinearity Error** (AOx)            | LE       | -1.5    | 0     | +1.5    | LSB  | Unloaded, VDD≤Vcc-0.1V, Vss≥0.1V, See Figure 8.         |  |

<sup>:</sup> The difference from the ideal increment value when the digital data is increased by 1 bit.

<sup>\*:</sup> The difference between the input-output curve for the straight line (ideal line) that connects the output voltage of the channel when #00 is set, and the output voltage when #FF is set.

#### **■ AC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted.)

| Downston                 | Comple of | Va  | lue | 11   | 0 1                                                 |  |

|--------------------------|-----------|-----|-----|------|-----------------------------------------------------|--|

| Parameter                | Symbol    | Min | Max | Unit | Condition                                           |  |

| Clock Low Time           | tclk      | 200 | -   | ns   |                                                     |  |

| Clock High Time          | tckH      | 200 | -   | ns   |                                                     |  |

| Clock Rise Time          | tCr       | -   | 200 | ns   |                                                     |  |

| Clock Fall Time          | tCf       | -   | 200 | ns   |                                                     |  |

| Data Setup Time          | tDCH      | 30  | -   | ns   |                                                     |  |

| Data Hold Time           | tCHD      | 60  | -   | ns   |                                                     |  |

| Load Strobe High Time    | tLDH      | 100 | -   | ns   |                                                     |  |

| Load Strobe Setup Time   | tCHL      | 200 | -   | ns   |                                                     |  |

| Load Strobe Hold Time    | tLDC      | 100 | -   | ns   |                                                     |  |

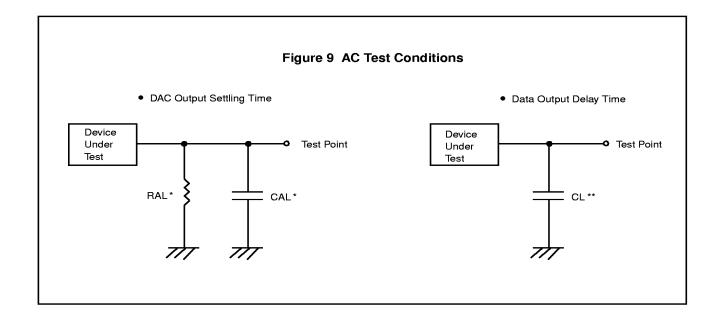

| DAC Output Settling Time | tLDD      | -   | 20  | μs   | *Ral = $10 \text{ k}\Omega$ , Cal = $50 \text{ pF}$ |  |

| Data Output Delay Time   | tDO       | 70  | 350 | ns   | **CL = 20 pF (Min.), 100 pF (Max.)                  |  |

## ■ PACKAGE DIMENSIONS MB88346B-P

#### MB88346B-PF

ma Pen

#### **MB88346B-PFV**