# 捷多邦,专业PCB打样工Prehiminary

# HD153110 Color Palette with Triple 8-bit DA Converter

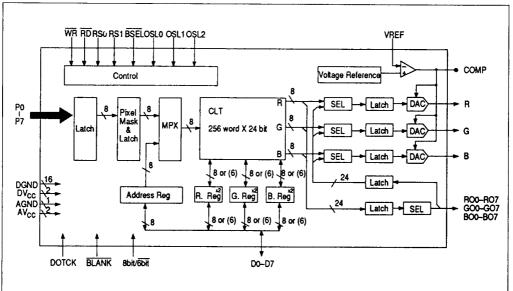

The HD153110FS is a color palette with built-in triple 8-bit DA converter. Manufactured with Hitachi's Hi-BiCMOS process, this LSI realizes high speed, high density, low power consumption and minimizes the need for externally connected parts. Also, in addition to applications for existing CRTs, the provision of digital R, G and B outputs for color LCD ensure that the HD153110FS can easily accomodate future systems using full-color LCD. With color palette, advanced functions, small size and low cost, the HD153110FS is an essential component for advanced graphics systems.

### **Ordering Information**

| Туре №.       | Max.<br>Operating Freq. | Package        |

|---------------|-------------------------|----------------|

| HD153110FS    | 50 MHz                  | 80 pin plastic |

| HD153110FS-65 | 65 MHz                  | QFP (FP-80B)   |

### Features

- Displays 256 colors simultaneously from a total of 16,777,216 possible colors.

- Three 8-bit DA converters for RGB video ouput on a single chip

- Read mask function for display control

- Compatible with VGA\* graphics standard

- For each pixel, dynamic switching between 16,777,216-color simultaneous display mode and normal mode

- In addition to existing CRT applications, direct digital RGB outputs from the color lookup table (CLT) are provided for color LCD applications.

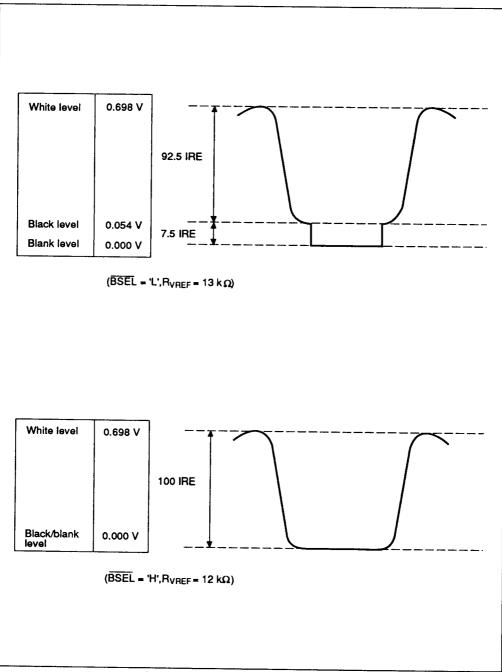

- Variable BLACK level (0 or 7.5 IRE)

- Switchable between 8-bit/6-bit mode; supports both 8-bit and 6-bit software.

- Dot rate maximum of 50/65 MHz

- TTL compatible I/O levels

- 28-pin DIP package

Note: VGA is a registered trademark of IBM.

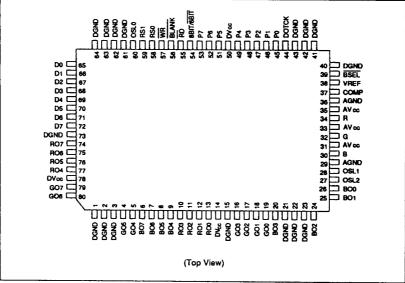

### **Pin Arrangement**

Figure 1

### **Block Diagram**

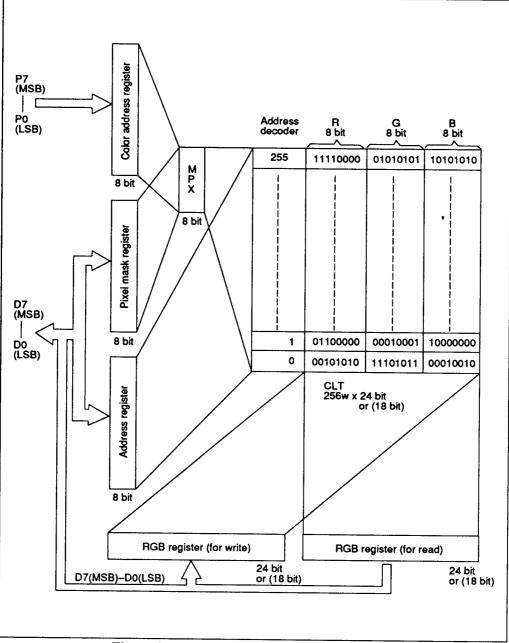

### Figure 2 Block Diagram

| Pin Name                                    | Pin Number                                                               | Description                                                                                                                                                        |

|---------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0 to P7                                    | 45 to 49, 51 to 53                                                       | CLT address inputs. P7 is MSB, P0 is LSB.                                                                                                                          |

| D0 to D7                                    | 65 to 72                                                                 | Data port for reading/writing CLT or address, pixel mask, R, G and B registers. D7 is MSB, D0 is LSB.                                                              |

| RD                                          | 55                                                                       | Read clock input. Strobes data from CLT or address, pixel mask, R, G or B registers during read operation.                                                         |

| WR                                          | 57                                                                       | Write clock input. Strobes data to CLT or address, pixel mask, R, G or B registers during write operation.                                                         |

| RS0, RS1                                    | 58, 59                                                                   | Select inputs for CLT, address register or pixel mask register                                                                                                     |

| RO0 to<br>RO7<br>GO0 to GO<br>BO0 to<br>BO7 | 13 to 10, 77 to 74<br>7 19 to 16, 4, 5, 79, 80<br>26 to 24, 20<br>9 to 6 | Palette (CLT) digital signal outputs. RO7, GO7 and BO7 are the MSBs and RO0, GO0, and BO0 are the LSBs.                                                            |

| VREF                                        | 38                                                                       | Terminal for connecting reference resistor to set DAC analog output level                                                                                          |

| СОМР                                        | 37                                                                       | Terminal for connecting a phase-compensation capacitor                                                                                                             |

| OSL0,<br>OSL1,<br>OSL2                      | 60, 28, 27                                                               | Select inputs for digital signal outputs                                                                                                                           |

| R, G, B                                     | 34, 32, 30                                                               | DAC analog signal outputs                                                                                                                                          |

| BLANK                                       | 56                                                                       | Video blank input for activating blank signal levels at DAC analog outputs                                                                                         |

| 8BIT/6BIT                                   | 54                                                                       | Inputs for setting color palette resolution. 'H' for an 8-bit palette, 'L' for a 6-bit palette                                                                     |

| BSEL                                        | 39                                                                       | Input for selecting DAC BLANK level (0 or 7.5 IRE)                                                                                                                 |

| DOTCK                                       | 44                                                                       | Reference clock input for digital and analog sections. On the rise of this signal, CLT and BLANK operations are processed and analog signal outputs become active. |

| DVcc                                        | 14, 50, 78                                                               | Digital power supply                                                                                                                                               |

| DGND                                        | 1 to 3, 15,<br>21 to 23, 40 to 43,<br>61 to 64, 73                       | Digital GND                                                                                                                                                        |

| AV <sub>CC</sub>                            | 31, 33, 35                                                               | Analog power supply                                                                                                                                                |

| AGND                                        | 29, 36                                                                   | Analog GND                                                                                                                                                         |

aobi

477

### Functions

#### Accessing the CLT and Registers

The CLT and registers are selected with inputs RS0 and RS1 (see Table 2).

### Registers

Address Register: To perform read/write operations on the CLT, the CLT address must be set in the address register through D7 to D0 (D7 is the MSB and D0 is the LSB).

For a CLT write operation, write the CLT address via D7 to D0 with RS0 = '0' and RS1 = '0' (in order to select the address register, write mode).

To set up the address register for a CLT read operation, write the CLT address via D7 to D0 with RS0 = '1' and RS1 = '1' (in order to select the address register, read mode).

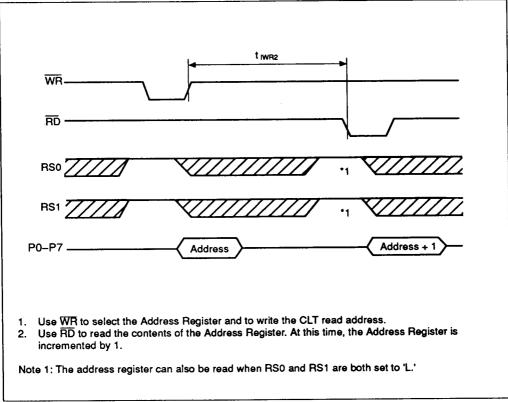

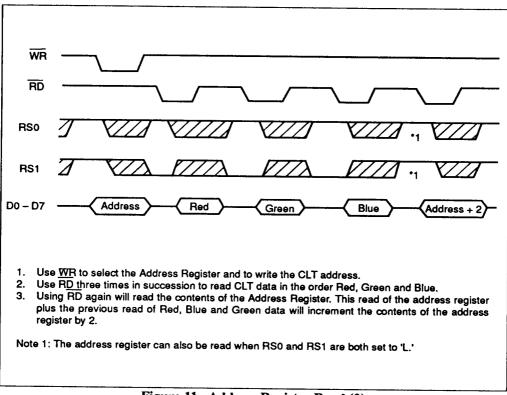

Also, the address register contents can be read as shown in figure 10 and figure 11.

**Pixel Mask Register:** The pixel mask register is used when displayed colors to be modified by altering the value input from video memory and the contents of the CLT. The pixel mask register is set by writing a pixel mask value to D7 (MSB) to D0(LSB) with RS0 = '0' and RS1 = '1' (in order to select the pixel mask register for a data write) as shown in figure 13. During color palette operations, the value input from video memory at P7 (MSB) to P0(LSB) is ANDed with the pixel mask register value, and the resulting value is applied as an address to the CLT. Consequently, pixel mask '0' bits will cancel corresponding video memory value '1' bits. The following table shows the CLT address that is generated for a particular pixel mask register value and video memory value.

**RGB Registers:** There are two RGB register types: one for writing color information to the CLT and one for reading color information from the CLT. Each register type is organized as an 24-bit word.

To read or write data to the CLT, set RS0 = '1' and RS1 = '0' to select the appropriate RGB register while performing the read or write via data port D7 (MSB) to D0 (LSB). Write or read the data in the order of R, G, B as shown in figure 7 and figure 8.

| Table | 2 | Register | Selection |

|-------|---|----------|-----------|

|-------|---|----------|-----------|

| RS1 | RS0 | Selection                     |  |  |  |  |

|-----|-----|-------------------------------|--|--|--|--|

| 0   | 0   | Address register (write mode) |  |  |  |  |

| 1   | 1   | Address register (read mode)  |  |  |  |  |

| 0   | 1   | CLT                           |  |  |  |  |

| 1   | 0   | Pixel mask register           |  |  |  |  |

#### Table 3 Pixel Mask Example

|                          | MSB |     |     |     |     |     |     | LSB |

|--------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Pixel mask register      | 1   | 0   | 1   | 0   | 1   | 1   | 0   | 1   |

| Address input (P7 to P0) | Pd7 | Pd6 | Pd5 | Pd4 | Pd3 | Pd2 | Pd1 | Pd0 |

| CLT address value        | Pd7 | 0   | Pd5 | 0   | Pd3 | Pd2 | 0   | Pd0 |

#### **OHITACHI** Chi Plaza • 2000 Sierra Point Pkwy • Brishane CA 94005-1819 • (415) 589-8300 479

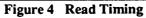

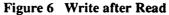

Figure 5 Read after Write

Figure 7 CLT Write

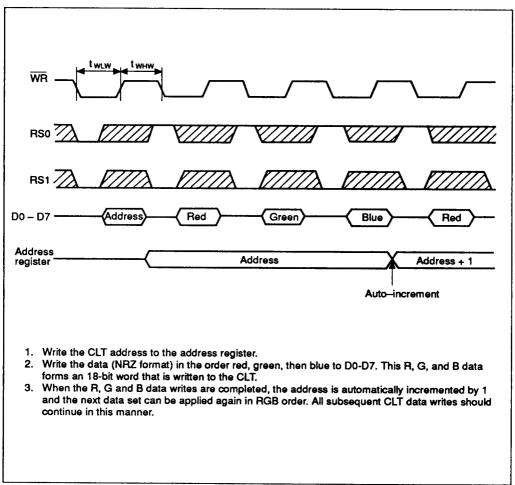

Figure 8 CLT Read

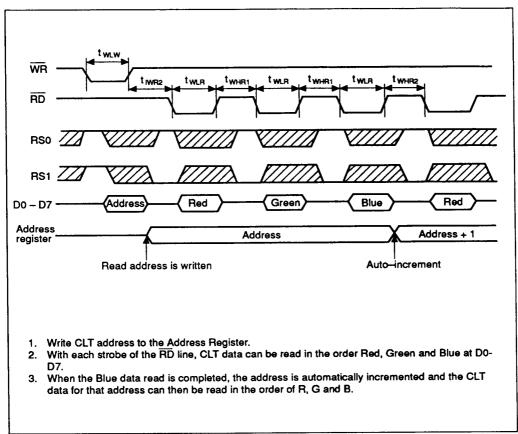

Figure 9 Video Output

Figure 10 Address Register Read (1)

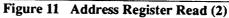

# Figure 12 Digital Output

Figure 13 Pixel Mask Register Write

Figure 14 Pixel Mask Register Read

# **(415) (415) (415) (415) (415)**

# Figure 15 Video Output Waveforms

C HITACHI itachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

### Mode Switching

HD153110 operating mode is switched as shown below. (8 bit/6bit='H') When the 8 bit/6bit terminal is 'L' a 6-bit color palette can be used; when in 24-bit digital output mode, the digital outputs will be on the upper six bits of each 8-bit word and the lower two bits will be set 'L.'

| Table 4 | Mode | Switching |

|---------|------|-----------|

|---------|------|-----------|

| OSL2 | OSL1 | OSL0 | Operating Mode                                                     | Notes |

|------|------|------|--------------------------------------------------------------------|-------|

| L    | L    | L    | DAC output mode                                                    | 1     |

| L    | L    | Н    | DAC direct Input (16,777,216-color simultaneous display mode)      | 1     |

| L    | н    | L    | Digital output 12-bit mode (R, G and B are output on upper 4 bits) | 2     |

| L    | н    | Н    | Prohibited (Digital output 24-bit mode)                            | 3     |

| Н    | L    | L    | Digital output 6-bit mode (Green output only)                      | 2     |

| Н    | L    | н    | Prohibited                                                         |       |

| Н    | н    | L    | Digital output 24-bit mode                                         | 2     |

| н    | н    | н    | Prohibited                                                         |       |

Notes: 1. Digital output is Hi-Z.

2. DAC outputs are off.

3. Both Digital and DAC outputs are active.

### **Register Correspondence with CLT**

# Figure 16 Register Correspondence with CLT

Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

2

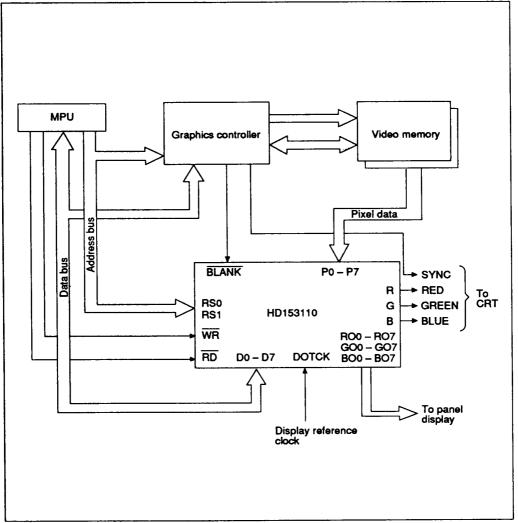

### System Configuration Example

Figure 17 System Configuration Example

### Table 5 Absolute Maximum Ratings

| Symbol           | Rating                                                 | Unit                                                                                       |

|------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------|

| V <sub>CC</sub>  | 7.0                                                    | v                                                                                          |

| V <sub>IN</sub>  | 0 to VCC                                               | v                                                                                          |

| T <sub>opr</sub> | 0 to +70                                               | °C                                                                                         |

| T <sub>stg</sub> | - 55 to +150                                           | °C                                                                                         |

|                  | V <sub>CC</sub><br>V <sub>IN</sub><br>T <sub>opr</sub> | V <sub>CC</sub> 7.0           V <sub>IN</sub> 0 to VCC           T <sub>opr</sub> 0 to +70 |

# **Electrical Characteristics**

| Table 6 DAC Section Electrical Characteristics ( $V_{cc} = 5 V$ , $Ta = 25 °C$ |

|--------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------|

| ltem                           | Symbol                | Min   | Тур   | Мах   | Unit     | Test Conditions        |

|--------------------------------|-----------------------|-------|-------|-------|----------|------------------------|

| Resolution                     |                       | 8 (6) | 8 (6) | 8 (6) | bits     |                        |

| Maximum operating frequency    | fCLK                  |       |       | 50/65 | MHz      |                        |

| Analog output voltage          | V <sub>A</sub> (Full) | -15   | _     | 15    | % of FSR |                        |

| $(R_{VREF} = 12 k\Omega)$      | V <sub>A</sub> (Zero) | 2     | _     | 2     | % of FSR |                        |

| Differential linearity         | DLE                   | -1    |       | +1    | LSB      |                        |

| Integral linearity             | ILE                   | -1    |       | +1    | LSB      |                        |

| Output rise time<br>(20 – 80%) | t <sub>r</sub>        |       | _     | 10    | ns       | C <sub>L</sub> = 15 pF |

| Output fall time<br>(80 – 20%) | t <sub>f</sub>        | _     |       | 10    | ns       | C <sub>L</sub> = 15 pF |

| Settling time                  | ts                    |       |       | 30    | ns       | C <sub>1</sub> = 15 pF |

| Glitch energy                  | EG                    | _     | 90    |       | PVS      |                        |

( ) indicates 6-bit mode.

# Table 7 Digital Section DC Characteristics

| (unless otherwise specified | V <sub>CC</sub> = 5 V ± | 5 %: Ta = 0 to +70 °C) |

|-----------------------------|-------------------------|------------------------|

|-----------------------------|-------------------------|------------------------|

| Item                       | Symbol | Min  | Тур | Max             | Unit | Test Conditions                                      | Notes |

|----------------------------|--------|------|-----|-----------------|------|------------------------------------------------------|-------|

| Input "High" level voltage | VIH    | 2.0  |     | V <sub>CC</sub> | V    |                                                      |       |

| Input "Low" level voltage  | VIL    | -0.3 | _   | 0.8             | V    |                                                      |       |

| Input clamp voltage        | VI     | _    |     | 1.5             | V    | V <sub>CC</sub> = 4.75 V<br>I <sub>IN</sub> = -18 mA |       |

4

### **Digital Section DC Characteristics**

(unless otherwise specified  $V_{CC} = 5 V \pm 5 \%$ : Ta = 0 to +70 °C) (cont)

| <b></b>                        | 00                  |     |     |      |      |                                                     |       |

|--------------------------------|---------------------|-----|-----|------|------|-----------------------------------------------------|-------|

| tem                            | Symbol              | Min | Тур | Max  | Unit | Test Conditions                                     | Notes |

| Output "High" level<br>voltage | VOH                 | 2.7 | _   | _    | V    | V <sub>CC</sub> = 4.75 V<br>I <sub>OH</sub> =400 μA |       |

| Output "Low" level voltage     | VOL                 |     | -   | 0.5  | V    | V <sub>CC</sub> = 4.75 V<br>I <sub>OL</sub> = 8 mA  |       |

| Input current                  | η                   |     |     | 1    | mA   | V <sub>CC</sub> = 5.25 V<br>V <sub>I</sub> = 5.5 V  |       |

| "High" level input<br>current  | lιΗ                 | _   |     | 20   | μA   | V <sub>CC</sub> = 5.25 V<br>V <sub>1</sub> = 2.7 V  |       |

| "Low" level input current      | μ                   | _   |     | -400 | μA   | V <sub>CC</sub> = 5.25 V<br>V <sub>I</sub> = 0.4 V  |       |

| Supply current (1)             | Icc (1)             | -   | 130 | 190  | mA   | V <sub>CC</sub> = 5.25 V                            | 1     |

| Supply current (2)             | I <sub>CC</sub> (2) | _   | 110 | 160  | mA   | V <sub>CC</sub> = 5.25                              | 2     |

Notes: 1. OSL0 = 'L', OSL1 ='L', OSL2 ='L'

2. OSL0 ='L', OSL1 = 'H', OSL2 = 'H'

# Table 8 Digital Section AC Characteristics ( $V_{CC} = 5 V$ , Ta = 25 °C)

| Item                    | Symbol             | 50 MHz             |     | 65 MHz             |     |      |                       | Reference  |

|-------------------------|--------------------|--------------------|-----|--------------------|-----|------|-----------------------|------------|

|                         |                    | Min                | Max | Min                | Max | Unit | Remarks               | Figure     |

| DOTCK cycle time        | tDCK               | 20                 | -   | 15.3               | _   | ns   |                       | 9          |

| DOTCK low level time    | <sup>t</sup> WLDCK | 8                  |     | 6                  |     | ns   |                       | 9          |

| DOTCK high level time   | <sup>t</sup> WHDCK | 8                  | _   | 6                  | _   | ns   |                       | 9          |

| Data setup time         | t <sub>sp</sub>    | 6                  |     | 5                  | _   | ns   |                       | 9          |

| Data hold time          | ţНЬ                | 6                  |     | 5                  | _   | ns   |                       | 9          |

| Data output delay time  | t <sub>PDA</sub>   | _                  | 30  | _                  | 30  | ns   | C <sub>L</sub> =15 pF | 9          |

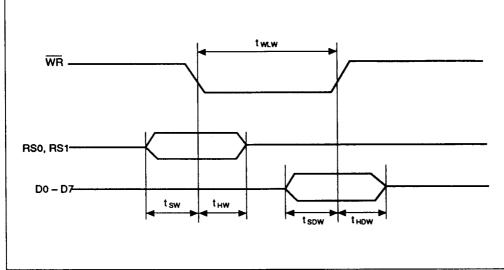

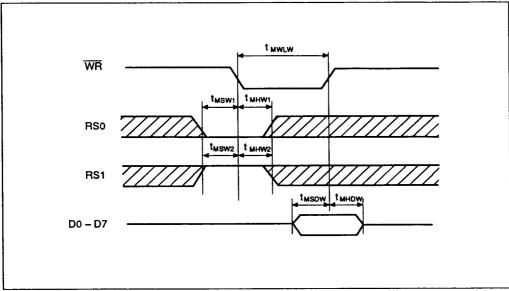

| WR low level time       | twLw               | 50                 |     | 50                 |     | ns   |                       | 3, 7, 8    |

| WR high level time      | twnw               | 3×t <sub>DCK</sub> | _   | 3×t <sub>DCK</sub> |     | ns   |                       | 7          |

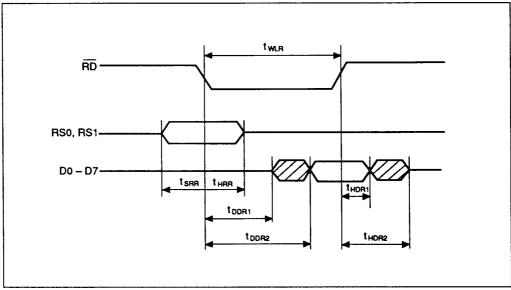

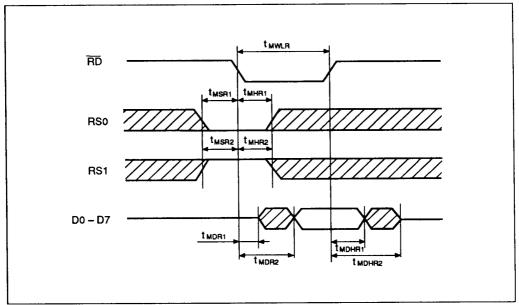

| RD low level time       | <sup>t</sup> WLR   | 50                 |     | 50                 | _   | ΠS   |                       | 8          |

| RD high level time (1)  | twHR1              | 3×tDCK             | _   | 3×t <sub>DCK</sub> |     | ns   |                       | 8          |

| RD high level time (2)  | twhr2              | 6×t <sub>DCK</sub> | _   | 6×t <sub>DCK</sub> | _   | ns   |                       | 8          |

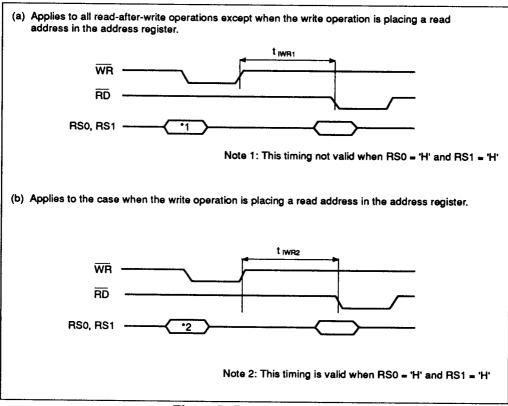

| WR/RD interval time (1) | tiwn1              | 3×t <sub>DCK</sub> |     | 3×t <sub>DCK</sub> | _   | ns   |                       | 5, 6       |

| WR/RD interval time (2) | tiwr2              | 6×tDCK             |     | 6×t <sub>DCK</sub> | _   | ns   |                       | 5, 6, 8, 9 |

### O HITACHI

| Item                          |                   | 50 MHz   |     | 65 MHz |     |      |                        | Reference |

|-------------------------------|-------------------|----------|-----|--------|-----|------|------------------------|-----------|

|                               | Symbol            | Min      | Max | Min    | Max | Unit | Remarks                | Figure    |

| WR/RS0, RS1 setup time        | tsw               | 10       |     | 10     |     | ns   |                        | 3         |

| WR/RS0, RS1 hold time         | 4HW               | 10       | _   | 10     | _   | ns   |                        | 3         |

| RD/RS0, RS1 setup time        | t <sub>SRR</sub>  | 10       | _   | 10     | _   | ns   |                        | 4         |

| RD/RS0, RS1 hold time         | <b>HRR</b>        | 10       |     | 10     | _   | ns   |                        | 4         |

| WR data setup time            | tsow              | 10       | -   | 10     | _   | ns   |                        | 3         |

| WR data hold time             | thow.             | 10       |     | 10     | _   | ns   |                        | 3         |

| RD data output delay time (1) | t <sub>DDR1</sub> | 5        | _   | 5      |     | ns   | C <sub>L</sub> = 15 pF | 4         |

| RD data output delay time (2) | tDDR2             |          | 40  |        | 40  | ns   | C <sub>L</sub>         | 4         |

| RD data output hold time (1)  | HDR1              | 5        |     | 5      | _   | ns   | C <sub>L</sub> =15 pF  | 4         |

| RD data output hold time (2)  | <sup>t</sup> HDR2 | <b>—</b> | 20  | _      | 20  | ns   | C <sub>L</sub> =15 pF  | 4         |

| Digital output delay time     | <sup>t</sup> PDO  | _        | 19  | -      | 19  | ns   | C <sub>L</sub> = 15 pF | 12        |

| WR low level time             | <sup>t</sup> MWLW | 50       |     | 50     | _   | ns   |                        | 13        |

| RD low level time             | <sup>t</sup> MWLR | 50       | _   | 50     |     | ns   |                        | 14        |

| WR/RS0, RS1 setup time        | t <sub>MSW1</sub> | 10       |     | 10     |     | ns   |                        | 13        |

|                               | 4MSW2             | 10       | _   | 10     |     | ns   |                        | 13        |

| WR/RS0, RS1 hold time         |                   | 10       |     | 10     | -   | ns   |                        | 13        |

|                               | tMHW2             | 10       | _   | 10     |     | ns   |                        | 13        |

| RD/RS0, RS1 setup time        | tMSR1             | 10       |     | 10     |     | ns   |                        | 14        |

|                               | tMSR2             | 10       | _   | 10     | _   | ns   |                        | 14        |

| RD/RS0, RS1 hold time         |                   | 10       | -   | 10     | -   | ns   |                        | 14        |

|                               | tMHR2             | 10       |     | 10     | _   | ns   |                        | 14        |

| WR data setup time            | <sup>t</sup> MSDW | 10       | _   | 10     | _   | ns   |                        | 13        |

| WR data hold time             | <sup>t</sup> MHDW | 10       | -   | 10     | _   | ns   |                        | 13        |

# Digital Section AC Characteristics (V<sub>CC</sub> = 5 V, Ta = 25 °C) (cont)

| item                         | Symbol             | 50 MHz |     | 65 MHz |     |      |                        | Reference |

|------------------------------|--------------------|--------|-----|--------|-----|------|------------------------|-----------|

|                              |                    | Min    | Max | Min    | Max | Unit | Remarks                | Figure    |

| RD data output delay<br>time | IMDR1              | 5      |     | 5      |     | ns   | C <sub>L</sub> = 15 pF | 14        |

|                              | tMDR2              |        | 40  |        | 40  | ns   | C <sub>L</sub> = 15 pF | 14        |

| RD data output hold time     | tMDHR1             | 5      | _   | 5      | -   | ns   | C <sub>L</sub> = 15 pF | 14        |

|                              | t <sub>MDHR2</sub> | _      | 20  |        | 20  | ns   | C <sub>L</sub> = 15 pF | 14        |

### Digital Section AC Characteristics (V<sub>CC</sub> = 5 V, Ta = 25 °C) (cont)

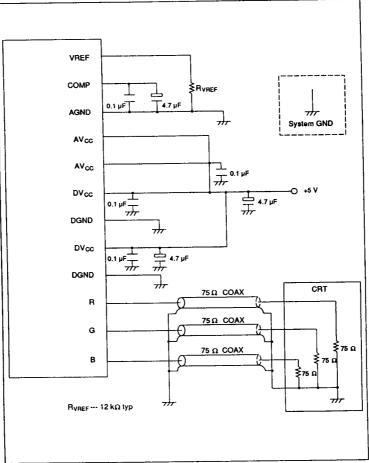

### Figure 18 Connection Example