# **YSS932**

# AC3D3B

96kHz DIR + Dolby Digital / Pro Logic II / DTS decoder + Sub DSP

## OUTLINE

YSS932 is one chip LSI consisting of three built-in blocks: SPDIF receiver (DIR), Dolby Digital (AC-3) / Pro Logic II & DTS decoder (Main DSP) and programmable sound fields processing DSP (Sub DSP).

The Sub DSP is capable of realizing various sound fields, such as virtual surround by down-loading the program and coefficient from outside.

## **■** FEATURES

#### [ DIR Block ]

- Sampling frequency: Two ranges are available including; 32k to 48kHz (normal rate) and 64k to 96kHz (double rate).

- Provides master clock, 256fs, to DAC, ADC and the other peripheral devices. The clock output can be controlled with various modes determined by register settings.

- Has a pin that indicates the double rate operation.

- Every channel status and user data can be read through the microprocessor interface.

- Has an output pin for interrupt that is activated by changing of the status information.

- Internal operation frequency: 25MHz

#### [ Main DSP Block ]

- Dolby Digital (AC-3) / Pro Logic II and DTS decode.

- High quality internal 24 bit DSP.

- No external memory is required. (Memory for the center and surround channel signal delay is included.)

- AC-3 Karaoke mode.

- Supports compression mode at AC-3 / DTS decoding.

- Included de-emphasis filter for the PCM signal.

- Pro Logic II decoding for Dolby Digital 2 channels decoded signal as well as ordinary PCM signal.

- Reads Dolby Digital / DTS decode information through the microprocessor interface.

- Internal operation frequency: 30MHz

YAMAHA CORPORATION

## [ Sub DSP Block ]

- Capable of realizing various sound fields, such as simulation surround, output configuration and virtual surround by downloading the programs from the microprocessor.

- Adoption of the 32 bit floating-point DSP assuring highly accurate processing.

- Up to 2.73 seconds delay at fs=48kHz achievable by adding DRAM or SRAM externally.

- Internal operation frequency: 30MHz

### [Other Features]

- Connectable to almost all ADC and DAC by making appropriate settings to the control register.

- Total of 16 general purpose input/output ports are provided.

- 2 built-in PLL circuits for generation of operation clocks for DIR block and DSP blocks.

- Power supply voltage: 2 power sources (2.5V for core logic section and 3.3V for I/O section)

- Si-gate CMOS process

- 128SQFP (YSS932-S)

Note: "AC-3" and "Pro Logic II" are registered trademarks of Dolby Laboratories Licensing corporation.

"DTS" is a registered trademark of DTS, Inc.

Use of this LSI must be licensed by both Dolby Laboratories Licensing Corporation and DTS, Inc.

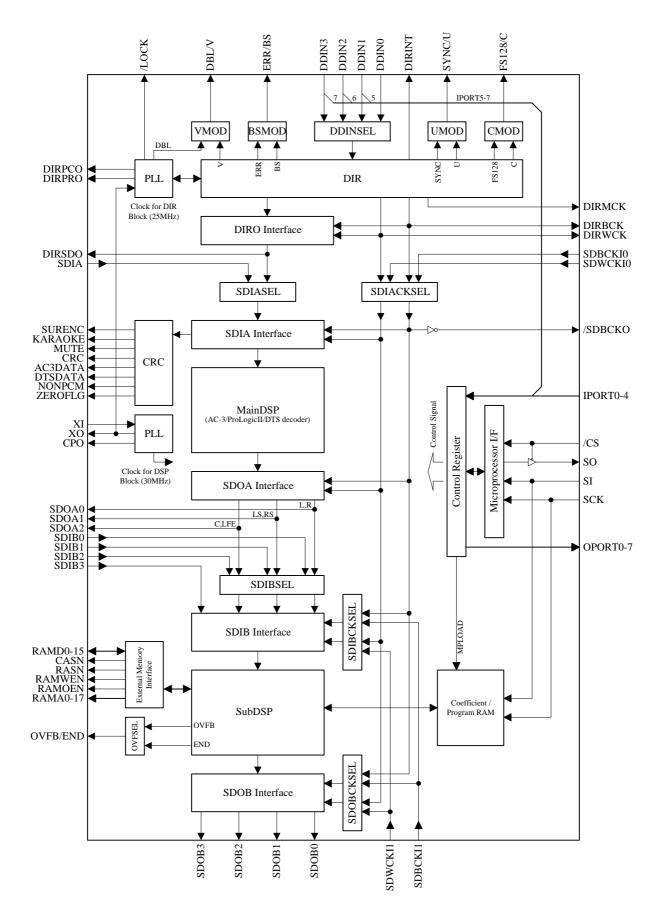

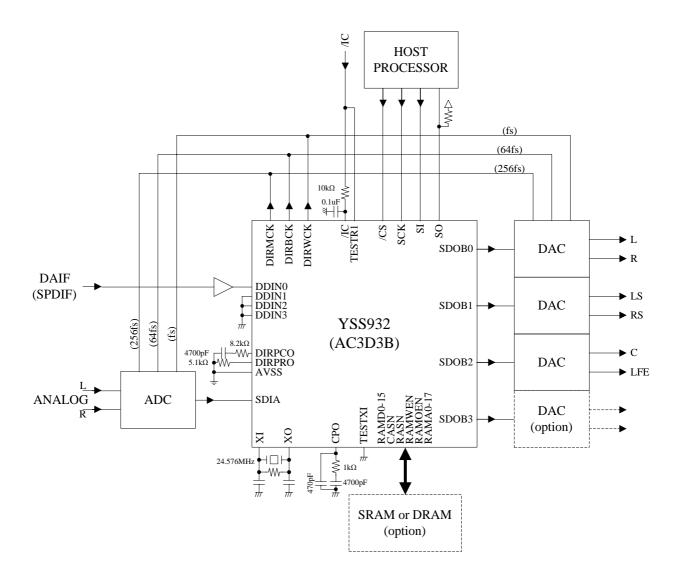

## **■ BLOCK DIAGRAM**

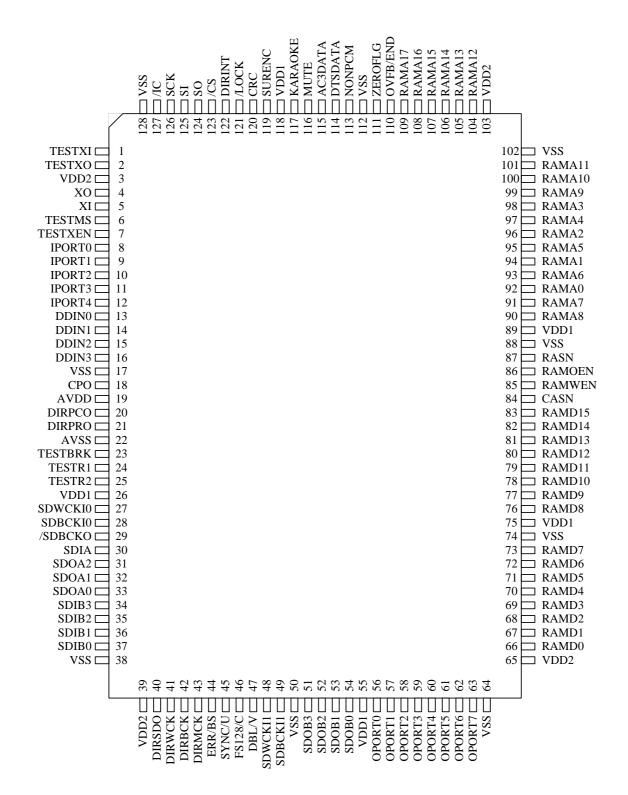

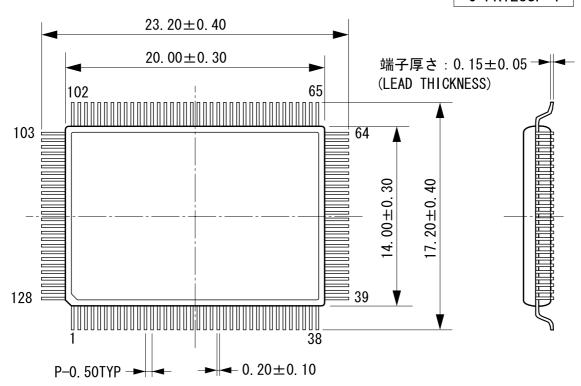

#### **■ PIN CONFIGRATION**

< 128SQFP TOP VIEW >

# **■ PIN FUNCTION**

| No. | Name    | I/O | Function                                                               |

|-----|---------|-----|------------------------------------------------------------------------|

| 1   | TESTXI  | I   | LSI Test pin (must be connected to VSS)                                |

| 2   | TESTXO  | 0   | LSI Test pin (to be open)                                              |

| 3   | VDD2    | -   | +2.5V power supply (for internal core logic)                           |

| 4   | XO      | 0   | Crystal oscillator connection                                          |

| 5   | ΧI      | I   | Crystal oscillator connection (24.576MHz)                              |

| 6   | TESTMS  | l+  | LSI Test pin (to be open)                                              |

| 7   | TESTXEN | l+  | LSI Test pin (to be open)                                              |

| 8   | IPORT0  | l+  | General purpose input port                                             |

| 9   | IPORT1  | l+  | General purpose input port                                             |

| 10  | IPORT2  | l+  | General purpose input port                                             |

| 11  | IPORT3  | l+  | General purpose input port                                             |

| 12  | IPORT4  | l+  | General purpose input port                                             |

| 13  | DDIN0   | ls  | DIR: Digital audio interface data input 0                              |

| 14  | DDIN1   | ls  | DIR: Digital audio interface data input 1 / General purpose input port |

| 15  | DDIN2   | ls  | DIR: Digital audio interface data input 2 / General purpose input port |

| 16  | DDIN3   | ls  | DIR: Digital audio interface data input 3 / General purpose input port |

| 17  | VSS     |     | Ground                                                                 |

| 18  | CPO     | Α   | PLL filter connection                                                  |

| 19  | AVDD    | -   | +3.3V power supply (for DIR block)                                     |

| 20  | DIRPCO  | Α   | DIR: PLL filter connection                                             |

| 21  | DIRPRO  | Α   | DIR: PLL filter connection                                             |

| 22  | AVSS    | -   | Ground (for DIR block)                                                 |

| 23  | TESTBRK | l+  | LSI Test pin (to be open)                                              |

| 24  | TESTR1  | l+  | Initial Clear input for PLL in DSP block                               |

| 25  | TESTR2  | l+  | LSI Test pin (to be open)                                              |

| 26  | VDD1    | -   | +3.3V power supply (for I/O)                                           |

| 27  | SDWCKI0 | l+  | Word clock input for SDIA, SDOA, SDIB, SDOB                            |

| 28  | SDBCKI0 | l+  | Bit clock input for SDIA, SDOA, SDIB, SDOB                             |

| 29  | /SDBCKO | 0   | Reverse clock output of DIRBCK or SDBCKI0                              |

| 30  | SDIA    | 1   | Input of bitstream or PCM data to Main DSP                             |

| 31  | SDOA2   | 0   | PCM data output from Main DSP (C, LFE)                                 |

| 32  | SDOA1   | 0   | PCM data output from Main DSP (LS, RS)                                 |

| 33  | SDOA0   | 0   | PCM data output from Main DSP (L, R)                                   |

| 34  | SDIB3   | l+  | PCM data input 3 to Sub DSP                                            |

| 35  | SDIB2   | l+  | PCM data input 2 to Sub DSP                                            |

| 36  | SDIB1   | l+  | PCM data input 1 to Sub DSP                                            |

| 37  | SDIB0   | l+  | PCM data input 0 to Sub DSP                                            |

| 38  | VSS     | -   | Ground                                                                 |

| 39  | VDD2    | -   | +2.5V power supply (for internal core logic)                           |

| 40  | DIRSDO  | 0   | Output of bitstream or PCM data from DIR                               |

| 41  | DIRWCK  | 0   | DIR: Serial data word clock (fs) output                                |

| 42  | DIRBCK  | 0   | DIR: Serial data bit clock (64fs) output                               |

| 43  | DIRMCK  | 0   | DIR: Serial data master clock (256fs or 128fs) output                  |

| 44  | ERR/BS  | 0   | DIR: Data error detect / Block start output                            |

| 45  | SYNC/U  | 0   | DIR: Serial data synchronized timing / User data output                |

| 46  | FS128/C | 0   | DIR: Serial data master clock 128fs / Channel status output            |

| 47  | DBL/V   | 0   | DIR: Double rate lock detect / Validity flag output                    |

| 48  | SDWCKI1 | l+  | Word clock input for SDIB, SDOB                                        |

| 49  | SDBCKI1 | l+  | Bit clock input for SDIB, SDOB                                         |

| 50  | VSS     | -   | Ground                                                                 |

| 51  | SDOB3   | 0   | PCM data output from Sub DSP                                           |

| 52  | SDOB2   | 0   | PCM data output from Sub DSP                                           |

| 53  | SDOB1   | 0   | PCM data output from Sub DSP                                           |

| 54  | SDOB0   | 0   | PCM data output from Sub DSP                                           |

| 55  | VDD1    | -   | +3.3v power supply (for I/O)                                           |

| No.        | Name             | I/O  | Function                                                                                     |

|------------|------------------|------|----------------------------------------------------------------------------------------------|

| 56         | OPORT0           | 0    | General purpose output port                                                                  |

| 57         | OPORT1           | 0    | General purpose output port                                                                  |

| 58         | OPORT2           | 0    | General purpose output port                                                                  |

| 59         | OPORT3           | 0    | General purpose output port                                                                  |

| 60         | OPORT4           | 0    | General purpose output port                                                                  |

| 61         | OPORT5           | 0    | General purpose output port                                                                  |

| 62         | OPORT6           | 0    | General purpose output port                                                                  |

| 63         | OPORT7           | 0    | General purpose output port                                                                  |

| 64         | VSS              | -    | Ground                                                                                       |

| 65         | VDD2             | -    | +2.5V power supply (for internal core logic)                                                 |

| 66         | RAMD0            | I+/O | Sub DSP: External memory interface Data 0                                                    |

| 67         | RAMD1            | I+/O | Sub DSP: External memory interface Data 1                                                    |

| 68         | RAMD2            | I+/O | Sub DSP: External memory interface Data 2                                                    |

| 69         | RAMD3            | I+/O | Sub DSP: External memory interface Data 3                                                    |

| 70         | RAMD4            | I+/O | Sub DSP: External memory interface Data 4                                                    |

| 71         | RAMD5            | I+/O | Sub DSP: External memory interface Data 5                                                    |

| 72         | RAMD6            | I+/O | Sub DSP: External memory interface Data 6                                                    |

| 73         | RAMD7            | I+/O | Sub DSP: External memory interface Data 7                                                    |

| 74         | VSS              | -    | Ground                                                                                       |

| 75         | VDD1             | -    | +3.3V power supply (for I/O)                                                                 |

| 76         | RAMD8            | I+/O | Sub DSP: External memory interface Data 8                                                    |

| 77         | RAMD9            | I+/O | Sub DSP: External memory interface Data 9                                                    |

| 78         | RAMD10           | I+/O | Sub DSP: External memory interface Data 10                                                   |

| 79         | RAMD11           | I+/O | Sub DSP: External memory interface Data 11                                                   |

| 80         | RAMD12           | I+/O | Sub DSP: External memory interface Data 12                                                   |

| 81         | RAMD13           | I+/O | Sub DSP: External memory interface Data 13                                                   |

| 82         | RAMD14           | I+/O | Sub DSP: External memory interface Data 14                                                   |

| 83         | RAMD15           | I+/O | Sub DSP: External memory interface Data 15                                                   |

| 84         | CASN             | 0    | Sub DSP: External DRAM interface Column address strobe output                                |

| 85         | RAMWEN           | 0    | Sub DSP: External memory interface Write enable output                                       |

| 86         | RAMOEN           | 0    | Sub DSP: External memory interface Output enable output                                      |

| 87         | RASN             | 0    | Sub DSP: External DRAM interface Row address strobe output                                   |

| 88         | VSS              | -    | Ground                                                                                       |

| 89         | VDD1             | -    | +3.3V power supply (for I/O)                                                                 |

| 90         | RAMA8            | 0    | Sub DSP: External memory interface Address 8                                                 |

| 91         | RAMA7            | 0    | Sub DSP: External memory interface Address 7                                                 |

| 92         | RAMA0            | 0    | Sub DSP: External memory interface Address 0                                                 |

| 93         | RAMA6            | 0    | Sub DSP: External memory interface Address 6                                                 |

| 94         | RAMA1            | 0    | Sub DSP: External memory interface Address 1                                                 |

| 95         | RAMA5            | 0    | Sub DSP: External memory interface Address 5                                                 |

| 96         | RAMA2            | 0    | Sub DSP: External memory interface Address 2                                                 |

| 97         | RAMA4            | 0    | Sub DSP: External memory interface Address 4                                                 |

| 98         | RAMA3            | 0    | Sub DSP: External memory interface Address 3                                                 |

| 99         | RAMA9            | 0    | Sub DSP: External memory interface Address 9                                                 |

| 100        | RAMA10           | 0    | Sub DSP: External memory interface Address 10                                                |

| 101        | RAMA11           | 0    | Sub DSP: External memory interface Address 11                                                |

| 102        | VSS              | -    | Ground                                                                                       |

| 103        | VDD2             | - (  | +2.5V power supply (for internal core logic) Sub DSP: External memory interface Address 12   |

| 104<br>105 | RAMA12<br>RAMA13 | 0 0  | Sub DSP: External memory interface Address 12 Sub DSP: External memory interface Address 13  |

| 105        | RAMA14           | 0    | Sub DSP: External memory interface Address 15 Sub DSP: External memory interface Address 14  |

| 106        | RAMA15           | 0    | Sub DSP: External memory interface Address 14  Sub DSP: External memory interface Address 15 |

| 107        | RAMA16           | 0    | Sub DSP: External memory interface Address 15 Sub DSP: External memory interface Address 16  |

| 109        | RAMA17           | 0    | Sub DSP: External memory interface Address 17  Sub DSP: External memory interface Address 17 |

|            | OVFB/END         | 0    | Sub DSP: Overflow / Program end detect                                                       |

| No. | Name    | I/O | Function                                                   |  |  |  |  |  |

|-----|---------|-----|------------------------------------------------------------|--|--|--|--|--|

| 111 | ZEROFLG | 0   | Iain DSP: Zero flag output                                 |  |  |  |  |  |

| 112 | VSS     | -   | Fround                                                     |  |  |  |  |  |

| 113 | NONPCM  | 0   | Main DSP: non-PCM data detect                              |  |  |  |  |  |

| 114 | DTSDATA | 0   | Main DSP: DTS data detect                                  |  |  |  |  |  |

| 115 | AC3DATA | 0   | Main DSP: AC-3 data detect                                 |  |  |  |  |  |

| 116 | MUTE    | 0   | Main DSP: Auto mute detect                                 |  |  |  |  |  |

| 117 | KARAOKE | 0   | Main DSP: AC-3 Karaoke data detect                         |  |  |  |  |  |

| 118 | VDD1    | -   | +3.3V power supply (for I/O)                               |  |  |  |  |  |

| 119 | SURENC  | 0   | Main DSP: AC-3 2/0 mode Dolby Surround Encode input detect |  |  |  |  |  |

| 120 | CRC     | 0   | Main DSP: AC-3 CRC error detect                            |  |  |  |  |  |

| 121 | /LOCK   | 0   | DIR: PLL lock detect                                       |  |  |  |  |  |

| 122 | DIRINT  | 0   | DIR: interrupt output                                      |  |  |  |  |  |

| 123 | /CS     | Is  | Microprocessor interface Chip select input                 |  |  |  |  |  |

| 124 | SO      | Ot  | Microprocessor interface Data output                       |  |  |  |  |  |

| 125 | SI      | Is  | Microprocessor interface Data input                        |  |  |  |  |  |

| 126 | SCK     | ls  | Microprocessor interface Clock input                       |  |  |  |  |  |

| 127 | /IC     | ls  | Initial clear input                                        |  |  |  |  |  |

| 128 | VSS     | -   | Ground                                                     |  |  |  |  |  |

I : Input pin

Is: Schmitt trigger input pin

I+ : Input pin with a pull-up resistor

O: Output pin

Ot: Tri-state output pin

A : Analog pin

#### **■ FUNCTION DESCRIPTION**

YSS932 consists of three blocks; the Main DSP block where AC-3 / Pro Logic II / DTS decoding is executed, the Sub DSP block where various sound field effects are added and the SPDIF receiver (DIR) block.

The Sub DSP is a 8 channel input / 8 channel output programmable DSP exclusively for sound field processing. It can apply such effects as simulation surround, output configuration and virtual surround. In addition, with SRAM or DRAM connected, it can produce reverberation up to 2.73 seconds delay at fs=48kHz. By using this function, it is possible to simulate various sound fields such as a hall or a church.

The SPDIF receiver (DIR) can handle the digital audio interface format input signals of the sampling frequency 32kHz through 96kHz.

Note)

If adopting some technology owned by another company is desired for use in Sub DSP block, note that a separate contract may be required between the owner of that technology and the user with respect to adoption of the technology.

#### PIN DESCRIPTION

- 1) DIR Block

- 1-1) Digital audio interface signal input

#### DDIN0-3

Input digital audio interface format signal (DAIF signal) into these pins. Then the signal selected by control register DDINSEL0, 1 is input to the DIR block.

As the pull-up resistors are not built in, connect the unnecessary pins to VSS.

Also, DDIN1, 2, 3 are served as IPORT5, 6, 7. If they are not used as DDIN input pins, they are usable as general purpose input ports.

#### 1-2) Clock

#### DIRMCK

The master clock for such peripheral devices as DAC and ADC is output.

The operation mode of DIRMCK is selected according to the lock condition of PLL in the DIR block and settings for the control register. The DIRMCK output modes are as follows.

- When PLL in the DIR block is not locked (/LOCK=H) ----- (1) DIRMCK outputs 12.288MHz.

- When PLL in the DIR block is locked (/LOCK=L) and CKMOD=1 ---- (2) DIRMCK outputs 12.288MHz

- When PLL in the DIR block is locked (/LOCK=L) and CKMOD=0 DIRMCK outputs according to the setting of LOCKMOD1-0.

| LOCKMOD1 | LOCKMOD0 | Normal rate | Double rate    |

|----------|----------|-------------|----------------|

| 0        | 0        | 256fs       | 256fs          |

| 0        | 1        | 256fs       | 128fs          |

| 1        | *        | 256fs       | 12.288MHz -(3) |

The mode like the above (1), (2) and (3) in which the XI's divided clock of 12.288 MHz is output from DIRMCK is referred to as "free-run mode".

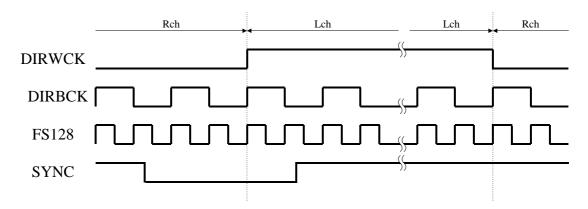

#### DIRBCK, DIRWCK, FS128, SYNC

The clock for such peripheral devices as DAC and ADC is output.

At CMOD=0 setting, FS128 is output from FS128/C pin and at UMOD=0 setting, SYNC is output from SYNC/U pin.

DIRBCK, DIRWCK and FS128 are obtained by dividing the clock of DIRMCK and the period of each clock is as follows.

DIRBCK  $\rightarrow$  64fs DIRWCK  $\rightarrow$  fs FS128  $\rightarrow$  128fs

SYNC is output according to the following timing.

Note) At settings of DIROWP=0, DIROBP=0

#### 1-3) Serial data output

#### DIRSDO

The DAIF signal data is output. The output is always 24-bit width including audio auxiliary bit. The data is output from the DIRSDO pin as well as goes into the Main DSP block through the SDIA interface.

It must be noted that the data output from the DIRSDO pin is muted during the free-run mode or at SDOMUTE=1 setting, but the data output to the Main DSP is muted only during the free-run mode regardless of SDOMUTE setting.

The output format can be selected by setting the DIR SDO register. For the details of the format, refer to "Serial Data Interface Format".

## 1-4) Status data output

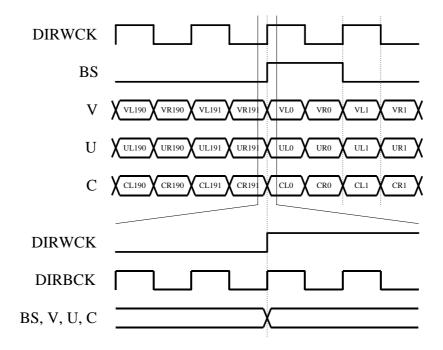

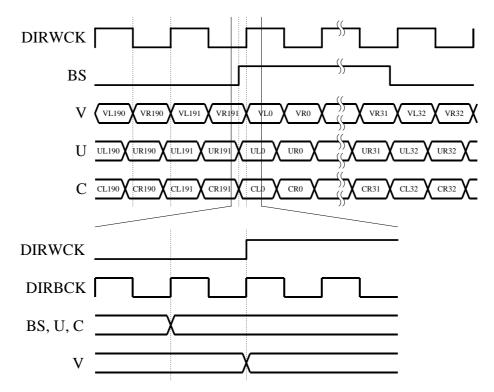

### • BS, V, U, C

The data of block start, validity flag, user data and channel status obtained from the DAIF signals are output as described below.

The block start is output from the ERR/BS pin at BSMOD=1 setting.

The validity flag is output from the DBL/V pin at VMOD=1 setting.

The user data is output from the SYNC/U pin at UMOD=1 setting.

The channel status is output from the FS128/C pin at CMOD=1 setting.

BS, V, U, C are fixed to the "L" level during the free-run mode or at VUCMUTE=1 setting.

BS, V, U and C are output according to the format shown below.

Alphabet clusters in the figure represent:

VLn --- Validity flag of L-ch frame n

ULn --- User data of L-ch frame n

CLn --- Channel status of L-ch frame n

CRn --- Channel status of R-ch frame n

#### When in mode 0 (CTIMMOD=0)

Note) at settings of DIROWP=0, DIROBP=0

When in mode 1 (CTIMMOD=1)

Note) at settings of DIROWP=0, DIROBP=0

#### ● /LOCK, ERR, DIRINT

The same data as LOCKN, DIRERR, DIRINT of DIR STATUS Register are output from /LOCK, ERR/BS, DIRINT pins respectively.

The DIRERR data is output from ERR/BS pin at BSMOD=0 setting.

#### • DBL

The information, whether the DDIN input signal is a double rate signal, is output from the DBL/V pin at VMOD=0 setting.

If PLL in the DIR block is locked at double rate and the free-run mode is not used, "H" level is output.

If PLL in the DIR block is locked at normal rate or the free-run mode is used, "L" level is output.

## 1-5) Analog circuit for PLL in DIR block

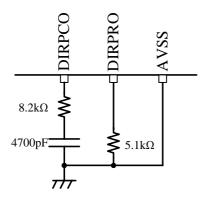

#### • DIRPCO, DIRPRO

These are capacitor and resistor connection pins for PLL in DIR block. As shown below, connect a 4700pF capacitor and an  $8.2k\Omega$  resistor between DIRPCO and AVSS as close as physically possible to DIRPCO and a  $5.1k\Omega$  resistor between DIRPRO and AVSS as close as physically possible to DIRPRO.

## 2) Main DSP Block

#### 2-1) Serial data input / output

#### SDIA

This is used to input PCM or bitstream into the Main DSP block. Normally, the PCM output of the external ADC is input.

The input format can be selected by setting the SDIA register.

For the format, refer to "Serial Data Interface Format".

The SDIA pin input or DIRSDO output of the DIR block is selected by SDIASEL, and processed in the Main DSP block.

#### • SDOA0-2

The PCM signal processed in the Main DSP block is output to these pins.

L-ch, R-ch signals are output from SDOA0 pin, LS-ch, RS-ch signals from SDOA1 pin and C-ch, LFE-ch signals from SDOA2 pin.

At the same time the signals are output from these pins, they are input to the Sub DSP block through the SDIB interface.

The output format can be selected by setting the SDOA register.

For the format, refer to "Serial Data Interface Format".

#### • SDBCKIO, SDWCKIO, SDBCKI1, SDWCKI1

These are input clocks for the serial data. When the serial data is synchronized not to DIRBCK, DIRWCK from DIR included in this LSI but to the clocks from the outside, supply clocks to these pins.

The clocks for the SDIA / SDOA interface will be DIRBCK / DIRWCK or SDBCKI0 / SDWCKI0 selected at SDIACKSEL.

The clocks for the SDIB / SDOB interfaces will be the same clocks for the SDIA interface (DIRBCK / DIRWCK or SDBCKI0 / SDWCKI0 selected at SDIACKSEL)

or

SDBCKI1 / SDWCKI1

(Refer to "Block Diagram".)

When not using the external clock, keep these pins unconnected.

#### /SDBCKO

A reverse clock of DIRBCK or SDBCKI0 selected at SDIACKSEL is output. This clock can be utilized when the polarity of the clock for the peripheral devices such as ADC and DAC differs.

Refer to "Block Diagram".

#### 2-2) Status output

### • DTSDATA, AC3DATA, SURENC, KARAOKE, MUTE, CRC, NONPCM

These pins output the status data of the signals processed in the Main DSP block.

The status, which is the same as the contents of the STATUS Register, is output from respective pins.

#### ZEROFLG

This pin indicates how long the input signal (SDIA or DIRSDO) for the Main DSP block is kept in the digital zero state. The same status as ZEROFLG of the ZERO Register is output.

#### 3) Sub DSP Block

#### 3-1) Serial data input / output

#### • SDIB0-3

These are PCM input pins to the Sub DSP block.

The data input to SDIB0-2 pins or the SDOA0-2 output from the Main DSP block are selected at SDIBSEL and processed in the Sub DSP block. The input data to the SDIB3 pin is always processed in the Sub DSP block regardless of SDIBSEL.

Refer to "Block Diagram".

The input format can be selected by setting the SDIB register.

For the format, refer to "Serial Data Interface Format".

#### SDOB0-3

These are the output pins for the PCM signals processed in the Sub DSP block.

The output format can be selected by setting the SDOB register.

For the format, refer to "Serial Data Interface Format".

#### 3-2) External memory interface

#### ● RAMA0-17, RAMD0-15, RAMWEN, RAMOEN, CASN, RASN

These pins are used to connect an external memory to the Sub DSP block for the data delay.

#### 3-3) Status output

#### OVFB/END

The output varies depending on OVFSEL settings of ERAM register bit 7. This output is used when programming Sub DSP.

#### OVFB at OVFSEL=0

This pin becomes "H" level when a digital overflow occurs as a result of operation in the Sub DSP block. "H" level is kept from the moment an overflow occurs to the moment the next PCM sample is output from the SDOB interface. When the next PCM sample output starts, the pin is reset to "L" level.

#### END at OVFSEL=1

This pin becomes "H" level while the program counter of Sub DSP is operating, and "L" level when all the processing is completed and the program counter stops. While operating correctly, it becomes "L" level once during one sample time. If it fails to become "L" level even once during one sample time, it means that the program has not been completed correctly and fully.

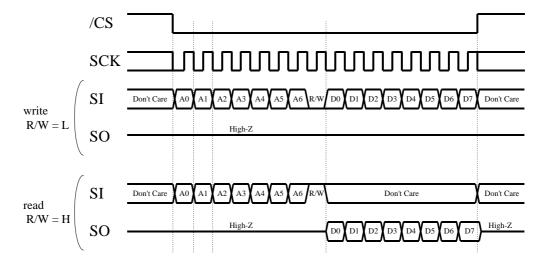

### 4) Microprocessor Interface

#### • /CS, SCK, SI, SO

The control registers are read / written via the four-wire serial microprocessor interface.

For the interface format, refer to "Microprocessor Interface Format".

#### • IPORT0-4, DDIN1-3

The signals input to these pins can be read via the IPORT register.

By connecting the status output of other devices to these pins, it is possible to read the data of other devices via the microprocessor interface of this device. It should be noted that DDIN1-3 are also used as input signal pins of DIR block.

IPORT0-4 pins may be left open when unused as pull-up resistors are built-in, but be sure to connect the unused DDIN1-3 pins to VSS as no pull-up resistors are built-in.

#### • OPORT0-7

The data written in the OPORT register are output from these pins.

By connecting the mode selection of other devices to these pins, the other device can be controlled via the microprocessor interface of this device.

## 5) Clock

## • XI, XO

These are crystal oscillator (24.576MHz) connection pins. Use a crystal oscillator of fundamental mode. Use XI when inputting the external clock.

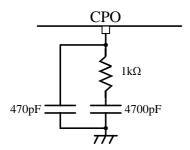

#### CPO

This is to connect external parts for PLL generating the operation clock of the DSP block. Connect a resistor and capacitors between CPO and AVSS as close as physically possible to CPO.

# ■ Control Register / Register Map

The decoding system is controlled by reading and writing the control registers as shown below through microprocessor interfaces (/CS, SCK, SI, SO).

All control registers are reset to "0" by initial clear (/IC=L).

| Address | Name           | bit 7     | bit 6    | bit 5   | bit 4           | bit 3           | bit 2    | bit 1     | bit 0   |  |

|---------|----------------|-----------|----------|---------|-----------------|-----------------|----------|-----------|---------|--|

| 0x00    | AUTO/DSN       | AUTOMOD   |          |         |                 | DSNIGN          |          | DSN2-0    |         |  |

| 0x01    | MUTE           | LMUTEN    | CMUTEN   | RMUTEN  | RSMUTEN         |                 | LFEMUTEN | I         | AMOFF   |  |

| 0x02    | SDIA           | SDIACKSEL | SDIASEL  | SDIAF   | MT1-0           | SDIABIT1-0      |          | SDIAWP    | SDIABP  |  |

| 0x03    | SDOA           |           |          |         |                 |                 |          |           | SDOABP  |  |

| 0x04    | OPORT          |           | OPORT7-0 |         |                 |                 |          |           |         |  |

| 0x05    | IPORT          |           | IPORT7-0 |         |                 |                 |          |           |         |  |

| 0x06    | (TEST)         |           |          |         |                 |                 |          |           |         |  |

| 0x07    | (TEST)         |           |          |         |                 |                 |          |           |         |  |

| 0x08    | PCM            | PLDECI    | MOD1-0   | PCMDLY  | LROUT           |                 |          |           |         |  |

| 0x09    | NOISE LEVEL    |           |          |         | •               | LEV7-0          |          |           |         |  |

| 0x0A    | CENTER DELAY   |           |          |         |                 |                 |          | CDELAY2-0 |         |  |

| 0x0B    | SURROUND DELAY |           |          |         |                 |                 | SRDEL    | AY3-0     |         |  |

| 0x0C    | NOISE          | NOISE     | PN/WN    | IMPULSE |                 | DIMCFG2-0       |          |           |         |  |

| 0x0D    | FS             |           | CWCFG2-0 | •       | SRF             | IL1-0           |          | FS2-0     |         |  |

| 0x0E    | L VOLUME       |           |          |         | LVO             | L7-0            |          |           |         |  |

| 0x0F    | C VOLUME       |           |          |         | CVO             | L7-0            |          |           |         |  |

| 0x10    | R VOLUME       |           | RVOL7-0  |         |                 |                 |          |           |         |  |

| 0x11    | LS VOLUME      |           | LSVOL7-0 |         |                 |                 |          |           |         |  |

| 0x12    | RS VOLUME      |           |          |         | RSVO            | OL7-0           |          |           |         |  |

| 0x13    | LFE VOLUME     |           |          |         | LFEV            | OL7-0           |          |           |         |  |

| 0x14    | COMPRESSION    | EMPON     | AIBON    | VOLON   | DITHOFF         | P11OFF          | DIALOFF  | COMPN     | MOD1-0  |  |

| 0x15    | HDYNRNG        |           |          |         | HDYNI           | RNG7-0          |          |           |         |  |

| 0x16    | LDYNRNG        |           |          |         | LDYNI           | RNG7-0          |          |           |         |  |

| 0x17    | MODE           | PCMMOD    | PLDECON  | RSINV   | DUALN           | MOD1-0          | (        | OUTMOD2-( | )       |  |

| 0x18    |                |           |          |         |                 |                 |          |           |         |  |

|         | BITSTREAM      |           |          | (0      | lescribed in th | ne later sectio | n)       |           | Ī       |  |

| 0x2A    |                |           |          |         |                 |                 |          |           |         |  |

| 0x2B    | (Unused)       |           |          |         | (Unde           | efined)         |          |           |         |  |

| 0x2C    | (Unused)       |           |          |         | (Unde           | efined)         |          |           |         |  |

| 0x2D    | Pc             |           |          | Т       | Pc              | 7-0             | Т        | Т         |         |  |

| 0x2E    | DATA STREAM    |           | STREAM6  | STREAM5 | STREAM4         | STREAM3         | STREAM2  | STREAM1   | STREAM0 |  |

| 0x2F    | STATUS         | DTSDATA   | AC3DATA  | 2/0MODE | SURENC          | KARAOKE         | MUTE     | CRC       | NONPCM  |  |

| 0x30    | ZERO           | ZEROFLG   |          |         |                 | ZERO6-0         |          |           |         |  |

| 0x31    | (TEST)         |           |          |         |                 |                 |          |           |         |  |

| 0x32    | MPCNT_H        | MPLOAD    | MPCLEARN |         |                 |                 | MPCN     | T11-8     |         |  |

| 0x33    | MPCNT_L        |           |          | 1       | MPC             | NT7-0           |          | 1         |         |  |

| 0x34    | SDIB           | SDIBCKSEL | SDIBSEL  | SDIBF   | MT1-0           | SDIBI           | BIT1-0   | SDIBWP    | SDIBBP  |  |

| 0x35    | SDOB           | SDOBCKSEL |          | SDOBI   | FMT1-0          | SDOB            | BIT1-0   | SDOBWP    | SDOBBP  |  |

| 0x36    | ERAM           | OVFSEL    | JMPSEL   |         |                 | RASREF          | ERAMMOD  | ERAM      | SEL1-0  |  |

| 0x37    | (TEST)         |           |          |         |                 |                 |          |           |         |  |

| 0x38 | MI0        |        | MI0REG7-0 |         |               |             |                       |          |             |  |  |  |

|------|------------|--------|-----------|---------|---------------|-------------|-----------------------|----------|-------------|--|--|--|

| 0x39 | MI1        |        |           |         |               | EG7-0       |                       |          |             |  |  |  |

| 0x3A | MI2        |        | MI2REG7-0 |         |               |             |                       |          |             |  |  |  |

| 0x3B | MI3        |        | MI3REG7-0 |         |               |             |                       |          |             |  |  |  |

| 0x3C | MI4        |        |           |         | MI4R          | EG7-0       |                       |          |             |  |  |  |

| 0x3D | MI5        |        |           |         | MI5R          | EG7-0       |                       |          |             |  |  |  |

| 0x3E | MI6        |        |           |         | MI6R          | EG7-0       |                       |          |             |  |  |  |

| 0x3F | MI7        |        |           |         | MI7R          | EG7-0       |                       |          |             |  |  |  |

| 0x40 | DIR CTRL   | CKMOD  | VUCMUTE   | SDOMUTE |               |             |                       | DDIN     | SEL1-0      |  |  |  |

| 0x41 | DIR SDO    | LOCKN  | MOD1-0    | DIROF   | MT1-0         | DIROI       | DIROBIT1-0 DIROWP DIR |          |             |  |  |  |

| 0x42 | DIR PIN    | BSMOD  | VMOD      | UMOD    | CMOD          |             |                       |          | CTIMMOD     |  |  |  |

| 0x43 | DIR INTMOD |        |           |         | INTM          | OD6-1       |                       |          |             |  |  |  |

| 0x44 | (TEST)     |        |           |         |               |             |                       |          |             |  |  |  |

| 0x45 | DIR CUADR  | DHLD   | R/L       | U/C     |               |             | CUADR4-0              |          |             |  |  |  |

| 0x46 | DIR CUDAT  |        |           |         | CUD           | AT7-0       |                       |          |             |  |  |  |

| 0x47 | DIR STATUS | DIRINT | DIRERR    | LOCKN   | VFLAG         | CSB1        | CSCHG                 | BSFLAG   | (Undefined) |  |  |  |

| 0x48 | DIR FS     |        |           |         |               | CSB3        |                       | DIRFS2-0 |             |  |  |  |

| 0x49 |            |        |           |         |               |             |                       |          |             |  |  |  |

|      | (TEST)     |        |           |         |               |             |                       |          |             |  |  |  |

| 0x57 |            |        |           |         |               |             |                       |          |             |  |  |  |

| 0x58 |            |        |           |         |               |             |                       |          |             |  |  |  |

|      | Invalid    |        |           | The out | put at the SO | pin becomes | High-Z.               |          |             |  |  |  |

| 0x7F |            |        |           |         |               |             |                       |          |             |  |  |  |

|             | lever write "1" into the shaded bits because the bits for testing are assigned there.     |     |

|-------------|-------------------------------------------------------------------------------------------|-----|

|             |                                                                                           |     |

|             | an access to addresses 0x06, 0x07, 0x31, 0x37, 0x44, 0x49 to 0x57 because the registers f | or  |

| testing are | signed there.                                                                             | - 1 |

The contents of the bitstream register (addresses 0x18 to 0x2A) vary depending on the input signal, i.e., the Main DSP input signal is AC-3 bitstream, DTS bitstream or PCM as shown below.

Only reading is allowed with the BITSTREAM register and not writing.

## 1) When the input signal is **AC-3 bitstream**

| Address | Name          | bit 7      | bit 6     | bit 5                         | bit 4     | bit 3    | bit 2         | bit 1       | bit 0           |

|---------|---------------|------------|-----------|-------------------------------|-----------|----------|---------------|-------------|-----------------|

| 0x18    | BITSTREAM 0   | fsc        | od        |                               |           | frmsi    | zecod         |             |                 |

| 0x19    | BITSTREAM 1   |            | bsid      |                               |           |          |               | bsmod       |                 |

| 0x1A    | BITSTREAM 2   |            | acmod     |                               | cmi       | xlev     | surm          | nixlev      | lfeon           |

| 0x1B    | BITSTREAM 3   | dsur       | mod       | copyrightb                    | origbs    | 0        | 0             | 0           | 0               |

| 0x1C    | BITSTREAM 4   | 0          | 0         | 0                             |           |          | dialnorm      |             |                 |

| 0x1D    | BITSTREAM 5   | 0          | 0         | 0                             |           |          | dialnorm2     |             |                 |

| 0x1E    | BITSTREAM 6   | audprodie  |           |                               | mixlevel  |          |               | roon        | ntyp            |

| 0x1F    | BITSTREAM 7   | audprodi2e |           |                               | mixlevel2 |          |               | room        | typ2            |

| 0x20    | BITSTREAM 8   | timecod1e  | 0         |                               | timecod1  |          |               |             |                 |

|         | (when bsid=6) | (xbsi1e)   | (0)       | (dmix                         | amod)     |          | (ltrtcmixlev) |             | (ltrtsurmixlev) |

| 0x21    | BITSTREAM 9   |            |           | -                             | time      | cod1     | _             |             |                 |

|         | (when bsid=6) | (ltrtsuri  | nixlev)   | (lorocmixlev) (lorosurmixlev) |           |          |               |             | )               |

| 0x22    | BITSTREAM 10  | timecod2e  | 0         |                               |           | time     | cod2          |             |                 |

|         | (when bsid=6) | (xbsi2e)   | (0)       | (dsure:                       | xmod)     | (dheadpl | nonmod)       | (adconvtyp) | (xbsi2)         |

| 0x23    | BITSTREAM 11  |            |           |                               | time      | cod2     |               |             |                 |

|         | (when bsid=6) |            |           |                               | (xbsi2)   |          |               |             | (encinfo)       |

| 0x24    | BITSTREAM 12  | langcode   | langcod2e | compre                        | compr2e   | 0        | 0             | 0           | 0               |

| 0x25    | BITSTREAM 13  |            |           |                               | lang      | cod      |               |             |                 |

| 0x26    | BITSTREAM 14  |            |           |                               | lango     | cod2     |               |             |                 |

| 0x27    | BITSTREAM 15  |            |           |                               | con       | npr      |               |             |                 |

| 0x28    | BITSTREAM 16  |            |           |                               | com       | pr2      |               |             |                 |

| 0x29    | BITSTREAM 17  |            |           |                               | dyn       | rng      |               |             |                 |

| 0x2A    | BITSTREAM 18  |            |           |                               | dynı      | rng2     |               |             |                 |

# 2) When the input signal is **DTS bitstream**

| Address | Name         | bit 7       | bit 6                  | bit 5       | bit 4 | bit 3  | bit 2       | bit 1       | bit 0     |

|---------|--------------|-------------|------------------------|-------------|-------|--------|-------------|-------------|-----------|

| 0x18    | BITSTREAM 0  | fsc         | fscod (Undefined) RATE |             |       |        |             |             |           |

| 0x19    | BITSTREAM 1  |             | (Undefined)            | l           | HDCD  |        | EXT_AUDIO_  | ĮD.         | EXT_AUDIO |

| 0x1A    | BITSTREAM 2  |             |                        | AMO         | ODE   |        |             | (Undefined) | lfeon     |

| 0x1B    | BITSTREAM 3  |             |                        | (Undefined) |       |        |             | PCMR        |           |

| 0x1C    | BITSTREAM 4  |             |                        |             |       |        |             |             |           |

|         |              |             | (Undefined)            |             |       |        |             |             |           |

| 0x23    | BITSTREAM 11 |             |                        |             |       |        |             |             |           |

| 0x24    | BITSTREAM 12 | (Unde       | fined)                 | DYNF        |       |        | (Undefined) |             |           |

| 0x25    | BITSTREAM 13 |             |                        |             | (Unde | fined) |             |             |           |

| 0x26    | BITSTREAM 14 |             |                        |             | (Unde | fined) |             |             |           |

| 0x27    | BITSTREAM 15 |             |                        |             | RAN   | NGE    |             |             |           |

| 0x28    | BITSTREAM 16 |             | (Undefined)            |             |       |        |             |             |           |

| 0x29    | BITSTREAM 17 | (Undefined) |                        |             |       |        |             |             |           |

| 0x2A    | BITSTREAM 18 |             |                        |             | (Unde | fined) |             |             |           |

## 3) When the input signal is **PCM**

The contents of BITSTREAM register (addresses 0x18 to 0x2A) are all undefined.

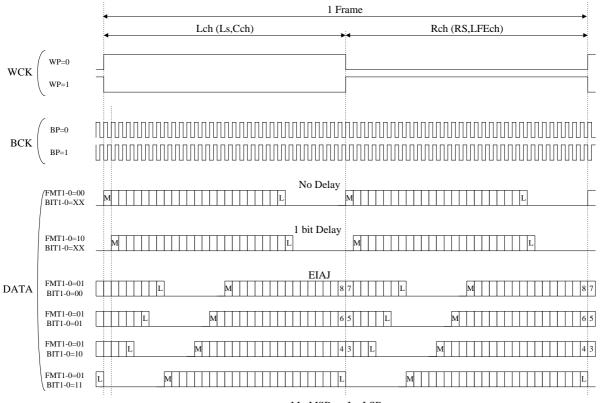

# ■ Serial Data Interface Format

Shown below are interface formats obtained by setting SDIA Register, SDOA Register, SDIB Register, SDOB Register and DIR SDO Register.

M: MSB L: LSB

# ■ Microprocessor Interface Format

A four-wire serial interface is used to read and write the control registers.

SO becomes an output pin only when all of the following conditions are met.

- -/CS=L

- When reading the valid addresses

- Timing of 8 bits data output

If any of the above conditions is not met, SO outputs High-Z. Thus SO, SI and SCK can be used jointly with other devices that have similar interfaces.

## [CAUTION]

Set /CS=H during /IC=L.

## **■ ELECTRICAL CHARACTERISTICS**

## 1. Absolute Maximum Ratings

| Parameter            | Symbol | Condition        | Min.    | Тур. | Max.     | Unit |

|----------------------|--------|------------------|---------|------|----------|------|

| Power Supply Voltage | VDD1   |                  | Vss-0.5 |      | 4.6      | V    |

|                      | AVdd   |                  | Vss-0.5 |      | 4.6      | V    |

|                      | VDD2   |                  | Vss-0.5 |      | 3.6      | V    |

| Input Voltage        | VI     | except XI pin *1 | -0.5    |      | 5.75     | V    |

|                      |        | XI pin           | -0.5    |      | VDD1+0.5 | V    |

| Storage Temperature  | Tstg   |                  | -50     |      | 125      | °C   |

\*1: 5V tolerant input terminal is used.

## 2. Recommended Operating Conditions

| Parameter             | Symbol            | Condition | Min. | Тур. | Max. | Unit |

|-----------------------|-------------------|-----------|------|------|------|------|

| Power Supply Voltage  | V <sub>DD</sub> 1 |           | 3.0  | 3.3  | 3.6  | V    |

|                       | AVDD              |           | 3.0  | 3.3  | 3.6  | V    |

|                       | V <sub>DD</sub> 2 |           | 2.3  | 2.5  | 2.7  | V    |

| Operating Temperature | Тор               |           | 0    | 25   | 70   | °C   |

## 2. DC Characteristics

Conditions: Under recommended operating conditions

| Parameter                 | Symbol           | Condition     | Min.     | Тур. | Max.    | Unit |

|---------------------------|------------------|---------------|----------|------|---------|------|

| Input Voltage "H" level 1 | VIH1             | *1            | 0.7Vdd1  |      |         | V    |

| Input Voltage "L" level 1 | Vı∟1             | *1            |          |      | 0.3Vpd1 | V    |

| Input Voltage "H" level 2 | VIH2             | *2            | 2.4      |      |         | V    |

| Input Voltage "L" level 2 | VIL2             | *2            |          |      | 8.0     | V    |

| Input Voltage "H" level 3 | VIH3             | *3            | 2.2      |      |         | V    |

| Input Voltage "L" level 3 | VIL3             | *3            |          |      | 0.8     | V    |

| Output Voltage "H" level  | Voн              | IOH = -80 μA  | VDD1-0.4 |      |         | V    |

| Output Voltage "L" level  | Vol              | IOL = 1.0  mA |          |      | 0.4     | V    |

| Input Leakage Current     | llı              | no pull-up    | -10      |      | 10      | μΑ   |

|                           |                  | resistor pin  |          |      |         | -    |

| Pull-up Resistor          | Rυ               |               | 40       |      | 160     | kΩ   |

| Power Consumption         | P <sub>D</sub> 1 | VDD1          |          | 60   | 120     | mW   |

| ·                         | PD2              | VDD2          |          | 220  | 260     | mW   |

<sup>\*1:</sup> Applicable to XI pin.

<sup>\*2:</sup> Applicable to /IC and DDIN0-3 pins.

<sup>\*3:</sup> Applicable to input pins except the above pins.

## **■ SYSTEM CONNECTION DIAGRAM**

Shown below is an example of basic connection of YSS932 (AC3D3B) and the peripheral circuits.

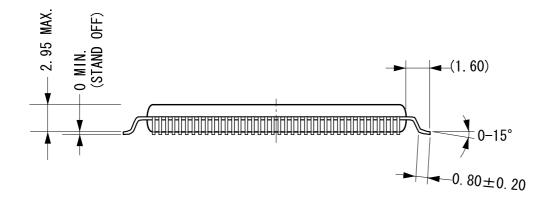

#### **EXTERNAL DIMENSIONS**

C-PK128SP-1

モールドコーナー形状は、この図面と若干異なるタイプのものもあります。 カッコ内の寸法値は参考値とする。

モールド外形寸法はバリを含まない。

単位(UNIT) : mm (millimeters)

The shape of the molded corner may slightly different from the shape in this diagram. The figure in the parenthesis ( ) should be used as a reference.

Plastic body dimensions do not include burr of resin.

UNIT: mm

注) 表面実装LSIは保管条件及び、半田付けについての特別な配慮が必要です。 詳しくはヤマハ代理店までお問い合わせ下さい。

Note: The LSIs for surface mount need special consideration on storage and soldering conditions. For detailed information, Please contact your nearest Yamaha agent.

## IMPORTANT NOTICE

- 1. Yamaha reserves the right to make changes to its Products and to this document without notice. The information contained in this document has been carefully checked and is believed to be reliable. However, Yamaha assumes no responsibilities for inaccuracies and makes no commitment to update or to keep current the information contained in this document.

- 2. These Yamaha Products are designed only for commercial and normal industrial applications, and are not suitable for other uses, such as medical life support equipment, nuclear facilities, critical care equipment or any other application the failure of which could lead to death, personal injury or environmental or property damage. Use of the Products in any such application is at the customer's sole risk and expense.

- 3. YAMAHA ASSUMES NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL, OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCTS.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANY THIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRANGIMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS' INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF YAMAHA PRODUCTS. YAMAHA ASSUMES NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMS OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

**Notice**

The specifications of this product are subject to improvement changes without prior notice.

AGENCY -

#### YAMAHA CORPORATION

Address inquiries to: Semiconductor Sales & Marketing Department

■ Head Office

203, Matsunokijima, Toyooka-mura Iwata-gun, Shizuoka-ken, 438-0192, Japan Tel. +81-539-62-4918 Fax. +81-539-62-5054

■ Tokyo Office 2-17-11, Takanawa, Minato-ku, Tokyo, 108-8568, Japan

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

Osaka Office 3-12-12, Minami Senba, Chuo-ku, Osaka City, Osaka, 542-0081, Japan

Tel. +81-6-6252-6221 Fax. +81-6-6252-6229