December 1994

### LM389 Low Voltage Audio Power Amplifier with NPN Transistor Array

#### **General Description**

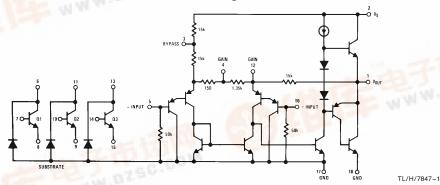

The LM389 is an array of three NPN transistors on the same substrate with an audio power amplifier similar to the LM386.

The amplifier inputs are ground referenced while the output is automatically biased to one half the supply voltage. The gain is internally set at 20 to minimize external parts, but the addition of an external resistor and capacitor between pins 4 and 12 will increase the gain to any value up to 200.

The three transistors have high gain and excellent matching characteristics. They are well suited to a wide variety of applications in DC through VHF systems.

#### **Features**

#### Amplifier

- Battery operation

- Minimum external parts

- Wide supply voltage range

- Low quiescent current drain

- Voltage gains from 20 to 200

- Ground referenced input

- Self-centering output quiescent voltage

- Low distortion

#### **Transistors**

- $\blacksquare$  Operation from 1  $\mu$ A to 25 mA

- Frequency range from DC to 100 MHz

- Excellent matching

#### **Applications**

- AM-FM radios

- Portable tape recorders

- Intercoms

- Toys and games

- Walkie-talkies

- Portable phonographs

- Power converters

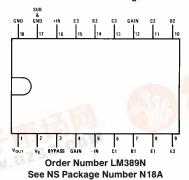

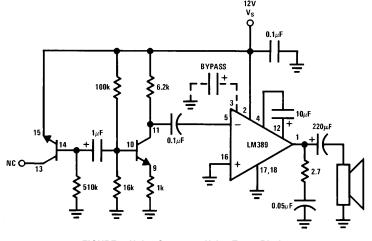

#### **Equivalent Schematic and Connection Diagrams**

**Dual-In-Line Package**

TL/H/7847-2

©1995 National Semiconductor Corporation TL/F

RRD-B30M115/Printed in U. S. A.

#### **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage

15V

Package Dissipation (Note 1)

1.89W

Input Voltage

± 0.4V

Storage Temperature

-65°C to +150°C

Operating Temperature

0°C to +70°C

Junction Temperature

150°C

Lead Temperature (Soldering, 10 sec.)

260°C

Collector to Emitter Voltage, VCEO

12V

Collector to Base Voltage, V<sub>CBO</sub> 15V Collector to Substrate Voltage, V<sub>CIO</sub> (Note 2) 15V Collector Current, I<sub>C</sub> 25 mA Emitter Current, IE 25 mA Base Current, IB 5 mA Power Dissipation (Each Transistor)  $T_A \le +70^{\circ}C$  150 mW Thermal Resistance 24°C/W  $\theta_{\sf JC}$  $\theta_{\mathsf{JA}}$ 70°C/W

#### **Electrical Characteristics** T<sub>A</sub> = 25°C

| Symbol              | Parameter                                              | Conditions                                                                                                                                                                                              | Min | Тур               | Max  | Units    |

|---------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|------|----------|

| AMPLIFIER           |                                                        |                                                                                                                                                                                                         | •   |                   |      |          |

| VS                  | Operating Supply Voltage                               |                                                                                                                                                                                                         | 4   |                   | 12   | V        |

| IQ                  | Quiescent Current                                      | $V_S = 6V, V_{IN} = 0V$                                                                                                                                                                                 |     | 6                 | 12   | mA       |

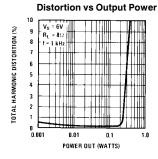

| P <sub>OUT</sub>    | Output Power (Note 3)                                  | $\begin{aligned} \text{THD} = \text{10\%} & & \text{V}_{\text{S}} = \text{6V}, \text{R}_{\text{L}} = 8\Omega \\ & \text{V}_{\text{S}} = \text{9V}, \text{R}_{\text{L}} = \text{16}\Omega \end{aligned}$ | 250 | 325<br>500        |      | mW<br>mW |

| A <sub>V</sub>      | Voltage Gain                                           | $V_S = 6V, f = 1 \text{ kHz}$<br>10 $\mu$ F from Pins 4 to 12                                                                                                                                           | 23  | 26<br>46          | 30   | dB<br>dB |

| BW                  | Bandwidth                                              | V <sub>S</sub> = 6V, Pins 4 and 12 Open                                                                                                                                                                 |     | 250               |      | kHz      |

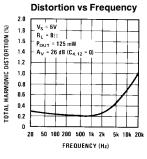

| THD                 | Total Harmonic Distortion                              | $V_S=6V, R_L=8\Omega, P_{OUT}=125  mW,$ f = 1 kHz, Pins 4 and 12 Open                                                                                                                                   |     | 0.2               | 3.0  | %        |

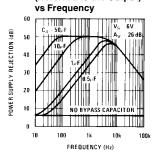

| PSRR                | Power Supply Rejection Ratio                           | $V_S=6V, f=1 \text{ kHz}, C_{BYPASS}=10 \ \mu\text{F},$ Pins 4 and 12 Open, Referred to Output                                                                                                          | 30  | 50                |      | dB       |

| R <sub>IN</sub>     | Input Resistance                                       |                                                                                                                                                                                                         | 10  | 50                |      | kΩ       |

| I <sub>BIAS</sub>   | Input Bias Current                                     | V <sub>S</sub> = 6V, Pins 5 and 16 Open                                                                                                                                                                 |     | 250               |      | nA       |

| TRANSISTOR          | ıs                                                     |                                                                                                                                                                                                         |     |                   |      |          |

| $V_{CEO}$           | Collector to Emitter<br>Breakdown Voltage              | $I_C = 1 \text{ mA}, I_B = 0$                                                                                                                                                                           | 12  | 20                |      | ٧        |

| $V_{CBO}$           | Collector to Base<br>Breakdown Voltage                 | $I_C = 10 \mu A, I_E = 0$                                                                                                                                                                               | 15  | 40                |      | ٧        |

| V <sub>CIO</sub>    | Collector to Substrate<br>Breakdown Voltage            | $I_C = 10 \mu A, I_E = I_B = 0$                                                                                                                                                                         | 15  | 40                |      | ٧        |

| V <sub>EBO</sub>    | Emitter to Base<br>Breakdown Voltage                   | $I_E = 10 \mu A, I_C = 0$                                                                                                                                                                               | 6.4 | 7.1               | 7.8  | V        |

| H <sub>FE</sub>     | Static Forward Current<br>Transfer Ratio (Static Beta) | $I_{C} = 10 \mu A$ $I_{C} = 1 mA$ $I_{C} = 10 mA$                                                                                                                                                       | 100 | 100<br>275<br>275 |      |          |

| h <sub>oe</sub>     | Open-Circuit Output Admittance                         | $I_{C} = 1 \text{ mA}, V_{CE} = 5V, f = 1.0 \text{ kHz}$                                                                                                                                                |     | 20                |      | μmho     |

| V <sub>BE</sub>     | Base to Emitter Voltage                                | I <sub>E</sub> = 1 mA                                                                                                                                                                                   |     | 0.7               | 0.85 | V        |

| $ V_{BE1}-V_{BE2} $ | Base to Emitter Voltage Offset                         | I <sub>E</sub> = 1 mA                                                                                                                                                                                   |     | 1                 | 5    | mV       |

| V <sub>CESAT</sub>  | Collector to Emitter<br>Saturation Voltage             | $I_C = 10 \text{ mA}, I_B = 1 \text{ mA}$                                                                                                                                                               |     | 0.15              | 0.5  | V        |

| C <sub>EB</sub>     | Emitter to Base Capacitance                            | V <sub>EB</sub> = 3V                                                                                                                                                                                    |     | 1.5               |      | pF       |

| C <sub>CB</sub>     | Collector to Base Capacitance                          | V <sub>CB</sub> = 3V                                                                                                                                                                                    |     | 2                 |      | pF       |

| C <sub>Cl</sub>     | Collector to Substrate<br>Capacitance                  | V <sub>Cl</sub> = 3V                                                                                                                                                                                    |     | 3.5               |      | pF       |

| h <sub>fe</sub>     | High Frequency Current Gain                            | $I_{C} = 10 \text{ mA}, V_{CE} = 5V, f = 100 \text{ MHz}$                                                                                                                                               | 1.5 | 5.5               |      |          |

Note 1: For operation in ambient temperatures above 25°C, the device must be derated based on a 150°C maximum junction temperature and a thermal resistance of 66°C/W junction to ambient.

Note 2: The collector of each transistor is isolated from the substrate by an integral diode. Therefore, the collector voltage should remain positive with respect to pin 17 at all times.

Note 3: If oscillation exists under some load conditions, add 2.7 $\Omega$  and 0.05  $\mu\text{F}$  series network from pin 1 to ground.

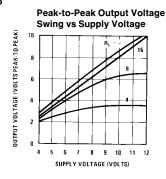

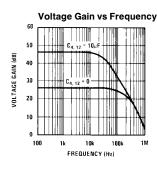

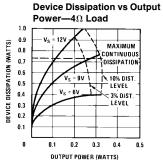

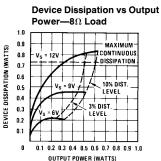

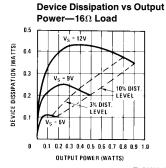

#### **Typical Amplifier Performance Characteristics Power Supply Rejection Ratio Quiescent Supply Current** (Referred to the Output) vs Supply Voltage vs Frequency SUPPLY CURRENT (mA) 40

8 9 10 11 12

SUPPLY VOLTAGE (VOLTS)

TL/H/7847-3

#### **Typical Transistor Performance Characteristics Forward Current Transfer Ratio** Saturation Voltage vs **Open Circuit Output Admittance** vs Collector Current **Collector Current** vs Collector Current FORWARD CURRENT TRANSFER RATIO (BETA) OPEN CIRCUIT DUTPUT ADMITTANCE (µmho) SATURATION VOLTAGE (mV) 200 300 150 200 100 100 0.01 COLLECTOR CURRENT (mA) COLLECTOR CURRENT (mA) COLLECTOR CURRENT (mA) TL/H/7847-4 **High Frequency Current Gain** Noise Voltage vs Frequency **Noise Current vs Frequency** vs Collector Current VOISE VOLTAGE (nV/√Hz) 16 NOISE CURRENT (pA/ $\sqrt{Hz}$ ) 14 h<sub>fe</sub> AT 100 MHz 12 10 4 6 8 10 12 14 16 FREQUENCY (Hz) FREQUENCY (Hz) I<sub>C</sub> - COLLECTOR CURRENT (mA) $g_{oe}\, and\, C_{oe}\, vs\, Collector$ goe and Coe vs Collector **Contours of Constant Noise** Figure 10k 7k OUTPUT CONDUCTANCE (µmhos) - OUTPUT CONDUCTANCE (µmhos) 180 18 700 160 16 - DRIVING SOURCE (12) 4k - OUTPUT CAPACITANCE 600 - OUTPUT CAPACITANCE (pF) 140 14 500 120 12 400 100 10 700 86 60 400 V<sub>CE</sub> = 5V f = 10.7 MHz 40 200 20 6 10 0.3 0.1 1.0 I<sub>C</sub> - COLLECTOR CURRENT (mA) I<sub>C</sub> - COLLECTOR CURRENT (mA) $I_C - COLLECTOR CURRENT (mA)$ TL/H/7847-5

#### **Application Hints**

#### **Gain Control**

To make the LM389 a more versatile amplifier, two pins (4 and 12) are provided for gain control. With pins 4 and 12 open, the 1.35  $k\Omega$  resistor sets the gain at 20 (26 dB). If a capacitor is put from pin 4 to 12, bypassing the 1.35  $k\Omega$  resistor, the gain will go up to 200 (46 dB). If a resistor is placed in series with the capacitor, the gain can be set to any value from 20 to 200. A low frequency pole in the gain response is caused by the capacitor working against the external resistor in series with the 150 $\Omega$  internal resistor. If the capacitor is eliminated and a resistor connects pin 4 to 12, then the output dc level may shift due to the additional dc gain. Gain control can also be done by capacitively coupling a resistor (or FET) from pin 12 to ground.

Additional external components can be placed in parallel with the internal feedback resistors to tailor the gain and frequency response for individual applications. For example, we can compensate poor speaker bass response by frequency shaping the feedback path. This is done with a series RC from pin 1 to 12 (paralleling the internal 15  $k\Omega$  resistor). For 6 dB effective bass boost:  $R\cong 15~k\Omega$ , the lowest value for good stable operation is  $R=10~k\Omega$  if pin 4 is open. If pins 4 and 12 are bypassed then R as low as 2  $k\Omega$  can be used. This restriction is because the amplifier is only compensated for closed-loop gains greater than 9V/V.

#### **Input Biasing**

The schematic shows that both inputs are biased to ground with a 50  $k\Omega$  resistor. The base current of the input transistors is about 250 nA, so the inputs are at about 12.5 mV when left open. If the dc source resistance driving the LM389 is higher than 250  $k\Omega$  it will contribute very little additional offset (about 2.5 mV at the input, 50 mV at the output). If the dc source resistance is less than 10  $k\Omega$ , then shorting the unused input to ground will keep the offset low (about 2.5 mV at the input, 50 mV at the output). For dc source resistances between these values we can eliminate excess offset by putting a resistor from the unused input to ground, equal in value to the dc source resistance. Of course all offset problems are eliminated if the input is capacitively coupled.

When using the LM389 with higher gains (bypassing the 1.35 k $\Omega$  resistor between pins 4 and 12) it is necessary to

bypass the unused input, preventing degradation of gain and possible instabilities. This is done with a 0.1  $\mu$ F capacitor or a short to ground depending on the dc source resistance of the driven input.

#### Supplies and Grounds

The LM389 has excellent supply rejection and does not require a well regulated supply. However, to eliminate possible high frequency stability problems, the supply should be decoupled to ground with a 0.1 µF capacitor. The high current ground of the output transistor, pin 18, is brought out separately from small signal ground, pin 17. If the two ground leads are returned separately to supply then the parasitic resistance in the power ground lead will not cause stability problems. The parasitic resistance in the signal ground can cause stability problems and it should be minimized. Care should also be taken to insure that the power dissipation does not exceed the maximum dissipation of the package for a given temperature. There are two ways to mute the LM389 amplifier. Shorting pin 3 to the supply voltage, or shorting pin 12 to ground will turn the amplifier off without affecting the input signal.

#### **Transistors**

The three transistors on the LM389 are general purpose devices that can be used the same as other small signal transistors. As long as the currents and voltages are kept within the absolute maximum limitations, and the collectors are never at a negative potential with respect to pin 17, there is no limit on the way they can be used.

For example, the emitter-base breakdown voltage of 7.1V can be used as a zener diode at currents from 1  $\mu$ A to 5 mA. These transistors make good LED driver devices, V<sub>SAT</sub> is only 150 mV when sinking 10 mA.

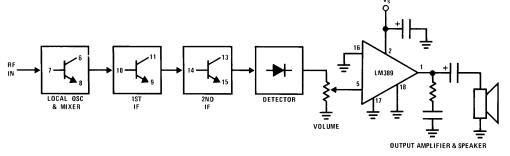

In the linear region, these transistors have been used in AM and FM radios, tape recorders, phonographs and many other applications. Using the characteristic curves on noise voltage and noise current, the level of the collector current can be set to optimize noise performance for a given source impedance. Some of the circuits that have been built are shown in *Figures 1–7*. This is by no means a complete list of applications, since that is limited only by the designers imagination.

FIGURE 1. AM Radio

TL/H/7847-6

# Application Hints (Continued) All switches in record mode Head characteristic 280 mH/300 $\Omega$ TL/H/7847-7 FIGURE 2. Tape Recorder TL/H/7847-8 FIGURE 3. Ceramic Phono Amplifier with Tone Controls

## **Application Hints** (Continued) TL/H/7847-9 FIGURE 4. FM Scanner Noise Squelch Circuit FREQ (250-1500 Hz) $f = \frac{1}{0.69 \; R \; 1 \; C \; 1}$ TL/H/7847-10 FIGURE 5. Siren \* Tremolo freq. $\leq \frac{1}{2\pi \; (\text{R} + 10\text{k})\text{C}}$ TL/H/7847-11 FIGURE 6. Voltage-Controlled Amplifier or Tremolo Circuit

#### **Application Hints** (Continued)

FIGURE 7. Noise Generator Using Zener Diode

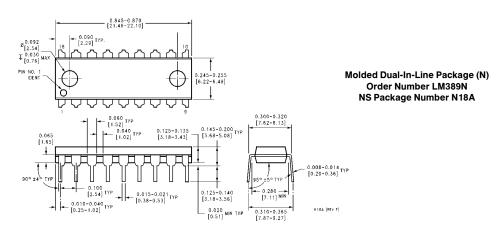

#### Physical Dimensions inches (millimeters)

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959

Fax: 1(800) 737-7018

National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Email: onlyge@tevm2.nsc.com

Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 78 32 Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

TI /H/7847-12

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.