查询D75P008CU供应商

# NEC Electronics Inc.

# 捷多邦,专业PCB打样工<mark>#PD75008 Family</mark> (µPD75004/006/008/P008) 4-Bit General-Purpose Single-Chip Microcontrollers

October 1994

# Description

The  $\mu$ PD75008 family of high performance 4-bit singlechip CMOS microcontrollers includes the following devices:

μPD75004 μPD75004(A) μPD75006 μPD75006(A) μPD75008 μPD75008(A) μPD75P008

These general-purpose microcontrollers have up to 8K bytes of ROM and 512 nibbles of RAM. The instruction set operates on 1, 4, and 8 bits of data.

Timing is generated by two oscillators. The main oscillator drives the CPU and all peripherals. The 32.768-kHz subsystem oscillator provides time keeping when the main oscillator is turned off. Since CMOS power dissipation is proportional to clock rate, the  $\mu$ PD75008 family provides selectable instruction cycle times from 0.95 to 122  $\mu$ s. The STOP and HALT modes turn off parts of the microcontroller for additional power savings. The data retention mode retains RAM contents down to 2.0 volts.

## Features

- 8-bit synchronous serial interface

- --- Full-duplex, three-wire mode

- Half-duplex, two-wire mode

- NEC serial bus interface (SBI) mode

- Timers: three channels

- 8-bit interval timer

- 8-bit timer/event counter

- -Watch (clock) timer:

- 0.5 second interrupt requests

- □ 34 I/O lines

- Eight input-only lines

- 18 bidirectional I/O lines of which four can directly drive LEDs

- Eight 10-V n-channel, open-drain lines that can directly drive LEDs

## - 25 software selectable pullup resistors

- Eight mask option selectable resistors (mask ROM devices only)

- Bit sequential buffer

- 16 bits of bit addressable RAM in peripheral address space.

- Standard CPU instruction set

- 107 instructions

- -Bit manipulation instructions

- 4-bit arithmetic instructions

- -4- and 8-bit move instructions

- Minimum instruction execution time

- 0.95, 1.91, and 15.3  $\mu \rm s$  using 4.19-MHz main system clock

- 122 µsec using 32.768-kHz subsystem clock

- Eight 4-bit registers

Usable as four 8-bit registers

- Memory-mapped, on-chip peripherals

- Vectored interrupt controller

- 12 external and 4 internal sources

- 12 edge detection inputs

- 5 vectored interrupt addresses

- Power saving and battery backup

- Variable CPU clock rate; 2.5 mA typical at 5 V and 4.19 MHz

- HALT mode stops CPU; 0.5 mA typical at 5 V and 4.19 MHz

- STOP mode stops main clock; 0.5 µA typical at 5 V

- 2.0 V data retention mode

- Subsystem oscillator allows watch timer to operate in power-down modes.

- CMOS operation

- --- ROM devices;  $V_{DD} = 2.7$  to 6.0 V

# Internal High-Capacity ROM and RAM

| Memory | μPD75004                 | μPD75006    | μPD75008    | μPD75P008   |

|--------|--------------------------|-------------|-------------|-------------|

| ROM    | 4K bytes                 | 6K bytes    | 8K bytes    |             |

| PROM   | 12 1 4 4 4 1 1 1 1 1 1 1 | _           |             | 8K bytes    |

| RAM    | 512 nibbles              | 512 nibbles | 512 nibbles | 512 nibbles |

818 |

# NEC

## **Ordering Information**

| Part Number           | Quality Grade | ROM  | Package                   | Package Drawing |

|-----------------------|---------------|------|---------------------------|-----------------|

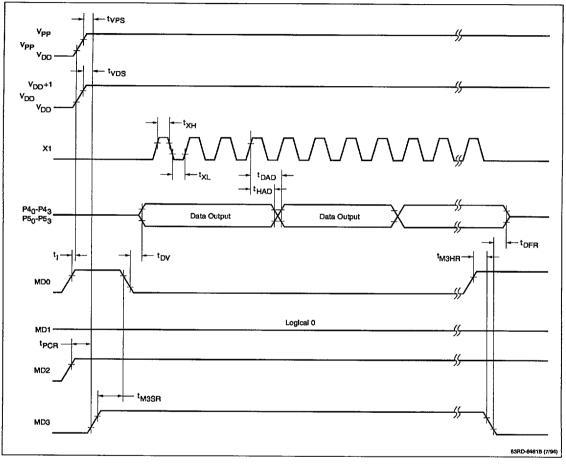

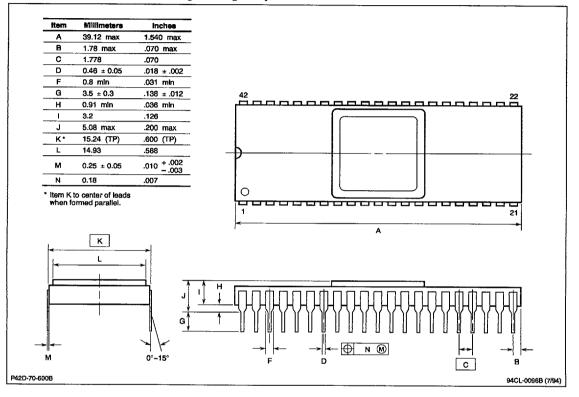

| μPD75004CU-xxx        | Standard      | Mask | 42-pin plastic shrink DIP | P42C-70-600A    |

| μPD75004CU(A)-xxx     | Special       | -    |                           |                 |

| μPD75006CU-xxx        | Standard      | -    |                           |                 |

| µPD75006CU(A)-xxx     | Special       | -    |                           |                 |

| μPD75008CU-xxx        | Standard      | -    |                           |                 |

| μPD75008CU(A)-xxx     | Special       | •    |                           |                 |

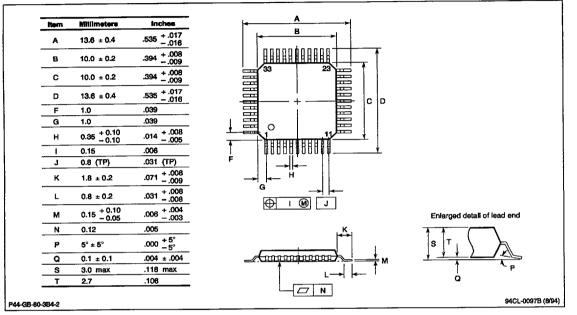

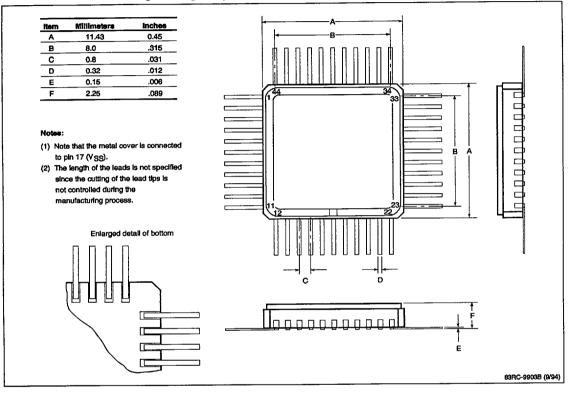

| μPD75004GB-xxx-3B4    | Standard      | Mask | 44-pin plastic QFP        | P44GB-80-3B4-2  |

| μPD75004GB(A)-xxx-3B4 | Special       | -    |                           |                 |

| μPD75006GB-xxx-3B4    | Standard      | -    |                           |                 |

| µPD75006GB(A)-xxx-3B4 | Special       | •    |                           |                 |

| μPD75008GB-xxx-3B4    | Standard      | •    |                           |                 |

| µPD75008GB(A)-xxx-3B4 | Special       |      |                           |                 |

| μPD75P008CU           | Standard      | OTP  | 42-pin plastic shrink DIP | P42C-70-600A    |

| µPD75P008GB-3B4       | Standard      | OTP  | 44-pin plastic QFP        | 44GB-80-3B4-2   |

#### Notes:

(1) Engineering samples are available in a 42-pin shrink DIP or 44-pin ceramic QFP

(2) xxx indicates ROM code number

## **Device Quality Grades**

The devices in the  $\mu$ PD75008 family are available in standard or special quality grades devices. Special grade devices have the symbol (A) embedded in the part number. A  $\mu$ PD75008CU is a standard grade and a  $\mu$ PD75008CU(A) is a special grade device. The selection of the correct grade depends upon the application.

# Differences Between Special and Standard Quality Grades

| ltem                           | Special                                                                                                                      | Standard                                                                                                                                                                          |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications                   | Automotive and<br>transportation<br>equipment, traffic<br>control systems, anti-<br>disaster systems, anti-<br>crime systems | Computers, office<br>equipment,<br>communications, test<br>and measurement,<br>machine tools,<br>industrial robots,<br>audio and visual<br>equipment, other<br>consumer products. |

| LED direct<br>drive            | No                                                                                                                           | Yes                                                                                                                                                                               |

| Absolute<br>maximum<br>ratings | Differences in low and high output current                                                                                   |                                                                                                                                                                                   |

| DC<br>characteristics          | Differences in low-voltage outputs                                                                                           |                                                                                                                                                                                   |

## **Pin Configurations**

## 42-Pin Plastic SDIP

| хтı d                       |                | 42 🗆 Voo                    |

|-----------------------------|----------------|-----------------------------|

|                             | •              |                             |

|                             | 2              | ·· P · · · ·                |

|                             | 3              | 40 P41                      |

|                             | 4              | 39 P42                      |

|                             | 5              | 38 P43                      |

|                             | 6              | 37 P P50                    |

| 2 -                         | 7              | 36 P P51                    |

|                             |                | 35 🗆 P5 <sub>2</sub>        |

|                             | 9              | 34 🖵 P53                    |

|                             | 10             | 33 P P60/KR0                |

|                             | 11             | 32 P61/KR1                  |

| 3-1                         | 12             | 31 P62/KR2                  |

|                             | 13             | 30 🗖 P63/KR3                |

|                             | 14             | 29 📮 P7 <sub>0</sub> /KR4   |

|                             | 15             | 28 P71/KR5                  |

|                             | 16             | 27 P72/KR6                  |

|                             | 17             | 26 P73/KR7                  |

|                             | 18             | 25 P20/PTO0                 |

|                             | 19             | 24 P21                      |

| NC (Vpp)                    | 20             | 23 P P22/PCL                |

|                             | 21             | 22   P2_/BUZ                |

| L                           |                |                             |

| Note : Vpp is the programmi | ing oin in the | 75B008 and should be        |

|                             |                | sted in the mask ROM parts. |

|                             |                | 83RD-6363A (7/94            |

0052604 754 🎟

# NEC

# µPD75008 Family

## **Pin Configurations**

# 44-Pin Plastic QFP

| Symbol                           | Function                                            |  |

|----------------------------------|-----------------------------------------------------|--|

| NC (V <sub>PP</sub> )            | No connection<br>(programming voltage for µPD75P008 |  |

| P0 <sub>0</sub> /INT4            | Port 0 input; interrupt 4                           |  |

| P01/SCK                          | Port 0 input; serial clock                          |  |

| P0 <sub>2</sub> /SO/SB0          | Port 0 input; serial out; serial interface          |  |

| P03/SI/SB1                       | Port 0 input; serial in; serial interface           |  |

| P1 <sub>0</sub> /INT0            | Port 1 input; interrupt 0                           |  |

| P1 <sub>1</sub> /INT1            | Port 1 input; interrupt 1                           |  |

| P1 <sub>2</sub> /INT2            | Port 1 input; interrupt 2                           |  |

| P1 <sub>3</sub> /TI0             | Port 1 input; timer 0 input                         |  |

| P20/PTO0                         | Port 2 I/O; timer/event counter output              |  |

| P21                              | Port 2 I/O                                          |  |

| P2 <sub>2</sub> /PCL             | Port 2 I/O; clock output                            |  |

| P23/BUZ                          | Port 2 I/O; buzzer output                           |  |

| P30-P33                          | Port 3 I/O                                          |  |

| P4 <sub>0</sub> -P4 <sub>3</sub> | Port 4 I/O                                          |  |

| P50-P53                          | Port 5 I/O                                          |  |

| P6 <sub>0</sub> /KR0             | Port 6 I/O; key scan input 0                        |  |

| P61/KR1                          | Port 6 I/O; key scan input 1                        |  |

| P6 <sub>2</sub> /KR2             | Port 6 I/O; key scan input 2                        |  |

| P6 <sub>3</sub> /KR3             | Port 6 I/O; key scan input 3                        |  |

| P7 <sub>0</sub> /KR4             | Port 7 I/O; key scan input 4                        |  |

| P7 <sub>1</sub> /KR5             | Port 7 I/O; key scan input 5                        |  |

| P7 <sub>2</sub> /KR6             | Port 7 I/O; key scan input 6                        |  |

| P73/KR7                          | Port 7 I/O; key scan input 7                        |  |

| P80-P81                          | Port 8 I/O                                          |  |

| RESET                            | Reset input                                         |  |

| V <sub>DD</sub>                  | Positive power supply                               |  |

| V <sub>SS</sub>                  | Ground                                              |  |

| X1, X2                           | Main clock inputs                                   |  |

| XT1, XT2                         | Subsystem clock inputs                              |  |

## **PIN FUNCTIONS**

P00-P03, INT4, SCK, SO/SB0, SI/SB1 (Port 0, Interrupt 4, Serial Interface). These pins can be used as 4-bit input port 0. P00 can also be used for vectored interrupt 4, which interrupts on either the leading edge or the trailing edge of the signal. P01-P03 may also be used for the serial interface in the SBI, 2-wire or 3-wire mode. SI is the serial input, SO is the serial output, and SCK is the serial clock. Reset causes these pins to default to the port 0 input mode.

P1<sub>0</sub>-P1<sub>3</sub>, INT0-INT2, TI0 (Port 1, Edge-Triggered Interrupts, Timer Input). These pins can be used as 4-bit input port 1. P1<sub>0</sub> and P1<sub>1</sub> can also be used for edgetriggered interrupts INT0 and INT1. P1<sub>2</sub> can be used for INT2, which is also an edge-triggered input, but one that generates an interrupt request and does not cause an interrupt. P1<sub>3</sub> can be used as an input clock to the timer/event counter to count external events. Reset causes these pins to default to the port 1 input mode.

P2<sub>0</sub>-P2<sub>3</sub>, PTO<sub>0</sub>, PCL, BUZ (Port 2, Timer/Event Counter, Clock, or Buzzer Output). These pins can be used as 4-bit I/O port 2. When used as an output the data is latched. When used as an input port the port outputs are three-state. P2<sub>0</sub> can also be used as the output of the timer/event counter flip flop (TOUT); P2<sub>2</sub> can be used as the output for the clock generator (PCL); and P2<sub>3</sub> can be used to output square waves for a buzzer. Reset causes these pins to default to the port 2 input mode.

**P3<sub>0</sub>-P3<sub>3</sub> (Port 3).** These pins are used for I/O port 3. Each bit in this port can be independently programmed to be either an input or an output. This port has latched outputs, and can directly drive LEDs. A reset signal causes this port to default to the input mode.

P4<sub>0</sub>-P4<sub>3</sub>, P5<sub>0</sub>-P5<sub>3</sub> (Ports 4 and 5). Ports 4 and 5 are 4-bit I/O ports that can be combined together to function as a single 8-bit port. They have latched outputs. Ports 4 and 5 will directly drive LEDs. Outputs are n-channel open drain, and can withstand up to 10 volts; pullup resistor mask options are available for these ports. A reset signal causes these ports to default to the input mode. P60-P63, P70-P73, KR0-KR7 (Ports 6, 7, and Edge Detection). Ports 6 and 7 are 4-bit I/O ports with latched outputs. Each pin of port 6 can be independently programmed to be either an input or an output, while port 7 can be programmed to be either all inputs or all outputs. Ports 6 and 7 can be paired together to function as one 8-bit port. Alternately, these pins may be used to detect the falling edge of inputs KR0-KR3 (port 6) and KR4-KR7 (port 7). A reset signal causes these ports to default to the input mode.

**P80-P81 (Port 8).** Port 8 is a 2-bit I/O port. Outputs are latched. A reset signal causes this port to default to the input mode.

NC/V<sub>PP</sub> (No Connection/Programming Pin). When using the programmable devices, this pin is used to input the programming voltage during the EPROM/OTP write/verify cycles. During normal operation of the programmable device, this pin should be tied to V<sub>DD</sub>. This pin may be left unconnected when using the mask ROM device,  $\mu$ PD7500x; however, to maintain socket compatibility with the EPROM/OTP devices, it is recommended that this pin be tied to V<sub>DD</sub>.

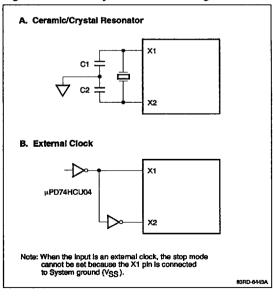

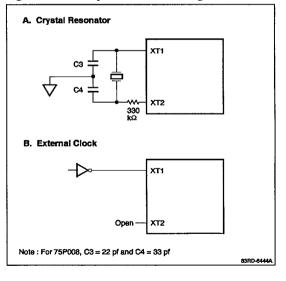

X1, X2 (Main System Clock Inputs). These pins are the main system clock inputs. The clock can be either a ceramic resonator or a crystal; an external logic signal may also be used.

XT1, XT2 (Subsystem Clock Inputs). These pins are the subsystem clock inputs. The clock can be either a ceramic resonator or a crystal; an external logic signal may also be used.

**RESET** (Reset). This is the reset input and it is active low.

**V<sub>DD</sub>** (Power Supply). The system positive power supply pin.

V<sub>SS</sub> (Ground). System ground.

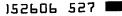

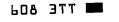

## **Block Diagram**

## **Product Comparison**

| Item                                         | 75004                                                                  | 75006                                    | 75008                                    | 75P008                               |

|----------------------------------------------|------------------------------------------------------------------------|------------------------------------------|------------------------------------------|--------------------------------------|

| Program Memory                               | Mask ROM<br>00H–FFH<br>4096 x 8 bits                                   | Mask ROM<br>0000H–177FH<br>6016 x 8 bits | Mask ROM<br>0000H-1F7FH<br>8064 x 8 bits | PROM<br>0000H-1F7FH<br>8064 x 8 bits |

| Data memory                                  |                                                                        | 512                                      | x 4 bits                                 | L                                    |

| 3-byte branch instructions                   | No                                                                     | Yes                                      | Yes                                      | Yes                                  |

| Other instruction set                        | Common to the products                                                 |                                          |                                          |                                      |

| Program counter                              | 12-bit                                                                 | 13-bit                                   | 13-bit                                   | 13-bit                               |

| Ports 0-3, ports 6-8 pullup resistor         | Software selectable                                                    |                                          |                                          |                                      |

| Ports 4 and 5 pullup resistor                | Mask option                                                            | Mask option                              | Mask option                              | No                                   |

| V <sub>PP</sub> , PROM program-<br>ming pins | No                                                                     | No                                       | No                                       | Yes                                  |

| Operating voltage range                      | 2.7 to 6.0 V                                                           | 2.7 to 6.0 V                             | 2.7 to 6.0 V                             | 5 V ± 5%                             |

| Package                                      | 42-pin plastic shrink DIP (600 mil)<br>44-pin plastic QFP (10 x 10 mm) |                                          |                                          |                                      |

## **CPU AND MEMORY ARCHITECTURE**

The 75X architecture has two separate address spaces, one for program memory (ROM) and another for data memory (RAM).

## Program Memory (ROM)

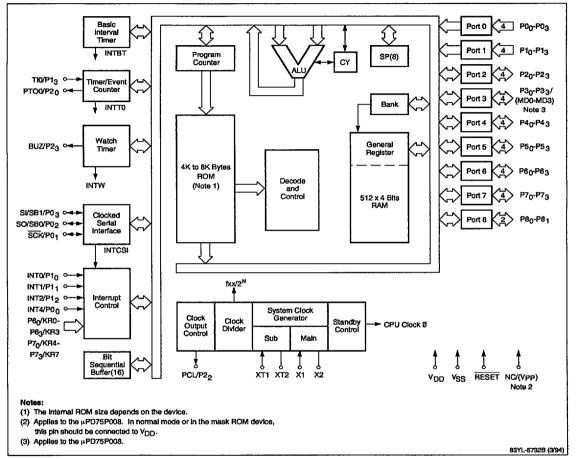

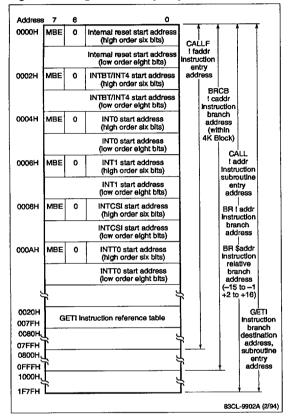

The ROM is addressed by the 12- or 13-bit program counter. The size of the program counter and the amount of ROM present depend on which part is being used. The ROM contains program object code, an interrupt vector table, a GETI instruction reference table, and table data. Table data can be obtained using table reference instruction MOVT.

Figure 1 shows the addressing range which can be made using a branch instruction or subroutine call instruction. In addition, the BR PCDE and BR PCXA instructions can be used for a branch where only the low 8 bits of the PC are changed. The program memory addresses are:

75004: 000H to FFFH 75006: 0000H to 177FH 75008: 0000H to 1F7FH 75P008: 0000H to 1F7FH

All locations in ROM except 0000H and 0001H can be used as program memory. However, if interrupts or GETI instructions are used, the locations corresponding to those functions cannot be used. Addresses are normally reserved as follows:

0000H to This address area is used as the 0001H vector address for RESET, and also contains the MBE bit. 0002H to<br/>000BHThis area is used for interrupt vector<br/>addresses. Each vector address<br/>contains an MBE bit value and the<br/>interrupt can start from any location<br/>except where noted above.0020H to<br/>0020H to<br/>007FHThis is the table area for GETI<br/>instructions. The GETI instruction is<br/>used to access one 2-byte or two<br/>1-byte instructions using one byte of<br/>program memory. This is useful in<br/>compacting code.

## Program Counter (PC)

This is a 12/13-bit binary counter that contains the address of the current program memory location. The  $\mu$ PD75004 contains a 12-bit PC and the 75006/008/P008 have a 13-bit PC.

When an instruction is executed, the PC is automatically incremented by the number of bytes of the current instruction. When a branch instruction (BR, BRCB) is executed, the contents of the immediate data or register pair indicating the new address are loaded into some or all bits of the PC.

When a subroutine call instruction (CALL, CALLF) is executed or an interrupt is generated, the PC is incremented to point to the next instruction, and this information is saved on the stack. During an interrupt, the program status word (PSW) is also automatically saved on the stack. The address to be jumped to by the CALL or interrupt is then loaded into the PC.

When a return instruction (RET,RETS, or RETI) is executed, the contents of the stack are restored to the PC.

#### Figure 1. Program Memory Map

#### Data Memory (RAM)

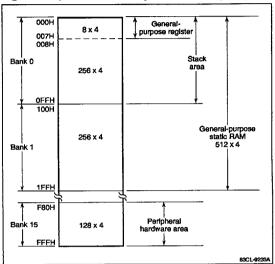

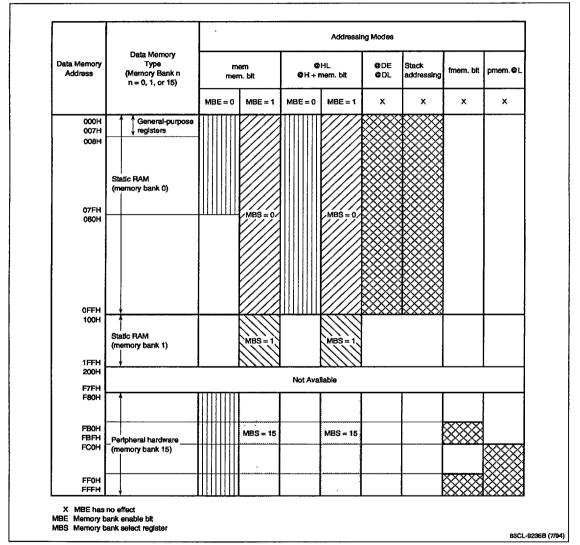

The data memory contains three memory banks: 0, 1, and 15. The RAM memory map is shown in figure 2. The memory consists of general-purpose static RAM and peripheral control registers.

The memory banks are accessed by using MBE (memory bank enable) and by programming the BS (bank select register). If MBE = 0, the lower 128 nibbles of memory bank 0 and the upper 128 nibbles of memory bank 15 are accessed. If MBE = 1, the upper four bits in the BS register will specify the memory bank. The values are 0H for memory bank 0, 1H for memory bank 1, and 0FH for memory bank 15.

Memory banks 0 and 1 each contain 256 nibbles. Although the memory is organized in nibbles, the 75X architecture allows the data to be manipulated in bytes, nibbles, and individual bits.

#### Figure 2. µPD75008 Family Data Memory Map

The data memory is used for storing processed data, general-purpose registers, and as a stack for subroutine or interrupt service. Because of its static nature, the RAM will retain its data when CPU operation is stopped and the chip is in the standby mode, provided  $V_{DD}$  is at least 2 volts.

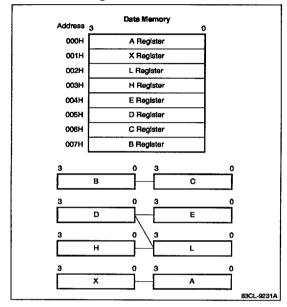

There are eight 4-bit general-purpose registers (figure 3) in bank 0 starting at location 00H. These registers may also be used as four 8-bit registers. The on-chip peripheral control registers and ports reside in the upper 128 nibbles of bank 15. Bank 15 addresses that are not assigned to a register are not available as random memory except for the 16-bit sequential buffer. Also, the lower 128 nibbles of bank 15 do not contain RAM.

Addressing Modes. The  $\mu$ PD75008 family can address data memory and ports as individual bits, nibbles, or bytes. These addressing modes are as follows:

1-bit direct data memory

4-bit immediate

4-bit register indirect (@rpa)

4-bit direct data memory

8-bit immediate

8-bit register indirect (@HL)

8-bit direct data memory

Tables 1 and 2 and figure 4 show the data memory addressing modes for the  $\mu$ PD75008 family.

# NEC

#### Figure 3. General-Purpose Register Configurations

#### Table 1. Data Memory Addressing Modes (Note 1)

| Addressing Mode            | Format   | Address                                                                                                                            |  |

|----------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------|--|

| 1-bit direct<br>addressing | mem. bit | The memory bank is:<br>if MBE = 0:<br>MB = 0 for addr 00H-7FH<br>MB = 15 for addr 80H-FFH<br>if MBE = 1:<br>MB = (MBE) • (MBS Reg) |  |

|                            |          | The memory location and bit<br>within the memory bank<br>is: mem.bit                                                               |  |

| 4-bit direct<br>addressing | mem      | The memory bank is:<br>if MBE = 0:<br>MB = 0 for addr 00H-7FH<br>MB = 15 for addr 80H-FFH<br>if MBE = 1:<br>MB = (MBE) • (MBS Reg) |  |

|                            |          | The memory location within the memory bank is: mem                                                                                 |  |

## Table 1. Data Memory Addressing Modes (Note 1) (cont)

| [                                        | e 1) (cont) |                                                                                                                                                                                                                                                                                               |  |

|------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Addressing Mode                          | Format      | Address                                                                                                                                                                                                                                                                                       |  |

| 8-bit direct<br>addressing               | məm         | The memory bank is<br>if MBE = 0:<br>MB = 0 for addr 00H-7FH<br>MB = 15 for addr 80H-FFH<br>if MBE = 1:<br>MB = (MBE)•(MBS Reg)<br>The memory location within the                                                                                                                             |  |

|                                          |             | memory bank is: mem<br>mem must be an even address                                                                                                                                                                                                                                            |  |

| 4-bit register<br>indirect<br>addressing | @ HL        | The memory bank is:<br>MB = (MBE)●(MBS Reg)                                                                                                                                                                                                                                                   |  |

| auuressing                               |             | The memory location within the<br>memory bank is:<br>contained in register HL                                                                                                                                                                                                                 |  |

|                                          | @ DE        | The memory bank is always bank 0.                                                                                                                                                                                                                                                             |  |

|                                          |             | The memory location within the<br>memory bank is:<br>contained in register DE                                                                                                                                                                                                                 |  |

|                                          | @ DL        | The memory bank is always bank 0.                                                                                                                                                                                                                                                             |  |

|                                          |             | The memory location within the<br>memory bank is:<br>contained in register DL                                                                                                                                                                                                                 |  |

| 8-bit register<br>indirect               | @ HL        | The memory bank is:<br>MB = (MBE)●(MBS Reg)                                                                                                                                                                                                                                                   |  |

| addressing                               |             | The memory location within the<br>memory bank is:<br>contained in register HL                                                                                                                                                                                                                 |  |

|                                          |             | HL must contain an even<br>address                                                                                                                                                                                                                                                            |  |

| Bit manipulation<br>addressing           | fmem. bit   | The memory bank is bank 15.<br>The memory location in bank 15<br>is fmem where:                                                                                                                                                                                                               |  |

|                                          |             | fmem = B0H-BFH for<br>interrupts<br>fmem = F0H-FFH for I/O<br>ports                                                                                                                                                                                                                           |  |

|                                          |             | The bit is specified<br>in: fmem.bit                                                                                                                                                                                                                                                          |  |

|                                          | pmem.@L     | The memory location is<br>independent of MBE and MBS.<br>The upper 10 bits of the<br>location are in the high order<br>10-bits of pmem and the 2<br>lower address bits are in the<br>upper 2-bits of register L. The<br>bit to be manipulated is<br>specified by the 2 LSBs of<br>register L. |  |

m m s 82

LO T58 🔳

#### Table 1. Data Memory Addressing Modes (Note 1)

| Addressing Mode                       | Format         | Address                                                                                                     |  |

|---------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------|--|

| Bit manipulation<br>addressing (cont) | @H+<br>mem.bit | The memory bank is:<br>MB = (MBE)●(MBS Reg)                                                                 |  |

|                                       |                | The memory location within the<br>memory bank is:<br>4 upper bits are in register H<br>4 lower bits are mem |  |

|                                       |                | The bit is specified in: mem.bit                                                                            |  |

| Stack<br>addressing                   |                | The stack is always in bank 0 and<br>the address is indicated by stack<br>pointer SP                        |  |

#### Note:

| (1) | MBE:     | Memory bank enable bit                       |

|-----|----------|----------------------------------------------|

|     | MB:      | Memory bank                                  |

|     | MBS:     | Memory bank select register                  |

|     | mem:     | A memory location within a memory bank       |

|     | mem.bit: | A memory location and a bit at that location |

### Table 2. On-Chip Peripherals Addressing Modes

| Type of<br>Manipulation | Addressing Mode                                                                                                                           | Hardware                                                           |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Bit                     | MBE = 0 or MBE = 1 and MBS<br>= 15; direct addressing with<br>bank address specified in<br>mem.bit.                                       | All hardware<br>where bit<br>manipulation<br>can be<br>performed   |

|                         | Direct addressing regardless of<br>the setting of MBE and MBS.<br>Bank address specified in<br>fmem. bit.                                 | ISTO, MBE;<br>IExxx,<br>IRQxxx,<br>PORTn.x                         |

|                         | Indirect addressing regardless<br>of the setting of MBE and MBS.<br>Bank address specified in<br>pmem. @L.                                | BSBn.x;<br>PORTn.x                                                 |

| 4-bit                   | MBE = 0 or MBE = 1 and MBS<br>= 15; direct addressing with<br>bank address specified in mem.                                              | All hardware<br>where 4-bit<br>manipulation                        |

|                         | MBE = 1 and MBS = 15;<br>register indirect addressing<br>with bank address specified in<br>HL.                                            | can be<br>performed                                                |

| 8-bit                   | MBE = 0 (or MBE = 1 and<br>MBS = 15); direct addressing<br>with bank address specified in<br>mem; mem must be an even<br>address.         | All hardware<br>where 8-bit<br>manipulation<br>can be<br>performed |

|                         | MBE = 1 and MBS = 15;<br>register indirect addressing<br>with bank address specified in<br>HL; L register must contain an<br>even number. | -                                                                  |

#### Figure 4. Data Memory Organization and Addressing Modes

10

.

-

# NEC

## FUNCTIONAL DESCRIPTION

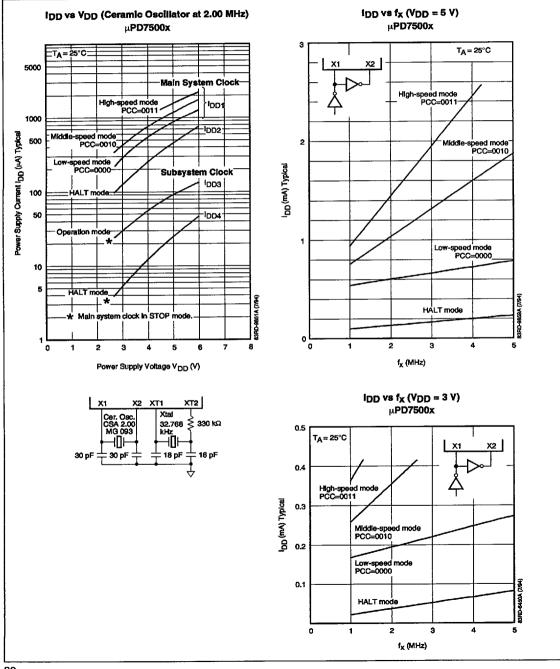

# Input/Output Ports

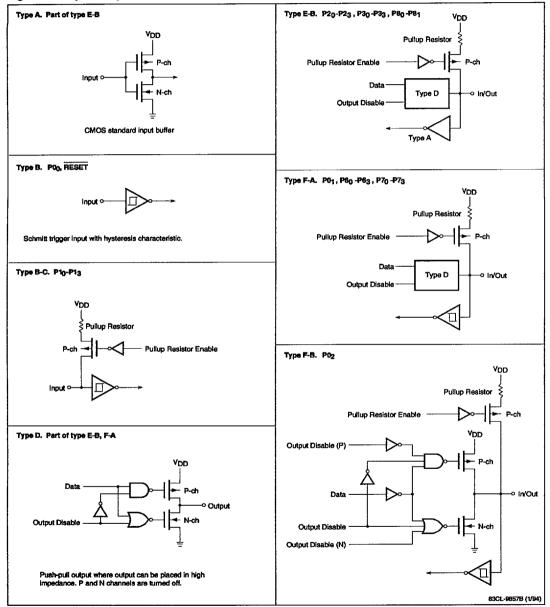

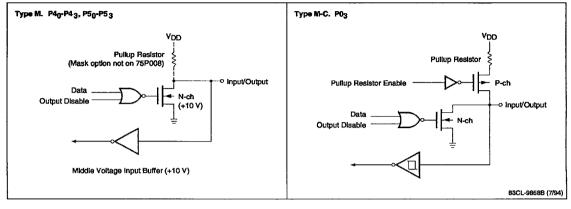

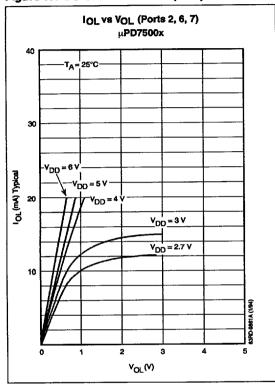

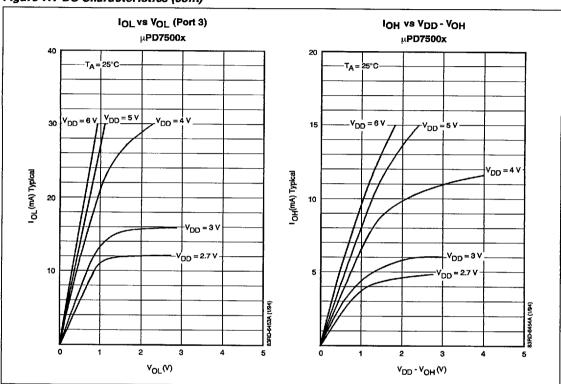

The  $\mu$ PD7500x provides eight 4-bit ports and one 2-bit port. Seven are input/output and two are input only. Table 3 lists the function and operation of the I/O ports. Figure 5 shows the internal circuits of the ports, which are classified as types A through Z.

Software selectable internal pullup resistors are available on ports 0, 1, 2, 3, 6, 7, and 8. They are selectable in 4-bit units except port 8, which is in 2-bit units. Port 0, bit 0 does not have a pullup resistor. Mask option, bit selectable internal pullup resistors are available for ports 4 and 5 on all mask ROM parts.

| Port   | Function                                                  | Operation and Features                                                                                                                                          | Remarks                                                                           |

|--------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| P0, P1 | 4-bit input                                               | Can be read or tested regardless of the operation mode of the following pins: SO/SB0, SI/SB1, SCK, INT0, INT1, INT2, INT4, or Tl0.                              | Pins are also used for SO/SB0, SI/SB1, SCK,<br>INT0, INT1, INT2, INT4, and TiO    |

| P3     | 4-bit input/output                                        | Can be set-up in input or output mode in 1-bit                                                                                                                  |                                                                                   |

| P6     | •                                                         | units.                                                                                                                                                          | Pins are also used for KR0-KR3                                                    |

| P2     | 4-bit input/output                                        | Can be set-up in input or output mode in 4-bit                                                                                                                  | Pins are also used for PTO0, PCL and BUZ                                          |

| P7     |                                                           | units. Ports 6 and 7 can be paired for data<br>input/output in 8-bit units.                                                                                     | Pins are also used for KR4-KR7                                                    |

| P8     | 2-bit input/output                                        | Can be set-up as either all inputs or all outputs.                                                                                                              |                                                                                   |

| P4, P5 | 4-bit input/output<br>(N-channel open<br>drain, 10 volts) | Can be set-up in input or output mode in 4-bit<br>units. Ports 4 and 5 can be paired for data<br>input/output in 8-bit units. An LED can be<br>driven directly. | Internal pullup resistor can be specified in 1-bit<br>units by using mask option. |

### Table 3. Types and Features of Digital Ports

Notes:

(1) These ports directly drive LEDs.

(2) Port 3 lines are also used for MD0-MD3 in only.

#### Figure 5. Input/Output Circuits

## Figure 5. Input/Output Circuits (cont)

# **Clock Generator**

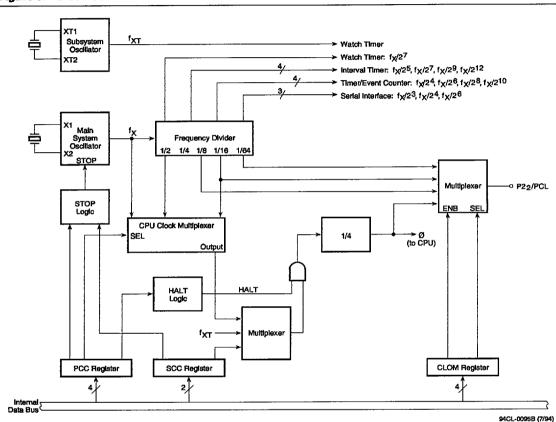

The clock generator uses a crystal as a time base to generate its clocks. Figure 6 shows the generator, which consists of main and subsystem oscillators, frequency dividers, multiplexers, and three control registers (PCC, SCC, and CLOM). Registers PCC and SCC are programmed to supply frequencies derived from the crystal to the CPU at one of four speeds. Register CLOM controls the clock output to the output pin PCL. Registers PCC and SCC control the HALT and STOP logic.

The  $\mu$ PD75008 family contains a subsystem clock with an oscillator driven by an external crystal. The clock operates from 32 to 35 kHz. It can be used as a clock source for the watch timer and the CPU.

## **Basic Interval Timer**

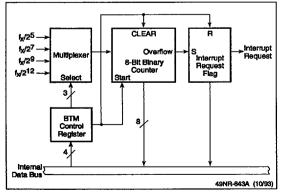

The basic interval timer provides continuous real time interrupts. The timer consists of a multiplexer, 8-bit free running counter, and the 4-bit BTM control register. See figure 7. Every time the counter increments to FFH, it generates an interrupt, overflows to 00H, and continues to count. In addition to clearing the counter and its interrupt request, the BTM register is used to select one of four clock inputs. The counter can generate 250 ms interrupts with a 4.19-MHz crystal. It also provides the STOP mode.

# **Timer/Event Counter**

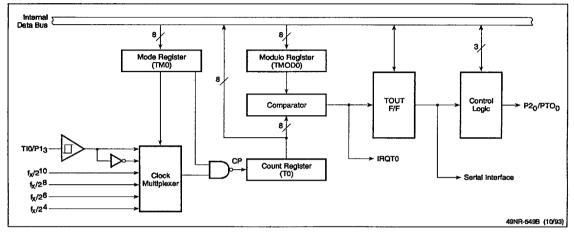

The timer/event counter consists of a binary 8-bit up-counter, an 8-bit modulo register, an 8-bit comparator, a clock multiplexer, mode control register (TM0), and a TOUT flip-flop. See figure 8. Control logic allows the TOUT flip-flop signal to be output to port 2, bit 0.

The counter operates when an 8-bit value is loaded into the modulo register. A count register clock is selected in the clock multiplexer by control register TM0. The 8-bit up-counter is incremented every time it receives a counter pulse (CP). When the count value equals the modulo register count, the 8-bit comparator outputs a signal. This toggles the TOUT flip-flop and resets the count register to 00H. The count register continues to count up unless it is stopped. Every time the comparator has a match, the TOUT flip-flop changes state and generates interrupt IRQT0. Signal TOUT can also be used as a clock for the serial interface.

## Watch Timer

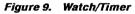

The watch timer (figure 9) is normally used as a time source for keeping track of the time of day. With a 4.19-MHz crystal, it will generate interrupt requests (not interrupts) at 0.5 second or 3.9 msec intervals. The timer consists of an input clock multiplexer, a frequency divider, an output multiplexer, control logic, and control register WM. When a subsystem clock is present, the timer can operate when the chip is in the STOP mode. Also, the watch timer can output a 2-kHz buzzer signal.

Figure 6. Clock Generator

#### Figure 8. Timer/Event Counter

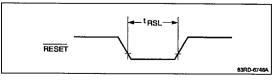

#### Serial Interface

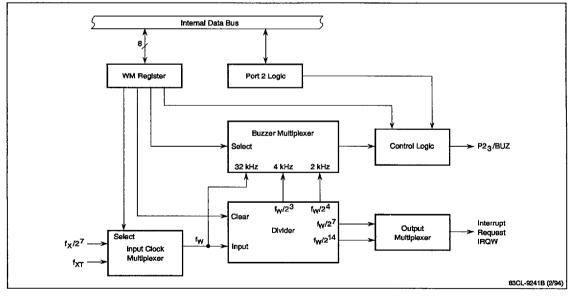

The 8-bit serial interface allows the  $\mu$ PD75008 family devices to communicate with other NEC or NEC-like serial interfaces. The serial interface consists of an 8-bit shift register (SIO), serial output latch (SO), 8-bit address comparator, slave address register (SVA), control registers (CSIM and SBIC), busy/acknowledge circuitry, and bus release/detect circuitry. See figure 10. The interface also contains a serial clock counter, clock

multiplexer, and serial clock control logic. The serial interface contains a three-wire interface, which consists of the following:

- Serial Data In (SI/SB1)

- Serial Data Out (SO/SB0)

- Serial Shift Clock (SCK)

#### Figure 10. Serial Interface Block Diagram

The three serial interface operation modes are:

- Two-wire serial mode

- Three-wire serial mode

- Two-wire SBI mode

The two or three-wire serial modes are the simplest modes; the 8-bit shift register is loaded with a byte of data and eight clock pulses are generated. The pulses shift data out the SO line and in from the SI line, thereby communicating in full duplex. When a byte of data is sent, a burst of eight clock pulses is generated and 8 bits of data are sent. The data may be sent with the LSB or MSB first. The interface can also be set to receive data only, consequently SO will be in the high impedance state. One of four internal clocks or an external clock clocks the data.

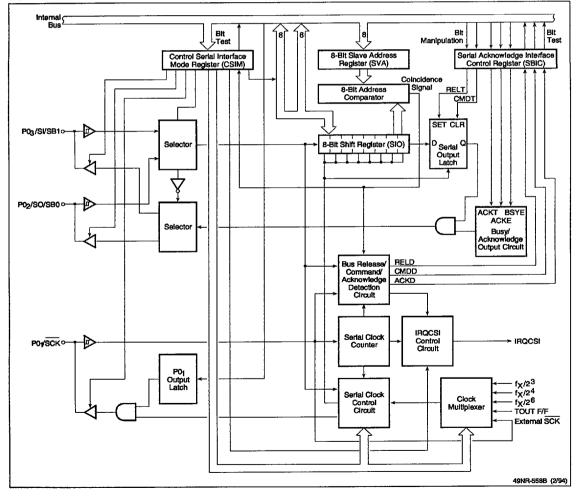

The SBI mode uses a two-wire interface with devices in a master/slave configuration. See figure 11. There is only one master device at a time; all others are slaves. The master sends addresses, commands, and data over the bus. The slaves are able to detect in hardware if their addresses were sent, a command was sent, or a portion of data was sent. There can be up to 256 slave addresses, 256 commands, and 256 data types. All commands are user definable. Commands can be sent to change slaves into masters; previous masters become slaves. Firmware performs this type of operation and thus the user decides whether the bus is simple or complex.

Figure 11. SBI Mode Master/Slave Configuration

#### **Bit Sequential Buffer**

The 16-bit sequential buffer is the only general-purpose RAM in the upper half of data memory bank 15. All the other locations in this bank contain either on-chip peripheral control registers or unused addresses. Its bits are addressed by register L. The buffer can be sequentially scanned by incrementing or decrementing register L. A typical application for this buffer is data storage for the next serial output or input. Another application is as a port output data storage area. The bit sequential buffer can be bit, nibble, or byte manipulated.

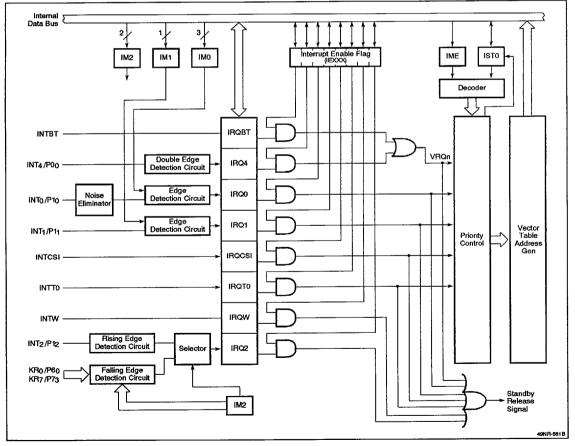

#### Interrupts

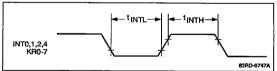

The three external and three internal interrupts are all vectored interrupts and are shown in figure 12. Table 4 lists a summary of the interrupts. Input INT2 detects rising edge inputs and generates an interrupt request flag, which is testable. Inputs KR0 through KR7 detect a falling edge and generate the same interrupt request flag as INT2. INT2 and KR0 through KR7 do not cause an interrupt, but can be used to release the standby mode. Interrupt requests and all interrupts except INT0 release the standby mode.

# NEC

# µPD75008 Family

## Table 4. Interrupt Sources

| Interrupt Source                                                                                                          | Internal/External | Interrupt Priority<br>(see note)                     | Vectored Interrupt Request<br>Table Address |  |

|---------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------|---------------------------------------------|--|

| INTBT<br>(Time reference interval signal from the basic<br>interval timer)                                                | Internal          | 1                                                    | VRQ1/0002H                                  |  |

| INT4<br>(Rising and falling edge detection)                                                                               | External          |                                                      |                                             |  |

| INTO<br>(Rising/falling edge detection)                                                                                   | External          | 2                                                    | VRQ2/0004H                                  |  |

| INT1<br>(Rising/falling edge detection)                                                                                   | External          | 3                                                    | VRQ3/0006H                                  |  |

| INTCSI<br>(Serial data transfer end signal)                                                                               | Internal          | 4                                                    | VRQ4/0008H                                  |  |

| INT TO<br>(Signal generated when programmable timer/<br>counter count register and modulo register<br>coincide)           | Internal          | 5                                                    | VRQ5/000AH                                  |  |

| INT2<br>(Rising edge input detection to INT2 pin or<br>falling edge input detection to KR <sub>0</sub> -KR <sub>7</sub> ) | External          | Testable input signals (Test if IRQ2 and IRQW are se |                                             |  |

| INTW<br>(Watch timer signal)                                                                                              | Internal          |                                                      |                                             |  |

Note: The interrupt priority determines the order when two or more simultaneous interrupts occur.

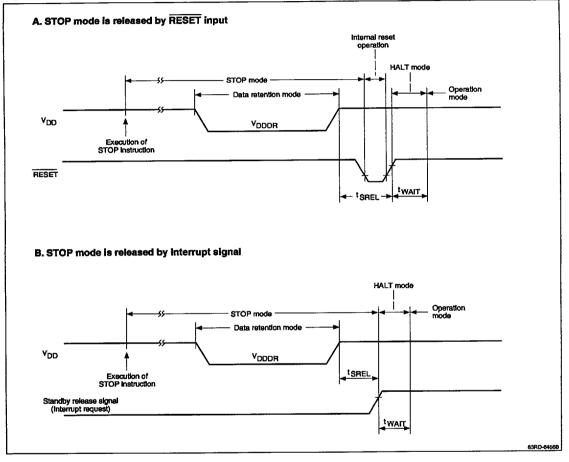

## Standby Modes

The three standby modes are described below and in table 5.

HALT Mode. The HALT mode is entered by executing the HALT instruction. In this mode, the clock to the CPU is shut off (thus stopping the CPU), while all other partsof the chip, with the exception of INT0, remain fully functional.

**STOP Mode.** The STOP mode is entered by executing the STOP instruction. In this mode, the chip's main system oscillator is shut off, thereby stopping all portions of the chip except those which function off the subsystem clock or interrupt requests. If the subsystem clock is used, it always remains on.

The HALT and STOP modes are released by a RESET or by any interrupt request except INT0.

**Data Retention Mode.** This mode may be entered after entering the STOP mode. Here, supply voltage  $V_{DD}$  may be lowered to 2 volts to further reduce power consumption. The contents of the RAM and registers are retained. This mode is released by first raising  $V_{DD}$  to the proper operating voltage range and then releasing the STOP mode.

#### Reset

See table 6 for the state of the chip after a  $\overrightarrow{\text{RESET}}$  is applied.

| Item                                                                                                                           | STOP Mode (Note 1)                                            | HALT Mode (Note 2)                                                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|

| Clock oscillator Only the main system clock oscillator is stopped. If a subsystem clock is present, it continues to oscillate. |                                                               | Only CPU clock $\phi$ is stopped. Main and subsystem oscillators continue to operate. |  |  |  |

| Basic interval timer                                                                                                           | Operation stops                                               | Operation continues (IRQBT is set at reference time intervals).                       |  |  |  |

| Serial interface Operates only when external SCK input is selected for serial clock.                                           |                                                               | Operational                                                                           |  |  |  |

| Timer/event counter                                                                                                            | Operates only when TIO pin input is selected for clock count. | Operational                                                                           |  |  |  |

| Watch timer                                                                                                                    | Operates when fXT is selected for the clock count.            | Operational                                                                           |  |  |  |

| External interrupts INT1, INT2, and INT4 are allowed to operate.<br>Only INT0 cannot operate.                                  |                                                               | All operational except INTO                                                           |  |  |  |

| CPU                                                                                                                            | Operational only from subsystem clock                         | Operation stops                                                                       |  |  |  |

| Release signal Enabled interrupt request signal (except INT0) or<br>RESET input.                                               |                                                               | Enabled interrupt request signal (except INT0) or RESET input.                        |  |  |  |

#### Table 5. Operation of the Standby Modes

#### Notes:

Use STOP instruction with main clock or SCC register with subsystem clock.

(2) Use HALT instruction for main or subsystem clock.

| Hardware                                              |                                   | RESET Input During<br>Standby Mode                                                                                                             | RESET Input During Normal<br>Operation |  |  |  |

|-------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

| Program counter (PC)                                  | μPD75004                          | The low-order 4 bits of program memory address 0000H a<br>into PC11 - PC8. The contents of address 0001H are loaded<br>PC7 - PC0.              |                                        |  |  |  |

|                                                       | μΡD75006<br>μΡD75008<br>μΡD75P008 | The low-order 5 bits of program memory address 0000H are loade<br>into PC12 - PC8. The contents of address 0001H are loaded into<br>PC7 - PC0. |                                        |  |  |  |

| PSW                                                   | Carry flag (CY)                   | Held                                                                                                                                           | Undefined                              |  |  |  |

|                                                       | Skip flags (SK0 - SK2)            | 0                                                                                                                                              | 0                                      |  |  |  |

|                                                       | Interrupt status flag (ISTO)      | 0                                                                                                                                              | 0                                      |  |  |  |

|                                                       | Memory bank enable flag (MBE)     | Bit 7 of program memory address 0000H is loaded into MBE                                                                                       |                                        |  |  |  |

| Stack pointer (SP)                                    |                                   | Undefined                                                                                                                                      | Undefined                              |  |  |  |

| Data memory (RAM)                                     |                                   | Held (Note 1)                                                                                                                                  | Undefined                              |  |  |  |

| General-purpose registers<br>(X, A, H, L, D, E, B, C) |                                   | Held                                                                                                                                           | Undefined                              |  |  |  |

| Memory bank selection<br>register (MBS)               |                                   | 0                                                                                                                                              | 0                                      |  |  |  |

| Basic interval timer                                  | Counter (BT)                      | Undefined                                                                                                                                      | Undefined                              |  |  |  |

|                                                       | Mode register (BTM)               | 0                                                                                                                                              | 0                                      |  |  |  |

| Timer/event counter                                   | Counter (T0)                      | 0                                                                                                                                              | 0                                      |  |  |  |

|                                                       | Modulo register (TMOD0)           | FFH                                                                                                                                            | FFH                                    |  |  |  |

|                                                       | Mode register (TM0)               | 0                                                                                                                                              | 0                                      |  |  |  |

|                                                       | TOE0, TOUT F/F                    | 0, 0                                                                                                                                           | 0, 0                                   |  |  |  |

| Watch timer                                           | Mode register (WM)                | 0                                                                                                                                              | 0                                      |  |  |  |

622 77T 🛲

### Table 6. State of the Device After Reset

ma Pana Pan

#### Table 6. State of the Device After Reset (cont)

| Hardware                                    |                                                                                                                                                                                                                                                          | RESET Input During<br>Standby Mode        | RESET Input During Normal<br>Operation    |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------|

| Serial interface                            | Shift register (SIO)                                                                                                                                                                                                                                     | Held                                      | Undefined                                 |

|                                             | Operation mode register (CSIM)                                                                                                                                                                                                                           | 0                                         | 0                                         |

|                                             | SBI control register (SBIC)                                                                                                                                                                                                                              | 0                                         | 0                                         |

|                                             | Slave address register (SVA)                                                                                                                                                                                                                             | Held                                      | Undefined                                 |

| Clock generator<br>and clock output circuit | Processor clock control register<br>(PCC)                                                                                                                                                                                                                | 0                                         | 0                                         |

|                                             | System clock control register<br>(SCC)                                                                                                                                                                                                                   | 0                                         | 0                                         |

|                                             | Clock output mode register<br>(CLOM)                                                                                                                                                                                                                     | 0                                         | 0                                         |

| Interrupt function                          | Interrupt request flags (IRQxxx)                                                                                                                                                                                                                         | Reset to 0                                | Reset to 0                                |

|                                             | Interrupt enable flags (IExxx)                                                                                                                                                                                                                           | 0                                         | 0                                         |

|                                             | Interrupt master enable flag<br>(IME)                                                                                                                                                                                                                    | 0                                         | 0                                         |

|                                             | INTO, INT1, and INT2 and mode<br>registers (IMO, IM1, and IM2)                                                                                                                                                                                           | 0, 0, 0                                   | 0, 0, 0                                   |

| Digital ports                               | Output buffers                                                                                                                                                                                                                                           | Off                                       | Off                                       |

|                                             | Output latches                                                                                                                                                                                                                                           | Cleared to 0                              | Cleared to 0                              |

|                                             | Input/output mode registers<br>(PMGA, B, C)                                                                                                                                                                                                              | 0                                         | 0                                         |

|                                             | Pullup resistor specification register (POGA, POGB)                                                                                                                                                                                                      | 0                                         | 0                                         |

| Bit sequential buffer                       |                                                                                                                                                                                                                                                          | Held                                      | Undefined                                 |

| Pin conditions                              | P0 <sub>0</sub> -P0 <sub>3</sub> , P1 <sub>0</sub> -P1 <sub>3</sub> ,<br>P2 <sub>0</sub> -P2 <sub>3</sub> , P3 <sub>0</sub> -P3 <sub>3</sub> ,<br>P6 <sub>0</sub> -P6 <sub>3</sub> , P7 <sub>0</sub> -P7 <sub>3</sub> , P8 <sub>0</sub> -P8 <sub>1</sub> | Input                                     | Input                                     |

|                                             | P4 <sub>0</sub> -P4 <sub>3</sub> , P5 <sub>0</sub> -P5 <sub>3</sub> ,                                                                                                                                                                                    | With incorporated pullup rea<br>impedance | sistor, high level; with open drain, high |

Note: (1) The data of data memory address 0F8H-0FDH is undefined by RESET.

# NEC

#### Caution

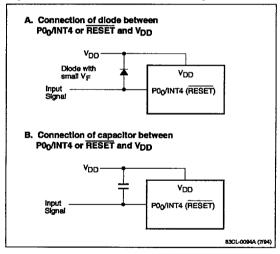

<u>Apart</u> from their normal functions, The P0<sub>0</sub>/INT4 and RESET pins are used to test the internal operation of the programmable devices. The test mode is entered by applying a voltage greater than  $V_{DD}$  to either of these pins.

For this reason, care must be taken to limit the voltage applied to these two pins. For example, it is conceivable that even during normal operation enough spurious noise may be present to set the chip into the test mode. If this happens, further normal operation is impossible. Consequently, it is important that interwiring noise be suppressed as much as possible. If this is inconvenient, anti-noise measures, like those shown in figure 13, should be implemented.

Figure 13. Noise Reduction Techniques

# **ELECTRICAL SPECIFICATIONS**

### **Absolute Maximum Ratings**

| $T_A = 25^{\circ}C$                                                                                   |                                         |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Supply voltage, V <sub>DD</sub>                                                                       | -0.3 to +7.0 V                          |

| Programming voltage, V <sub>PP</sub><br>(µPD75P008 only)                                              | -0.3 to +13.5 V                         |

| Input voltage, V <sub>I1</sub> (Note 1)                                                               | -0.3 to V <sub>DD</sub> + 0.3 V         |

| Input voltage, V <sub>I2</sub><br>(Ports 4 and 5 with open drain)                                     | –0.3 to 11 V                            |

| Output voltage, V <sub>O</sub>                                                                        | -0.3 to V <sub>DD</sub> + 0.3 V         |

| High-level output current, I <sub>OH</sub><br>(Single pin; standard grade)                            | -10 mA                                  |

| High-level output current, I <sub>OH</sub><br>(Single pin; special grade)                             | –10 mA peak<br>–5 mA rms (Note 2)       |

| High-level output current, I <sub>OH</sub><br>(Total of all pins; standard grade)                     | -30 mA                                  |

| High-level output current, I <sub>OH</sub><br>(Total of all pins; special grade)                      | –30 mA peak<br>–15 mA rms (Note 2)      |

| Low-level output current, I <sub>OL</sub><br>(Single pin; ports 0, 3-5;<br>standard grade)            | 30 mA peak,<br>15 mA rms (Notes 2, 3)   |

| Low-level output current, I <sub>OL</sub><br>(Single pin; ports 3-5;<br>special grade)                | 20 mA peak,<br>10 mA rms (Note 2)       |

| Low-level output current, I <sub>OL</sub><br>(Single pin; all ports except 0, 3-5;<br>standard grade) | 20 mA peak,<br>10 mA rms (Notes 2, 3)   |

| Low-level output current, I <sub>OL</sub><br>(Single pin; all ports except 3-5;<br>special grade)     | 10 mA peak,<br>5 mA rms (Note 2)        |

| Low-level output current, I <sub>OL</sub><br>(Total of ports 0, 3-5, 8;<br>standard grade)            | 160 mA peak,<br>120 mA rms (Notes 2, 3) |

| Low-level output current, I <sub>OL</sub><br>(Total of ports 0, 3, 8;<br>special grade)               | 80 mA peak,<br>40 mA rms (Notes 2, 3)   |

| Low-level output current, I <sub>OL</sub>                             | 66 mA peak,        |

|-----------------------------------------------------------------------|--------------------|

| (Total of ports 2, 6-7;<br>standard grade)                            | 33 mA rms (Note 2) |

| Low-level output current, IOI                                         | 40 mA peak,        |

| (Total of ports 2, 6-7;<br>special grade)                             | 20 mA rms (Note 2) |

| Low-level output current, I <sub>OL</sub>                             | 100 mA peak,       |

| (Total of ports 4-5;<br>special grade)                                | 60 mA rms (Note 2) |

| Storage temperature, T <sub>STG</sub>                                 | –65 to +150°C      |

| Operating temperature, T <sub>OPT</sub><br>(µPD7500x and µPD7500x(A)) | -40 to +85℃        |

| Operating temperature, T <sub>OPT</sub><br>(µPD75P008 only)           | -10 to +70°C       |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC characteristics.

#### Notes:

- (1) All ports: ports 4 and 5 have pullup resistors. Does not apply to  $\mu {\rm PD75P008}.$

- (2) Effective value = Peak value x (Duty) $^{1/2}$

- (3) Does not include port 0, bit 0.

####

| Parameter             | Symbol          | Min | Max | Unit | Conditions                        |

|-----------------------|-----------------|-----|-----|------|-----------------------------------|

| Input<br>capacitance  | C <sub>IN</sub> |     | 15  | рF   | f = 1 MHz;<br>all unmeasured pins |

| Output<br>capacitance | Cout            |     | 15  | рF   | returned to ground                |

| I/O<br>capacitance    | сю              |     | 15  | рF   | -                                 |

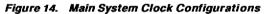

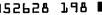

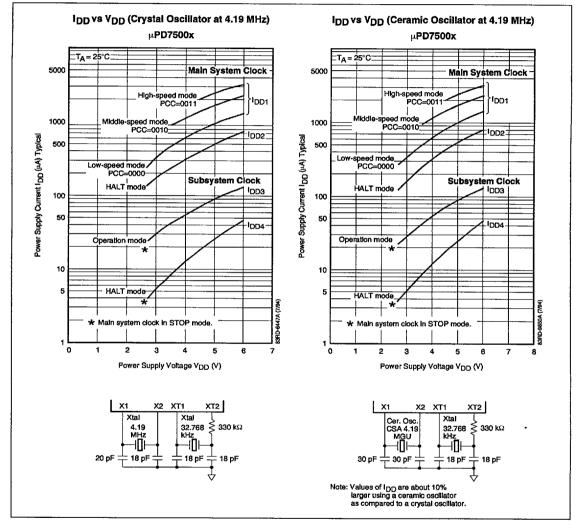

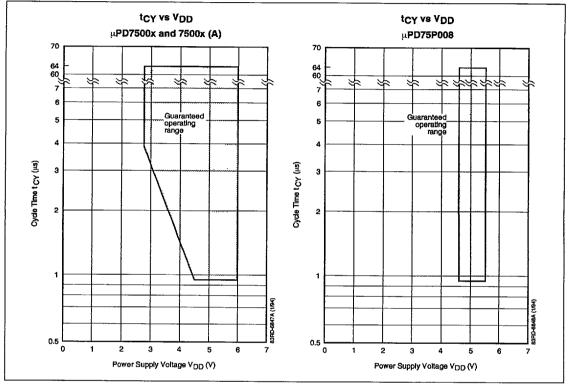

#### Main System Clock Oscillator

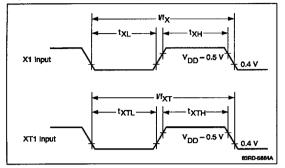

Refer to figures 14 and 16.

$\label{eq:main_prod} \begin{array}{l} \mu \text{PD7500x} (00x(\text{A}); \ \text{T}_{\text{A}} = -40 \ \text{to} \ +85^{\circ}\text{C}, \ \text{V}_{\text{DD}} = \ 2.7 \ \text{to} \ 6.0 \ \text{V} \\ \mu \text{PD75P008}; \ \text{T}_{\text{A}} = -10 \ \text{to} \ +70^{\circ}\text{C}, \ \text{V}_{\text{DD}} = \ 4.5 \ \text{to} \ 5.5 \ \text{V} \end{array}$

| Oscillator                         | Parameter                                  | Symbol                                       | Min | Тур  | Max          | Unit | Conditions                                                                            |

|------------------------------------|--------------------------------------------|----------------------------------------------|-----|------|--------------|------|---------------------------------------------------------------------------------------|

| Ceramic resonator<br>(Figure 14 A) | Oscillation frequency (Note 1)             | fx                                           | 1.0 |      | 5.0          | MHz  | V <sub>DD</sub> is in the oscillator voltage range.                                   |

|                                    | Oscillation stabilization time<br>(Note 2) |                                              |     |      | 4 (Note 3)   | ms   | After V <sub>DD</sub> reaches the minimum oscillator operating voltage range.         |

| Crystal resonator<br>(Figure 14 A) | Oscillation frequency (Note 1)             | fx                                           | 1.0 | 4.19 | 5.0 (Note 4) | MHz  |                                                                                       |

|                                    | Oscillation stabilization time<br>(Note 2) |                                              |     |      | 10 (Notes 3) | ms   | $V_{DD} = 4.5$ to 6.0 V for 7500x and 7500x(A) or<br>4.5 to 5.5 V for $\mu$ PD75P008. |

|                                    |                                            |                                              |     |      | 30 (Notes 3) | ms   | For $\mu$ PD7500x and 7500x(A) only at V <sub>DD</sub> = 2.7 - 6.0 V.                 |

| External clock<br>(Figure 14 B)    | X1 input frequency (Note 1)                | fx                                           | 1.0 |      | 5.0 (Note 4) | MHz  |                                                                                       |

|                                    | X1 input low- and high-level width         | <sup>t</sup> XH <sup>,</sup> <sup>t</sup> XL | 100 |      | 500          | ns   |                                                                                       |

#### Notes:

- (1) The oscillation frequency and X1 input frequency are included only to show the characteristics of the oscillators. Refer to the AC Characteristics table for actual instruction execution times.

- (2) The oscillation stabilization time is the time required for the oscillator to stabilize after voltage is applied or the STOP mode is released.

- (3) Values shown are for the recommended resonators. Values for resonators not shown in this data sheet should be obtained from the manufacturer's specification sheets.

- (4) When the oscillation frequency is  $f_x = 4.19$  to 5.0 MHz, do not select PCC = 0011 as the instruction execution time; otherwise, one machine cycle is set to less than 0.95  $\mu$ s, falling short of the rated minimum value of 0.95  $\mu$ s.

## Subsystem Clock Oscillator

Refer to figures 15 and 16.

$\mu$ PD7500x and 7500x(A): T<sub>A</sub> = -40 to +85°C; V<sub>DD</sub> = 2.7 to 6.0 V  $\mu$ PD75P008: T<sub>A</sub> = -10 to +70°C; V<sub>DD</sub> = 4.5 to 5.5 V

| Oscillator                      | Parameter                           | Symbol                                         | Min | Тур    | Max | Unit | Conditions                                                                    |

|---------------------------------|-------------------------------------|------------------------------------------------|-----|--------|-----|------|-------------------------------------------------------------------------------|

| Crystal resonator               | Oscillation frequency               | fхт                                            | 32  | 32.768 | 35  | kHz  |                                                                               |

| (figure 15 A)                   | Oscillation stabilization time      |                                                |     | 1.0    | 2   | 5    | $V_{DD} = 4.5$ to 6.0 V for 7500x and 7500x(A) or 4.5 to 5.5 V for µPD75P008. |

|                                 |                                     |                                                |     |        | 10  | S    | For $\mu$ PD7500x and 7500x(A) only at $V_{DD} = 2.7 - 6.0 V.$                |

| External clock<br>(figure 15 B) | XT1 input frequency                 | fхт                                            | 32  |        | 100 | kHz  |                                                                               |

|                                 | XT1 input low- and high-level width | <sup>t</sup> x⊤н <sup>,</sup> <sup>t</sup> x⊤∟ | 5   |        | 15  | μs   |                                                                               |

ma Per

## Recommended Oscillator Circuit Constants (For 7500x only)

Main system clock = Ceramic;  $T_A = -40$  to  $+85^{\circ}C$

|              | Part Number   | Frequency | C1       | C2       | Oscillatio | on Voltage |

|--------------|---------------|-----------|----------|----------|------------|------------|

| Manufacturer | (Note 1)      | (MHz)     | (PF)     | (pF)     | Min (V)    | Max (V)    |

| Murata       | CSA x.xxMK    | 1.0-1.99  | 30       | 30       | 2.7        | 6.0        |

|              | CSA x.xxMG093 | 2.0-2.44  | 30       | 30       | 2.7        | 6.0        |

|              | CST x.xxMG093 | 2.0-2.44  | (Note 2) | (Note 2) | 2.7        | 6.0        |

|              | CSA x.xxMGU   | 2.45-5.0  | 30       | 30       | 2.7        | 6.0        |

|              | CST x.xxMGU   | 2.45-5.0  | (Note 2) | (Note 2) | 2.7        | 6.0        |

|              | CSA x.xxMG    | 2.0-5.0   | 30       | 30       | 3.0        | 6.0        |

|              | CST x.xxMG    | 2.0-5.0   | (Note 2) | (Note 2) | 3.0        | 6.0        |

| Куосега      | KBR-1000H     | 1.0       | 100      | 100      | 2.7        | 6.0        |