This version: Jan. 1998

Previous version: Aug. 1996

# MSM81C55-5RS/GS/JS

2048-Bit CMOS STATIC RAM WITH I/O PORTS AND TIMER

#### GENERAL DESCRIPTION

The MSM81C55-5 has a 2k-bit static RAM (256 bytes) with parallel I/O ports and a timer. It uses silicon gate CMOS technology and consumes a standby current of 100 micro ampere, maximum, while the chip is not selected. Featureing a maximum access time of 400 ns, the MSM81C55-5 can be used in an MSM80C85AH system without using wait states. The parallel I/O consists of two 8-bit ports and one 6-bit port (both general purpose).

The MSM81C55-5 also contains a 14-bit programmable counter/timer which may be used for sequence-wave generation or terminal count-pulsing.

#### **FEATURES**

- High speed and low power achieved with silicon gate CMOS technology

- 256 words x 8bits RAM

- Single power supply, 3 to 6 V

- Completely static operation

- On-chip address latch

- 8-bit programmable I/O ports (port At and B)t4U.com

- TTL Compatible

- RAM data hold characteristic at 2 V

- 6-bit programmable I/O port (port C)

- 14-bit programmable binary counter/timer

- Multiplexed address/data bus

- Direct interface with MSM80C85AH

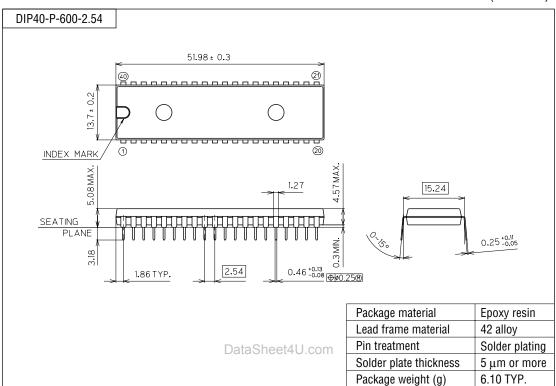

- 40-pin Plastic DIP (DIP40-P-600-2.54): (Product name: MSM81C55-5RS)

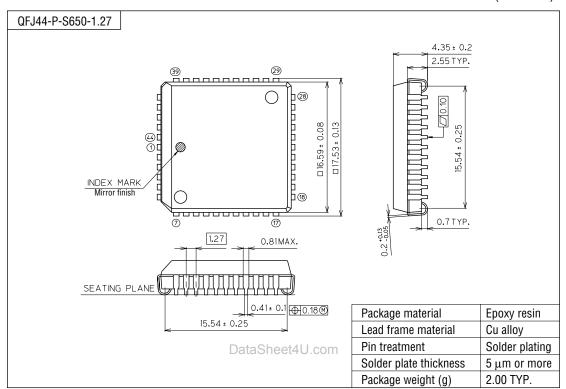

- 44-pin Plastic QFJ (QFJ44-P-S650-1.27): (Product name: MSM81C55-5JS)

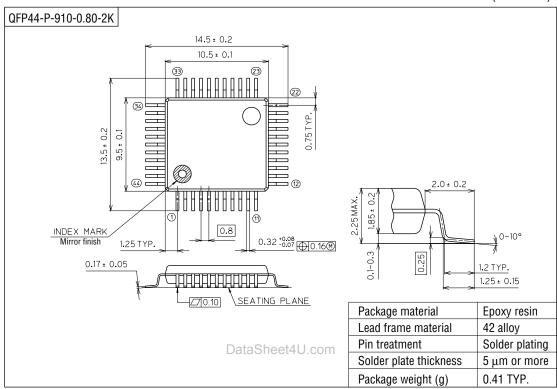

- 44-pin Plastic QFP (QFP44-P-910-0.80-2K): (Product name: MSM81C55-5GS-2K)

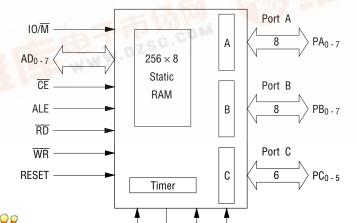

#### FUNCTIONAL BLOCK DIAGRAM

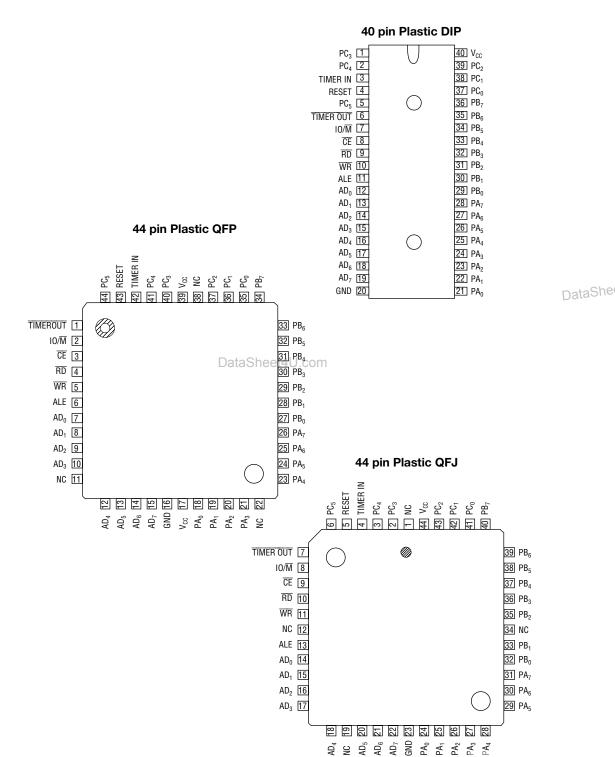

## PIN CONFIGURATION (TOP VIEW)

## **ABSOLUTE MAXIMUM RATING**

| Daramatar            | Parameter Symbol |                      | Conditions                   |              |              |      |  |

|----------------------|------------------|----------------------|------------------------------|--------------|--------------|------|--|

| Parameter            | Syllibol         | Conditions           | MSM81C55-5RS                 | MSM81C55-5GS | MSM81C55-5JS | Unit |  |

| Power Supply Voltage | V <sub>CC</sub>  | Deferenced           | −0.5 to +7                   |              |              | V    |  |

| Input Voltage        | V <sub>IN</sub>  | Referenced<br>to GND | -0.5 to V <sub>CC</sub> +0.5 |              |              | V    |  |

| Output Voltage       | V <sub>OUT</sub> | to divid             | -0.5 to V <sub>CC</sub> +0.5 |              |              | V    |  |

| Storage Temperature  | T <sub>STG</sub> | _                    | -55 to +150                  |              |              | °C   |  |

| Power Dissipation    | P <sub>D</sub>   | Ta = 25°C            | 1.0                          | 0.7          | 1.0          | W    |  |

## **OPERATING CONDITION**

| Parameter             | Symbol          | Range      | Unit |

|-----------------------|-----------------|------------|------|

| Power Supply Voltage  | V <sub>CC</sub> | 3 to 6     | V    |

| Operating Temperature | T <sub>OP</sub> | -40 to +85 | °C   |

# et4U.com

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                       | Symbol          | Sheelin. | Тур. | Max.                 | Unit |

|---------------------------------|-----------------|----------|------|----------------------|------|

| Power Supply Voltage (81C55)    | V <sub>CC</sub> | 4.5      | 5    | 5.5                  | V    |

| Operating Temperature (81C55)   | T <sub>OP</sub> | -40      | +25  | +85                  | °C   |

| "L" Level Input                 | $V_{IL}$        | -0.3     | _    | +0.8                 | V    |

| "H" Level Input                 | $V_{IH}$        | 2.2      | _    | V <sub>CC</sub> +0.3 | V    |

| Supply Voltage (81C55-5)        | $V_{CC}$        | 4.75     | 5    | 5.25                 | V    |

| Operating Temperature (81C55-5) | $V_{OP}$        | -40      | +25  | +70                  | °C   |

#### DC CHARACTERISTICS

| Parameter                 | Symbol           | Cond                       | dition                           | Min. | Тур. | Max. | Unit |  |  |

|---------------------------|------------------|----------------------------|----------------------------------|------|------|------|------|--|--|

| "L" Level Output Voltage  | V <sub>OL</sub>  | I <sub>OL</sub> = 2 mA     |                                  | _    | _    | 0.45 | V    |  |  |

| "II" Lovel Output Voltage | V <sub>OH</sub>  | I <sub>OH</sub> = -400 μA  |                                  | 2.4  | _    | _    | V    |  |  |

| "H" Level Output Voltage  | VOH              | $I_{OH} = -40 \mu A$       |                                  | 4.2  | _    | _    | V    |  |  |

| Input Leak Current        | ILI              | $0 \le V_{IN} \le V_{CC}$  | V <sub>CC</sub> = 4.5 V to 5.5 V | -10  | _    | 10   | μΑ   |  |  |

| Output Leak Current       | I <sub>L0</sub>  | $0 \le V_{OUT} \le V_{CC}$ | Ta = -40°C to 85°C               | -10  | _    | 10   | μΑ   |  |  |

| Standby Current           | I <sub>CCS</sub> |                            |                                  | _    | 0.1  | 100  | μА   |  |  |

| Mean Operating<br>Current | Icc              | Memory cycle<br>time: 1 μs |                                  | _    | _    | 5    | μΑ   |  |  |

DataSheet4U.com

## **AC CHARACTERISTICS**

| Parameter                                         | Symbol                          | V <sub>CC</sub> = 4.5 V<br>Ta = -40 to<br>80C85AH 3 | +80°C | Ta = -40 to | $V_{CC}$ = 4.75 V to 5.25 V,<br>Ta = -40 to +70°C<br>80C85AH 5MHz I/F |    | Remarks       |

|---------------------------------------------------|---------------------------------|-----------------------------------------------------|-------|-------------|-----------------------------------------------------------------------|----|---------------|

|                                                   |                                 | Min.                                                | Max.  | Min.        | Max.                                                                  |    |               |

| Address/latch Setup Time                          | t <sub>AL</sub>                 | 50                                                  | _     | 37          | _                                                                     | ns |               |

| Latch/address Holt Time                           | t <sub>LA</sub>                 | 30                                                  | _     | 30          | _                                                                     | ns |               |

| Latch/read (write) Delay Time                     | t <sub>LC</sub>                 | 100                                                 | _     | 40          | _                                                                     | ns |               |

| Read/output Delay Time                            | t <sub>RD</sub>                 |                                                     | 170   | _           | 140                                                                   | ns |               |

| Address/output Delay Time                         | t <sub>AD</sub>                 |                                                     | 400   |             | 330                                                                   | ns |               |

| Latch Width                                       | t <sub>LL</sub>                 | 100                                                 | _     | 70          | _                                                                     | ns |               |

| Read/data Bus Floating Time                       | t <sub>RDF</sub>                | 0                                                   | 100   | 0           | 80                                                                    | ns |               |

| Read (write)/latch Delay Time                     | t <sub>CL</sub>                 | 20                                                  | _     | 20          | _                                                                     | ns |               |

| Read (write) Width                                | t <sub>CC</sub>                 | 250                                                 | _     | 200         | _                                                                     | ns |               |

| Data In/write Setup Time                          | t <sub>DW</sub>                 | 150                                                 | _     | 100         | _                                                                     | ns |               |

| Write/data-in Hold Time                           | t <sub>WD</sub>                 | 0                                                   | _     | 25          | _                                                                     | ns |               |

| Recovery Time                                     | t <sub>RV</sub>                 | 300                                                 | _     | 200         | _                                                                     | ns |               |

| Write/port Output Delay Time                      | t <sub>WP</sub>                 | _                                                   | 400   |             | 300                                                                   | ns |               |

| Port Input/read Setup Time                        | t <sub>PR</sub>                 | 70                                                  | _     | 50          | _                                                                     | ns | Load capaci-  |

| Read/port Input Hold Time                         | t <sub>RP</sub>                 | 50                                                  | _     | 10          | _                                                                     | ns | tance: 150 pF |

| Strobe/buffer Full Delay Time                     | t <sub>SBF</sub>                | ataSheet4                                           | 400   | _           | 300                                                                   | ns |               |

| Strobe Width                                      | t <sub>SS</sub>                 | 200                                                 | _     | 150         | _                                                                     | ns |               |

| Strobe/buffer Empty Delay Time                    | t <sub>RBE</sub>                | _                                                   | 400   | -           | 300                                                                   | ns |               |

| Strobe/interrupt-on Delay Time                    | t <sub>SI</sub>                 | _                                                   | 400   | _           | 300                                                                   | ns |               |

| Read/interrupt-off Delay Time                     | t <sub>RDI</sub>                | _                                                   | 400   |             | 300                                                                   | ns |               |

| Port Input/strobe Setup Time                      | t <sub>PSS</sub>                | 50                                                  | _     | 20          | _                                                                     | ns |               |

| Strobe/port-input Hold Time                       | t <sub>PHS</sub>                | 120                                                 | _     | 100         | _                                                                     | ns |               |

| Strobe/buffer-empty Delay Time                    | t <sub>SBE</sub>                | _                                                   | 400   | -           | 300                                                                   | ns |               |

| Write/buffer-full Delay Time                      | t <sub>WBF</sub>                | _                                                   | 400   |             | 300                                                                   | ns |               |

| Write/interrupt-off Delay Time                    | t <sub>WI</sub>                 | _                                                   | 400   | _           | 300                                                                   | ns |               |

| Time Output Delay Time Low                        | t <sub>TL</sub>                 | _                                                   | 400   |             | 300                                                                   | ns |               |

| Time Output Delay Time High                       | t <sub>TH</sub>                 | _                                                   | 400   |             | 300                                                                   | ns |               |

| Read/data Buse Enable Delay Time                  | t <sub>RDE</sub>                | 10                                                  | _     | 10          | _                                                                     | ns |               |

| Timer Cycle Time                                  | t <sub>CYC</sub>                | 320                                                 | _     | 320         | _                                                                     | ns |               |

| Timer Input Rise and Fall Times                   | t <sub>r</sub> , t <sub>f</sub> | _                                                   | 80    |             | 80                                                                    | ns |               |

| Timer Input Low Level Time                        | t <sub>1</sub>                  | 80                                                  | _     | 40          | _                                                                     | ns |               |

| Timer Input High Level Time                       | t <sub>2</sub>                  | 120                                                 | _     | 70          | _                                                                     | ns | 1             |

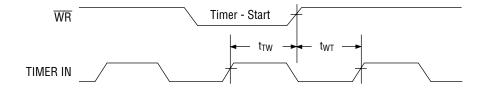

| WRITE to TIMER-IN for writes which start counting | t <sub>WT</sub>                 | 200                                                 | _     | 200         | _                                                                     | ns |               |

| TIMER-IN to WRITE for writes which start counting | t <sub>TW</sub>                 | 0                                                   | _     | 0           | _                                                                     | ns |               |

Note: Timings are measured wth  $V_L$  = 0.8 V and  $V_H$  = 2.2 V for both input and output.

as Comments

DataSheet4U.com

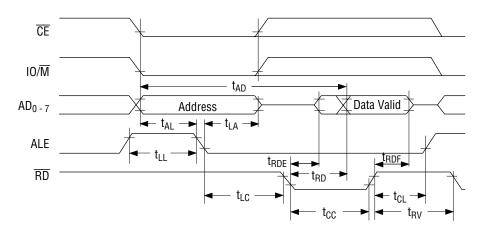

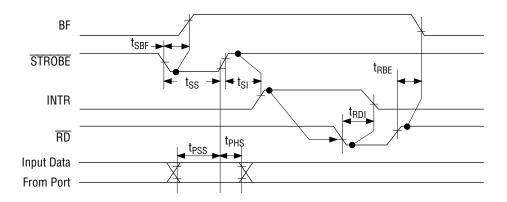

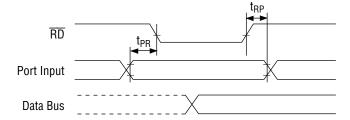

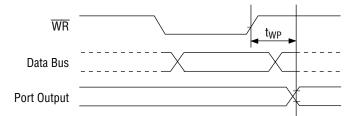

## **TIMING DIAGRAM**

## **Read Cycle**

et4U.com

DataShe

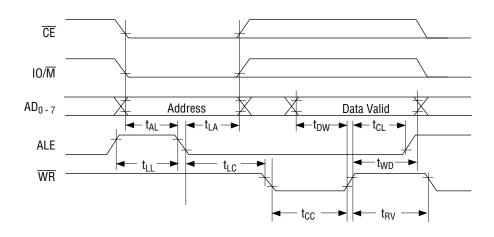

## **Write Cycle**

## **Strobe Input Mode**

# Strobe Output Mode

BF ◆ t<sub>SBE</sub> → STROBE DataShect4U.com INTR  $\overline{\mathsf{WR}}$ twp Output Data -To Port -

## MSM81C55-5RS/GS/JS

#### **Basic Input Mode**

## **Basic Output Mode**

et4U.com

**Note:** The DATA BUS timing is the same as the read and write cycles. DataSheet4U.com

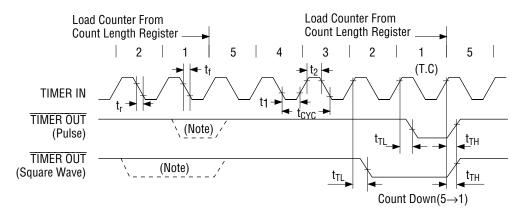

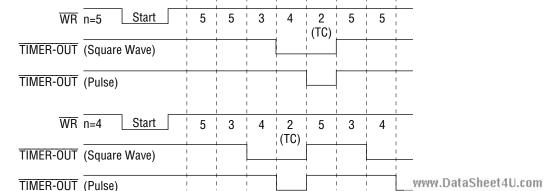

#### **Timer Waveforms 1**

**Note:** Periodically outut according to the output mode (m1=1) programming contents.

ma Pen and

#### **OKI** Semiconductor

## MSM81C55-5RS/GS/JS

#### **Timer Waveforms 2**

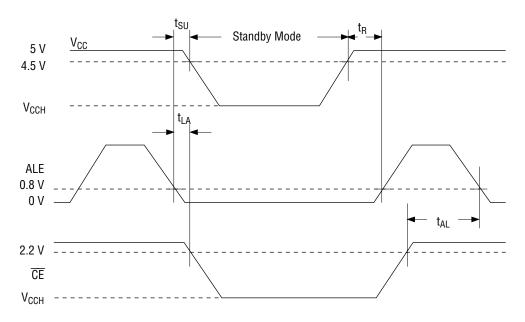

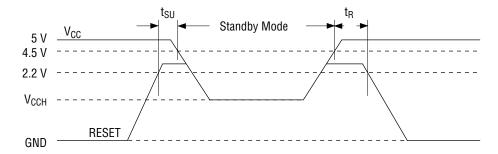

#### RAM DATA HOLD CHARACTERISTICS AT LOW SUPPLY VOLTAGE

| lk                          | Compleal         | O a maditi a m                                               | Specification |      |      | 11   |

|-----------------------------|------------------|--------------------------------------------------------------|---------------|------|------|------|

| Item                        | Symbol           | Condition                                                    | Min.          | Тур. | Max. | Unit |

| Data Holding Supply Voltage | V <sub>CCH</sub> | $V_{IN} = 0 \text{ V or } V_{CC}, \text{ ALE} = 0 \text{ V}$ | 2.0           | _    | _    | V    |

| Data Holding Supply Current | I <sub>CCH</sub> | $V_{CC} = V_{CCH}$ , ALE = 0<br>$V_{IN} = 0$ V or $V_{CC}$   | _             | 0.05 | 20   | μА   |

| Setup Time                  | t <sub>SU</sub>  |                                                              | 30            | _    |      | ns   |

| Hold Time                   | t <sub>R</sub>   |                                                              | 20            | _    | _    | ns   |

DataShe

DataSheet4U.com

## Two ways to place device in standby mode:

## (1) Method using $\overline{CE}$

DataSheet+O.com

## (2) Method using RESET

Note: In this case, the C/S register is reset, the port is set into the input mode, and the timer stops.

#### PIN FUNCTION

et4U.com

| Symbol                                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                                         | A high level input to this pin resets the chip, places all three I/O ports in the input mode, resets all output latches and stops timer.                                                                                                                                                                                                                                                                                                   |

| ALE                                           | Negative going edge of the ALE (Address Latch Enable) input latches $AD_{0-7}$ , $IO/\overline{M}$ , and $\overline{CE}$ signals into the respective latches. DataSheet4U.com                                                                                                                                                                                                                                                              |

| AD <sub>0 - 7</sub>                           | Three-state, bi-directional address/data bus. Eight-bit address information on this bus is read into the internal address latch at the negative going edge of the ALE. Eight bits of data can be read from or written to the chip using this bus depending on the state of the WRITE or READ input.                                                                                                                                        |

| CE                                            | When the $\overline{\text{CE}}$ input is high, both read and write operations to the chip are disabled.                                                                                                                                                                                                                                                                                                                                    |

| IO/M                                          | A high level input to this pin selects the internal I/O functions, and a low level selects the memory.                                                                                                                                                                                                                                                                                                                                     |

| RD                                            | If this pin is low, data from either the memory or ports is read onto the $AD_{0-7}$ lines depending on the state of the $IO/\overline{M}$ line.                                                                                                                                                                                                                                                                                           |

| WR                                            | If this pin is low, data on lines $AD_{0-7}$ is written into either the memory or into the selected port depending on the state of the line $IO/\overline{M}$ line.                                                                                                                                                                                                                                                                        |

| PA <sub>0 - 7</sub><br>(PB <sub>0 - 7</sub> ) | General-purpose I/O pins. Input/output directions can be determined by programming the command/status (C/S) register.                                                                                                                                                                                                                                                                                                                      |

| PC <sub>0 - 5</sub>                           | Three pins are usable either as general-purpose I/O pins or control pins for the PA and PB ports.  When used as control pins, they are assigned to the following functions:  PC <sub>0</sub> : A INTR (port A interrupt)  PC <sub>1</sub> : A BF (port A full)  PC <sub>2</sub> : A STB (port A strobe)  PC <sub>3</sub> : B INTR (port B interrupt)  PC <sub>4</sub> : B BF (port B buffer full)  PC <sub>5</sub> : B STB (port B strobe) |

| TIMER IN                                      | Input to the counter/timer                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TIMER OUT                                     | Timer output. When the present count is reached during timer operation, this pin provides a square-wave or pulse output depending on the programmed control status.                                                                                                                                                                                                                                                                        |

| V <sub>CC</sub>                               | 3–6V power supply                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GND                                           | GND                                                                                                                                                                                                                                                                                                                                                                                                                                        |

m 280

DataSheet4U.com

#### **OPERATION**

#### **Description**

The MSM81C55-5 has three functions as described below.

- 2K-bit static RAM (256 words × 8 bits)

- Two 8-bit I/O ports (PA and PB) and a 6-bit I/O port (PC)

- 14-bit timer counter

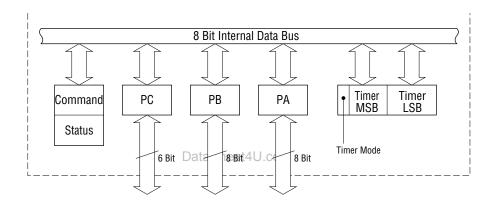

The internal register is shown in the figure below, and the I/O addresses are described in the table below.

DataShe

|                       |                       |                       | I/O Ac                | ldress                |                |                       | Colontina Domintos |                                                               |  |

|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|-----------------------|--------------------|---------------------------------------------------------------|--|

| <b>A</b> <sub>7</sub> | <b>A</b> <sub>6</sub> | <b>A</b> <sub>5</sub> | <b>A</b> <sub>4</sub> | <b>A</b> <sub>3</sub> | A <sub>2</sub> | <b>A</b> <sub>1</sub> | A <sub>0</sub>     | Selecting Register                                            |  |

| ×                     | ×                     | ×                     | ×                     | ×                     | 0              | 0                     | 0                  | Internal command/status register                              |  |

| ×                     | ×                     | ×                     | ×                     | ×                     | 0              | 0                     | 1                  | Universal I/O port A (PA)                                     |  |

| ×                     | ×                     | ×                     | ×                     | ×                     | 0              | 1                     | 0                  | Universal I/O port B (PB)                                     |  |

| ×                     | ×                     | ×                     | ×                     | ×                     | 0              | 1                     | 1                  | I/O port C (PC)                                               |  |

| ×                     | ×                     | ×                     | ×                     | ×                     | 1              | 0                     | 0                  | Timer count lower position 8 bits (LSB)                       |  |

| ×                     | ×                     | ×                     | ×                     | ×                     | 1              | 0                     | 1                  | Timer count upper position 6 bits and timer mode 2 bits (MSB) |  |

×: Don't care.

Dataoneet 40.com

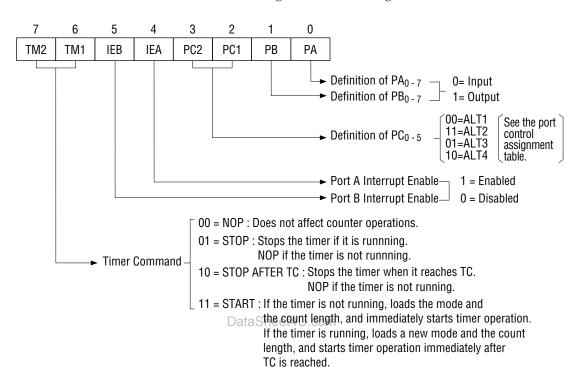

## (1) Programming the Command/Status (C/S) Register

The contents of the command register can be written during an I/O cycle by addressing it with an I/O address of xxxxx000. Bit assignments for the register are shown below:

#### **Port Control Assignment Table**

| Pin             | ALT1       | ALT2        | ALT3        | ALT4   |

|-----------------|------------|-------------|-------------|--------|

| PC <sub>0</sub> | Input port | Output port | A INTR      | A INTR |

| PC <sub>1</sub> | Input port | Output port | A BF        | A BF   |

| PC <sub>2</sub> | Input port | Output port | A STB       | A STB  |

| PC <sub>3</sub> | Input port | Output port | Output port | B INTR |

| PC <sub>4</sub> | Input port | Output port | Output port | B BF   |

| PC <sub>5</sub> | Input port | Output port | Output port | B STB  |

as Pen Agan

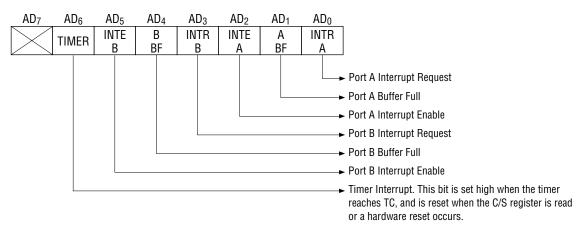

#### (2) Reading the C/S Register

The I/O and timer status can be accessed by reading the contents of the Status register located at I/O address xxxxx000. The status word format is shown below:

et4U.com

DataShe

#### (3) PA and PB Registers

These registers may be used as either input or output ports depending on the programmed contents of the C/S register. They may also be used either in the basic mode or in the strobe mode.

DataSheet4U.com

I/O address of the PA register: xxxxx001 I/O address of the PB register: xxxxx010

## (4) PC Register

The PC register may be used as an input port, output port or control register depending on the programmed contents of the C/S register. The I/O address of the PC register is xxxxx011.

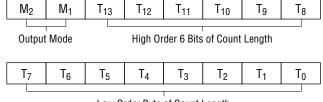

## (5) Timer

The timer is a 14-bit down counter which counts TIMER IN pulses.

The low order byte of the timer register has an I/O address of xxxxx100, and the high order byte of the register has an I/O address of xxxxx101.

The count length register (CLR) may be preset with two bytes of data. Bits 0 through 13 are assigned to the count length and bits 14 and 15 specify the timer output mode. A read operation of the CLR reads the contents of the counter and the pertinent output mode. The initial value range which can initially be loaded into the counter is 2 through 3FFF hex. Bit assignments to the timer counter and possible output modes are shown in the following.

Low Order Byte of Count Length

ma Pen

DataShe

#### **OKI** Semiconductor

| $M_2$ | $M_1$ |                                                                                |

|-------|-------|--------------------------------------------------------------------------------|

| 0     | 0     | Outputs a low-level signal in the latter half (Note 1) of a count period.      |

| 0     | 1     | Outputs a low-level signal in the latter half of a count period, automatically |

|       |       | loads the programmed count length, and restarts counting when the TC           |

|       |       | value is reached.                                                              |

| 1     | 0     | Outputs a pulse when the TC value is reached.                                  |

| 1     | 1     | Outputs a pulse each time the preset TC value is reached, automatically        |

|       |       | loads the programmed count length, and restarts from the beginning.            |

Notes: 1. When counting an asymmetrical value such as (9), a high level is output during the first period of five, and a low level is output during the second period of four.

2. If an internal counter of the MSM81C55-5 receives a reset signal, count operation stops but the counter is not set to a specific initial value or output mode. When restarting count operation after reset, the START command must be executed again through the C/S register.

Note that while the counter is counting, you may load a new count and mode into the CLR. Before the new count and mode will be used by the counter, you must issue a START command to the counter. Please note the timer circuit on the MSM81C55-5 is designed to be a square-wave timer, not a event counter. To achieve this, it counts down by twos twice in completing one cycle. Thus, its registers do not contain values directly representing the number of TIMER IN pulse received. After the timer has started counting down, the values residing in the count registers can be used to calculate the actual number of TIMER IN pulse required to complete the timer cycle if desired. To obtain the remaining count, perform the following operations in order.

et4U.com

- 1. STOP the counter

- 2. Read in the 16-bit value from the count registers.

- 3. Reset the upper two mode bits

- 4. Reset the carry and rotate right one position all 16 bits through carry

- 5. If carry is set, add 1/2 of the full original count (1/2 full count-1 if full count is odd).

Note: If you started with an odd count and you read the count registers before the third count pulse occurs, you will not be able to recognize whether one or two counts have occurred. Regardless of this, the MSM81C55-5 always counts out the right number of pulses in generating the TIMER OUT Waveforms. WR n=5 5 Start 5 3 2 5 (TC)

DataSheet4U.com

the value set in the CLD. Figures in the diagram refer to counter values

#### MSM81C55-5RS/GS/JS

#### (6) Standby Mode (see page 7)

The MSM81C55-5 is placed in standby mode when the high level at the  $\overline{\text{CE}}$  input is latched during the negative going edge of ALE. All input ports and the timer input should be pulled up or down to either  $V_{CC}$  or GND potential.

When using battery back-up, all ports should be set low or in input port mode. The timer output should be set low. Otherwise, a buffer should be added to the timer output and the battery should be connected to the power supply pins of the buffer.

By setting the reset input to a high level, the standby mode can be selected. In this case, the command register is reset, so the ports automatically set to the input mode and the timer stops.

et4U.com

DataShe

#### NOTICE ON REPLACING LOW-SPEED DEVICES WITH HIGH-SPEED DEVICES

The conventional low speed devices are replaced by high-speed devices as shown below. When you want to replace your low speed devices with high-speed devices, read the replacement notice given on the next pages.

| High-speed device (New) | Low-speed device (Old) | Remarks         |

|-------------------------|------------------------|-----------------|

| M80C85AH                | M80C85A/M80C85A-2      | 8bit MPU        |

| M80C86A-10              | M80C86A/M80C86A-2      | 16bit MPU       |

| M80C88A-10              | M80C88A/M80C88A-2      | 8bit MPU        |

| M82C84A-2               | M82C84A/M82C84A-5      | Clock generator |

| M81C55-5                | M81C55                 | RAM.I/O, timer  |

| M82C37B-5               | M82C37A/M82C37A-5      | DMA controller  |

| M82C51A-2               | M82C51A                | USART           |

| M82C53-2                | M82C53-5               | Timer           |

| M82C55A-2               | M82C55A-5              | PPI             |

et4U.com

DataShe

#### MSM81C55-5RS/GS/JS

#### Differences between MSM81C55-5 and MSM81C55

#### 1) Manufacturing Process

These devices use a 3  $\mu$  Si-CMOS.

#### 2) Design

These devices use the same chip. However, different outgoing inspection standards are used for these devices separately.

#### 3) Electrical Characteristics

"Oki's '96 Data Book for MICROCONTROLLER" describes that the MSM81C55-5 satisfies the electrical characteristics of the MSM81C55.

As shown above, the devices can be replaced without any trouble.

et4U.com

DataShe

#### PACKAGE DIMENSIONS

(Unit: mm)

et4U.com

DataShe

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

(Unit: mm)

DataShe

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

pataoneet 40.00m

et4U.com

#### **OKI** Semiconductor

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

Dataonecta com