**YAMAHA LSI**

# V6366 (PCDC)

## ■ OUTLINE

The PCDC (Panel Display & CRT Display Controller) is a display controller that has the two functions: (1) the display control of a high-capacity flat-panel display (hereafter referred to as a "Panel") and (2) the display control of a raster-scan type CRT. By merely performing initialization, however, even the Panel can be used without changing the software for conventional CRTs, enabling the simple system configuration of a handheld or portable computer which uses the Panel. (If so required, the PCDC can also be used to switch the display monitor between a CRT and a Panel.)

The PCDC is compatible with the CGA (Color Graphics Adapter), MDA (Monochrome Display Adapter), and HGC (Hercules Graphics Card), all for IBM PC application. In case the software and hardware for connecting a regular monitor come as a pair, the PCDC offers compatibility without requiring software changes (initialization is also unnecessary). Even in case of connecting different monitors, initialization will only be performed once at Power Start-Up, then compatibility will be available without requiring any software changes. It is thus possible, for example, to run CGA software using an IBM monochrome monitor and the Panel. (A gray scaling/hatching display can be used with a monochrome monitor.)

Because the PCDC has the display capacity of the IBM PC as well as numerous other expansion functions, including Kanji display, Color Palette, and the capability to simultaneously display up to 256 colors, a high-performance display system can be easily configured.

**YAMAHA CORPORATION**

**■ FEATURES**

- All functions of MC6845 are built in (excluding the Interlacing & Video Mode and the Skew function).

- In addition to a CRT or LCD, a EL and Plasma Display can also be connected.

- A 640 by 400 PEL Panel can be driven (a 720 by 350 PEL Panel can also be driven).

- A one-screen Panel or two-screen Panel (split into top and bottom halves) can be used.

- A two-screen panel allows, at a maximum duty, display of up to 512 lines (1/256).

- Selection of 1-, 2-, 4- or 8-bit parallel transmission of data to the Panel.

- A gray scaling/hatching display can be used with the Panel or a monochrome monitor.

- IBM PC software for 640 by 200 PELs can be directly displayed on a 640 by 400 PEL screen. (An 8 by 16 character font can be used, and can be displayed even in Double Scan Mode.)

- In addition to the standard IBM PC Graphics Modes, a variety of other Graphics Modes are provided: 320 by 200 PELs x 16 or 256 colors, 320 by 400 PELs x 4 or 16 colors, 640 by 200 PELs x 4 or 16 colors, 640 by 400 PELS x 4 colors, 640 by 350 PELs x 16 colors, and so on.

- A Protect Bit is provided for software protection.

- An SRAM or DRAM can be used as the VRAM. (Because the timing for display and the CPU are separate, the CPU can access VRAM at any time (without awaiting the retrace-timing.))

- Built-in interface for the Light Pen

- With a linear RGB monitor, 16 out of 512 colors can be simultaneously displayed.

- With an EGA monitor, 16 out of 64 colors can be simultaneously displayed.

- A Color Lookup Table can even be used with an IBM color monitor.

- A Standby function is provided to conserve power dissipation.

- Kanji display capacity of 16 by 16, 24 by 24 or 32 by 32 "PELs" (picture elements or pixels). (Attributes can also be used).

- The font configuration can be selected. Horizontal: 6, 7, 8, 9, 10, or [8 x integer] PELs (capable of a mixed display of half-width and full-width text); Vertical: 1 to 32 PELs.

- Capable of smooth scrolling and (in Interlace Mode only) external synchronization

- Simultaneous display capability with an IBM color monitor and a one-screen LCD of 640 x 200.

- CMOS, 5V power supply, 100-pin QFP or 84-pin PLCC

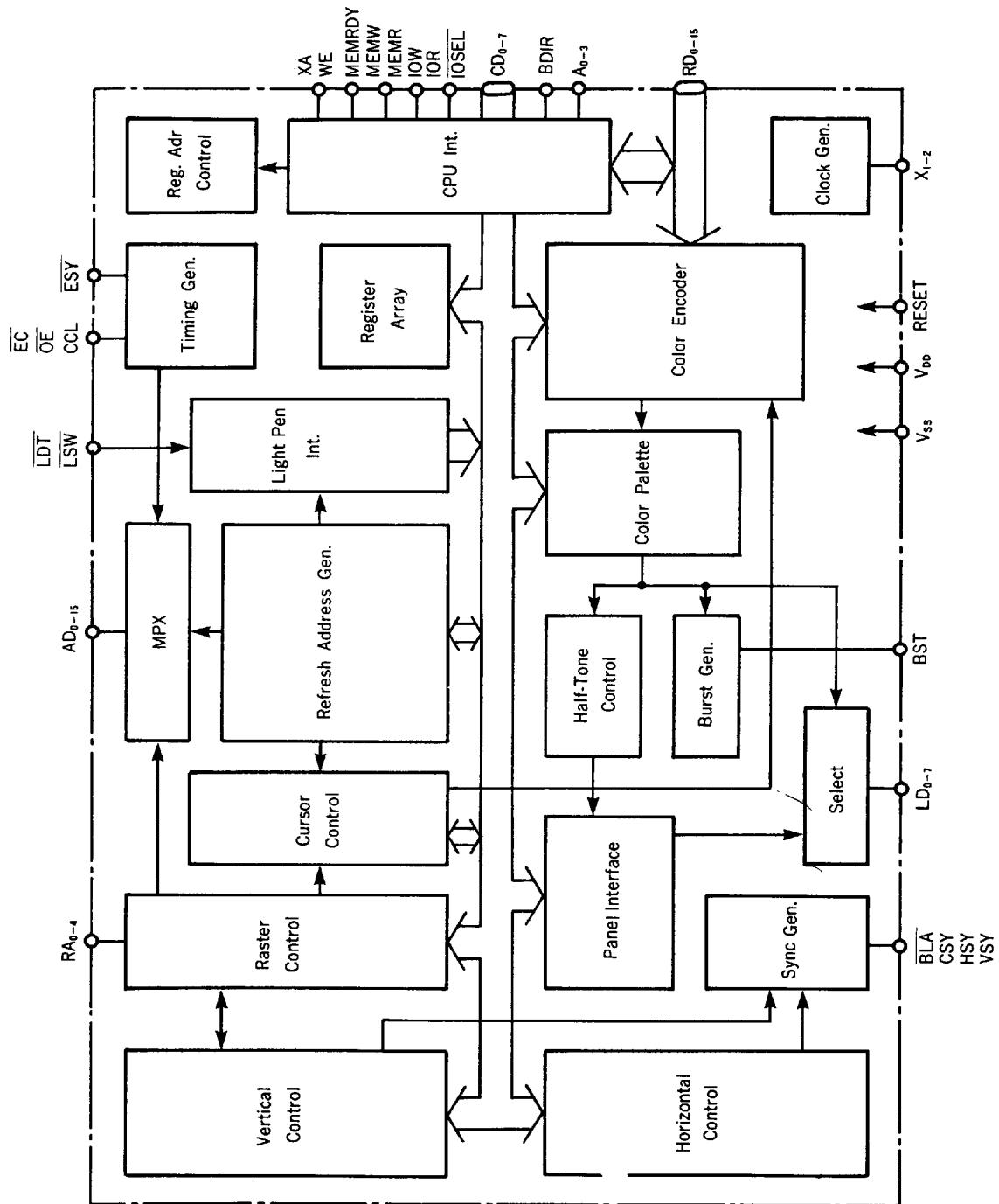

## ■ BLOCK DIAGRAM

## ■ DESCRIPTION OF TERMINAL FUNCTIONS

| Signal Name                                   | I/O                          | Terminal Functions                                                                                                                                                                                                                                                                               |

|-----------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0<br> <br>A3                                 | I                            | Address for I/O register selection. A0 is also used for selecting the high or low byte.                                                                                                                                                                                                          |

| CD0<br> <br>CD7                               | I/O<br>I/O                   | Data Bus for the CPU                                                                                                                                                                                                                                                                             |

| MEMRDY<br>MEMW<br>MEMR<br>IOW<br>IOR<br>IOSEL | O<br>I<br>I<br>I<br>I<br>I   | Read/Write Ready signal for the Memory ('0': Wait)<br>Controls writing to Memory<br>Controls reading from Memory<br>Controls writing to the I/O registers<br>Controls reading from the I/O registers<br>Enable signal to the I/O Register D and E ('0': Enable)                                  |

| RESET<br>LSW<br>LDT<br>X1<br>X2<br>BDIR       | I<br>I<br>I<br>I<br>I/O<br>O | Reset signal<br>Light Pen Switch signal (At RESET, specifies an 8- or 16-bit Data Bus for VRAM)<br>Light Pen Detection signal (At RESET, specifies VRAM from SRAM or DRAM)<br>For X'tal oscillation or external clock input<br>Direction control of the bi-direction buffer for the CPU Data Bus |

| RA0<br> <br>RA3<br>RA4                        | O<br>O<br>I/O                | Raster Address<br>Raster Address or AC Conversion signal (At RESET, specifies the Hercules or CGA Mode)                                                                                                                                                                                          |

| RD0<br> <br>RD7<br>RD8<br> <br>RD15           | I/O<br>I/O<br>I/O<br>I/O     | Data bus for VRAM (Low side)<br>Data bus for VRAM (High side)                                                                                                                                                                                                                                    |

| EC<br>OE<br>CCL<br>WE<br>XA                   | O<br>O<br>O<br>O<br>O        | Transmission control for the RD Bus of Character Font Data<br>Output control (for SRAM)<br>Latch clock for character codes<br>Controls writing of VRAM<br>CPU-related timing for VRAM                                                                                                            |

| Vss<br>Vss<br>Vdd<br>Vdd                      | I<br>I<br>I<br>I             | 0V<br>+5V                                                                                                                                                                                                                                                                                        |

| Signal Name                                                              | I/O | Terminal Functions              |           |   |                |                 |                 |  |  |

|--------------------------------------------------------------------------|-----|---------------------------------|-----------|---|----------------|-----------------|-----------------|--|--|

| AD <sub>0</sub> /XR                                                      | O   | CPU RAS Address timing for DRAM |           |   |                |                 |                 |  |  |

| AD <sub>1</sub> /XC                                                      | O   | CPU CAS Address timing for DRAM |           |   |                |                 |                 |  |  |

| AD <sub>2</sub> /RAS                                                     | O   | RAS for DRAM                    |           |   |                |                 |                 |  |  |

| AD <sub>3</sub> /CAS                                                     | O   | CAS for DRAM                    |           |   |                |                 |                 |  |  |

| AD <sub>4</sub>                                                          | O   |                                 |           |   |                |                 |                 |  |  |

| AD <sub>5</sub> /AD <sub>0</sub>                                         | O   |                                 |           |   |                |                 |                 |  |  |

| AD <sub>6</sub> /AD <sub>1</sub>                                         | O   |                                 |           |   |                |                 |                 |  |  |

| AD <sub>7</sub> /AD <sub>2</sub>                                         | O   |                                 |           |   |                |                 |                 |  |  |

| AD <sub>8</sub> /AD <sub>3</sub>                                         | O   | Addresses of SRAM               |           |   |                |                 |                 |  |  |

| AD <sub>9</sub> /AD <sub>4</sub>                                         | O   |                                 |           |   |                |                 |                 |  |  |

| AD <sub>10</sub> /AD <sub>5</sub>                                        | O   |                                 |           |   |                |                 |                 |  |  |

| AD <sub>11</sub> /AD <sub>6</sub>                                        | O   |                                 |           |   |                |                 |                 |  |  |

| AD <sub>12</sub> /AD <sub>7</sub>                                        | O   |                                 |           |   |                |                 |                 |  |  |

| AD <sub>13</sub>                                                         | O   |                                 |           |   |                |                 |                 |  |  |

| AD <sub>14</sub>                                                         | O   |                                 |           |   |                |                 |                 |  |  |

| AD <sub>15</sub> /GPE                                                    | O   | Addresses of DRAM               |           |   |                |                 |                 |  |  |

| Also, OR output of Bits 0 and 1 of the Control Register in Hercules Mode |     |                                 |           |   |                |                 |                 |  |  |

| LD <sub>4</sub>                                                          | O   | DB                              | Primary   | B | B <sub>0</sub> | LD <sub>4</sub> |                 |  |  |

| LD <sub>5</sub>                                                          | O   | DG                              | Primary   | G | B <sub>1</sub> | LD <sub>5</sub> |                 |  |  |

| LD <sub>6</sub>                                                          | O   | DR                              | Primary   | R | B <sub>2</sub> | LD <sub>6</sub> |                 |  |  |

| LD <sub>7</sub>                                                          | O   | DI                              | Secondary | G | G <sub>0</sub> | LD <sub>7</sub> |                 |  |  |

| LD <sub>0</sub>                                                          | O   | BFP                             |           | ← | G <sub>1</sub> | for linear      | LD <sub>0</sub> |  |  |

| LD <sub>1</sub>                                                          | O   |                                 |           |   | R <sub>0</sub> | RGB monitor     | LD <sub>1</sub> |  |  |

| LD <sub>2</sub>                                                          | O   |                                 | Secondary | R | R <sub>1</sub> |                 | LD <sub>2</sub> |  |  |

| LD <sub>3</sub>                                                          | O   | Video                           | Secondary | B | R <sub>2</sub> |                 | LD <sub>3</sub> |  |  |

| BLA                                                                      | O   | BLANK                           |           | ← |                |                 | HSY             |  |  |

| BST                                                                      | O   | Color Burst                     |           | ← |                |                 | SCK             |  |  |

| CSY                                                                      | O   | Composite Sync                  |           | ← |                |                 | VSY             |  |  |

| HSY                                                                      | O   | Horizontal synchronization      |           | ← |                |                 | (ECK)           |  |  |

| VSY                                                                      | O   | Vertical synchronization        |           | ← |                |                 |                 |  |  |

| ESY                                                                      | I/O | for external synchronization    |           |   |                |                 |                 |  |  |

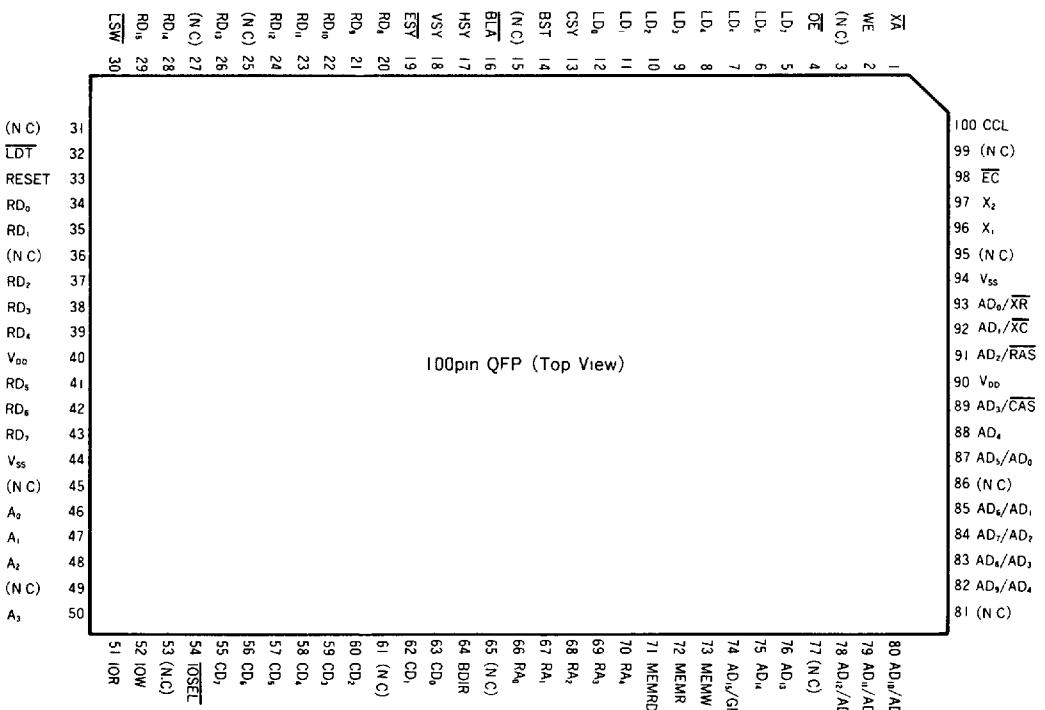

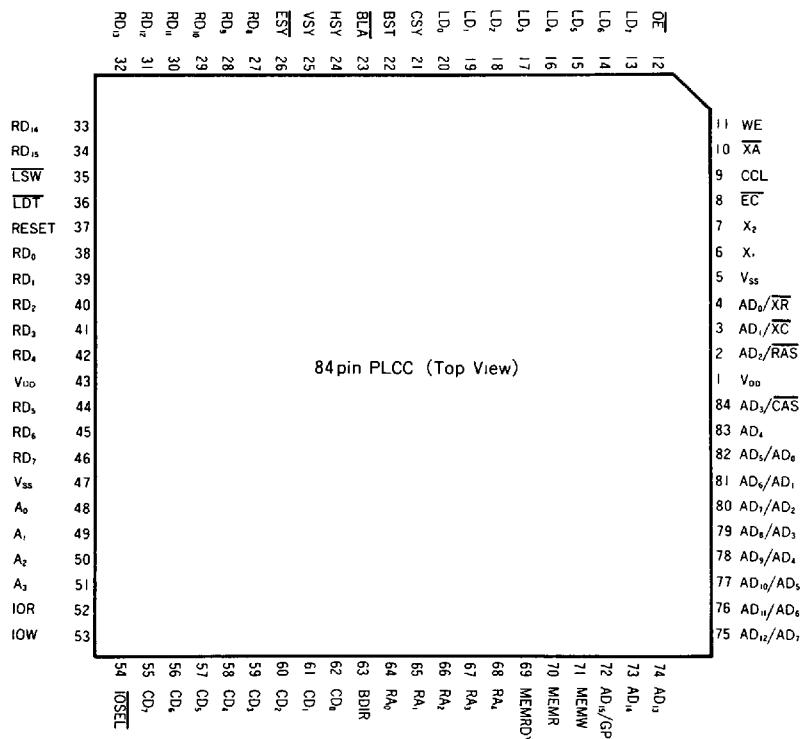

## ■ PIN ASSIGNMENT

**(1) 100pin QFP**

(2) 84pin PLCC

## ■ ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings

| Item                  | Symbol           | Min. | Max.                 | Unit |

|-----------------------|------------------|------|----------------------|------|

| Supply voltage        | V <sub>DD</sub>  | -0.3 | +7.0                 | V    |

| Input voltage         | V <sub>I</sub>   | -0.3 | V <sub>DD</sub> +0.3 | V    |

| Output voltage        | V <sub>O</sub>   | -0.3 | V <sub>DD</sub> +0.3 | V    |

| Operating temperature | T <sub>OP</sub>  | 0    | +70                  | °C   |

| Storage temperature   | T <sub>STG</sub> | -50  | +125                 | °C   |

(Based on the reference voltage of V<sub>SS</sub>=0.0V)

### Recommended Condition for Use

Supply voltage: +5V±5% (based on V<sub>SS</sub>=0.0V)

Operating temperature: 0~70°C

### DC Characteristics (V<sub>DD</sub>=5V±5%, T<sub>OP</sub>=0~70°C)

| Item                                         | Symbol           | Condition               | Min.                 | Max. | Unit |

|----------------------------------------------|------------------|-------------------------|----------------------|------|------|

| High-level output voltage (for TTL driving)  | V <sub>OH</sub>  | I <sub>OH</sub> =-0.4mA | 2.7                  |      | V    |

| Low-level output voltage (for TTL driving)   | V <sub>OL</sub>  | I <sub>OL</sub> =0.8mA  |                      | 0.4  | V    |

| High-level output voltage (for CMOS driving) | V <sub>OH</sub>  | I <sub>OH</sub>  <10μA  | V <sub>DD</sub> -0.4 |      | V    |

| Low-level output voltage (for CMOS driving)  | V <sub>OL</sub>  | I <sub>OL</sub>  <10μA  |                      | 0.4  | V    |

| High-level input voltage                     | V <sub>IH</sub>  |                         | 2.2                  |      | V    |

| Low-level input voltage                      | V <sub>IL</sub>  |                         |                      | 0.8  | V    |

| Input leak current                           | I <sub>IL</sub>  |                         | -10                  | 10   | μA   |

| OFF status leak current                      | I <sub>ILZ</sub> |                         | -10                  | 10   | μA   |

| Power current (during normal operation)      | I <sub>DD</sub>  |                         |                      | 70   | mA   |

| Power current (during Standby)               | I <sub>DD</sub>  |                         |                      | 10   | mA   |

NOTE: ILZ applies while the CD0-CD7, RD0-RD15, X2, RA4, or ESY pins are in input status or while the AD0/XR ~ AD15/GPE or MEMRDY pins are in high-impedance status.

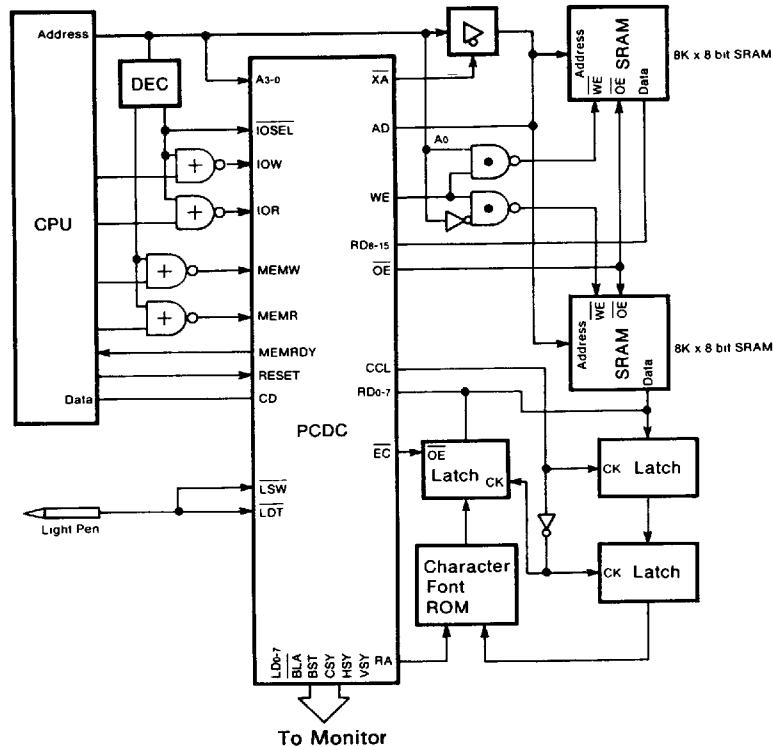

## ■ SYSTEM CONFIGURATIONS

### (1) Use of SRAM (For 16-Bit Bus, CGA)

### (2) Use of DRAM (For 8-Bit Bus, Hercules)

## ■ PACKAGE OUTLINES

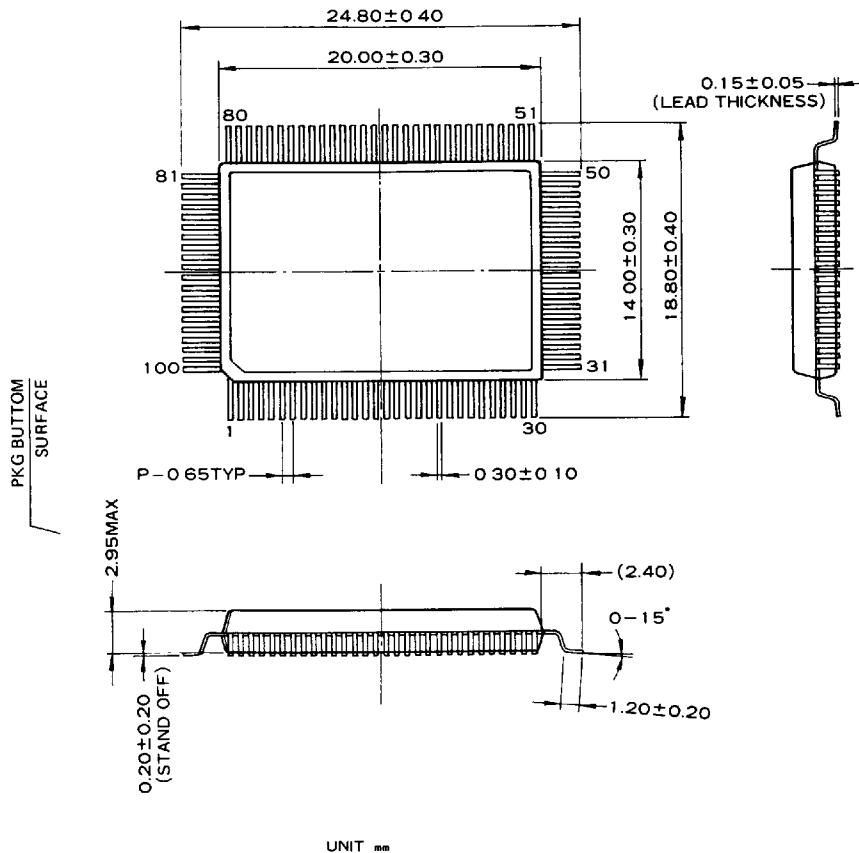

### (1) 100pin QFP

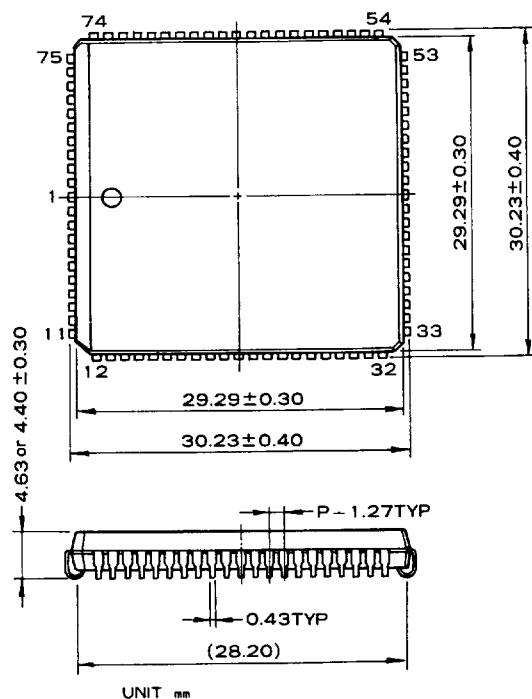

### (2) 84pin PLCC

The specifications of this product are subject to improvement changes without prior notice.

— AGENCY —

— YAMAHA CORPORATION —

— YAMAHA CORPORATION —

Address inquiries to:

Semi-conductor Sales Department

■ Head Office 203, Matsunokijima, Toyooka-mura,

Iwata-gun, Shizuoka-ken, 438-01

Electronic Equipment business section

Tel. 0539-62-4918 Fax. 0539-62-5054

■ Tokyo Office 2-17-11, Takanawa, Minato-ku,

Tokyo, 108

Tel. 03-5488-5431 Fax. 03-5488-5088

3-12-9, Minami Senba, Chuo-ku,

Osaka City, Osaka, 542

■ Osaka Office Shinsaibashi Plaza Bldg. 4F

Tel. 06-252-7980 Fax. 06-252-5615

■ U.S.A. Office YAMAHA Systems Technology.

100 Century Center Court, San Jose, CA95112

Tel. 408-467-2300 Fax. 408-437-8791