MATRA MHS

# HM 65764

# 8K × 8 High Speed CMOS SRAM

### **Description**

The HM 65764 is a high speed CMOS static RAM organized as 8192x8 bits. It is manufactured using MHS high performance CMOS technology.

Access times as fast as 15 ns are available with maximum power consumption of only 743 mW.

The HM 65764 features fully static operation requiring no external clocks or timing strobes. The automatic power-down feature reduces the power consumption by 73 % when the circuit is deselected.

Easy memory expansion is provided by active low chip select (CSI), an active high chip select (CS2), an active low output enable (OE) and three state drivers.

All inputs and outputs of the HM 65764 are TTL compatible and operate from single 5 V supply thus simplifying system design.

The HM 65764 is 100 % processed following the test methods of MIL STD 883C and/or ESA/SCC 9000 making it ideally suitable for military/space applications that demand superior levels of performance and reliability.

### **Features**

Fast Access Time

Commercial: 15/20/25/35/45/55 ns (max)

Industrial/Automotive/Military: 20/25/35/45/55 ns (max)

Low Power Consumption Active: 380 mW (typ)

Standby: 110 mW (typ)

Wide Temperature Range: -55°C to 125°C

- 300 and 600 Mils Width Package

- TTL Compatible Inputs and Outputs

- Asynchronous

- Capable Of Withstanding Greater Than 2000 V Electrostatic Discharge

- Single 5 Volt Supply

3.3 Volt version available (see L 65764 specification)

### Interface

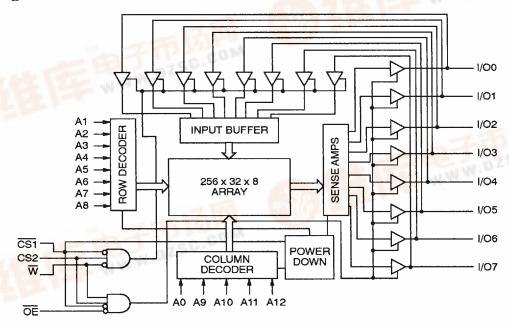

### **Block Diagram**

MATRA MHS

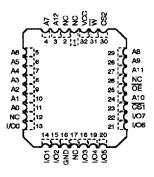

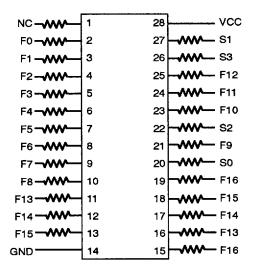

### **Pin Configuration**

SOIC & SOJ 300 mils, 28 pins, DIL. SOIC 330 mils, 28 pins Plastic 300 & 600 mils, 28 pins, DIL.

NC 1 28 VCC

A12 27 W

A7 3 26 CS2

A6 4 25 A8

A5 5 24 A9

A4 6 23 A11

A3 7 22 OE

A2 8 21 A10

A1 0 20 CS1

A0 0 19 1/07

1/00 11 18 U/06

1/01 12 17 U/05

1/02 13 16 U/04

GND 14 15 U/03

Pinout DIL/SOIC/SOJ 28 pins (top view)

Ceramic 300 mils, 600 mils, 28 pins, DIL LCC 32 pins

Pinout LCC 32 pins (top view)

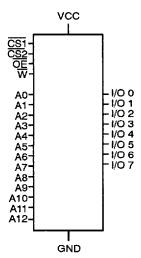

### **Logic Symbol**

### Pin Names

| A0-A13: A | ddress inputs    | CS1                     | : Chip-select 1 |

|-----------|------------------|-------------------------|-----------------|

| I/O0-I/O7 | : Inputs/Outputs | CS2                     | : Chip Select 2 |

| VCC       | : Power          | ŌĒ                      | : Output enable |

| GND       | : Ground         | $\overline{\mathbf{w}}$ | : Write enable  |

### **Truth Table**

| CSI | CS2 | ŌĒ | w | DATA- IN | DATA-<br>OUT | MODE              |

|-----|-----|----|---|----------|--------------|-------------------|

| Н   | X   | X  | X | Z        | Z            | Deselect          |

| L   | Н   | L  | Н | Z        | Valid        | Read              |

| L   | Н   | X  | L | Valid    | Z            | Write             |

| L   | Н   | Н  | Н | z        | Z            | Output<br>disable |

L = low - H = high - X = H or L - Z = High impedance.

2

### MATRA MHS

# HM 65764

### **Electrical Characteristics**

| Supply voltage to GND potential:0.5 V to +7.0 V   | Storage temperature:                                     |

|---------------------------------------------------|----------------------------------------------------------|

| DC input voltage :                                | Output current into outputs (low):                       |

| DC output voltage in high Z state:0.5 V to +7.0 V | Electro static discharge voltage: > 2000 V (MIL STD 883C |

|                                                   | method 3015.2)                                           |

## **Operating Range**

|            |      | OPERATING VOLTAGE | OPERATING TEMPERATURE |

|------------|------|-------------------|-----------------------|

| Military   | (-2) | 5 V ± 10 %        | - 55°C to + 125°C     |

| Automotive | (-A) | 5 V ± 10 %        | 40°C to + 125°C       |

| Industrial | (-9) | 5 V ± 10 %        | – 40°C to + 85°C      |

| Commercial | (-5) | 5 V ± 10 %        | 0°C to + 70°C         |

### **Recommended DC Operating Conditions**

| PARAMETER | DESCRIPTION        | MINIMUM | TYPICAL | MUMIXAM | UNIT |

|-----------|--------------------|---------|---------|---------|------|

| Vcc       | Supply Voltage     | 4.5     | 5.0     | 5.5     | v    |

| Gnd       | Ground             | 0.0     | 0.0     | 0.0     | v    |

| VIL       | Input low voltage  | - 3.0   | 0.0     | 0.8     | V    |

| VIH       | Input high voltage | 2.2     | -       | VCC     | v    |

## Capacitance

| PARAMETER | DESCRIPTION        | MINIMUM | TYPICAL | MAXIMUM | UNIT |

|-----------|--------------------|---------|---------|---------|------|

| Cin (1)   | Input capacitance  | -       | -       | 5       | pF   |

| Cout (1)  | Output capacitance | -       | -       | 7       | pF   |

Note: 1. TA = 25 \(\text{QC}\), f = 1 MHz, Vcc = 5.0 V, these parameters are not 100 % tested.

### **DC Parameters**

| PA  | RÁMETER | DESCRIPTION                  | MINIMUM | TYPICAL | MAXIMUM | UNIT |

|-----|---------|------------------------------|---------|---------|---------|------|

| пх  | (2)     | Input leakage current        | - 10.0  | -       | 10.0    | μΑ   |

| IOZ | (3)     | Output leakage current       | - 10.0  | -       | 10.0    | μА   |

| IOS | (3)     | Output short circuit current | -       | -       | - 300.0 | mA   |

| VOL | (4)     | Output low voltage           | -       | -       | 0.4     | V    |

| VOH | (5)     | Output high voltage          | 2.4     | _       | _       | V    |

Notes: 2. Gnd < Vin < Vcc, Gnd < Vout < Vcc output disabled.

- 3. Vcc = max, Vout = Gnd, duration of the short circuit should not exceed 30 seconds. Not more than 1 output should be shorted at one time.

- 4. Vec min, IOL = 8.0 mA.

- 5. Vcc min, IOH = -4.0 mA.

### Consumption for Commercial (-5) Specification

| SYMBOL        | PARAMETER                 | 65764<br>E-5 | 65764<br>F-5 | 65764<br>H-5 | 65764<br>K-5 | 65764<br>M-5 | 65764<br>N-5 | UNIT | VALUE |

|---------------|---------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------|-------|

| ICCSB<br>(6)  | Standby supply current    | 40           | 40           | 30           | 30           | 30           | 30           | mA   | max   |

| ICCSB1<br>(7) | Standby supply current    | 20           | 20           | 20           | 20           | 20           | 20           | mА   | max   |

| ICCOP<br>(8)  | Dynamic operating current | 135          | 125          | 125          | 125          | 125          | 125          | mA   | max   |

### Consumption for Industrial (-9), Automotive (-A) and Military (-2) Specifications

| SYMBOL        | PARAMETER                 | 65764<br>F-9/-2 | .65764<br>H-9/-2 | 65764<br>K-9/-2 | 65764<br>M-9/-2 | 65764<br>N-9/-2 | UNIT | VALUE |

|---------------|---------------------------|-----------------|------------------|-----------------|-----------------|-----------------|------|-------|

| ICCSB<br>(6)  | Standby supply current    | 40              | 40               | 30              | 30              | 30              | mA   | max   |

| ICCSB1<br>(7) | Standby supply current    | 20              | 20               | 20              | 20              | 20              | mA   | max   |

| ICCOP<br>(8)  | Dynamic operating current | 135             | 125              | 125             | 125             | 125             | mA   | max   |

Notes: 6.  $\overline{CS1} \ge VIH$ ,  $CS2 \le VIL$  min duty cycle = 100 %, a pull-up resistor to VCC on the  $\overline{CS}$  input is required to keep the device deselected during Vcc power-up otherwise IccSB will exceed above values.

- 7.  $\overline{\text{CS1}} \ge \text{Vec} -0.3 \text{ V. CS2} < 0.3 \text{ V. lout} = 0 \text{ mA}.$

- 8. Vcc max, Output current = 0 mA, f = max, Vin = Vcc or Gnd.

### **AC Parameters**

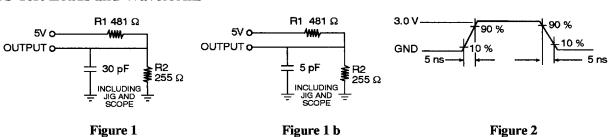

### **AC Conditions**

| Input pulse levels: | Input timing reference levels:                      |

|---------------------|-----------------------------------------------------|

| Input rise :        | Output loading IOL/IOH (see figure 1a and 1b)+30 pF |

### **AC Test Loads and Waveforms**

Equivalent to : THEVENIN EQUIVALENT

167 Ω OUTPUT **o \\\\\\\\\\\** o 1.73 V

### MATRA MHS

# HM 65764

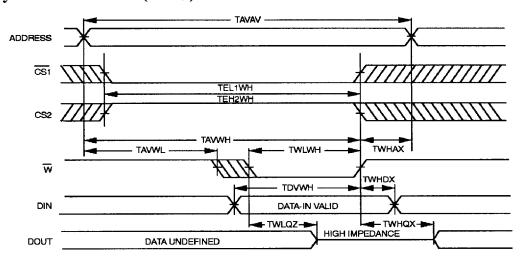

## Write Cycle: Commercial (-5) Specification

| SYMBOL       | PARAMETER                      | 65764<br>E-5 | 65764<br>F-5 | 65764<br>H-5 | 65764<br>K-5 | 65764<br>M-5 | 65764<br>N-5 | UNIT | VALUE |

|--------------|--------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------|-------|

| TAVAV        | Write cycle time               | 15           | 20           | 20           | 25           | 40           | 50           | ns   | min   |

| TAVWL        | Address set-up time            | 0            | 0            | 0            | 0            | 0            | 0            | ns   | min   |

| TAVWH        | Address valid to end write     | 12           | 15           | 20           | 25           | 30           | 40           | ns   | min   |

| TDVWH        | Data set-up time               | 10           | 10           | 10           | 15           | 15           | 25           | ns   | min   |

| TEL1WH       | CS1 low to write end           | 12           | 15           | 20           | 25           | 30           | 40           | ns   | min   |

| TEH2WH       | CS2 high to write end          | 12           | 15           | 20           | 20           | 25           | 30           | ns   | min   |

| TWLQZ (9)    | Write low to high Z            | 7            | 7            | 7            | 10           | 15           | 20           | ns   | max   |

| TWLWH        | Write pulse width              | 12           | 15           | 15           | 20           | 20           | 25           | ns   | min   |

| TWHAX        | Address hold from end of write | 0            | 0            | 0            | 0            | 0            | 0            | ns   | min   |

| TWHDX        | Data hold time                 | 0            | 0            | 0            | 0            | 0            | О            | ns   | min   |

| TWHQX (8, 9) | Write high to low Z            | 3            | 5            | 5            | 5            | 5            | 5            | ns   | min   |

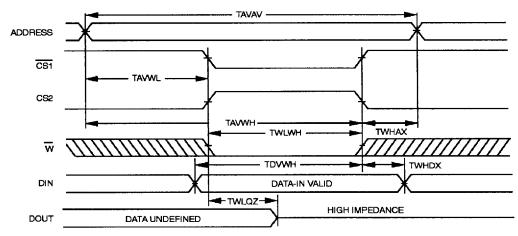

## Write Cycle: Industrial (-9), Automotive (-A) and Military (-2) Specifications

| SYMBOL       | PARAMETER                      | 65764<br>F-9/-2<br>/-A | 65764<br>H-9/-2<br>/-A | 65764<br>K-9/-2<br>/-A | 65764<br>M-9/-2<br>/-A | 65764<br>N-9/-2<br>/-A | UNIT | VALUE |

|--------------|--------------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------|-------|

| TAVAV        | Write cycle time               | 20                     | 20                     | 25                     | 40                     | 50                     | ns   | min   |

| TAVWL        | Address set-up time            | 0                      | 0                      | 0                      | 0                      | 0                      | ns   | min   |

| TAVWH        | Address valid to end of write  | 15                     | 20                     | 25                     | 30                     | 40                     | ns   | min   |

| TDVWH        | Data set-up time               | 10                     | 10                     | 15                     | 15                     | 25                     | ns   | min   |

| TEL1WH       | CS1 low to write end           | 15                     | 20                     | 25                     | 30                     | 40                     | ns   | min   |

| TEH2WH       | CS2 high to write end          | 15                     | 20                     | 20                     | 25                     | 30                     | ns   | min   |

| TWLQZ (8)    | Write low to high Z            | 7                      | 7                      | 10                     | 15                     | 20                     | ns   | max   |

| TWLWH        | Write pulse width              | 15                     | 15                     | 20                     | 20                     | 25                     | ns   | min   |

| TWHAX        | Address hold to end from write | 0                      | 0                      | 0                      | 0                      | 0                      | ns   | min   |

| TWHDX        | Data hold time                 | 0                      | 0                      | 0                      | 0                      | 0                      | ns   | min   |

| TWHQX (8, 9) | Write high to low Z            | 5                      | 5                      | 5                      | 5                      | 5                      | ns   | min   |

Note: 8. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

## Write Cycle 1 W Controlled (note 9)

## Write Cycle 2 CS1 Controlled (note 9)

Note: 9. The internal write time of the memory is defined by the overlap of  $\overline{CE}$  LOW and  $\overline{WE}$  LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input setup and hold timing should be referenced to the rising edge of the signal that terminates the write. Data out is HIGH impedance if  $\overline{OE} = VIH$ .

### MATRA MHS

# HM 65764

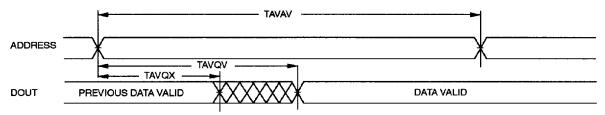

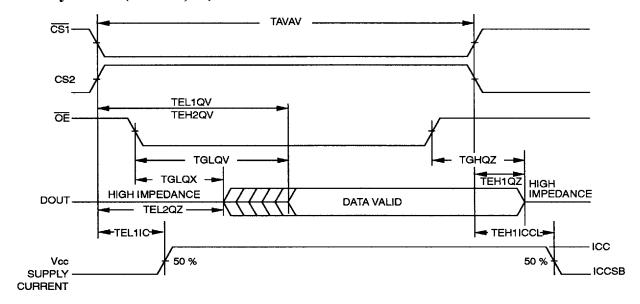

## Read Cycle: Commercial (-5) Specification

| SYMBOL      | PARAMETER                 | 65764<br>E-5 | 65764<br>F-5 | 65764<br>H-5 | 65764<br>K-5 | 65764<br>M-5 | 65764<br>N-5 | UNIT | VALUE |

|-------------|---------------------------|--------------|--------------|--------------|--------------|--------------|--------------|------|-------|

| TAVAV       | READ cycle time           | 15           | 20           | 25           | 35           | 45           | 55           | ns   | min   |

| TAVQV       | Address access time       | 15           | 20           | 25           | 35           | 45           | 55           | ns   | max   |

| TAVQX       | Address valid to low Z    | 3            | 3            | 3            | 3            | 3            | 3            | ns   | min   |

| TEL1QV      | Chip-select 1 access time | 15           | 20           | 25           | 35           | 45           | 55           | ns   | max   |

| TEH2QV      | Chip-select 2 access time | 15           | 20           | 25           | 25           | 30           | 40           | ns   | max   |

| TEL1QX      | CS1 low to low Z          | 3            | 5            | 5            | 5            | 5            | 5            | ns   | min   |

| TEH2QX      | CS2 high to high Z        | 3            | 3            | 3            | 3            | 3            | 3            | ns   | min   |

| TEH1QZ (11) | CS1 high to high Z        | 8            | 8            | 10           | 15           | 15           | 20           | ns   | max   |

| TEL2QZ (11) | CS2 low to high Z         | 8            | 8            | 10           | 15           | 15           | 20           | ns   | max   |

| TEL1IC      | CS1 low to power up       | 0            | 0            | 0            | 0            | 0            | 0            | ns   | min   |

| TEH1ICCL    | CS1 high to power down    | 15           | 20           | 20           | 20           | 25           | 25           | ns   | max   |

| TGLQV       | Output enable access time | 10           | 10           | 12           | 15           | 20           | 25           | ns   | max   |

| TGLQX       | OE low to low Z           | 3            | 3            | 3            | 3            | 3            | 3            | ns   | min   |

| TGHQZ       | OE high to high Z         | 8            | 8            | 10           | 12           | 15           | 20           | ns   | max   |

# Read Cycle: Industrial (-9), Automotive (-A) and Military (-2) Specifications

| SYMBOL      | PARAMETER                 | 65764<br>F-9/2<br>/-A | 65764<br>H-9/-2<br>/-A | 65764<br>K-9/-2<br>/-A | 65764<br>M-9/-2<br>/-A | 65764<br>N-9/-2<br>/-A | UNIT | VALUE |

|-------------|---------------------------|-----------------------|------------------------|------------------------|------------------------|------------------------|------|-------|

| TAVAV       | READ cycle time           | 20                    | 25                     | 35                     | 45                     | 55                     | ns   | min   |

| TAVQV       | Address access time       | 20                    | 25                     | 35                     | 45                     | 55                     | ns   | max   |

| TAVQX       | Address valid to low Z    | 3                     | 3                      | 3                      | 3                      | 3                      | ns   | min   |

| TEL1QV      | Chip-select 1 access time | 20                    | 25                     | 35                     | 45                     | 55                     | ns   | max   |

| TEH2QV      | Chip-select 2 access time | 20                    | 25                     | 25                     | 30                     | 40                     | ns   | max   |

| TEL1QX      | CS1 low to low Z          | 5                     | 5                      | 5                      | 5                      | 5                      | ns   | min   |

| TEH2QX      | CS2 high to high Z        | 3                     | 3                      | 3                      | 3                      | 3                      | ns   | min   |

| TEH1QZ (11) | CS1 high to high Z        | 8                     | 10                     | 15                     | 15                     | 20                     | ns   | max   |

| TEL2QZ (11) | CS2 high to high Z        | 8                     | 10                     | 15                     | 15                     | 20                     | ns   | max   |

| TEL1IC      | CSI low to power up       | 0                     | 0                      | 0                      | 0                      | 0                      | ns   | min   |

| TEH1ICCL    | CS1 high to power down    | 20                    | 20                     | 20                     | 25                     | 25                     | ns   | max   |

| TGLQV       | Output enable access time | 10                    | 12                     | 15                     | 20                     | 25                     | ns   | max   |

| TGLQX       | OE low to low Z           | 3                     | 3                      | 3                      | 3                      | 3                      | ns   | min   |

| TGHQZ       | OE high to high Z         | 8                     | 10                     | 12                     | 15                     | 20                     | ns   | min   |

MATRA MHS

## Read Cycle nb 1 (notes 10, 11)

### Read Cycle nb 2 (notes 10, 12)

Notes: 10.  $\overline{W}$  is HIGH for read cycle.

- 11. Device is continuously selected.  $\overline{CS}_1 \& \overline{OE} = VIL$  and  $CS_2 = VIH$ .

- 12. Address valid prior to or coincident with  $\overline{CS}_1$  transition low.

### MATRA MHS

# HM 65764

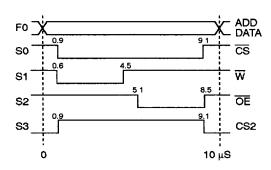

#### **Burn-in Schematics**

Vcc = 5V(-0, +0.5)

$R = 1K\Omega$  per pin

$FO = 50KHz \pm 20\%$

Fn = 1/2 Fn - 1

S0 to S3 = programmable signals for write/read cycles.

NC: Not Connected.

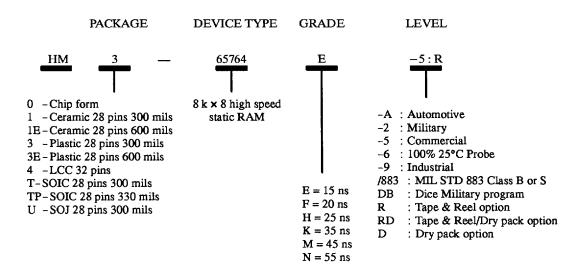

## **Ordering Information**

The information contained herein is subject to change without notice. No responsibility is assumed by MATRA MHS SA for using this publication and/or circuits described herein: nor for any possible infringements of patents or other rights of third parties which may result from its use.