## Data Sheet Summary

MC68HC908QY4SM/D 9/2002

MC68HC908QY4, MC68HC908QY2, MC68HC908QY2, MC68HC908QY1, MC68HC908QY1, MC68HC908QT1

### Introduction

This document provides an overview of the MC68HC908QY4, MC68HC908QT4, MC68HC908QY2, MC68HC908QT2, MC68HC908QY1, and MC68HC908QT1 devices. For complete details refer to the *MC68HC908QY4 Data Sheet* (Motorola document order number MC68HC908QY4/D).

## **General Description**

The MC68HC908QY4 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). The M68HC08 Family is a Complex Instruction Set Computer (CISC) with a Von Neumann architecture. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

**Table 1. MC Order Numbers**

| MC Order Number | ADC | FLASH Memory | Package                |

|-----------------|-----|--------------|------------------------|

| MC68HC908QY1    | _   | 1536 bytes   | 16-pins                |

| MC68HC908QY2    | Yes | 1536 bytes   | PDIP, SOIC,            |

| MC68HC908QY4    | Yes | 4096 bytes   | and TSSOP              |

| MC68HC908QT1    |     | 1536 bytes   |                        |

| MC68HC908QT2    | Yes | 1536 bytes   | 8-pins<br>PDIP or SOIC |

| MC68HC908QT4    | Yes | 4096 bytes   |                        |

Temperature and package designators:

$C = -40^{\circ}C \text{ to } +85^{\circ}C$

V = -40°C to +105°C (available for  $V_{DD} = 5 V$  only)

M = -40°C to +125°C (available for  $V_{DD} = 5$  V only)

P = Plastic dual in-line package (PDIP)

DW = Small outline integrated circuit package (SOIC)

DT = Thin shrink small outline package (TSSOP)

#### **Features**

#### Features include:

- High-performance M68HC08 CPU core

- Fully upward-compatible object code with M68HC05 Family

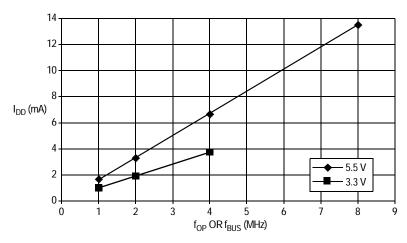

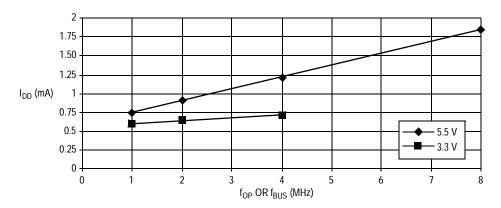

- 5-V and 3-V operating voltages (V<sub>DD</sub>)

- 8-MHz internal bus operation at 5 V, 4-MHz at 3 V

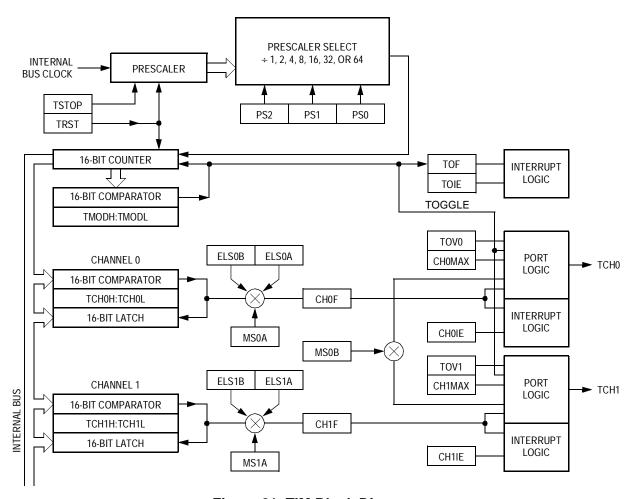

- Trimmable internal oscillator

- 3.2 MHz internal bus operation

- 8-bit trim capability, ± 5% trimmed

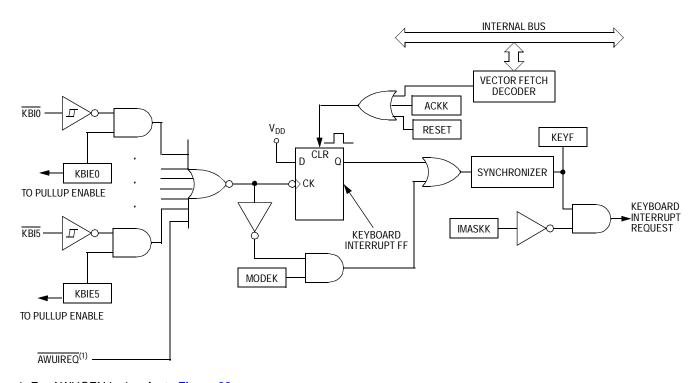

- Auto wake-up from STOP capability

- Configuration (CONFIG) register for MCU configuration options, including low-voltage inhibit (LVI) trip point

- In-system FLASH programming

- FLASH security<sup>(1)</sup>

- On-chip in-application programmable FLASH memory (with internal program/erase voltage generation)

- MC68HC908QY4 and MC68HC908QT4 4096 bytes

- MC68HC908QY2, MC68HC908QY1, MC68HC908QT2, and MC68HC908QT1 — 1536 bytes

- 128 bytes of on-chip random-access memory (RAM)

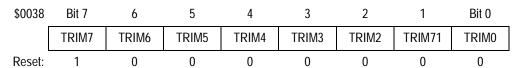

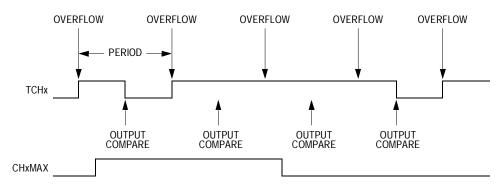

- 2-channel, 16-bit timer interface module (TIM)

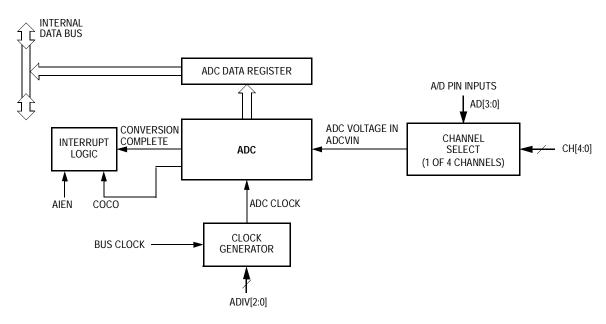

- 4-channel, 8-bit analog-to-digital converter (ADC) on MC68HC908QY2, MC68HC908QY4, MC68HC908QT2, and MC68HC908QT4

- 5 or 13 bidirectional input/output (I/O) lines and one input only:

- High current sink/source capability on all port pins

- Selectable pullups on all ports, selectable on an individual bit basis

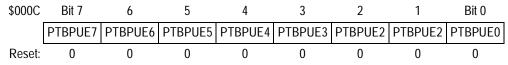

- 6-bit keyboard interrupt with wakeup feature (KBI)

- Low-voltage inhibit (LVI) module features software selectable trip point in CONFIG register

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

<sup>1.</sup> No security feature is absolutely secure. However, Motorola's strategy is to make reading or copying the FLASH difficult for unauthorized users.

- System protection features:

- Computer operating properly (COP) watchdog

- Low-voltage detection with reset

- Illegal opcode detection with reset

- Illegal address detection with reset

- External asynchronous interrupt pin with internal pullup (IRQ) shared with general-purpose input pin

- Master asynchronous reset pin (RST) shared with general-purpose I/O pin

- Power-on reset

- Internal pullups on IRQ and RST to reduce external components

- Memory mapped I/O registers

- Power saving stop and wait modes

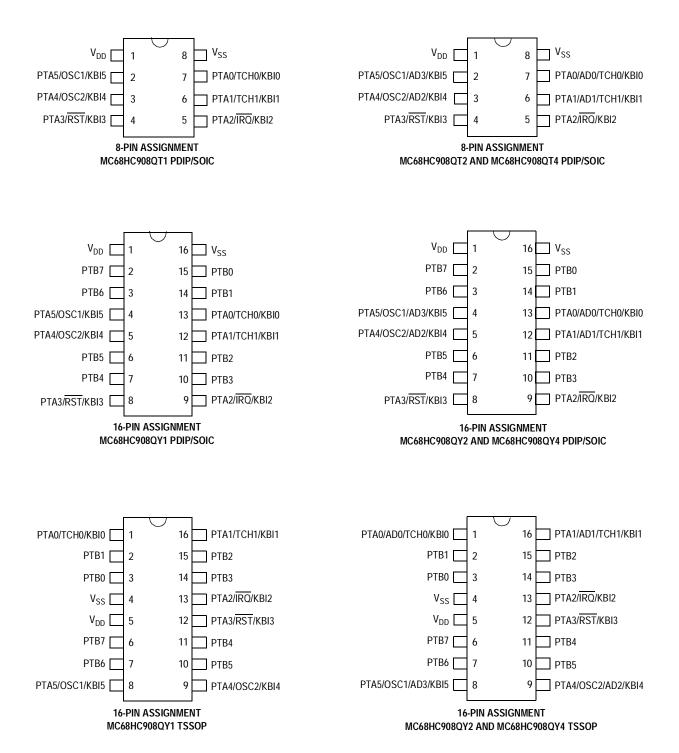

- MC68HC908QY4, MC68HC908QY2, and MC68HC908QY1 are available in these packages:

- 16-pin plastic dual in-line package (PDIP)

- 16-pin small outline integrated circuit (SOIC) package

- 16-pin thin shrink small outline package (TSSOP)

- MC68HC908QT4, MC68HC908QT2, and MC68HC908QT1 are available in these packages:

- 8-pin PDIP

- 8-pin SOIC

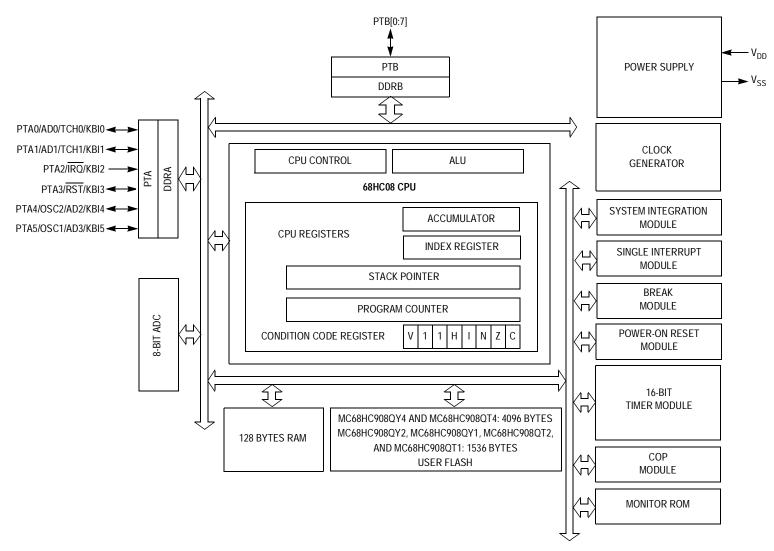

## **MCU Block Diagram**

See Figure 1.

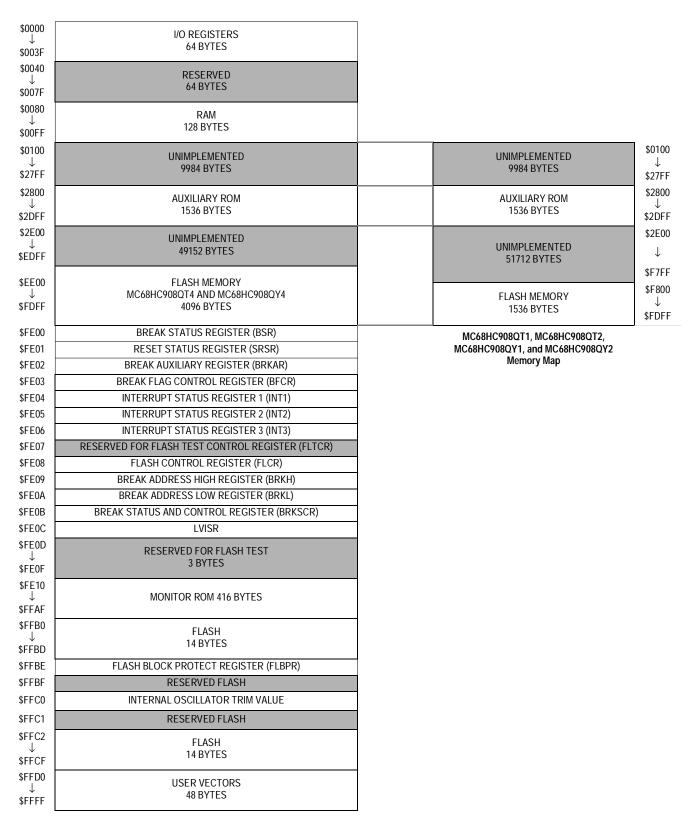

### Memory

The central processor unit (CPU08) can address 64 Kbytes of memory space. The memory map is shown in **Figure 3**.

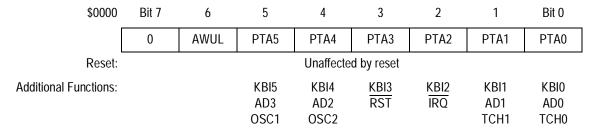

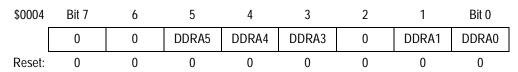

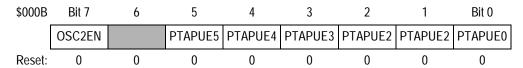

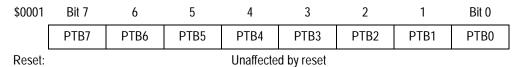

Addresses \$0000–\$003F, shown in **Figure 4**, contain most of the control, status, and data registers.

The vector addresses are shown in Table 3.

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

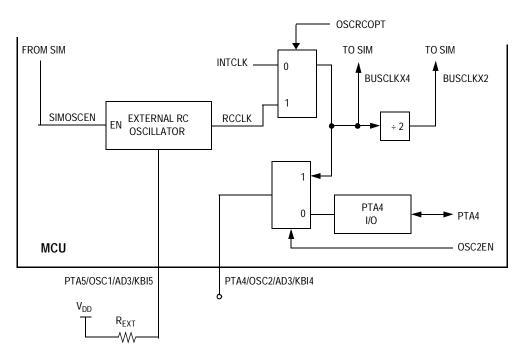

RST, IRQ: Pins have internal (about 30K Ohms) pull up

PTA[0:5]: High current sink and source capability

PTA[0:5]: Pins have programmable keyboard interrupt and pull up

PTB[0:7]: Not available on 8-pin devices - MC68HC908QT1, MC68HC908QT2, and MC68HC908QT4

Figure 1. Block Diagram

## **Pin Assignments**

Figure 2. MCU Pin Assignments

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

### **Pin Functions**

Table 2 provides a description of the pin functions.

**Table 2. Pin Functions**

| Pin<br>Name             | Description                                                                                                        | Input/Output     |

|-------------------------|--------------------------------------------------------------------------------------------------------------------|------------------|

| $V_{DD}$                | Power supply                                                                                                       | Power            |

| V <sub>SS</sub>         | Power supply ground                                                                                                | Power            |

|                         | PTA0 — General purpose I/O port                                                                                    | Input/Output     |

| PTA0                    | AD0 — A/D channel 0 input                                                                                          | Input            |

| PTAU                    | TCH0 — Timer Channel 0 I/O                                                                                         | Input/Output     |

|                         | KBI0 — Keyboard interrupt input 0                                                                                  | Input            |

|                         | PTA1 — General purpose I/O port                                                                                    | Input/Output     |

| PTA1                    | AD1 — A/D channel 1 input                                                                                          | Input            |

| FIAI                    | TCH1 — Timer Channel 1 I/O                                                                                         | Input/Output     |

|                         | KBI1 — Keyboard interrupt input 1                                                                                  | Input            |

|                         | PTA2 — General purpose input-only port                                                                             | Input            |

| PTA2                    | IRQ — External interrupt with programmable pullup and Schmitt trigger input                                        | Input            |

|                         | KBI2 — Keyboard interrupt input 2                                                                                  | Input            |

|                         | PTA3 — General purpose I/O port                                                                                    | Input/Output     |

| PTA3                    | RST — Reset input, active low with internal pullup and Schmitt trigger                                             | Input            |

|                         | KBI3 — Keyboard interrupt input 3                                                                                  | Input            |

|                         | PTA4 — General purpose I/O port                                                                                    | Input/Output     |

| PTA4                    | OSC2 — XTAL oscillator output (XTAL option only)  RC or internal oscillator output (OSC2EN = 1 in PTAPUE register) | Output<br>Output |

|                         | AD2 — A/D channel 2 input                                                                                          | Input            |

|                         | KBI4 — Keyboard interrupt input 4                                                                                  | Input            |

|                         | PTA5 — General purpose I/O port                                                                                    | Input/Output     |

| PTA5                    | OSC1 —XTAL, RC, or external oscillator input                                                                       | Input            |

| FIAS                    | AD3 — A/D channel 3 input                                                                                          | Input            |

|                         | KBI5 — Keyboard interrupt input 5                                                                                  | Input            |

| PTB[0:7] <sup>(1)</sup> | 8 general-purpose I/O ports.                                                                                       | Input/Output     |

<sup>1.</sup> The PTB pins are not available on the 8-pin packages.

$MC68HC908QY4 \bullet MC68HC908QT4 \bullet MC68HC908QY2 \bullet MC68HC908QT2 \bullet MC68HC908QY1 \bullet MC68HC908QT1$

Figure 3. Memory Map

| Addr.             | Register      | Bit 7   | 6           | 5       | 4       | 3       | 2       | 1       | Bit 0   |

|-------------------|---------------|---------|-------------|---------|---------|---------|---------|---------|---------|

| \$0000            | PTA           | 0       | AWUL        | PTA5    | PTA4    | PTA3    | PTA2    | PTA1    | PTA0    |

| \$0001            | РТВ           | PTB7    | PTB6        | PTB5    | PTB4    | PTB3    | PTB2    | PTB1    | PTB0    |

| \$0002            | Unimplemented |         |             |         |         |         |         |         |         |

| \$0003            | Unimplemented |         |             |         |         |         |         |         |         |

| \$0004            | DDRA          | 0       | 0           | DDRA5   | DDRA4   | DDRA3   | 0       | DDRA1   | DDRA0   |

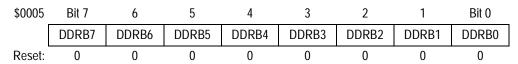

| \$0006            | DDRB          | DDRB7   | DDRB6       | DDRB5   | DDRB4   | DDRB3   | DDRB2   | DDRB1   | DDRB0   |

| \$0007-           | Unimplemented |         |             |         |         |         |         |         |         |

| \$0007–<br>\$000A | Unimplemented |         |             |         |         |         |         |         |         |

| \$000B            | PTAPUE        | OSC2EN  | 0           | PTAPUE5 | PTAPUE4 | PTAPUE3 | PTAPUE2 | PTAPUE1 | PTAPUE0 |

| \$000C            | PTBPUE        | PTBPUE7 | PTBPUE6     | PTBPUE5 | PTBPUE4 | PTBPUE3 | PTBPUE2 | PTBPUE1 | PTBPUE0 |

| \$000D-           | Unimplemented |         |             |         |         |         |         |         |         |

| \$0019            | Unimplemented |         |             |         |         |         |         |         |         |

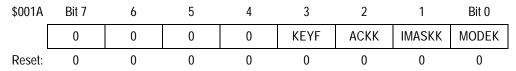

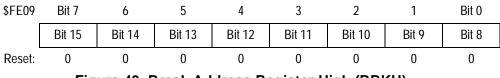

| \$001A            | KBSCR         | 0       | 0           | 0       | 0       | KEYF    | ACKK    | IMASKK  | MODEK   |

| \$001B            | KBIER         | 0       | AWUIE       | KBIE5   | KBIE4   | KBIE3   | KBIE2   | KBIE1   | KBIE0   |

| \$001C            | Unimplemented |         |             |         |         |         |         |         |         |

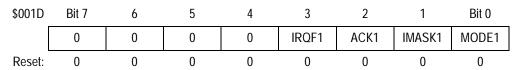

| \$001D            | INTSCR        | 0       | 0           | 0       | 0       | IRQF1   | ACK1    | IMASK1  | MODE1   |

| \$001E            | CONFIG2       | IRQPUD  | IRQEN       |         | OSCOPT1 | OSCOPT0 |         |         | RSTEN   |

| \$001F            | CONFIG1       | COPRS   | LVISTOP     | LVIRSTD | LVIPWRD | LVI5OR3 | SSREC   | STOP    | COPD    |

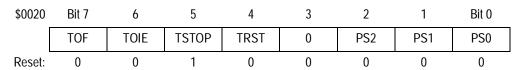

| \$0020            | TSC           | TOF     | TOIE        | TSTOP   | TRST    | 0       | PS2     | PS1     | PS0     |

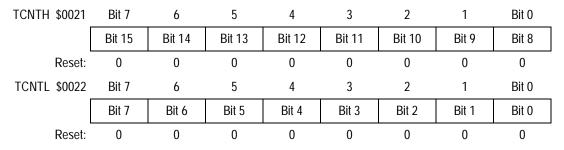

| \$0021            | TCNTH         | Bit 15  | Bit 14      | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   |

| \$0022            | TCNTL         | Bit 7   | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

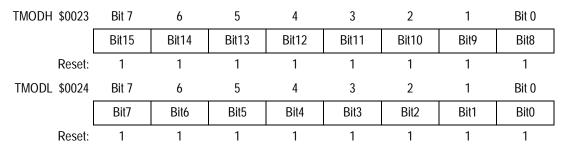

| \$0023            | TMODH         | Bit 15  | Bit 14      | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   |

| \$0024            | TMODL         | Bit 7   | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

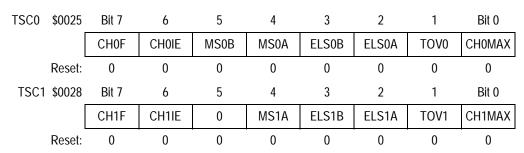

| \$0025            | TSC0          | CH0F    | CH0IE       | MS0B    | MS0A    | ELS0B   | ELS0A   | TOV0    | CH0MAX  |

| \$0026            | ТСН0Н         | Bit 15  | Bit 14      | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   |

| \$0027            | TCH0L         | Bit 7   | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

| \$0028            | TSC1          | CH1F    | CH1IE       | 0       | MS1A    | ELS1B   | ELS1A   | TOV1    | CH1MAX  |

| \$0029            | тсн1н         | Bit 15  | Bit 14      | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8   |

| \$002A            | TCH1L         | Bit 7   | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

| \$002B-           | Unimplemented |         |             |         |         |         |         |         |         |

| \$0035            | Unimplemented |         |             |         |         |         |         |         |         |

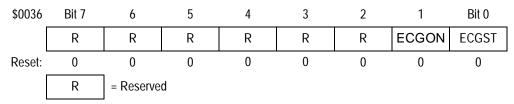

| \$0036            | OSCSTAT       |         |             |         |         |         |         | ECGON   | ECGST   |

| \$0037            | Unimplemented |         |             |         |         |         |         |         |         |

| \$0038            | OSCTRIM       | TRIM7   | TRIM6       | TRIM5   | TRIM4   | TRIM3   | TRIM2   | TRIM1   | TRIM0   |

| \$0039-           | Unimplemented |         |             |         |         |         |         |         |         |

| \$0037-<br>\$003B | Unimplemented |         |             |         |         |         |         |         |         |

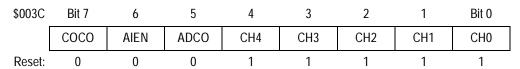

| \$003C            | ADSCR         | COCO    | AIEN        | ADCO    | CH4     | CH3     | CH2     | CH1     | CH0     |

| \$003D            | Unimplemented |         |             |         |         |         |         |         |         |

| \$003E            | ADR           | AD7     | AD6         | AD5     | AD4     | AD3     | AD2     | AD1     | AD0     |

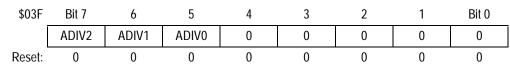

| \$003F            | ADICLK        | ADIV2   | ADIV1       | ADIV0   | 0       | 0       | 0       | 0       | 0       |

| •                 | 7-11          |         | = Unimpleme | I -     | I       |         | _       | I       |         |

Figure 4. Control, Status, and Data Registers (Sheet 1 of 2)

$MC68HC908QY4 \bullet MC68HC908QT4 \bullet MC68HC908QY2 \bullet MC68HC908QT2 \bullet MC68HC908QY1 \bullet MC68HC908QT1$

| Addr.   | Register                | Bit 7                                 | 6      | 5      | 4           | 3          | 2      | 1     | Bit 0 |

|---------|-------------------------|---------------------------------------|--------|--------|-------------|------------|--------|-------|-------|

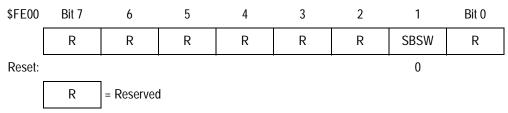

| \$FE00  | BSR                     |                                       |        |        |             |            |        | SBSW  |       |

| \$FE01  | SRSR                    | POR                                   | PIN    | COP    | ILOP        | ILAD       | MODRST | LVI   | 0     |

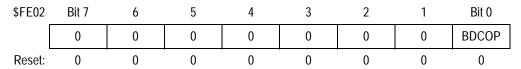

| \$FE02  | BRKAR                   | 0                                     | 0      | 0      | 0           | 0          | 0      | 0     | BDCOP |

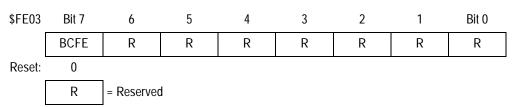

| \$FE03  | BFCR                    | BCFE                                  |        |        |             |            |        |       |       |

| \$FE04  | INT1                    | 0                                     | IF5    | IF4    | IF3         | 0          | IF1    | 0     | 0     |

| \$FE05  | INT2                    | IF14                                  | 0      | 0      | 0           | 0          | 0      | 0     | 0     |

| \$FE06  | INT3                    | 0                                     | 0      | 0      | 0           | 0          | 0      | 0     | IF15  |

| \$FE07  | Reserved                |                                       |        |        |             |            |        |       |       |

| \$FE08  | FLCR                    | 0                                     | 0      | 0      | 0           | HVEN       | MASS   | ERASE | PGM   |

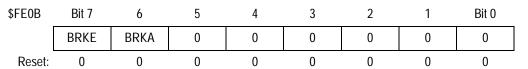

| \$FE09  | BRKH                    | Bit 15                                | Bit 14 | Bit 13 | Bit 12      | Bit 11     | Bit 10 | Bit 9 | Bit 8 |

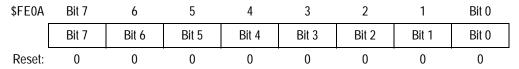

| \$FE0A  | BRKL                    | Bit 7                                 | Bit 6  | Bit 5  | Bit 4       | Bit 3      | Bit 2  | Bit 1 | Bit 0 |

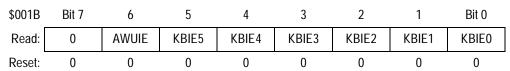

| \$FE0B  | BRKSCR                  | BRKE                                  | BRKA   | 0      | 0           | 0          | 0      | 0     | 0     |

| \$FE0C  | LVISR                   | LVIOUT                                | 0      | 0      | 0           | 0          | 0      | 0     |       |

| \$FE0D- | Reserved for FLASH Test |                                       |        |        |             |            |        |       |       |

| \$FE0F  | Reserved for FLASH Test |                                       |        |        |             |            |        |       |       |

| \$FFBE  | FLBPR                   | BPR7                                  | BPR6   | BPR5   | BPR4        | BPR3       | BPR2   | BPR1  | BPR0  |

| \$FFBF  | Reserved                |                                       |        |        |             |            |        |       |       |

| \$FFC0  | TRIMLOC                 |                                       | -      | NON-VO | LATILE TRIM | ADJUSTMENT | VALUE  |       | •     |

| \$FFC1  | Reserved                |                                       |        |        |             |            |        |       |       |

| \$FFFF  | COPCTL                  | WRITE ANY VALUE TO RESET COP WATCHDOG |        |        |             |            |        |       |       |

|         |                         | = Unimplemented or Reserved           |        |        |             |            |        |       |       |

Figure 4. Control, Status, and Data Registers (Sheet 2 of 2)

Address **Vector Priority** Vector Vector Lowest \$FFDE ADC conversion complete vector (high) IF15 \$FFDF ADC conversion complete vector (low) \$FFE0 Keyboard vector (high) IF14 \$FFE1 Keyboard vector (low) IF13 through Not used IF6 \$FFF2 TIM overflow vector (high) IF5 \$FFF3 TIM overflow vector (low) \$FFF4 TIM Channel 1 vector (high) IF4 \$FFF5 TIM Channel 1 vector (low) \$FFF6 TIM Channel 0 vector (high) IF3 \$FFF7 TIM Channel 0 vector (low) IF2 Not used \$FFFA IRQ vector (high) IF1 \$FFFB IRQ vector (low) \$FFFC SWI vector (high) \$FFFD SWI vector (low) \$FFFE Reset vector (high) \$FFFF Highest Reset vector (low)

**Table 3. Vector Addresses**

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

#### **FLASH Module**

The FLASH memory consists of an array of 4096 or 1536 bytes with an additional 80 bytes for user vectors and miscellaneous. The minimum size of FLASH memory that can be erased is 64 bytes; and the maximum size of FLASH memory that can be programmed in a program cycle is 32 bytes (a row). Program and erase operations are facilitated through control bits in the FLASH control register (FLCR). Details for these operations appear later in this section. The address ranges for the user memory and vectors are:

- \$EE00 \$FDFF; user memory, 4096 bytes: MC68HC908QY4 and MC68HC908QT4

- \$F800 \$FDFF; user memory, 1536 bytes: MC68HC908QY2, MC68HC908QT2, MC68HC908QY1 and MC68HC908QT1

- \$FFB0 \$FFFF; user interrupt vectors etc., 80 bytes.

#### NOTE:

An erased bit reads as logic 1 and a programmed bit reads as logic 0. A security feature prevents unauthorized viewing of the FLASH contents.

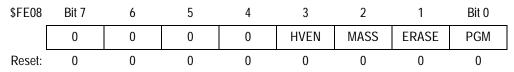

# FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 5. FLASH Control Register (FLCR)

HVEN — High Voltage Enable Bit

1 = High voltage enabled to array and charge pump on

MASS — Mass Erase Control Bit

1 = Mass Erase operation selected

ERASE — Erase Control Bit

1 = Erase operation selected

PGM — Program Control Bit

1 = Program operation selected

# FLASH Page Erase Operation

Use the following procedure to erase a page of FLASH memory. A page consists of 64 consecutive bytes starting from addresses \$XX00, \$XX40, \$XX80, or \$XXC0. The 80-byte user interrupt vectors area includes two pages (\$FFB0-\$FFBF and \$FFC0-\$FFFF). Any FLASH memory page can be erased alone.

- 1. Set the ERASE bit and clear the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register (\$FFBE).

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

- 3. Write any data to any FLASH location within the address range of the block to be erased.

- 4. Wait for a time,  $t_{nvs}$  (minimum 10  $\mu s$ ).

- 5. Set the HVEN bit.

- 6. Wait for a time, t<sub>Erase</sub> (minimum 1 ms or 4 ms).

- 7. Clear the ERASE and MASS bits.

- 8. Wait for a time,  $t_{nvh}$  (minimum 5  $\mu$ s).

- 9. Clear the HVEN bit.

- 10. After time,  $t_{rcv}$  (typical 1  $\mu s$ ), the memory can be accessed in read mode again.

#### NOTE:

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. These operations must be performed in the order as shown, but other unrelated operations may occur between the steps.

In applications that need up to 10,000 program/erase cycles, use the 4 ms page erase specification to get improved long-term reliability. Any application can use this 4 ms page erase specification. However, in applications where a FLASH location will be erased and reprogrammed less than 1000 times, and speed is important, use the 1 ms page erase specification to get a lower minimum erase time.

# FLASH Program Operation

Programming of the FLASH memory is done on a row basis. A row consists of 32 consecutive bytes starting from addresses \$XX00, \$XX20, \$XX40, \$XX60, \$XX80, \$XXA0, \$XXC0, or \$XXE0. Use the following step-by-step procedure to program a row of FLASH memory.

## **NOTE:**

Only bytes which are currently \$FF may be programmed.

- 1. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 2. Read from the FLASH block protect register (\$FFBE).

- 3. Write any data to any FLASH location within the address range desired.

- 4. Wait for a time,  $t_{nvs}$  (minimum 10  $\mu s$ ).

- 5. Set the HVEN bit.

- 6. Wait for a time,  $t_{pas}$  (minimum 5  $\mu$ s).

- 7. Write data to the FLASH address being programmed<sup>(1)</sup>.

- 8. Wait for time,  $t_{PROG}$  (minimum 30  $\mu$ s).

- 9. Repeat step 6 and 7 until desired bytes within the row are programmed.

- 10. Clear the PGM bit<sup>(1)</sup>.

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

The time between each FLASH address change, or the time between the last FLASH address programmed to clearing PGM bit, must not exceed the maximum programming time, t<sub>PROG</sub> maximum.

- 11. Wait for time,  $t_{nvh}$  (minimum 5  $\mu$ s).

- 12. Clear the HVEN bit.

- 13. After time,  $t_{rcv}$  (typical 1  $\mu$ s), the memory can be accessed in read mode again.

#### NOTE:

Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory. These operations must be performed in the order shown, other unrelated operations may occur between the steps. Do not exceed  $t_{PROG}$  maximum.

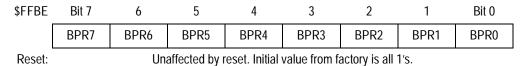

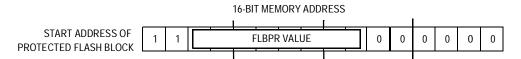

## FLASH Block Protect Register

The FLASH block protect register is implemented as a byte within the FLASH memory, and therefore it is programmed using a FLASH memory byte-programming operation. The value in this register determines the starting address of the protected range within the FLASH memory. The FLASH is protected from this address to the end of FLASH memory at \$FFFF.

Figure 6. FLASH Block Protect Register (FLBPR)

BPR[7:0] — FLASH Protection Register Bits [7:0]

Figure 7. FLASH Block Protect Start Address

Table 4. Examples of Protect Start Address

| BPR[7:0]                  | Start of Address of Protect Range                                                  |

|---------------------------|------------------------------------------------------------------------------------|

| \$00-\$B8                 | The entire FLASH memory is protected.                                              |

| \$B9 ( <b>1011 1001</b> ) | \$EE40 (11 <b>10 1110 01</b> 00 0000)                                              |

| \$BA ( <b>1011 1010</b> ) | \$EE80 (11 <b>10 1110 10</b> 00 0000)                                              |

| \$BB ( <b>1011 1011</b> ) | \$EEC0 (11 <b>10 1110 11</b> 00 0000)                                              |

| \$BC ( <b>1011 1100</b> ) | \$EF00 (11 <b>10 1111 00</b> 00 0000)                                              |

| and so on                 |                                                                                    |

| \$DE ( <b>1101 1110</b> ) | \$F780 (11 <b>11 0111 10</b> 00 0000)                                              |

| \$DF (1101 1111)          | \$F7C0 (11 <b>11 0111 11</b> 00 0000)                                              |

| \$FE (1111 1110)          | \$FF80 (11 <b>11 1111 10</b> 00 0000)<br>FLBPR, OSCTRIM, and vectors are protected |

| \$FF                      | The entire FLASH memory is not protected.                                          |

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

## **Configuration Registers (CONFIG1, CONFIG2)**

The configuration registers are used to initialize various options. The configuration registers can each be written once after each reset. Most of the configuration register bits are cleared during reset. Since the various options affect the operation of the microcontroller unit (MCU) it is recommended that these registers be written immediately after reset. The configuration registers are located at \$001E and \$001F, and may be read at anytime.

| \$001E | Bit 7  | 6         | 5 | 4           | 3       | 2 | 1 | Bit 0 |

|--------|--------|-----------|---|-------------|---------|---|---|-------|

|        | IRQPUD | IRQEN     | R | OSCOPT1     | OSCOPT0 | R | R | RSTEN |

| Reset: | 0      | 0         | 0 | 0           | 0       | 0 | 0 | U     |

| POR:   | 0      | 0         | 0 | 0           | 0       | 0 | 0 | 0     |

|        | R      | = Reserve | d | U = Unaffec | ted     |   |   |       |

Figure 8 Configuration Register 2 (CONFIG2)

IRQPUD — IRQ Pin Pullup Disable Control Bit

$0 = Internal pullup is connected between IRQ pin and <math>V_{DD}$  (if IRQEN = 1)

IRQEN — IRQ Pin Function Selection Bit

1 = PTA2/IRQ/KBI2 pin configured for IRQ function

0 = Pin configured for PTA2 or KBI2 function

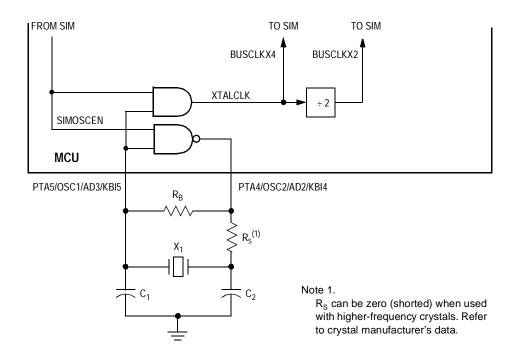

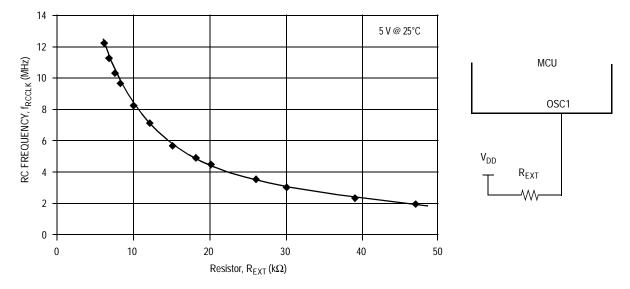

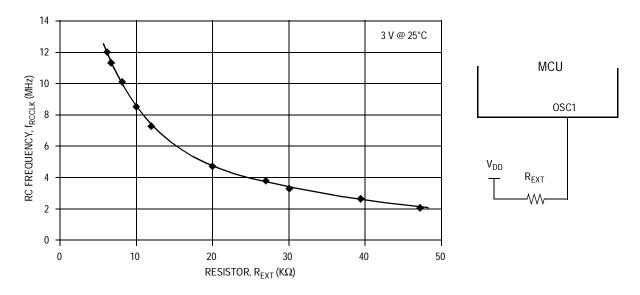

OSCOPT1:OSCOPT0 — Selection Bits for Oscillator Option

(0:0) Internal oscillator

(0:1) External oscillator

(1:0) External RC oscillator

(1:1) External XTAL oscillator

RSTEN — RST Pin Function Selection

1 = PTA2/RST/KBI3 pin configured for RESET function

0 = Pin configured for PTA3 or KBI3 function

**NOTE:** The RSTEN bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

| \$001F | Bit 7      | 6       | 5       | 4       | 3       | 2     | 1    | Bit 0 |

|--------|------------|---------|---------|---------|---------|-------|------|-------|

|        | COPRS      | LVISTOP | LVIRSTD | LVIPWRD | LVI5OR3 | SSREC | STOP | COPD  |

| Reset: | 0          | 0       | 0       | 0       | U       | 0     | 0    | 0     |

| POR:   | 0          | 0       | 0       | 0       | 0       | 0     | 0    | 0     |

|        | U = Unaffe | cted    |         |         |         |       |      |       |

Figure 9 Configuration Register 1 (CONFIG1)

COPRS (Out of STOP Mode) — COP Reset Period Selection Bit

1 = COP reset short cycle =  $(2^{13} - 2^4)$  x BUSCLKX4

$0 = COP \text{ reset long cycle} = (2^{18} - 2^4) \times BUSCLKX4$

To prevent a reset due to a COP watchdog timeout, write any value to COPCTL (\$FFFF) before the COP timer reaches the selected timeout.

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

COPRS (In STOP Mode) — Auto Wake-up Period Selection Bit

1 = Auto wake-up short cycle = approximately 16 ms

0 = Auto wake-up long cycle = approximately 512 ms

LVISTOP — LVI Enable in Stop Mode Bit

1 = LVI enabled during stop mode

0 = LVI disabled during stop mode

LVIRSTD — LVI Reset Disable Bit

1 = LVI module resets disabled

0 = LVI module resets enabled

LVIPWRD — LVI Power Disable Bit

1 = LVI module power disabled

LVI5OR3 — LVI 5-V or 3-V Operating Mode Bit

1 = LVI operates in 5-V mode

0 = LVI operates in 3-V mode

**NOTE:** The LVI5OR3 bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

SSREC — Short Stop Recovery Bit

1 = Stop mode recovery after 32 BUSCLKX4 cycles

0 = Stop mode recovery after 4096 BUSCLKX4 cycles

**NOTE:** Exiting stop mode by an LVI reset will result in the long stop recovery.

STOP — STOP Instruction Enable Bit

1 = STOP instruction enabled

0 = STOP instruction treated as illegal opcode

COPD — COP Disable Bit

1 = COP module disabled (does not force resets)

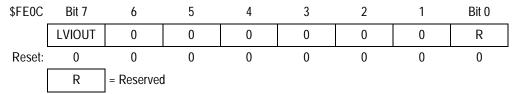

## **LVI Status Register**

The LVI status register (LVISR) indicates if the  $V_{DD}$  voltage was detected below the  $V_{TRIPF}$  level while LVI resets have been disabled.

Figure 10. LVI Status Register (LVISR)

LVIOUT — LVI Output Bit

This read-only flag becomes set when the  $V_{DD}$  voltage falls below the  $V_{TRIPF}$  trip voltage and is cleared when  $V_{DD}$  voltage rises above  $V_{TRIPR}$ .

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

## **IRQ Status and Control Register**

Figure 11. IRQ Status and Control Register (INTSCR)

IRQF1 — IRQ Flag

This read-only status bit is high when the IRQ interrupt is pending.

1 = IRQ interrupt pending

ACK1 — IRQ Interrupt Request Acknowledge Bit

Writing a logic 1 to this write-only bit clears the IRQ latch. ACK1 always reads as logic 0.

IMASK1 — IRQ Interrupt Mask Bit

1 = IRQ interrupt requests disabled

MODE1 — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin.

1 = IRQ interrupt requests on falling edges and low levels

0 = IRQ interrupt requests on falling edges only

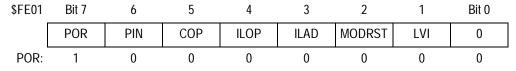

## SIM Reset Status Register

This register contains seven flags that show the source of the last reset. Clear the SIM reset status register by reading it. A power-on reset sets the POR bit and clears all other bits in the register.

Figure 12. SIM Reset Status Register (SRSR)

POR — Power-On Reset Bit

1 = Last reset caused by POR circuit

PIN — External Reset Bit

$1 = \text{Last reset caused by external reset pin } (\overline{RST})$

COP — Computer Operating Properly Reset Bit

1 = Last reset caused by COP timeout

ILOP — Illegal Opcode Reset Bit

1 = Last reset caused by an illegal opcode

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

ILAD — Illegal Address Reset Bit (opcode fetches only)

1 = Last reset caused by an opcode fetch from an illegal address

MODRST — Monitor Mode Entry Module Reset Bit

1 = Last reset caused by monitor mode entry when vector locations FFFE and FFFF are FFF after POR while  $PTA2/\overline{IRQ} = V_{DD}$

LVI — Low Voltage Inhibit Reset Bit

1 = Last reset caused by LVI circuit

## Interrupt Status Registers (INT1, INT2, INT3)

These three registers include status flags which indicate which interrupt sources currently have pending requests. See **Table 3**.

| \$FE04  | Bit 7 | 6   | 5    | 4    | 3 | 2   | 1 | Bit 0 |  |

|---------|-------|-----|------|------|---|-----|---|-------|--|

|         | 0     | IF5 | IF4  | IF3  | 0 | IF1 | 0 | 0     |  |

| Reset:  | 0     | 0   | 0    | 0    | 0 | 0   | 0 | 0     |  |

| Source: |       | TOF | TCH1 | TCH0 |   | ĪRQ |   |       |  |

Figure 13. Interrupt Status Register 1 (INT1)

| \$FE05  | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|---------|-------|---|---|---|---|---|---|-------|

|         | IF14  | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| Reset:  | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| Source: | KBI   |   |   |   |   |   |   |       |

Figure 14. Interrupt Status Register 2 (INT2)

| \$FE06  | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|---------|-------|---|---|---|---|---|---|-------|

|         | 0     | 0 | 0 | 0 | 0 | 0 | 0 | IF15  |

| Reset:  | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

| Source: |       |   |   |   |   |   |   | ADC   |

Figure 15. Interrupt Status Register 3 (INT3)

IFxx — Interrupt Flags

These flags indicate the presence of interrupt requests from the sources shown below the corresponding IFxx bit.

1 = Interrupt request pending

0 = No interrupt request present

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

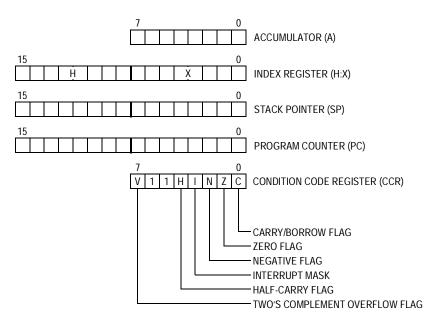

## **Central Processor Unit (CPU)**

**Figure 16** shows the five CPU registers. CPU registers are not part of the memory map.

Figure 16. CPU Registers

## **Instruction Set Summary**

**Table 5** provides a summary of the M68HC08 instruction set.

Table 5. Instruction Set Summary (Sheet 1 of 7)

| Source<br>Form                                                                                      | Operation                              | Description                              |          |          |   | ec<br>CC |          |          | Address<br>Mode                                                                              | Opcode                                           | Operand                                      | Cycles                               |

|-----------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------|----------|----------|---|----------|----------|----------|----------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------|--------------------------------------|

| 1 01111                                                                                             |                                        | ,                                        |          |          | I | Ν        | Z        | С        | Add                                                                                          | obo                                              | ď                                            | ပိ                                   |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC, X<br>ADC opr,SP<br>ADC opr,SP      | Add with Carry                         | $A \leftarrow (A) + (M) + (C)$           | <b>‡</b> | <b>‡</b> | _ | ‡        | <b>1</b> | ţ        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A9<br>B9<br>C9<br>D9<br>E9<br>F9<br>9EE9<br>9ED9 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff    | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| ADD #opr<br>ADD opr<br>ADD opr,<br>ADD opr,X<br>ADD opr,X<br>ADD opr,SP<br>ADD opr,SP<br>ADD opr,SP | Add without Carry                      | $A \leftarrow (A) + (M)$                 | <b>1</b> | ‡        | _ | ‡        | <b>‡</b> | ‡        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | AB<br>BB<br>CB<br>DB<br>EB<br>FB<br>9EEB<br>9EDB | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff    | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| AIS #opr                                                                                            | Add Immediate Value (Signed) to SP     | $SP \leftarrow (SP) + (16   ^{\vee}  M)$ | -        | -        | - | -        | ı        | -        | IMM                                                                                          | A7                                               | ii                                           | 2                                    |

| AIX #opr                                                                                            | Add Immediate Value (Signed) to H:X    | $H:X \leftarrow (H:X) + (16 \% M)$       | -        | -        | - | -        | ı        | -        | IMM                                                                                          | AF                                               | ii                                           | 2                                    |

| AND #opr<br>AND opr<br>AND opr<br>AND opr,X<br>AND opr,X<br>AND,X<br>AND opr,SP<br>AND opr,SP       | Logical AND                            | $A \leftarrow (A) \ \& \ (M)$            | 0        | -        | _ | ‡        | <b>‡</b> | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4         |                                              | 2 3 4 4 3 2 4 5                      |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL opr,SP                                        | Arithmetic Shift Left<br>(Same as LSL) | © - 0 b0                                 | 1        | _        | _ | ‡        | <b>1</b> | ‡        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                               | 4<br>1<br>1<br>4<br>3<br>5           |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR opr,X<br>ASR opr,SP                                     | Arithmetic Shift Right                 | b7 b0                                    | <b>‡</b> | _        | - | <b>‡</b> | 1        | <b>‡</b> | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                               | 4<br>1<br>1<br>4<br>3<br>5           |

| BCC rel                                                                                             | Branch if Carry Bit Clear              | $PC \leftarrow (PC) + 2 + rel?(C) = 0$   | -        | -        | - | -        | -        | -        | REL                                                                                          | 24                                               | rr                                           | 3                                    |

| BCLR n, opr                                                                                         | Clear Bit n in M                       | Mn ← 0                                   | _        | _        | _ | _        | _        | _        | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D           | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 4<br>4<br>4<br>4<br>4<br>4<br>4      |

| BCS rel                                                                                             | Branch if Carry Bit Set (Same as BLO)  | PC ← (PC) + 2 + rel? (C) = 1             | _        | -        | - | _        | _        | _        | REL                                                                                          | 25                                               | rr                                           | 3                                    |

MC68HC908QY4•MC68HC908QT4•MC68HC908QY2•MC68HC908QT2•MC68HC908QY1•MC68HC908QT1

Table 5. Instruction Set Summary (Sheet 2 of 7)

| Source<br>Form                                                                                  | Operation                                            | Description                                             | Description E: |   |   |          |          |   | Address<br>Mode                                                                              | Opcode                                   | Operand                                                              | les                                  |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|----------------|---|---|----------|----------|---|----------------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------|--------------------------------------|

| FOIIII                                                                                          | •                                                    | •                                                       | ٧              | Н | ı | N        | Z        | С | Ado                                                                                          | odo                                      | obe                                                                  | Cycles                               |

| BEQ rel                                                                                         | Branch if Equal                                      | $PC \leftarrow (PC) + 2 + rel? (Z) = 1$                 |                |   |   | -        | _        | - | REL                                                                                          | 27                                       | rr                                                                   | 3                                    |

| BGE opr                                                                                         | Branch if Greater Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + rel? (N \oplus V) = 0$        | _              | _ | - | _        | _        | - | REL                                                                                          | 90                                       | rr                                                                   | 3                                    |

| BGT opr                                                                                         | Branch if Greater Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel? (Z)   (N \oplus V) = 0$  | _              | _ | - | _        | _        | - | REL                                                                                          | 92                                       | rr                                                                   | 3                                    |

| BHCC rel                                                                                        | Branch if Half Carry Bit Clear                       | PC ← (PC) + 2 + rel? (H) = 0                            | -              | _ | - | -        | -        | - | REL                                                                                          | 28                                       | rr                                                                   | 3                                    |

| BHCS rel                                                                                        | Branch if Half Carry Bit Set                         | PC ← (PC) + 2 + rel? (H) = 1                            | -              | _ | - | -        | _        | _ | REL                                                                                          | 29                                       | rr                                                                   | 3                                    |

| BHI rel                                                                                         | Branch if Higher                                     | $PC \leftarrow (PC) + 2 + rel? (C)   (Z) = 0$           | _              | - | _ | -        | _        | - | REL                                                                                          | 22                                       | rr                                                                   | 3                                    |

| BHS rel                                                                                         | Branch if Higher or Same (Same as BCC)               | PC ← (PC) + 2 + rel? (C) = 0                            | _              | _ | _ | _        | _        | - | REL                                                                                          | 24                                       | rr                                                                   | 3                                    |

| BIH rel                                                                                         | Branch if IRQ Pin High                               | PC ← (PC) + 2 + rel?                                    | -              | _ | _ | _        | _        | _ | REL                                                                                          | 2F                                       | rr                                                                   | 3                                    |

| BIL rel                                                                                         | Branch if IRQ Pin Low                                | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 0$     | -              | _ | - | -        | _        | _ | REL                                                                                          | 2E                                       | rr                                                                   | 3                                    |

| BIT #opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT opr,X<br>BIT,X<br>BIT opr,SP<br>BIT opr,SP | Bit Test                                             | (A) & (M)                                               | 0              | _ | _ | <b>‡</b> | <b>‡</b> | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9ED5 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff                            | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| BLE opr                                                                                         | Branch if Less Than or Equal To (Signed Operands)    | $PC \leftarrow (PC) + 2 + rel ? (Z)   (N \oplus V) = 1$ | -              | - | - | _        | -        | - | REL                                                                                          | 93                                       | rr                                                                   | 3                                    |

| BLO rel                                                                                         | Branch if Lower (Same as BCS)                        | PC ← (PC) + 2 + rel? (C) = 1                            | _              | _ | _ | _        | _        | _ | REL                                                                                          | 25                                       | rr                                                                   | 3                                    |

| BLS rel                                                                                         | Branch if Lower or Same                              | PC ← (PC) + 2 + rel? (C)   (Z) = 1                      | _              | _ | - | -        | -        | - | REL                                                                                          | 23                                       | rr                                                                   | 3                                    |

| BLT opr                                                                                         | Branch if Less Than (Signed Operands)                | PC ← (PC) + 2 + <i>rel</i> ? (N ⊕ V) =1                 | -              | - | - | _        | _        | - | REL                                                                                          | 91                                       | rr                                                                   | 3                                    |

| BMC rel                                                                                         | Branch if Interrupt Mask Clear                       | PC ← (PC) + 2 + rel? (I) = 0                            | -              | - | - | -        | -        | - | REL                                                                                          | 2C                                       | rr                                                                   | 3                                    |

| BMI rel                                                                                         | Branch if Minus                                      | PC ← (PC) + 2 + rel? (N) = 1                            | -              | _ | _ | _        | _        | _ | REL                                                                                          | 2B                                       | rr                                                                   | 3                                    |

| BMS rel                                                                                         | Branch if Interrupt Mask Set                         | PC ← (PC) + 2 + rel? (I) = 1                            | _              | - | _ | -        | _        | - | REL                                                                                          | 2D                                       | rr                                                                   | 3                                    |

| BNE rel                                                                                         | Branch if Not Equal                                  | $PC \leftarrow (PC) + 2 + rel? (Z) = 0$                 | _              | _ | - | -        | -        | - | REL                                                                                          | 26                                       | rr                                                                   | 3                                    |

| BPL rel                                                                                         | Branch if Plus                                       | $PC \leftarrow (PC) + 2 + rel? (N) = 0$                 | _              | - | - | -        | _        | - | REL                                                                                          | 2A                                       | rr                                                                   | 3                                    |

| BRA rel                                                                                         | Branch Always                                        | PC ← (PC) + 2 + <i>rel</i>                              | -              | - | - | -        | -        | - | REL                                                                                          | 20                                       | rr                                                                   | 3                                    |

| BRCLR n,opr,rel                                                                                 | Branch if Bit <i>n</i> in M Clear                    | PC ← (PC) + 3 + rel? (Mn) = 0                           | _              | _ | _ | _        | _        | ‡ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01<br>03<br>05<br>07<br>09<br>0B<br>0D   | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 55555555                             |

| BRN rel                                                                                         | Branch Never                                         | PC ← (PC) + 2                                           | _              | _ | _ | -        | _        | _ | REL                                                                                          | 21                                       | rr                                                                   | 3                                    |

Table 5. Instruction Set Summary (Sheet 3 of 7)

| Source                                                                                                | Operation                       | Description                                                                                                                                                                                                                                                                                                                                      |          |   |   |          | t<br>R   |          | Address<br>Mode                                                                              | Opcode                                       | Operand                                                              | les                                   |

|-------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---|---|----------|----------|----------|----------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------|---------------------------------------|

| Form                                                                                                  |                                 | •                                                                                                                                                                                                                                                                                                                                                | ٧        | Н | I | N        | Z        | С        | Add                                                                                          | obc                                          | obe                                                                  | Cycles                                |

| BRSET n,opr,rel                                                                                       | Branch if Bit <i>n</i> in M Set | PC ← (PC) + 3 + rel? (Mn) = 1                                                                                                                                                                                                                                                                                                                    | _        | _ | _ | _        | _        | <b>‡</b> | DIR (b0) DIR (b1) DIR (b2) DIR (b3) DIR (b4) DIR (b5) DIR (b6) DIR (b7)                      | 00<br>02<br>04<br>06<br>08<br>0A<br>0C<br>0E | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 |

| BSET n,opr                                                                                            | Set Bit <i>n</i> in M           | Mn ← 1                                                                                                                                                                                                                                                                                                                                           | _        | _ | _ | _        | _        | _        | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10<br>12<br>14<br>16<br>18<br>1A<br>1C       | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd                         | 4<br>4<br>4<br>4<br>4<br>4<br>4       |

| BSR rel                                                                                               | Branch to Subroutine            | $\begin{array}{c} PC \leftarrow (PC) + 2;  push  (PCL) \\ SP \leftarrow (SP) - 1;  push  (PCH) \\ SP \leftarrow (SP) - 1 \\ PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                                                                       | _        | _ | _ | _        | _        | _        | REL                                                                                          | AD                                           | rr                                                                   | 4                                     |

| CBEQ opr,rel<br>CBEQA #opr,rel<br>CBEQX #opr,rel<br>CBEQ opr,X+,rel<br>CBEQ X+,rel<br>CBEQ opr,SP,rel | Compare and Branch if Equal     | $\begin{array}{l} PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (X) - (M) = \$00 \\ PC \leftarrow (PC) + 3 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 2 + rel ? (A) - (M) = \$00 \\ PC \leftarrow (PC) + 4 + rel ? (A) - (M) = \$00 \\ \end{array}$ | _        | _ | _ | _        | _        | _        | DIR<br>IMM<br>IMM<br>IX1+<br>IX+<br>SP1                                                      | 31<br>41<br>51<br>61<br>71<br>9E61           | dd rr<br>ii rr<br>ii rr<br>ff rr<br>rr<br>ff rr                      | 5<br>4<br>4<br>5<br>4<br>6            |

| CLC                                                                                                   | Clear Carry Bit                 | C ← 0                                                                                                                                                                                                                                                                                                                                            | -        | _ | _ | -        | _        | 0        | INH                                                                                          | 98                                           |                                                                      | 1                                     |

| CLI                                                                                                   | Clear Interrupt Mask            | I ← 0                                                                                                                                                                                                                                                                                                                                            | -        | _ | 0 | _        | _        | _        | INH                                                                                          | 9A                                           |                                                                      | 2                                     |

| CLR opr<br>CLRA<br>CLRX<br>CLRH<br>CLR opr,X<br>CLR ,X<br>CLR opr,SP                                  | Clear                           | $\begin{array}{l} M \leftarrow \$00 \\ A \leftarrow \$00 \\ X \leftarrow \$00 \\ H \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ M \leftarrow \$00 \\ \end{array}$                                                                                                                                           | 0        | - | - | 0        | 1        | _        | DIR<br>INH<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                 | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F     | dd<br>ff<br>ff                                                       | 3<br>1<br>1<br>3<br>2<br>4            |

| CMP #opr<br>CMP opr<br>CMP opr<br>CMP opr,X<br>CMP opr,X<br>CMP,X<br>CMP opr,SP<br>CMP opr,SP         | Compare A with M                | (A) – (M)                                                                                                                                                                                                                                                                                                                                        | <b>1</b> | _ | _ | <b>1</b> | <b>‡</b> | <b>‡</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A1<br>B1<br>C1<br>D1<br>E1<br>F1<br>9EE1     |                                                                      | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5  |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                          | Complement (One's Complement)   | $\begin{array}{l} M \leftarrow (\overline{M}) = SFF - (M) \\ A \leftarrow (\Delta) = SFF - (M) \\ X \leftarrow (X) = SFF - (M) \\ M \leftarrow (\underline{M}) = SFF - (M) \\ M \leftarrow (\underline{M}) = SFF - (M) \\ M \leftarrow (M) = SFF - (M) \\ M \leftarrow (M) = SFF - (M) \end{array}$                                              | 0        | _ | _ | <b>‡</b> | <b>‡</b> | 1        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 33<br>43<br>53<br>63<br>73<br>9E63           | dd<br>ff<br>ff                                                       | 4<br>1<br>1<br>4<br>3<br>5            |

| CPHX #opr<br>CPHX opr                                                                                 | Compare H:X with M              | (H:X) – (M:M + 1)                                                                                                                                                                                                                                                                                                                                | ţ        | _ | _ | <b>‡</b> | ‡        | 1        | IMM<br>DIR                                                                                   | 65<br>75                                     | ii ii+1<br>dd                                                        | 3 4                                   |

$MC68HC908QY4 \bullet MC68HC908QT4 \bullet MC68HC908QY2 \bullet MC68HC908QT2 \bullet MC68HC908QY1 \bullet MC68HC908QT1$

Table 5. Instruction Set Summary (Sheet 4 of 7)

| Source<br>Form                                                                                     | Operation Description            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |   | ec       |   |          | Address<br>Mode                                     | Opcode                                           | Operand                                   | Cycles                               |

|----------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|----------|---|----------|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------|

| Form                                                                                               |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ٧ | Н | I | Ν        | Z | С        | Add                                                 | obc                                              | do                                        | Š                                    |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP      | Compare X with M                 | (X) – (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ‡ | _ | ı | <b>‡</b> | ‡ | <b>‡</b> | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 |                                           | 2 3 4 4 3 2 4 5                      |

| DAA                                                                                                | Decimal Adjust A                 | (A) <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U | - | - | <b>+</b> | ‡ | ‡        | INH                                                 | 72                                               |                                           | 2                                    |

| DBNZ opr,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ opr,X,rel<br>DBNZ X,rel<br>DBNZ opr,SP,rel          | Decrement and Branch if Not Zero | $\begin{array}{l} A \leftarrow (A) - 1 \text{ or } M \leftarrow (M) - 1 \text{ or } X \leftarrow (X) - 1 \\ PC \leftarrow (PC) + 3 + rel? (\text{result}) \neq 0 \\ PC \leftarrow (PC) + 2 + rel? (\text{result}) \neq 0 \\ PC \leftarrow (PC) + 2 + rel? (\text{result}) \neq 0 \\ PC \leftarrow (PC) + 3 + rel? (\text{result}) \neq 0 \\ PC \leftarrow (PC) + 2 + rel? (\text{result}) \neq 0 \\ PC \leftarrow (PC) + 2 + rel? (\text{result}) \neq 0 \\ PC \leftarrow (PC) + 4 + rel? (\text{result}) \neq 0 \end{array}$ | _ | _ | _ | ı        | _ | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr | 5 3 3 5 4 6                          |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                       | Decrement                        | $\begin{array}{l} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                   | ‡ | _ | - | <b>‡</b> | ‡ | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

| DIV                                                                                                | Divide                           | A ← (H:A)/(X)<br>H ← Remainder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _ | _ | _ | -        | ‡ | <b>‡</b> | INH                                                 | 52                                               |                                           | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP      | Exclusive OR M with A            | $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 | _ | _ | <b>‡</b> | ‡ | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 |                                           | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                       | Increment                        | $\begin{array}{l} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array}$                                                                                                                                                                                                                                                                                                                                                   | ‡ | _ | _ | <b>‡</b> | ‡ | _        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff                            | 4<br>1<br>1<br>4<br>3<br>5           |

| JMP opr<br>JMP opr<br>JMP opr,X<br>JMP opr,X<br>JMP ,X                                             | Jump                             | PC ← Jump Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _ | _ | - | ı        | _ | _        | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BC<br>CC<br>DC<br>EC<br>FC                       | dd<br>hh II<br>ee ff<br>ff                | 2<br>3<br>4<br>3<br>2                |

| JSR opr<br>JSR opr<br>JSR opr,X<br>JSR opr,X<br>JSR ,X                                             | Jump to Subroutine               | PC $\leftarrow$ (PC) + $n$ ( $n$ = 1, 2, or 3)<br>Push (PCL); SP $\leftarrow$ (SP) - 1<br>Push (PCH); SP $\leftarrow$ (SP) - 1<br>PC $\leftarrow$ Unconditional Address                                                                                                                                                                                                                                                                                                                                                       | _ | _ | - | ı        | _ | _        | DIR<br>EXT<br>IX2<br>IX1<br>IX                      |                                                  | dd<br>hh II<br>ee ff<br>ff                | 4<br>5<br>6<br>5<br>4                |

| LDA #opr<br>LDA opr<br>LDA opr<br>LDA opr,X<br>LDA opr,X<br>LDA opr,SP<br>LDA opr,SP<br>LDA opr,SP | Load A from M                    | A ← (M)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0 | _ | ı | <b>‡</b> | ‡ | _        | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | C6                                               |                                           | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

Table 5. Instruction Set Summary (Sheet 5 of 7)

| Source<br>Form                                                                                    | Operation Description               |                                                                                                                                                                                                       |           |    |   | ec       |          |   | Address<br>Mode                                     | Opcode                                           | Operand                                   | Cycles                               |

|---------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----|---|----------|----------|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------|

| 1 01111                                                                                           |                                     |                                                                                                                                                                                                       | ٧         | Н  | I | N        | Z        | С | Add                                                 | obo                                              | do                                        | Cyc                                  |

| LDHX #opr<br>LDHX opr                                                                             | Load H:X from M                     | $H:X \leftarrow (M:M+1)$                                                                                                                                                                              | 0         | -  | - | ‡        | 1        | - | IMM<br>DIR                                          | 45<br>55                                         | ii jj<br>dd                               | 3 4                                  |